We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

186,000

200M

Our authors are among the

TOP 1% most cited scientists

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

# Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

### Continuous-Time Analog Filtering: Design Strategies and Programmability in CMOS Technologies for VHF Applications

Aránzazu Otín, Santiago Celma and Concepción Aldea Group of Electronic Design, Aragón Institute for Engineering Research (I3A). Zaragoza University, Zaragoza. Spain

#### 1. Introduction

The evolution of wireless applications (the performance as well as the number of users) has undergone explosive growth in the last years, resulting in an increasing demand for smaller, low-cost wireless transceivers with low power consumption. In order to meet this demand, continuous development must take place both in CMOS technology and in RF electronics, the goal of which should be to achieve a fully-integrated single-chip receiver in a low-cost CMOS process. This demand for complex read channel and multi-standard receiver ICs calls for the design and implementation of one category of analog interface chips as continuous-time (CT) filters, suitable for high speed with variable bandwidths over a wide frequency range, preferably using the G<sub>m</sub>-C approach rather than other existing solutions.

Filters based on the  $G_m$ -C technique were used quite early on with bipolar technology and they have now become the dominant option to implement monolithic filters for very high frequency. The basic building block of a  $G_m$ -C filter is the integrator, which involves the use of transconductors and capacitors only and whose structure is therefore simpler than others, such as operational amplifiers. The simplicity of the transconductor coupled with the openloop operation, which does not involve any complex frequency compensation schemes, point to this cell as the basic active element to be considered and the best option to operate in a VHF range with low supply voltages.

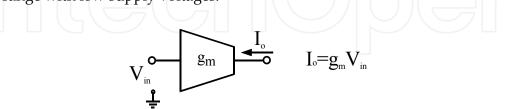

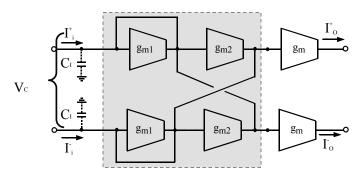

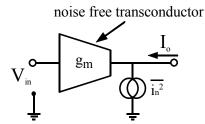

Fig. 1. Ideal transconductor V<sub>in</sub> to I<sub>o</sub> converter of transconductance g<sub>m</sub> (conversion factor).

All the benefits of the  $G_m$ -C approach lie in the ideal behaviour of the transconductor. Nevertheless, its use as the basic element in the VHF active filter implementation forces one to consider some drawbacks related with the non-idealities of this fundamental cell: finite output resistance, finite bandwidth, noise, non-linearity, etc. The main disadvantages inherent to this technique are its high sensitivity to parasitic capacitors and the non-linear

Source: Advances in Solid State Circuits Technologies, Book edited by: Paul K. Chu, ISBN 978-953-307-086-5, pp. 446, April 2010, INTECH, Croatia, downloaded from SCIYO.COM

behaviour of the transconductor, to the extent of appearing a distortion brought about mainly by the non-linearities generated in the V-I conversion. Certain specific strategies require to be used to minimize these effects.

By taking differential or balanced transconductor structures into account, distortion is reduced (even non-linear components are cancelled) and better immunity to common-mode noise is obtained. Furthermore, the use of tuning techniques compensates parameter deviations due to process and temperature variations. These ideas, together with a careful layout, a detailed study of the technology and a deep analysis of the device, lead to an improvement in the transconductor behaviour, and consequently, in the filter performance. Thus, while developing the design of an active  $G_m$ -C filter, the effects of transconductor non-idealities must be analysed in depth to achieve optimum filter performance. The implementation of the transconductor should show a trade-off between dc-gain, linearity and low phase-error at the cut-off frequency.

Any pole or zero frequency in filters based on the  $G_m$ -C technique is of the  $G_m/C$  type. This means that there are two fundamental ways of programming the frequency response of the filter: keeping  $G_m$  constant and varying C, or vice versa. The choice of filter approach will affect noise and power dissipation (Pavan et al., 2000). The constant-C approach has the advantage of maintaining the noise specifications constant over the entire programming range while decreasing the power consumption for lower frequencies. Due to the above considerations, the constant-C scaling technique is the preferred approach for implementing filters operating in a very high frequency range, focusing on the design of tunable CMOS transconductors. On the other hand, discrete tuning is currently being more widely used than continuous tuning, both to preserve the dynamic range and take advantage of the digital system in mixed design to determine the control signal that calibrates and reconfigures the filter. A possible discrete tuning technique is based on a parallel connection of transconductors, where the desired time-constant can be digitally programmed (Pavan et al., 2000a). This approach succeeds in keeping the Q-factor constant and maintains an adequate dynamic range over the entire bandwidth setting.

The target is to implement a transconductor that is compatible with the latest low-cost pure digital CMOS technologies and programmable over a very high frequency range while maintaining an adequate dynamic range (DR). The concrete values of these specifications depend on each particular application. This work does not focus on a concrete application but on carrying out an overall analysis to seek the structure that provides the best trade-off between operation frequency, programmability, dynamic range and power consumption.

Considering all these points, an optimal solution for digitally programmable analog filters in the VHF/UHF range is to take advantage of current-mode pseudo-differential topologies and endow them with digital programmability. The design strategy is therefore as follows: after analysing the transconductor parameters that limit its ideal behaviour, a very well-known current-mode topology (Smith et al., 1996; Zele et al., 1996) will be characterized; starting from the Zele-Smith architecture, two different transconductors will be presented and in-depth analysis will be carried out, following which all the characteristic parameters of each active cell will be obtained; programmability will then be added to the VHF transconductors and the experimental results of a low-cost  $0.35 \ \mu m$  CMOS implementation will be presented. As the active cell is based on a classical structure, a broad diversity of digitally programmable and continuously tunable CT filters can be obtained, where the programmability exhibited by the filter is achieved due to the design of a generic programmable transconductor. Due to the lack of special capacitor structures in standard digital technologies, the use of the MOS structure as

an intended passive device is probably as old as the MOS transistor concept itself. An alternative to implementing linear capacitors is to use the *gate-to-channel capacitance* of MOSFET devices as capacitors, where the gate-oxide thickness is a well-controlled variable in the process. This option will be considered in this work.

Therefore, in this chapter we will show the best way to implement key analog building blocks of a high-speed system in a CMOS technology with a wide programmable frequency range; considering new design techniques and uncovering potential problems associated with the design of high-speed analog circuits using short-channel and low-voltage devices. These are the challenges of CMOS filter design at very high frequencies and this study addresses the theoretical and practical problems encountered in the design of robust, programmable continuous-time filters with very high bandwidths implemented in low-cost digital CMOS technologies.

#### 2. The Integrator: building-block in the Gm-C technique

The majority of continuous-time (CT) integrated filters, circuits where high frequency at low cost of silicon and power is required, present a frequency response controlled by time-constants, and one of the simplest implementations for these factors is taking advantage of the integrator structure. Therefore, the integrator is the dominant building block for many high-frequency active circuit design techniques, and its frequency response and linearity directly determine the filter performance.

Accordingly, systems based on the  $G_m$ -C technique are the first option for implementing CT filters, thanks to their acceptable performance over the VHF range. The active building element used by the  $G_m$ -C filter approach, based on an open-loop integrator, is the transconductor cell (Fig. 1), which ideally delivers an output current proportional to the input signal voltage:

$$I_o = g_m V_{in} \tag{1}$$

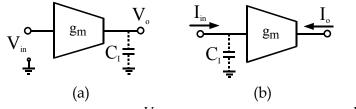

where  $g_m$  is the transconductance of the element. When a grounded capacitor is connected to the output node of the transconductor in order to take this current out, an integrator is obtained leading to  $V_{in}$ - $V_o$  conversion, as shown in Fig. 2(a). It turns out that an ideal voltage-mode integrator has been obtained with a simple transconductance-capacitor combination. Nevertheless, a second structure can be considered taking into account the current-mode signal processing, whereby two different, yet completely equivalent, topologies are obtained. In this case, the input current is taken across the integration capacitance in order to obtain the transconductor input voltage and then, after the active cell, the output current. Thus, Fig. 2(b) shows the  $I_{in}$ - $I_o$  conversion.

Fig. 2. Ideal integrator; (a) voltage-mode:  $\frac{V_o}{V_{in}} = -\frac{g_m}{sC_I}$ , (b) current-mode:  $\frac{I_o}{I_{in}} = \frac{g_m}{sC_I}$ .

Due to the grounded location of most parasitic capacitors of the active cell (the total output/input node effective parasitic capacitance, depending on the configuration), they must be considered by constituting a percentage of the total integration capacitance  $C_I$ , which is particularly significant at high frequencies. An extreme situation can be reached when considering the proposed transconductor as an integrator where total integration capacitance  $C_I$  is constituted only by these parasitic capacitances, with no need for any external capacitor. Nevertheless, these capacitances are not linear and, depending on their contribution, the total linearity of the system will be affected. As technological process variations will also affect the value of these parasitic capacitances, sensitivity to these capacitors requires a detailed study of the device models and integration technology together with a careful system layout.

The ideal integrator has an infinite dc-gain and no parasitic effects, thus obtaining a phase of  $-\pi/2$  for all the frequencies. The unity-gain frequency is  $\omega_t = g_m/C_I$ . Nevertheless, a real integrator presents a non-zero transconductor output conductance  $g_{out}$  and parasitic poles and zeros, which distort the transfer function:

$$H(s) = A_{DC} \frac{\left(1 - \frac{s}{\omega_2}\right)}{\left(1 + \frac{s}{\omega_1}\right)}$$

(2)

where  $A_{DC}=g_m/g_{out}$  is the dc-gain and  $\omega_1=\omega_t/A_{DC}=g_{out}/C_I$  is the frequency of the dominant pole. The effects of parasitic poles and zeros at frequencies much higher than the frequency range of the transconductor can be modelled with a single effective zero  $\omega_2$ : positive  $\omega_2$  results in an effective parasitic RHP-zero and negative  $\omega_2$  in an LHP-zero.

Non-zero transconductor output conductance  $g_{out}$  causes finite dc-gain in real integrators in the filter. In addition, parasitic poles and zeros in the integrator transfer function, together with finite  $A_{DC}$ , generate deviations of the inverter integrator phase response from  $-\pi/2$ , and it is well-known that phase error is the main source of misfunctions in filters. In particular, phase deviations around  $\omega_t$  can cause significant errors in the filter transfer, depending on filter quality factors. The accuracy of the overall frequency response of the filter depends on how closely the individual integrators in the filter follow the ideal response. The filter remains very close to the ideal one if the integrator phase at its unity-gain frequency  $\omega_t$  is equal to its ideal value  $-\pi/2$ ; the amount by which the phase at  $\omega_t$  deviates from this quantity will be called  $\Delta \varphi(\omega_t)$ .

$$\varphi(\omega_t) = -\frac{\pi}{2} + \tan^{-1}\left(\frac{\omega_1}{\omega_t}\right) - \tan^{-1}\left(\frac{\omega_t}{\omega_2}\right) \Rightarrow \Delta\varphi(\omega_t) \approx \tan^{-1}\left(\frac{g_{out}}{g_m}\right) - \tan^{-1}\left(\frac{\omega_t}{\omega_2}\right)$$

(3)

Low dc-gain causes a leading phase error, and parasitic high-frequency poles and zeros in the integrator create lagging ( $\omega_2>0$ , RHP-zero) or leading ( $\omega_2<0$ , LHP-zero) phase errors. The acceptable worst case value of  $\Delta \varphi(\omega_t)$  depends on the specifications for the high-frequency response of the overall filter and the poles and quality factor of the transconductor transfer function. The integrator phase error can be modelled with a frequency-dependent integrator quality factor Q<sub>int</sub> (Nauta, 1993), concluding that a high and accurate filter quality factor puts strong constraints on the integrators phase error, i.e. on Q<sub>int</sub>.

$$\frac{1}{Q_{\rm int}(\omega)} \approx \Delta \varphi(\omega) = \frac{\omega_1}{\omega} - \frac{\omega}{\omega_2}$$

(4)

The filter performance is dominated by the performance of the transconductors, since the filter specifications (dynamic range, dissipation and chip area) depend not only on filter properties (Q, cut-off frequency, impedance level) but also on transconductor properties ( $A_{DC}$ ,  $\omega_t$ ,  $\omega_1$ ,  $\omega_2$ , noise behaviour, linearity, area and power consumption). It is therefore useful to put effort into the study of a high-performance transconductor that would improve all its specifications, in order to obtain a proper design for these VHF filter building blocks.

#### 3. Fully-balanced pseudo-differential transconductor cell

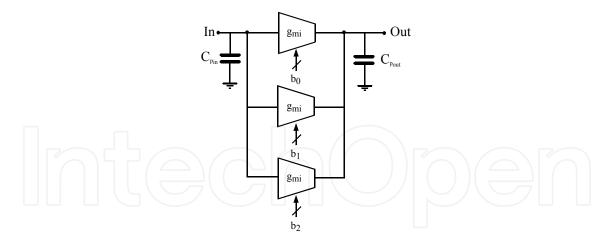

In this section, the development of a fully-balanced current-mode integrator based on a classical structure is described, which is characterized by low-power, high rejection of supply noise and VHF potential application. Fig. 3 shows the conceptual scheme of the Zele-Smith pseudo-differential integrator (Smith et al., 1996; Zele et al., 1996), a complete fully-balanced transconductance cell arranged for using a current-mode integrator.

Fig. 3. Conceptual scheme of the complete fully-balanced current-mode transconductor.

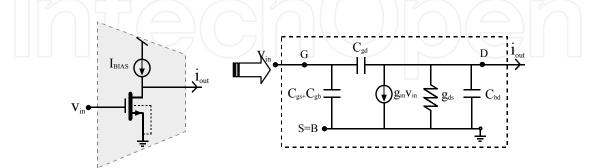

To understand the basic operation we analyse the simple first-order model of the proposed transconductor, considering each unit cell as a simple transistor, i.e., single common-source stages as shown in Fig. 4. Under these conditions, the small-signal analysis gives the expression for the differential gain of the integrator (Eq. 5), where gmi is the i-cell transconductance and  $g_0$  is the sum of output conductances  $g_{dsi}$  at the input node.

Fig. 4. Small-signal model for the common-source transconductor stage.

By analysing this expression and considering a first-order approximation, i.e., neglecting the  $g_{ds}$  effects of each transistor, an infinite dc-gain is achieved if perfect matching is obtained between  $g_{m1}$  and  $g_{m2}$ , so that  $\delta g_m = g_{m1} - g_{m2} = 0$ . Nevertheless, the effect of the output

conductances is not avoidable and the implementation of a negative resistance ( $\delta g_m < 0$ ), inherent to this topology, provides the possibility of achieving dc-gain enhancement. Note that by making  $\delta g_m + g_o \rightarrow 0$ , then  $|A_{DC}| \rightarrow \infty$ . In practice, mismatching between transistors limits the differential gain by up to 55 dB at most. Another equivalent way for analysing this improvement is to consider the differential-mode input resistance of the transconductor cell.

$$A_{DC} = \left| \frac{I_{O}^{+} - I_{O}^{-}}{I_{i}^{+} - I_{i}^{-}} \right| \approx \frac{g_{m}}{g_{m1} - g_{m2} + g_{O}^{+}} \cong \frac{g_{m}}{\delta g_{m} + g_{O}^{+}}; \quad R_{D}(in) \approx \frac{2}{g_{m1} - g_{m2} + g_{O}^{+}} = \frac{2A_{DC}}{g_{m}}$$

(5)

As a result, this scheme shows the basic pseudo-differential structure obtained by considering two dual transconductor cells  $(g_m)$ , leading to current integration through input capacitance  $C_I$ . Thanks to the additional negative resistance shown in grey in the same figure, dc-gain is increased by providing positive feedback compensation for the signal current and boosting the input resistance of the transconductor.

The approximate common-mode gain, which must be less than unity to guarantee stability in closed-loop configurations, is constrained by device ratios to a stable value over all frequencies (Eq. 6). Common-mode stability is assured by designing  $(g_{m1}+g_{m2})/g_m>1$ . Common-mode behaviour analysis can be also carried out by calculating common-mode input resistance.

$$|A_{CM}| = \left|\frac{I_{O}^{+} + I_{O}^{-}}{I_{i}^{+} + I_{i}^{-}}\right| \approx \frac{g_{m}}{g_{m1} + g_{m2} + g_{O}^{+}}; \quad R_{CM}(in) \approx \frac{1}{2(g_{m1} + g_{m2} + g_{O}^{+})} = \frac{|A_{CM}|}{2g_{m}}$$

(6)

The common-mode feedback resulting from the interconnection of the negative resistance provides both a naturally high differential gain and low common-mode gain for the integrator, improving these limits attached to a real integrator structure. Consequently, the basic operation of the transconductor will be best understood by explaining, first, that the common-mode control and dc-enhancement circuitry is connected at the input of the circuit and then, that the linear V-I conversion mechanism occurs in the output stage.

The gain of the basic current integrator is independent of the supply voltage to the firstorder approximation. When fully-differential current topologies are used, the small remaining supply noise feedthrough is common to both sides of the signal and thus has no direct effect, except through random device mismatch. Therefore, the integrator has good immunity to supply noise. Device mismatch can be minimized with careful layout and specific design techniques to around 0.1-1 %, in many applications (Croon et al., 2002; Otin et al., 2004; Otin et al., 2005).

The use of an integrator based on transconductance cells implemented by using single transistors (no internal nodes), results in a proper frequency response because the only nodes are at the inputs and at the outputs. To a first-order approximation, no parasitic poles or zeros exist in the differential ac-response of the basic integrator circuit. Both differential and common-mode gains can be independently set by the different values of  $g_{m1}$  and  $g_{m2}$ . The ideal integrator function is a result of setting  $\delta g_m + g_0' = 0$  and the phase error at the unity-gain frequency,  $\omega_t = g_m/C_L$  can be calculated by:

$$\Delta\varphi(\omega_t) = \tan^{-1}\left(\frac{\omega_1}{\omega_t}\right) \approx \tan^{-1}\left(\frac{\delta g_m + g_o'}{g_m}\right) = \frac{\pi}{2} - \tan^{-1}\left(\frac{g_m}{\delta g_m + g_o'}\right)$$

(7)

To summarize, infinite differential input impedance can be obtained if  $\delta g_m + g_0 \rightarrow 0$  while maximizing the differential dc-gain and minimizing the phase error at  $\omega_t$ , and common-mode input impedance can be reduced by maximizing the sum of the transconductances  $(g_{m1}+g_{m2})$ . Consequently, the common-mode rejection ratio (CMRR) is improved. Nevertheless, an important concept should be borne in mind: as the dc-gain depends on the difference  $(g_0 - |\delta g_m|)$ , the structure can lead to instability if this quantity becomes negative (total negative input conductance) due to overcompensation.

By analysing the small signal model of each common-source stage forming the complete transconductor topology (Fig. 4), the need to solve a frequency problem arises: the feedforward ac-current path from the gate (input) to the drain (output), through the overlap parasitic capacitance  $C_{gd}$ . When considering the stages forming the negative resistance, the repercussion of this effect is not important because the contribution to the total behaviour of the cell decreases as these capacitances are short-circuited with their respective  $g_{mi}$ . However, the feedforward current through  $C_{gd}$  in the fully-balanced output-stage  $g_m$  of the transconductor structure generates a transmission zero ( $g_m/C_{gd}$ ) in the right complex halfplane. This parasitic RHP-zero modifies the integrator frequency response and creates a phase-lag at the unity-gain frequency. Furthermore, the Miller effect, also associated with this parasitic capacitor, introduces larger equivalent input capacitance ( $C_{in}=C_{gs}+C_{gb} \Rightarrow C_{in}=C_{gs}+C_{gb}+(1+A)C_{gd}$ ) and an additional component to the equivalent output capacitance ( $C_{out}=C_{bd} \Rightarrow C_{out}=C_{bd}+(1+A-1)C_{gd}$ ), where  $A\approx g_m/g_{ds}$ . Therefore, the neutralization of this effect will involve bandwidth enhancement.

Many methods have been proposed to minimize the Miller effect: the cascode technique (Gray et al., 2001), the inductor shunt peaking technique (Mohan et al., 2000), the capacitive compensation technique (Wakimoto et al., 1990; Vadipour, 1993), the distributed amplification technique (Ahn et al., 2002) and the active inductor technique (Säckinger et al., 2000). They all have the advantages of low-voltage compatibility and low area; however, the solutions considered in this work will be the use of cascode structures together with the capacitive compensation technique.

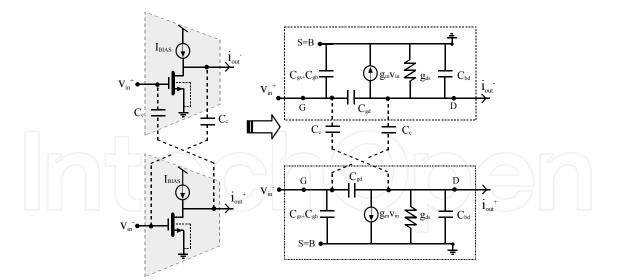

Differential systems allow the  $C_c$ -cancellation technique, using positive feedback to generate negative capacitances, which can cancel the positive ones to yield bandwidth increases. These  $C_c$  capacitors are the overlap  $C_{gd}$  parasitic capacitances of dummy compensation transistors used in a cross-coupled way to neutralize the feedback action of these Miller capacitors. The connection is between the output and the opposite sign input, available in a balanced configuration. Under these conditions, the RHP-zero is moved to infinity, i.e., the cause of phase lag is removed, thus expanding the bandwidth of the transconductor. At the same time, compensation capacitor  $C_c$  will cancel the Miller effect and a lower input node effective capacitance is obtained due to the reduction of the feedforward effect. This technique depends on feeding back a current that is precisely the same as the one flowing through the Miller capacitance  $C_{gd}$  and, in consequence, the neutralization capacitor must match precisely. However, it is remarkable that  $C_{gd}$  is voltage-dependent and compensation can only work with small signals. In the case of mismatch between  $C_{gd}$  and  $C_c$ , parasitic zero is not at infinity and can cause a small phase lag or lead.

However, this is not the full story of the high frequency behaviour of the transconductor cell and there are more frequency limits. Mismatch in common-mode feedback circuits can result in unexpected parasitic poles and zeros. In addition, high frequency models of the MOS transistor show that  $g_m$  is not independent of frequency, but has a finite delay  $g_m(s)$

Fig. 5. Cancellation of transmission zero  $g_m/C_{gd}$  and neutralization of the Miller effect:  $C_c$ -cancellation technique.

and begins to roll off at very high frequencies. Although the frequency where this roll-off begins can be in the GHz range, the phase shift from this effect can become significant at much lower frequencies. Since most active filters are very sensitive to small phase changes in the integrator response, it is thus important to take this effect into account.

The first way to minimize these effects is to eliminate the internal nodes or, if this is not possible, to design them as low-impedance nodes. This procedure can be carried out by considering cascode topologies. Moreover, their use further prevents bandwidth reduction generated by transmission zero because one side of  $C_c$  is connected to the internal low-impedance node, i.e., to the low-gain point of the cascode transistor source.

Therefore, an enhancement of the integrator dc-gain has been obtained with this topology by means of the differential negative resistance, increasing the differential input resistance of the transconductor and keeping the common-mode gain lower than unity. With regard to frequency limit-related problems, transmission zero has been reduced by using C<sub>c</sub>-capacitor compensation, taking advantage of the pseudo-differential topology. This solution can also be improved by considering cascode topologies, giving higher dc-gains in a natural way, which will also reduce the frequency drawbacks associated to the internal nodes of other topologies by avoiding internal high-impedance nodes in the signal path.

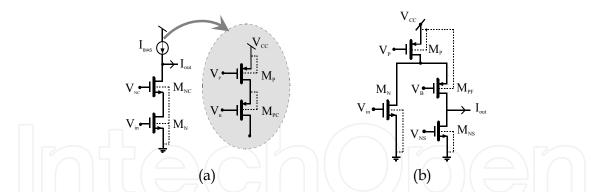

As a result, a low-voltage transconductor with high linearity, very high operation frequency and high power efficiency has been designed where cascode structures should be considered to obtain an improvement in the high-frequency behaviour of the basic topology. The main advantage of using cascode stages instead of single common-source stages is the higher dc-gain while maintaining a good frequency response. Hence, a higher quality factor of the integrator is expected due to the higher differential dc-gain (Abidi, 1988). Basic cascode circuits require high supply voltages to operate due to the large overhead bias from threshold voltages. However, variations of the cascode technique exist which can be used with lower voltage supplies. Two options are considered in this work, the so-called **highswing cascode (HS)** stage and the **folded cascode (FC)** stage (Baker et al., 1998; Sansen et al. 1999; Sedra et al., 2004). The unit cells replacing the common-source stages previously used are shown in Fig. 6. The complete fully-balanced current-mode transconductance cells implemented by using these cascode stages are described in the following sections.

## Continuous-Time Analog Filtering: Design Strategies and Programmability in CMOS Technologies for VHF Applications

Fig. 6. Unit transconductance cell: (a) high-swing (HS) and (b) folded cascode (FC) topology.

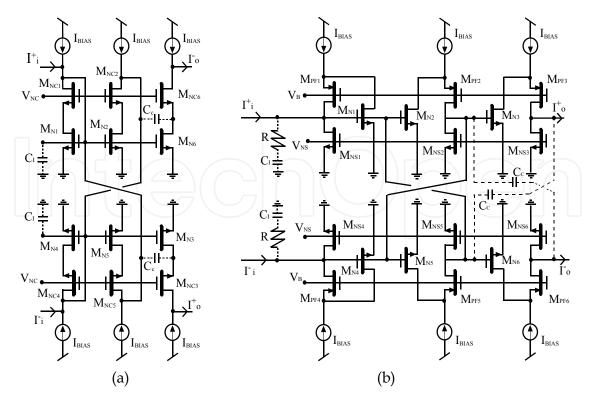

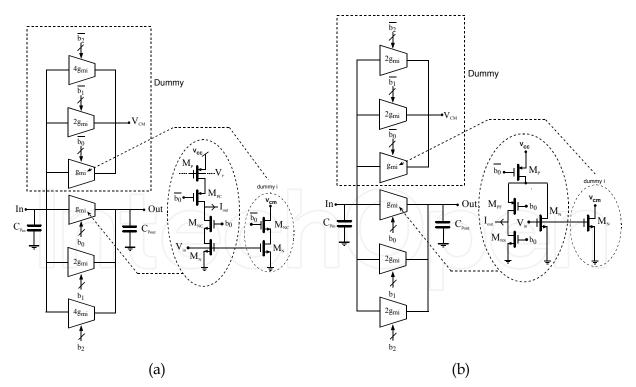

#### 3.1 High-swing cascode section: HS topology

Fig. 7(a) shows the transconductor arranged for using the current-mode integrator described in Fig. 3, where the unit cells have been implemented by using high-swing cascode stages (Baker et al., 1998; Sansen et al. 1999; Sedra et al., 2004). As illustrated in the corresponding HS unit cell (Fig. 6(a)), current sources are also implemented by using high-swing cascode elements. The substrate terminals of NMOS transistors are connected to the reference voltage as usual, and those of the PMOS transistors are connected to the corresponding source node of each transistor.

The use of high-swing cascode elements offers as high accuracy as using basic cascode stages to implement each unit cell of the transconductor but, because of the slightly different connection between transistors, needs lower supply voltage and has fewer internal parasitic poles, generating nodes between the input and the output, giving a better frequency response of the integrator. The main disadvantage of the improved cascode topology is that due to biasing constraints, the gate-source voltages must be kept small, resulting in larger devices for a bias current level.

#### 3.2 Folded cascode section: FC topology

In order to obtain an improvement in biasing flexibility and further reduction of the supply voltage in the design of the transconductor cell, we can also take advantage of folded-cascode sections (Sansen et al. 1999; Sedra et al., 2004). The schematic used to describe the complete integrator based on the proposed current-mode pseudo-differential transconductor is shown in Fig. 7(b), where the unit cells have been implemented by using FC stages illustrated in Fig. 6(b). In this case, current sources are implemented by using single elements, both bias sources  $I_{BIAS}$  and cascode sources  $M_{NSi}$ . The substrate terminals of NMOS transistors are connected to the reference voltage as usual, and those of PMOS transistors, both those used to implement current sources  $I_{BIAS}$  and those implementing folded transistors  $M_{PFi}$ , are connected to the V<sub>CC</sub> node.

The use of folded cascode elements exhibits a substantial improvement in biasing flexibility, because of the increased drain-voltage of the transistors, at the cost of additional current sources and bias voltages. Another significant benefit of using these stages is that by avoiding the biasing constraints associated to the high-swing cascode structure, we obviate the need to keep gate-source voltages low, which results in smaller and simpler devices for a given bias current level, lower voltage supply and larger unity-gain frequencies.

Fig. 7. Fully-balanced pseudo-differential current-mode cell, based on (a) high-swing cascode unit stages: **HS transconductor**; (b) folded-cascode unit stages: **FC transconductor**.

#### 3.3 General considerations: basic principle

A similar notation and index-linking have been adopted in both transconductor implementations in order to simplify the description of the basic principle and to unify the topology analysis. Assuming ideal behaviour for the integrator, the balanced input current flows entirely into integration capacitance  $C_I$ . Diode-connected stages  $M_{1,4}$  adequately bias cascode output  $M_{3,6}$ , whilst transistors  $M_{2,5}$  provide positive feedback compensation for the signal current flowing into  $M_{1,4}$  and boost the input resistance of the integrator.

Regarding the gain enhancement by means of the negative resistance formed by transistors M<sub>2,5</sub>, this technique is absolutely necessary for Zele-Smith topologies and other voltagemode transconductors (Nauta, 1993), in order to obtain reasonably high dc-gain values. Theoretically, the dc-gain could be infinity by adjusting the equivalent negative resistance, but in practice mismatching limits the dc-gain by about 40 dB in single transistor stages. However, the use of cascode topologies leads to a natural enhancement of this parameter and differential dc-gain values of up to 55 dB can be reached with identical transistors under identical bias conditions by means of a lower mismatching sensitive design. Nevertheless, there is a key difference between the HS and the FC cascode structure:

- The high output resistance is directly guaranteed thanks to the true cascode output stage exhibited by the HS transconductor. Therefore, positive feedback compensation is not necessary to boost differential resistance or enhance the dc-gain.

- On the other hand, the output-node for the FC transconductor is not a very high impedance node, and the negative resistance proves necessary to obtain real input resistance enhancement. In this approach, positive feedback compensation for the signal current flowing into M<sub>3,6</sub> is essential, boosting the input resistance of the integrator and increasing dc-gain.

The reason for this difference is that the FC unit cell considered and shown in Fig. 6(b) is a pseudo-cascode topology. To obtain similar output impedance to that of the HS approach, the M<sub>NS</sub> current source would have to be implemented by using a cascode current source. Nevertheless, even if the HS implementation undergoes an immediate dc-gain/input resistance improvement, both topologies require positive feedback compensation (negative resistance) to reduce common-mode gain (common-mode input resistance) and stabilize common-mode voltages. On the other hand, the use of pseudo-differential structures requires careful and efficient control over the common-mode behaviour of the circuit. It is worth noting that this structure not only stabilises the common-mode voltage, but also rejects common-mode signals by means of partial positive feedback. This idea has already been used for high-frequency transconductors in (Nauta, 1993) and for a class of current-mode filters (Smith et al., 1996; Zele et al., 1996).

Thus, considering this topology implemented by using cascode stages, dc-gains of about 55 dB and CMRR of 60 dB can be obtained with inherent stability of common-mode voltages. Note that the propagation of common-mode (CM) signals in balanced circuits can instability and distortion. Further, current consumption, cause linearity and transconductance value are strongly dependent on the CM input signals. Additional techniques can be used in the proposed topology if a greater CMRR is needed, such as feedforward cancellation of the input CM signal. Balanced transconductors with high-input common-mode rejection that are capable of operating with low-voltage supplies are obtained by using an additional transconductor that is only sensitive to CM signals (Baschirotto et al., 1994; Wyszynski et al., 1994). Considering this technique, CMRR values up to 70 dB could be obtained.

#### 4. High frequency response

In this section, the bandwidth of the transconductor will be analysed. Note that if single transistor stages and unrealistic simplified models are used in the proposed topology (Fig.3), the bandwidth could be infinite owing to the absence of internal nodes influencing the transfer function of the integrator. A more complete model of the MOS transistor does predict a finite bandwidth due to the second-order frequency effects such as the transmission zero associated to overlap parasitic capacitance  $C_{gd}$ , frequency dependence of the transconductance  $g_m(s)$  and mismatch in common-mode feedback circuits. A closer explanation of MOS behaviour at high-frequencies (splitting it into an **intrinsic** and an **extrinsic** part) is required before starting the study of the complete integrator. Taking into account a non-quasistatic model (Tsividis, 1996), the high-frequency behaviour of the current mode integrator will be calculated.

When analysing transconductor bandwidth, several general factors must be considered:

- The output of the complete transconductor may be assumed to be short-circuited for acsignals when calculating the frequency response of the integrator.

- In all the equations:  $g_m$  is the transconductance,  $g_{ds}$  the output conductance,  $g_{mb}$  the bulk-transconductance and  $C_{gd}$ ,  $C_{gs}$ ,  $C_{ds}$ ,  $C_{bs}$  and  $C_{bd}$  the parasitic capacitances.

- All the unit cells are designed to seek perfect matching between them. Therefore, all similar transistors have the same properties except for transconductance g<sub>m</sub> of the N-transistor processing the signal (M<sub>N</sub> transistor in both unit cells shown in Fig. 6). In this way, considering the notation and index-linking previously used in Fig. 3: g<sub>m</sub>(N<sub>1</sub>)=A<sub>N</sub>g<sub>m</sub>(N); g<sub>m</sub>(N<sub>2</sub>)=A<sub>P</sub>g<sub>m</sub>(N); g<sub>m</sub>(N<sub>3</sub>)=g<sub>m</sub>(N). Consequently, δg<sub>m</sub>=(A<sub>N</sub>-A<sub>P</sub>)g<sub>m</sub>

represents the difference between  $M_1$  and  $M_2$ , or,  $M_4$  and  $M_5$  due to the difference in dimensions and bias currents of N-transistors, which gives rise to the negative resistance that enhances the dc-gain of the system.

- Total integration capacitance C<sub>I</sub> comprises not only the external capacitance, but also the contribution of parasitic capacitors (C<sub>I</sub>=C<sub>ext</sub>+C<sub>p</sub>). Intrinsic capacitance C<sub>gs</sub> is the main contribution of these parasitic capacitances C<sub>p</sub> and consideration of it as a great percentage of total integration capacitance acquires great significance.

- External capacitor C<sub>ext</sub> can be implemented by using double-poly, metal-metal or MOS capacitors, depending on the technological process.

- Current source is modelled with a Norton equivalent circuit, where G<sub>s</sub> and C<sub>s</sub> are the admittance and capacitance components. The external capacitance C<sub>ext</sub> connected to the transconductor input is in parallel with C<sub>s</sub>. For purposes of simplicity, from now on, C<sub>s</sub> will include the equivalent capacitance of the current source and the external capacitance (C<sub>s</sub>≡C<sub>s</sub>+C<sub>ext</sub>). Therefore, total integration capacitance can be expressed as: C<sub>I</sub>=C<sub>s</sub>+C<sub>p</sub>, including parasitic effects, the external capacitance and the equivalent-model of the non-ideal current source.

Firstly, a model for the V-I conversion of the unit cell is derived, in both implementations to show the calculation process of the bandwidth of the complete transconductance cell.

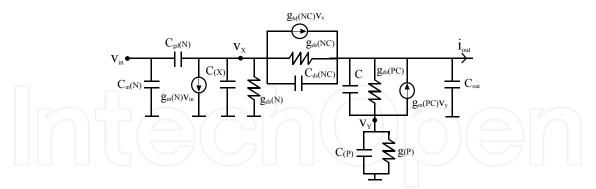

#### 4.1 High-frequency model of the HS unit cell

The following circuit represents the high frequency model for the HS unit cell previously shown in Fig. 6(a), where X(N) denote the parameters associated to the M<sub>N</sub>-transistor, X(NC) those associated to the cascode transistor, X(P) those associated to current sources  $I_{BIAS}$  and X(PC) those associated to the cascode current sources as shown in Fig. 6(a). Table 1 summarizes the parameters associated to the impedances shown in the small-signal equivalent circuit. The rest of the elements:  $g_m(N)$ ,  $g_{ds}(N)$ ,  $g_{ds}(NC)$ ,  $g_{ds}(PC)$ ,  $g_m(PC)$ ,  $C_{gd}(N)$  and  $C_{ds}(NC)$  directly represent the parameters of the respective transistor.

| $g_M(NC) = g_m(NC) + g_{mb}(NC)$                                     | $g(P) = g_{ds}(P)$                                       |  |  |

|----------------------------------------------------------------------|----------------------------------------------------------|--|--|

| $C_{in}(N) = C_{gs}(N) + C_{gb}(N)$                                  | $C(x) = C_{ds}(N) + C_{bd}(N) + C_{gs}(NC) + C_{bs}(NC)$ |  |  |

| $C = C_{ds}(PC) + C_{bd}(PC)$                                        | $C_{out} = C_{gb}(NC) + C_{bd}(NC) + C_{gd}(PC)$         |  |  |

| $C(P) = C_{gd}(P) + C_{ds}(P) + C_{bd}(P) + C_{gb}(PC) + C_{gs}(PC)$ |                                                          |  |  |

Table 1. Small-signal parameters for the HS unit cell.

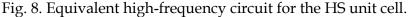

#### 4.2 High-frequency model of the FC unit cell

The following circuit represents the high frequency model for the FC unit cell previously shown in Fig. 6(b), where X(N) are the parameters associated to the M<sub>N</sub>-transistor, X(PF)those associated to the folded transistor, X(P) those associated to the current sources IBIAS and X(NS) those associated to the current source of the folded transistor, which is implemented with a single NMOS transistor as previously illustrated.

Fig. 9. Equivalent high-frequency circuit for the FC unit cell.

Table 2 summarizes the parameters associated to the impedances shown in the small-signal equivalent circuit. The rest of the elements:  $g_m(N)$ ,  $g_{ds}(PF)$ ,  $C_{gd}(N)$  and  $C_{ds}(PF)$  directly represent the parameters of the respective transistor.

$$g = g_{ds}(N) + 2g_{ds}(P) \qquad C_{in}(N) = C_{gs}(N) + C_{gb}(N)$$

$$g_{out} = g_{ds}(NS) \qquad C = C_{ds}(N) + C_{bd}(N) + 2C_{gd}(P) + 2C_{ds}(P) + 2C_{bd}(P) + C_{gs}(PF) + C_{bs}(PF)$$

$$g_{MP}(PF) = g_{m}(PF) + g_{mb}(PF) \qquad C_{out} = C_{gd}(PF) + C_{bd}(NS) + C_{ds}(NS) + C_{bd}(NS)$$

Table 2. Small-signal parameters for the FC unit cell.

Great similarity is obtained in the description of both unit cells. Even the FC capacitive parameter C will be equivalent to C+C(x) in the HS description. This parallelism will also appear in the complete transconductor analysis.

#### 4.3 High-frequency model of the complete transconductance cell

Under these conditions, the differential gain of the proposed transconductor cell (in both implementations) can be calculated by:

here:

$$H(s) = k \frac{(s-s_0)(s+s_1)}{s^2 + x_1 s + x_2} \approx K \frac{(s-s_0)}{(s+\delta_1)(s+\delta_2)}$$

(8)

$$K = \frac{-A_{DC} \,\delta_1 \,\delta_2}{s_0}; \quad x_1 = \frac{\beta}{\gamma}; x_2 = \frac{\alpha}{\gamma}; \quad \delta_1 = \frac{\alpha}{\beta} = \frac{x_2}{x_1}; \quad \delta_2 = \frac{\beta}{\gamma} - \delta_1 \approx \frac{\beta}{\gamma} = x_1 \tag{9}$$

Denominator factorization of Eq.(8) leads to obtain two parasitic poles,  $-\delta_1$  and  $-\delta_2$ , but only if the approximation  $(\alpha \cdot \gamma / \beta^2) < 1$  is verified. Furthermore, parasitic zero  $-s_1$  must be negligible in the frequency range of interest. Both considerations will be demonstrated, either in the HS or in the FC approach ( $s_1 >>s$  and  $s_1 >>s_0$ :  $s_1(HS)=1600 s_0=1100$  GHz,  $s_1(FC)=30 s_0=1900 \text{ GHz}$ ).

Due to the use of a pseudo-differential structure, a careful study of the common-mode behaviour is mandatory. Thanks to the topology proposed, the common-mode voltage is stabilized by means of partial positive feedback as previously explained. Under these assumptions:

$$A_{CM}(s) = k_{CM} \frac{(s - s_0)(s + s_1)}{s^2 + y_1 s + y_2} \approx K_{CM} \frac{(s - s_0)}{s^2 + y_1 s + y_2}$$

(10)

$$K_{CM} = \frac{-A_{CM} y_2}{s_0}; \quad y_1 = \frac{\beta_{CM}}{\gamma_{CM}}; y_2 = \frac{\alpha_{CM}}{\gamma_{CM}}$$

(11)

Eq.(10) once more shows the need to neglect parasitic zero  $-s_1$ , leading to the same consideration as in the differential gain equation. In this analysis, denominator factorization is more difficult to accomplish. However, the approximate equations are easily derived and, making use of the figures obtained in each particular design, the possibility of using the approximate common-mode transfer function will be analysed. Therefore, if  $(\alpha_{CM}\cdot\gamma_{CM}/\beta_{CM}^2) <<1$  is verified, the common-mode gain can be expressed as:

$$A_{CM}(s) = K_{CM} \frac{(s - s_0)}{(s + \xi_1)(s + \xi_2)}$$

(12)

$$\xi_{1} = \frac{\alpha_{CM}}{\beta_{CM}} = \frac{y_{2}}{y_{1}}; \quad \xi_{2} = \frac{\beta_{CM}}{\gamma_{CM}} - \xi_{1} \approx \frac{\beta_{CM}}{\gamma_{CM}} = y_{1}$$

(13)

Both transfer functions are characterized by two parasitic poles and one RHP-zero; the differential-mode by  $-\delta_1$ ,  $-\delta_2$ , and  $s_0$ ; and the common-mode by  $-\xi_1$ ,  $-\xi_2$ , and  $s_0$  (zero  $s_0$  is the same in both transfer functions)<sup>1</sup>. Consequently, in order to obtain a transconductor design that is compatible with all the requirements of the active G<sub>m</sub>-C filter implementation, a proper analysis and characterization of these parasitic elements becomes a top-priority challenge. From this study, their origin and frequency location may lead to some design considerations to improve the integrator frequency response.

Differential dc-gain, common-mode dc-gain,  $s_0$  and  $s_1$  are summarized in table 3 for both implementations. The parasitic poles can be calculated by using  $\alpha$ ,  $\beta$ ,  $\gamma$ ,  $\alpha_{CM}$ ,  $\beta_{CM}$ ,  $\gamma_{CM}$ , as shown in Eqs.(9) and (13). As the resulting relations are very complicated, it is necessary to look for the dominant terms and obtain approximate expressions to draw conclusions. They can be simplified to analyse and understand the behaviour of the transconductance cell and its frequency limits that are associated to second order effects, which differentiate between the frequency behaviour of the proposed topology and the expected ideal response.

#### 4.4 HS transconductance cell frequency response

Considering the previous study of the HS unit cell, a detailed analysis of the frequency response of the complete HS integrator is carried out. The dominant terms of these expressions are subsequently obtained in this section. In order to simplify the notation, the small-signal parameters are redefined in table 4.

<sup>&</sup>lt;sup>1</sup> According to stable systems, negative poles  $-\delta_1$ ,  $-\delta_2$ ,  $-\xi_1$  and  $-\xi_2$  have been obtained in the transfer functions for both implementations. For purposes of simplicity, when referring to these poles, their associated frequency ( $\delta_1$ ,  $\delta_2$ ,  $\xi_1$ ,  $\xi_2$ ) will be the considered magnitude.

# Continuous-Time Analog Filtering: Design Strategies and Programmability in CMOS Technologies for VHF Applications

|                 | HS transconductor                                            | FC transconductor                                               |

|-----------------|--------------------------------------------------------------|-----------------------------------------------------------------|

| $S_0$           | $s_0 = \frac{g_m(N)}{C_{gd}(N)}$                             | $s_0 = \frac{g_m(N)}{C_{gd}(N)}$                                |

| $S_1$           | $s_1 = \frac{g_M(NC) + g_{ds}(NC)}{C_{ds}(NC)}$              | $s_1 = \frac{g_{MP}(PF) + g_{ds}(PF)}{C_{ds}(PF)}$              |

| A <sub>DC</sub> | $A_{DC} = \frac{g_m(N)(g_M(NC) + g_{ds}(NC))}{\alpha}$       | $A_{DC} = \frac{g_m(N)(g_{MP}(PF) + g_{ds}(PF))}{\alpha}$       |

| A <sub>CM</sub> | $A_{CM} = \frac{-g_m(N)(g_M(NC) + g_{ds}(NC))}{\alpha_{CM}}$ | $A_{CM} = \frac{-g_m(N)(g_{MP}(PF) + g_{ds}(PF))}{\alpha_{CM}}$ |

Table 3. Summary of the high-frequency parameters.

$$G = g_{ds}(N) + g_{M}(NC) + g_{ds}(NC)$$

$$C_{IN} = C_{s} + 2C_{in}(N) + C_{out} = C_{s} + 2C_{gs}(N) + 2C_{gb}(N) + C_{gb}(NC) + C_{bd}(NC) + C_{gd}(PC)$$

$$C_{\beta} = C_{out} + C_{in}(N) = C_{gs}(N) + C_{gb}(N) + C_{gb}(NC) + C_{bd}(NC) + C_{gd}(PC)$$

Table 4. Impedance parameters for the HS integrator.

By analysing in detail the small-signal equivalent model for the complete HS integrator, the value of total integration capacitance  $C_I$  can be calculated by Eq.(14). This definition will lead to a simplification of the parasitic pole expressions.

$$C_{I} = C_{IN} + C_{\beta} = C_{s} + 3C_{in}(N) + 2C_{out}$$

(14)

Firstly, the differential and common-mode gain can be expressed as follows:

$$A_{DC} \approx \left[ \left( A_N - A_P \right) + \frac{2g_{ds}(NC)g_{ds}(N)}{g_m(N)(g_M(NC) + g_{ds}(NC))} \right]^{-1}$$

(15)

$$A_{CM} \approx -\left[ (A_N + A_P) - \frac{2g_{ds}(NC)g_{ds}(N)}{g_m(N)(g_M(NC) + g_{ds}(NC))} \right]^{-1} \approx \frac{-1}{A_N + A_P}$$

(16)

In these expressions, the differential negative resistance obtained by the partial positive feedback compensation is shown by means of the difference  $\delta g_m = (A_N - A_P)g_m(N)$ . The existence of this negative resistance allows the differential dc-gain to be enhanced. Parasitic poles  $\delta_1$  and  $\delta_2$  can be calculated by means of ratios between  $\alpha$ ,  $\beta$  and  $\gamma$ . Final expressions are summarized in table 6. The origin of second order effects can be better understood by focusing on their dependence.

$$\alpha \approx ((A_N - A_P)g_m(N))(g_M(NC) + g_{ds}(NC)) + 2g_{ds}(NC)g_{ds}(N) \approx 2g_{ds}(NC)g_{ds}(N)$$

(17)

$$\beta \approx G(C_s + 3C_{in}(N) + 2C_{out}) = G C_I$$

(18)

where considering the dominant term in the transconductance G, the expression can be written as:

$$\beta \approx (g_{ds}(N) + g_M(NC) + g_{ds}(NC))C_I \approx g_M(NC)C_I$$

<sup>(19)</sup>

Therefore, the parasitic pole  $\delta_1$  can be expressed as:

$$\delta_1 = \frac{\alpha}{\beta} \approx \frac{2g_{ds}(NC)g_{ds}(N)}{g_M(NC)C_I}$$

(20)

Following the same process for the other pole  $\delta_2$ , we obtain:

$$\gamma \approx C_I \left( C_{gd}(N) + C_{ds}(NC) + C(x) \right) \approx C_I C(x) \approx C_I C_{gs}(NC)$$

(21)

$$\delta_{2} = \frac{\beta}{\gamma} \approx \frac{G}{C(X)} = \frac{g_{ds}(N) + g_{M}(NC) + g_{ds}(NC)}{C_{ds}(N) + C_{bd}(N) + C_{gs}(NC) + C_{bs}(NC)} \approx \frac{g_{M}(NC)}{C_{gs}(NC)}$$

(22)

Similar results can be obtained for the common-mode frequency response:

$$\alpha_{CM} \approx \left( \left( A_N + A_P \right) g_m(N) \right) \left( g_M(NC) + g_{ds}(NC) \right) \approx \left( A_N + A_P \right) g_m(N) g_M(NC)$$

(23)

$$\beta_{CM} \approx \beta \approx g_M(NC) C_I; \quad \gamma_{CM} \approx \gamma \approx C_I C_{gs}(NC)$$

(24)

$$\xi_{1} = \frac{\alpha_{CM}}{\beta_{CM}} \approx \frac{(A_{N} + A_{P})g_{m}(N)g_{M}(NC)}{GC_{I}} \approx \frac{(A_{N} + A_{P})g_{m}(N)}{C_{I}}; \quad \xi_{2} = \frac{\beta_{CM}}{\gamma_{CM}} \approx \delta_{2} \approx \frac{G}{C(X)} \approx \frac{g_{M}(NC)}{C_{gs}(NC)}$$

(25)

#### 4.5 FC transconductance cell frequency response

Considering the previous study of the FC unit cell, a detailed analysis of the frequency response of the complete FC integrator is carried out. The dominant terms of these expressions are obtained in this section. In order to simplify the notation, two small-signal parameters are redefined in table 5.

$$G_{I} = G_{s} + 2g_{out}$$

$$C_{I} = C_{s} + 3C_{in}(N) + 2C_{out} = C_{s} + 3C_{gs}(N) + 3C_{gb}(N) + 2C_{gd}(PF)$$

$$+ 2C_{bd}(PF) + 2C_{gd}(NS) + 2C_{ds}(NS) + 2C_{bd}(NS)$$

Table 5. Impedance parameters for the FC integrator.

In accordance with the analysis of the small-signal equivalent model for the complete FC integrator, parameter  $C_I$ , defined in table 5, directly represents the total integration capacitance, the expression of which is the same as in the HS integrator. Therefore, the total integrator capacitance of both integrator implementations can be calculated by Eq.(26).

$$C_{I} = C_{s} + 3C_{in}(N) + 2C_{out}$$

(26)

For the FC integrator, the differential and common-mode gain can be expressed as follows:

Continuous-Time Analog Filtering: Design Strategies and Programmability in CMOS Technologies for VHF Applications

$$A_{DC} \approx \left[ \left( A_{N} - A_{P} \right) + \frac{2g_{ds}(NS) \left( g_{MP}(PF) + 2g_{ds}(P) \right)}{g_{m}(N) \left( g_{MP}(PF) + g_{ds}(PF) \right)} \right]^{-1} \approx \left[ \left( A_{N} - A_{P} \right) + \frac{2g_{ds}(NS)}{g_{m}(N)} \right]^{-1}$$

(27)

$$A_{CM} \approx -\left[\left(A_N + A_P\right) + \frac{2g_{ds}(NS)}{g_m(N)}\right]^{-1} \approx \frac{-1}{A_N + A_P}$$

(28)

In these expressions, the negative resistance obtained by the partial positive feedback compensation is shown again by means of the difference  $\delta g_m = (A_N - A_P)g_m(N)$ . Parasitic poles,  $\delta_1$  and  $\delta_2$ , are obtained by means of ratios among  $\alpha$ ,  $\beta$  and  $\gamma$ , as in the HS implementation. The final expressions are summarized in table 6. Consequently, parasitic poles  $\delta_1$  and  $\delta_2$  can be expressed as:

$$\alpha \approx \left( \left( A_N - A_P \right) g_m(N) \right) \left( g_{MP}(PF) + g_{ds}(PF) \right) + 2g_{ds}(NS) \left( g_{MP}(PF) + 2g_{ds}(P) \right) \approx 2g_{ds}(NS) \left( g_{MP}(PF) + 2g_{ds}(P) \right)$$

$$(29)$$

$$\beta \approx \left(g + g_{ds}(PF) + g_{MP}(PF)\right)C_{I} \approx \left(g_{MP}(PF) + 2g_{ds}(P)\right)C_{I}$$

(30)

$$\delta_1 = \frac{\alpha}{\beta} \approx \frac{2g_{ds}(NS)}{C_1} \tag{31}$$

$$\gamma \approx C_{I} \left( C_{ds}(PF) + C_{gd}(N) + C \right) \approx C_{I} C \approx$$

$$\approx C_{I} \left( 2C_{gd}(P) + 2C_{ds}(P) + C_{gs}(PF) + C_{bs}(PF) \right) \approx 2C_{I} C_{gd}(P)$$

(32)

$$\delta_{2} = \frac{\beta}{\gamma} \approx \frac{g_{MP}(PF) + 2g_{ds}(P)}{2C_{gd}(P) + 2C_{ds}(P) + C_{gs}(PF) + C_{bs}(PF)} \approx \frac{g_{MP}(PF) + 2g_{ds}(P)}{2C_{gd}(P)}$$

(33)

Similar results can be obtained for the common-mode frequency response:

$$\alpha_{CM} \approx \left( \left( A_N + A_P \right) g_m(N) \right) \left( g_{MP}(PF) + g_{ds}(PF) \right) + 2g_{ds}(NS) \left( g_{MP}(PF) + 2g_{ds}(P) \right) \approx \left( A_N + A_P \right) g_m(N) \left( g_{MP}(PF) + g_{ds}(PF) \right)$$

(34)

$$\beta_{CM} \approx \beta \approx \left( g_{MP}(PF) + 2g_{ds}(P) \right) C_{I}; \quad \gamma_{CM} \approx \gamma \approx 2 C_{I} C_{gd}(P)$$

(35)

$$\xi_1 = \frac{\alpha_{CM}}{\beta_{CM}} \approx \frac{(A_N + A_P)g_m(N)}{C_I}; \quad \xi_2 = \frac{\beta_{CM}}{\gamma_{CM}} \approx \delta_2 \approx \frac{g_{MP}(PF) + 2g_{ds}(P)}{2C_{gd}(P)}$$

(36)

#### 4.6 Comments and discussion

A full analysis has been developed in previous sections in order to draw some design strategies and implement a competitive and robust transconductor cell. Great similarity was found between the two topologies, as reflected in table 6.

The first conclusion regards total integration capacitance,  $C_I$ , which has the same definition in both implementations:  $C_I=C_s+3C_{in}(N)+2C_{out}$  (Eq. 26), where  $C_s$  represents the equivalent

|    | $\mathbf{S}_{0}$           | S <sub>1</sub>                                                                                        | $\delta_1$                                    | δ2                                           | ξ1                                    | <b>ξ</b> 2                                   |

|----|----------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------|---------------------------------------|----------------------------------------------|

| HS | $\frac{g_m(N)}{C_{gd}(N)}$ | $\frac{g_{\scriptscriptstyle M}(NC) + g_{\scriptscriptstyle ds}(NC)}{C_{\scriptscriptstyle ds}(NC)}$  | $\frac{2g_{ds}(NC)g_{ds}(N)}{g_{M}(NC)C_{I}}$ | $\frac{g_{M}(NC)}{C_{g^{s}}(NC)}$            | $\frac{(A_N + A_P)g_m(Q_I)}{C_I}$     | $\frac{g_M(NC)}{C_{gs}(NC)}$                 |

| FC | $\frac{g_m(N)}{C_{gd}(N)}$ | $\frac{g_{\scriptscriptstyle MP}(PF) + g_{\scriptscriptstyle ds}(PF)}{C_{\scriptscriptstyle ds}(PF)}$ | $\frac{2g_{ds}(NS)}{C_{I}}$                   | $\frac{g_{MP}(PF) + 2g_{ds}(P)}{2C_{gd}(P)}$ | $\frac{(A_{N}+A_{P})g_{m}(N)}{C_{I}}$ | $\frac{g_{MP}(PF) + 2g_{ds}(P)}{2C_{gd}(P)}$ |

Table 6. Parasitic poles and zeros for the integrator topology.

parallel capacitance between the external capacitance and the Norton capacitance of the input current source. This definition can easily be obtained by taking two different ideas into account. Considering the proposed integrator topology (Fig. 3), the expected integration capacitance will be the external capacitance in addition to the contribution of parasitic capacitors to the input node. For example, looking at the positive branch (the upper one) in this figure, there are three transconductor cell inputs ( $g_m(1+)$ ,  $g_m(2+)$  and  $g_m(-)$ ) and two outputs ( $g_m(1+)$ ,  $g_m(2-)$ ) connected to the integrator input and contributing to C<sub>I</sub>. Each unit cell forming the complete integrator has been studied in detail and their corresponding models obtained (tables 1 and 2). From this analysis,  $C_{in}(N)$  and  $C_{out}$  are the equivalent input and output capacitance respectively for each unit cell; which, combined with the previous consideration, leads directly to the definition obtained for C<sub>I</sub>.

The low-impedance internal node strategy combined with the use of a negative resistance to enhance the differential dc-gain of the system, while increasing the differential input resistance and reducing the phase error, suggested the use of cascode topologies to us, also taking advantage of their inherent transmission zero reduction. The differential dc-gain obtained in both structures, shown in Eq.(15) and (27) respectively, reflects the existence of this positive feedback compensation, making the ideal infinite dc-gain of the integrator possible. Regarding the common-mode behaviour of the circuit, both implementations are described with the same expression complying with the stability requirement  $|A_{CM}| < 1$ :  $A_{CM} \sim -1/(A_N + A_P) \sim -1/2$ .

Variations on the negative resistance value are equivalent to considering a mismatching between  $M_N(1)$  and  $M_N(2)$ , which generates a difference between the drain currents of these transistors. Furthermore, the same effect can also be achieved by modifying bias currents  $I_{BIAS}$  in these two branches of the circuit. In consequence, the tuning of the value of this negative resistance allows for correction in process deviations and mismatching between the transistors  $M_N$  that process the signal.

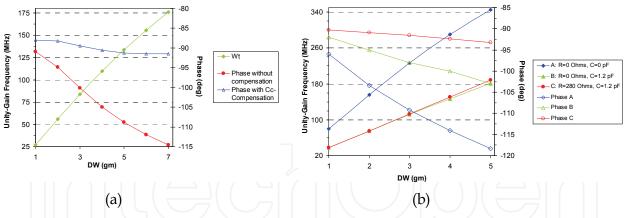

Finally, cascode stages introduce two dominant parasitic poles and a dominant zero as shown in Eq.(8), which stem from parasitic capacitances mainly associated with the source nodes of cascode transistors. In consequence, an excess phase shift  $\Delta \varphi(\omega_t)$  takes place at unity-gain frequency (Eq. 37). Theoretically, by using the minimum length for cascode transistors and minimizing source and drain diffusion areas, the parasitic poles and zero can be located further away from the unity-gain frequency. This consideration will also minimize distributed-channel effects, which cannot be ignored at high frequencies (Tsividis, 1999). However, the minimum channel length is conditioned by the required transistor matching (Pelgrom et al., 1989).

$$\Delta\varphi(\omega_t) \approx \frac{\pi}{2} - \tan^{-1}\left(\frac{\omega_t}{\delta_1}\right) - \tan^{-1}\left(\frac{\omega_t}{\delta_2}\right) - \tan^{-1}\left(\frac{\omega_t}{\delta_2}\right)$$

(37)

These general considerations reflect the benefits of the topology and its frequency limits. Nevertheless, both integrators have been implemented, and the real values drawn from these designs allow a better study of the frequencies related to parasitic effects to be carried out and a comparison to be made between both topologies.

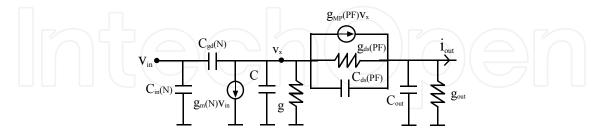

**Second-order frequency dependence.** The previous study for the frequency behaviour of the integrator was summarized in Eq.(8), and, taking into account the definition for the integrator quality factor (Eq. 4), the general relation in both approximations can be reported as:

$$\frac{1}{Q_{\text{int}}} = \frac{\delta g_m + g_o}{g_m(N)} - \frac{C_{gd}(N)}{C_I} - \frac{C_p(C)}{C_I} \frac{g_m(N)}{g_m(C)}$$

(38)

where  $g_0$  is the sum of output conductances at the input node,  $C_I$  is the total integration capacitance,  $g_m(C)$  is the transconductance of the cascode element ( $g_m(NC)$  and  $g_m(PF)$  for the HS and FC approach respectively), and  $C_p(C)$  the parasitic capacitance at the low-impedance node associated to the cascode structures (node X in Figs. 8 and 9).

The second-order frequency dependence can be analysed when considering the  $M_N$  transistor mismatch  $A_N$ - $A_P$ = $\delta g_m/g_m$  and including the frequency dependence for their transconductance  $g_m(s)$  (Eq. 39) in the transfer function (Smith et al., 1996; Zele et al., 1996). In this way, the non-quasistatic model for the MOS transistor, required for operation at very high frequencies, is included.

$$g_m(s) = \frac{g_m(N)}{1+s\tau} \quad ; \quad \tau = \frac{2}{5} \frac{C_{gs}(N)}{g_m(N)}$$

(39)

By simplifying the result obtained to draw some conclusions, the frequency behaviour of the integrator is described (Eq. 40) reflecting the effect of these additional second-order dependencies.

$$\frac{1}{Q_{\rm int}} = \left(\frac{g_o'}{g_m(N)}\right)^2 + \frac{\delta g_m}{g_m(N)} - \frac{3C_{gs}(N)}{7C_l} - \frac{C_{gd}(N)}{C_l} - \frac{C_p(C)}{C_l} \frac{g_m(N)}{g_m(C)}$$

(40)

From this study, a set of parasitic poles and zeros appear at frequencies higher than 15 GHz in the proposed designs, the effect of which is considered negligible in a first-order approximation.

#### 5. Noise

In general, the range of signals that can be accurately driven by electronic devices is limited. For low-signals, electrical noise restricts the minimum amplitude that can be processed. Noise is considered as all the unwanted electrical signals generated within the device or externally and coupled to the output of the system. These signals appear in the system whether input signals are applied or not. Noise signals interfere with the incoming signal and make it impossible to detect with sufficient quality the signals presenting an amplitude comparable to the noise level. Moreover, signals below this level are almost impossible to detect. So, noise in the system represents the lowest level for the incoming signal (SilvaMartínez et al., 2003). The origins of noise can be classified as intrinsic and extrinsic transistor noise sources, following a similar notation to that used for the parasitic elements of the MOS transistor. There are two dominant intrinsic noise sources in CMOS transistors: channel thermal noise and 1/f or flicker noise. Extrinsic noise is mainly due to the signals produced by the surrounding circuitry and coupled to the device or to the system. The only noise considered in this work is noise generated by the transistor.

The noise of a  $G_m$ -C filter is caused by the noise output currents of the transconductors and the mean square noise currents are generally proportional to the corresponding transconductance. Considering the model of a noisy transconductor, the output mean square noise current over a certain frequency interval df is given by:

$$\overline{i_n^2} = 4 \ k \ T \ NF \ g_m \ df \tag{41}$$

where k is the Boltzmann constant, T the absolute temperature and NF a noise factor determined by the electronic design of the transconductor. NF=1 corresponds to a transconductor output noise current equal to the thermal noise current of a resistor of value  $R=1/g_m$ .

Fig. 10. Transconductor noise model.

To investigate the latter effect in the frequency design of VHF filters, calculating the noise factor and its frequency dependence becomes necessary in both HS and FC transconductor implementations, because filter noise behaviour not only depend on the filter parameters but also on the transconductor noise behaviour. Therefore, the NF-factor appears as a useful quantity to translate the transconductor noise properties to the filter noise properties and, likewise, the properties of each unit cell to the complete transconductor implementation. In consequence, transconductor output noise is determined by the noise properties of the unit cell and by the properties of the transconductor topology.

The transconductor topology analysed is the balanced structure shown in Fig. 3. First, the noise behaviour of each single unit cell is calculated ( $H_{HS}(s)$  and  $H_{FC}(s)$ ) and then the noise factor of the complete transconductor in both implementations,  $F_{HS}(s)$  and  $F_{FC}(s)$ .

#### 5.1 Noise model for the unit cell

For high and very-high frequencies, the 1/f or flicker noise can be neglected. Assuming only thermal noise, the drain-current noise of a single transistor can be written as:

$$i_n^2 = 4 \ k \ T \ c \ g_m \ df \tag{42}$$

where k is the Boltzmann constant, T the absolute temperature,  $g_m$  the small-signal transconductance of the transistor, and df the frequency interval over which the noise is

measured. The constant c value is 2.5 for a short-channel transistor working in the saturation region<sup>2</sup> (Tsividis, 1999). The noise output current of the HS unit cell (Fig. 6(a)) is:

$$i_n^2(HS) = 4 \ k \ T \ H_{HS} \ df \tag{43}$$

where:

$$H_{HS} = (1 - \sqrt{\alpha})^{2} c(PC) g_{m}(PC) + \alpha c(P) g_{m}(P) + (1 - \sqrt{\beta})^{2} c(NC) g_{m}(NC) + \beta c(N) g_{m}(N)$$

(44)

$$\sqrt{\alpha} = \frac{g_m(PC) + g_{ds}(PC)}{g_m(PC) + g_{ds}(PC) + g_{ds}(P)}; \quad \sqrt{\beta} = \frac{g_m(NC) + g_{ds}(NC)}{g_m(NC) + g_{ds}(NC) + g_{ds}(N)}$$

(45)

For the FC approach, the noise output current of the unit cell (Fig. 6(b)) can be written as:

$$i_n^2(FC) = 4 k T H_{FC} df$$

(46)

where:

$$H_{FC} = (1 - \sqrt{\alpha})^2 c(PF) g_m(PF) + 2\alpha c(P) g_m(P) + c(NS) g_m(NS) + \alpha c(N) g_m(N)$$

(47)

$$\sqrt{\alpha} = \frac{g_m(PF) + g_{ds}(PF)}{g_m(PF) + g_{ds}(PF) + 2g_{ds}(P) + 2g_{ds}(N)}$$

(48)

As a result, certain conclusions can be drawn from this study. The main noise sources in both topologies are transistors  $M_N$  processing the signal and bias current sources, to which the main contribution applies. The FC unit cell presents a noise factor 2.5 times higher than the HS topology, which is due to the additional current sources required in this topology.

#### 5.2 Noise model for the complete transconductor cell

The noise factor of the complete transconductor can be calculated using the model obtained for the unit cells (Nauta, 1993), or by calculating the complete noise model of the proposed transconductance cell from the start. We use this second option to obtain a more accurate result, modelling the output noise currents of the transistors with noise current sources in parallel with the outputs as in the previous section. The two noise output currents of the differential transconductor are  $\overline{i_{n,plus}^2}$  and  $\overline{i_{n,minus}^2}$ . Following a similar process as in the noise study on the unit cells, the noise output current of the complete HS transconductor can be written as:

$$\overline{i_{n,plus}^{2}(HS)} = \overline{i_{n,\min}^{2}(HS)} = 4 \ k \ T \ F_{HS} \ df$$

(49)

<sup>&</sup>lt;sup>2</sup> The constant c, which models transistor noise behaviour, depends on both its operation region and its dimensions. A theoretical derivation for the transistor working in the linear region leads to 1 < c < 2; however, c = 2/3 for a long-channel device and c = 2.5 for a short-channel device are obtained in the saturation region (Tsividis, 1999).

where:

$$F_{HS} = c(PC) F_{HS}(PC) + c(P) F_{HS}(P) + c(NC) F_{HS}(NC) + c(N) F_{HS}(N)$$

(50)

$$F_{HS}(PC) = x_1^2 \left[ (A_N + A_P - 2)g_m(N) \cdot (g_m(NC) + g_{ds}(NC)) \cdot x_2 + 2g_{ds}(P)g_{ds}(PC)x_3 + 2g_{ds}(N)g_{ds}(NC)x_2 \right]^2 g_m(PC)$$

(51)

$$F_{HS}(P) = \frac{F_{HS}(PC)}{g_m(PC)} \left(\frac{g_m(PC) + g_{ds}(PC)}{g_{ds}(P)}\right)^2 g_m(P)$$

(52)

$$F_{HS}(NC) = \left(g_{ds}(N) + \frac{x_2 g_m(N)(g_m(NC) + g_{ds}(NC))(g_m(NC) + g_{ds}(NC) - g_{ds}(N))}{\alpha}\right)^2 x_2^2 g_m(NC)$$

(53)

$$F_{HS}(N) = \left(1 + \frac{x_2^2 (g_m(NC) + g_{ds}(NC))^2 (A_N + A_P) g_m^2(N)}{\alpha^2}\right) x_2^2 (g_m(NC) + g_{ds}(NC))^2 g_m(N) \quad (54)$$

$$x_{1} = \frac{g_{ds}(P) x_{3}}{\alpha}; \quad x_{2} = \frac{1}{g_{ds}(N) + g_{m}(NC) + g_{ds}(NC)}; \quad x_{3} = \frac{1}{g_{ds}(P) + g_{m}(PC) + g_{ds}(PC)}$$

(55)

$$\alpha = x_2(g_m(NC) + g_{ds}(NC))((A_N + A_P)g_m(N) - 2g_{ds}(NC)) + 2g_{ds}(NC) + 2g_{ds}(PC)x_3$$

(56)

The noise output current of the complete transconductor implemented with FC unit cells can be written as:

$$\overline{i_{n,plus}^2(FC)} = \overline{i_{n,minus}^2(FC)} = 4 \ k \ T \ F_{FC} \ df$$

(57)

where:

$$F_{FC} = c(PF) F_{FC}(PF) + c(P) F_{FC}(P) + c(NS) F_{FC}(NS) + c(N) F_{FC}(N)$$

(58)

$$F_{FC}(PF) = \left(1 - \alpha - \frac{2\alpha(1 - \alpha)}{\chi}\right)^2 g_m(PF); \quad F_{FC}(P) = 2\alpha^2 \left(1 - \frac{2\alpha}{\chi}\right)^2 g_m(P) \tag{59}$$

$$F_{FC}(NS) = \left(1 - \frac{2\alpha}{\chi}\right)^2 g_m(NS); \quad F_{FC}(N) = \left(1 + \frac{\alpha^2}{\chi^2}(A_N + A_P)\right) \alpha^2 g_m(N)$$

(60)

$$\alpha = \frac{g_m(PF) + g_{ds}(PF)}{g_m(PF) + g_{ds}(PF) + 2g_{ds}(P) + g_{ds}(N)}; \quad \chi = 2(1-\alpha)\frac{g_{ds}(PF)}{g_m(N)} + 2\frac{g_{ds}(NS)}{g_m(N)} + \alpha(A_N + A_P)$$

(61)

From this study, the major noise contributions are those due to NMOS transistors in the signal path,  $M_N$ , representing almost the total contribution for the FC implementation. The contribution of the bias current sources, which was relevant in the noise analysis of the unit cells, becomes negligible when implementing the complete fully-balanced current-mode

topology. A significant benefit of this structure is that the previous noise-related difference existing between the two unit cells disappears in the complete transconductor, with the same value being obtained mostly for  $F_{HS}$  and  $F_{FC}$ . Another important conclusion is that the output noise current is independent of the value of the negative resistance  $\delta g_m$ , inherent characteristic of the topology.

Hence, the noise is dominated by the  $M_N$  transistors involved in the V to I conversion, with similar noise contributions being achieved for both transconductor implementations. The post-layout simulation results corroborate this idea, with a total input-referred noise of 11  $nA_{rms}$  being obtained for the HS topology and 8  $nA_{rms}$  for the FC approach. This is a very important design conclusion and requires be further considered in the design of high-performance filters.

#### 6. Distortion

The ability to handle large signals with minimum distortion is an important consideration in most linear applications. In this section, the large signal characteristics of the current mode integrator for differential inputs are analysed using first-order square-law MOSFET models, which can provide a sufficiently accurate description of the large signal behaviour for design purposes. The proposed transconductor topology (Fig. 3) has been implemented by using two different cascode architectures: the HS and the FC approach. Transconductor V-I conversion is obtained in the output stage  $g_{m}$ , and a negative resistance, shown in grey in the same figure, is connected at the input in order to improve the topology characteristics.

A theoretical distortion analysis including all the non-linearities would be too complex and provides no practical benefit. Consequently, a separate study of each factor affecting linearity has been developed to obtain simple and efficient design strategies. There are two main contributions to transconductor distortion, the first one will be non-linearities in V to I conversion, and the second non-linearities in the negative resistance. Each effect is analysed separately. The effects of capacitor non-linearities are not taken into account here.

#### 6.1 Non-linearities in V-I conversion

For this study, only the output stage will be considered, i.e., the transconductor cell without the negative resistance. This differential structure will present good linearity in V-I conversion if both paths are perfectly matched. Using a simple model of the MOS transistor, the drain currents of the N- and P-channel MOS transistor in strong inversion can be written as:

$$I_{dn} = \beta_n \left( V_{gsn} - V_{tn} \right)^2; \quad I_{dp} = \beta_p \left( V_{gsp} - V_{tp} \right)^2 \quad with \quad \beta_n = \frac{\mu_n C'_{ox} W_n}{2L_n}; \quad \beta_p = \frac{\mu_p C'_{ox} W_p}{2L_p} \quad (62)$$

Considering  $V_{IN}^+=V_C+v_{in}/2$ ,  $V_{IN}^-=V_C-v_{in}/2$  and  $v_{in}$  the differential input voltage of the transconductor cell, the differential output current can be written as:

$$I_{out} = i_{out}^{+} - i_{out}^{-} = 2\sqrt{I_{BIAS}\beta_n(N)} v_{in}$$

(63)

where  $I_{BIAS}$  is the bias current per branch and  $\beta_n(N)$  the factor associated to the  $M_N$  transistor in both implementations. The same result has been obtained with the two possible transconductor structures, the HS and the FC topologies, leading to the same distortion

analysis in both situations. This equation is valid as long as the transistors operate in strong inversion and saturation, and show that the differential voltage to current conversion of the transconductor is perfectly linear, making use of the square-law and matching properties of the MOS transistors. However, mobility reduction will cause deviations from the transistor square-law behaviour, generating distortion. The mobility of the NMOS and PMOS transistors can be expressed in the first-order approximation as:

$$\mu_{n} = \frac{\mu_{on}}{1 + \theta_{n}(V_{gsn} - V_{tn})}; \qquad \mu_{p} = \frac{\mu_{op}}{1 - \theta_{p}(V_{gsp} - V_{tp})}$$

(64)

Considering again the output stage of the complete cell (Fig. 3), driven balanced around the common-mode voltage level  $V_C$  as previously explained, the differential output current can be calculated as:

$$I_{out} = i_{out}^{+} - i_{out}^{-}$$

(65)

Using the previous expressions for mobility reduction and assuming equal transistors operating in saturation, the differential output current can be expanded into Taylor series:

$$I_{out} = \frac{k_{on}V_{on}\left(1 + \frac{1}{2}\theta_{n}V_{on}\right)}{\left(1 + \theta_{n}V_{on}\right)^{2}}v_{in} - \frac{\theta_{n}k_{on}}{\left(1 + \theta_{n}V_{on}\right)^{4}}\frac{1}{8}v_{in}^{3} - \frac{\theta_{n}^{3}k_{on}}{\left(1 + \theta_{n}V_{on}\right)^{6}}\frac{1}{32}v_{in}^{5} + \cdots;$$

(66)

where:  $V_{on} = V_C - V_{tn} = \sqrt{\frac{I_{BLAS}}{\beta}} > 0$  and  $k_{on} = \frac{\mu_{on}C'_{ox}W_n}{L_n}$ .

The fifth and higher order distortion terms can be neglected, giving the following as a result for distortion calculation:

$$I_{out} = C_1 v_{in} + C_3 v_{in}^{3}; \quad with \quad C_1 = \frac{k_{on} V_{on} \left(1 + \frac{1}{2} \theta_n V_{on}\right)}{\left(1 + \theta_n V_{on}\right)^2}; \quad C_3 = \frac{-\theta_n k_{on}}{\left(1 + \theta_n V_{on}\right)^4} \frac{1}{8}$$

(67)

$$HD_{3} = \frac{C_{3}}{C_{1}} = \frac{-\theta_{n}}{8V_{on}\left(1 + \theta_{n}V_{on}\right)^{2}\left(1 + \frac{1}{2}\theta_{n}V_{on}\right)} \approx \frac{-\theta_{n}}{8V_{on}}$$

(68)

The expression for HD<sub>3</sub> can be simplified as  $\theta_n V_{on} <<1$ . This expression is the same for both implementations of the transconductor cell. The main conclusion from Eq.(68) is that increasing  $V_{on}$ , i.e., the common-mode voltage  $V_C$  or the bias current I<sub>BIAS</sub>, lowers the distortion in the V-I transfer.

#### 6.2 Non-linearities in the negative resistance

Non-linearities in V-I conversion and non-linearities in the negative resistance will introduce non-linear effects in the input resistance of the differential transconductor (Nauta, 1993). The effect of these non-linearities is a signal dependent integrator quality factor, i.e., a phase error; and can cause distortion in filters, especially high-Q filters. As long as the value

of the input impedance is high enough and an enhancement of the dc-gain is obtained, the effect of non-linearities will be slight. Considering the equations for a single transistor reported in Eq.(62) and analysing the structure shown in Fig. 3, the differential input voltage can be written as:

$$v_{in} = \sqrt{\frac{I_{BIAS}}{\beta_n}} \left( \sqrt{1 + \frac{i}{I_{BIAS}}} - \sqrt{1 - \frac{i}{I_{BIAS}}} \right)$$

(69)

where (2i) is the differential input current, i.e.,  $I_i^+ = i$  and  $I_i^- = -i$ , considering the description shown in Fig. 3. The same relation has been obtained in both implementations, leading again to the same distortion analysis. This expression can be expanded into Taylor series, where  $A=i/I_{BIAS}$ ,  $\alpha_1=1$  and  $\alpha_3=1/8$ .

$$v_{in} = \alpha_1 A Cos(wt) + \alpha_2 A^2 Cos^2(wt) + \alpha_3 A^3 Cos^3(wt); HD_2 = \frac{\alpha_2 A}{2\alpha_1}; HD_3 = \frac{\alpha_3 A^2}{4\alpha_1} \Rightarrow HD_3 = \frac{1}{32} \left(\frac{i}{I_{BIAS}}\right)^2$$

(70)

The large signal output characteristics of the current mode integrator present a similar form to that of the standard MOS differential pair. On the other hand, the distortion generated in positive feedback compensation through negative resistance is only dependent on the ratio between the input current and the bias current I<sub>BIAS</sub>. This analysis is the same for both implementations of the transconductor topology.

#### 6.3 Matching and harmonic-distortion

The process that causes time-independent random variations in physical parameters of identically designed devices is called mismatch, and is a limiting factor in general-purpose analog signal processing. The impact of MOS transistors mismatching becomes very important because the dimensions of the devices are reduced and the available signal swings decrease. To obtain a better circuit design, the physical origin of this effect has been discussed in several studies (Pelgrom et al., 1989), not only for its random but also for its systematic contribution (Gregor, 1992), and also possible measurements for its characterization (Felt et al., 1994).

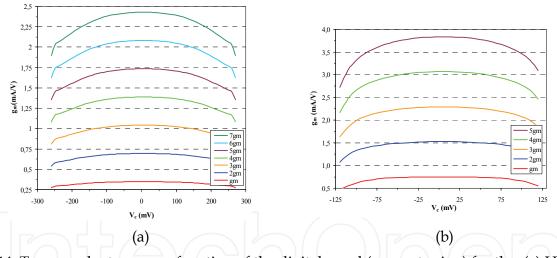

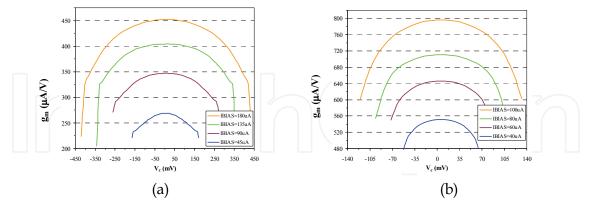

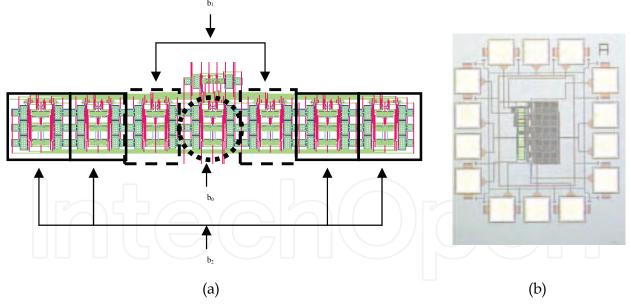

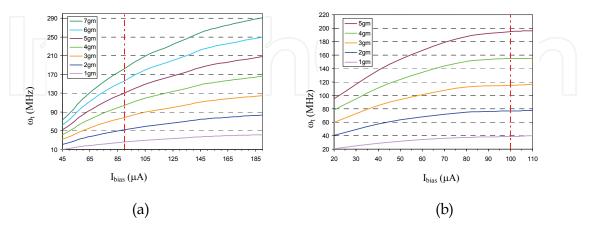

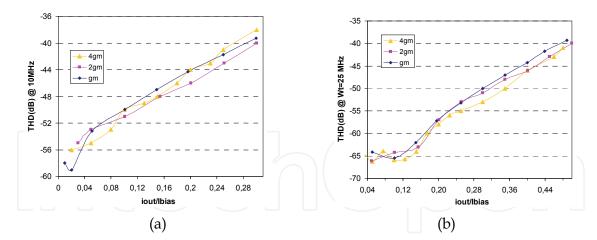

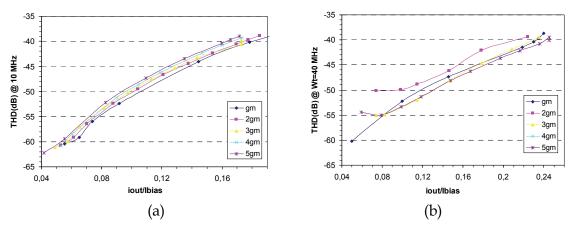

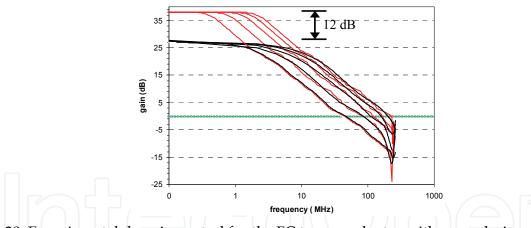

Thanks to the use of a fully-balanced pseudo-differential topology, with this inherent positive feedback compensation providing the system with an enhancement of the differential dc-gain, distortion resulting from mismatch is small. As mentioned above, the existing negative resistance enables small variations in dimensions of  $M_N$  transistors and bias current sources  $I_{BLAS}$  to be controlled. In order to obtain a good matching, the minimum channel length related to the considered CMOS technology must be avoided. However, high frequency operation requires short channels, relying on the negative resistance to obtain the adequate matching between transistors in the signal path. In addition, channel length modulation is not considered, as it only has a substantial effect on integrator response linearity at low frequencies, where distortion is suppressed by feedback (Smith et al., 1996; Zele et al., 1996). In consequence, transistors are assumed to be well matched, which will be achieved by means of a lower mismatching sensitive design while obtaining the final layout.