## We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

6,900

186,000

200M

Download

154

Countries delivered to

Our authors are among the

**TOP 1%**

most cited scientists

12.2%

Contributors from top 500 universities

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected.

For more information visit www.intechopen.com

# Simulation of Power Converters Using Matlab-Simulink

Christophe Batard, Frédéric Poitiers, Christophe Millet and Nicolas Ginot

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/46419

#### 1. Introduction

A static converter is an electrical circuit which can control the transfer of energy between a generator and a receiver. The efficiency of a converter should be excellent. The components constituting a converter are:

- Capacitors, inductors and transformers with minimum losses,

- Power semiconductors operating as switches.

The design of power converter consumes time with a significant cost. Performance is generally determined after testing converters at nominal operating points. Thus, simulation can substantially reduce development cost.

The development of specific software dedicated to simulation of power electronic systems (PSIM, SABER, PSCAD, "SimPowerSystems" toolbox of Simulink...) allows simulating fast and accurately the converter behavior. Unfortunately, the designers of converters don't always have such available software. In many cases, they have to simulate power electronics devices for occasional need. So they don't want to buy the SimPowerSystems toolbox in addition to Matlab and Simulink. The purpose of this chapter is to present the ability to simulate power converters using only Simulink. Simulink is a graphical extension to MATLAB for representing mathematical functions and systems in the form of block diagram, and simulate the operation of these systems.

Traditionally two approaches are used to simulate power electronic systems:

The first, so called fixed topology, where semiconductors are impedances with low or high values based on their on-state or off-state. Equations system does not depend on the state of the semiconductor. Despite its simplicity, this approach raises problems of compromise between accuracy of the results and stability of numerical integration methods.

- The second, so called variable topology, assimilates the switches to open-circuits or short-circuits. The system equations then depend on the state of the semiconductor. There are no accuracy problems but writing the equations of different configurations can be laborious as well as obtain switching conditions of the semiconductor.

In this chapter, we propose a method for simulating static converters with Simulink based on the variable topology approach where switching conditions of semiconductor are realized by switching functions.

#### 2. Linear load modeling in Simulink

This paragraph deals with the modelling of linear elements commonly encountered in the electrical energy conversion. Elementary linear dipoles are described by a system of linear differential equations. There are several different ways to describe linear differential equations. The state-space representation (SSR) is the most easy to use with Matlab. The SSR is given by equations (1) and (2).

$$\dot{X} = A X + B U \tag{1}$$

$$Y = C X \tag{2}$$

where X is an n by 1 vector representing the state (commonly current through an inductance or voltage across the capacitance), U is a scalar representing the input (voltage or current), and Y is a scalar representing the output. The matrices A (n by n), B (n by 1), and C (1 by n) determine the relationships between the state and input and output variables.

The commonly elementary dipoles encountered in power electronics are:

- RL series dipole

- RLC series dipole

- RC parallel dipole

- L in series with RC parallel dipole

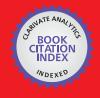

#### 2.1. RL series dipole

The variation of the current through the dipole is governed by equation (3).

$$v(t) = R i(t) + L di/dt \implies i(t) = \frac{1}{L} \int (v(t) - R i(t)) dt$$

(3)

The RL series dipole is modelled by the scheme illustrated in figure 1.

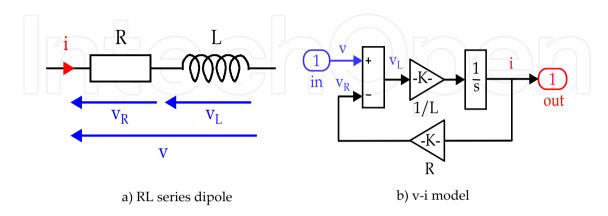

#### 2.2. RLC series dipole

The variation of the current through the dipole is governed by equation (4) and the variation of the voltage across the capacity is governed by equation (5).

$$\mathbf{v}(\mathbf{t}) = R \, i(t) + v_{\mathcal{C}}(t) + L \, di / dt \quad \Rightarrow \quad i(t) = \frac{1}{L} \int \left( v(t) - Ri(t) - v_{\mathcal{C}}(t) \right) dt \tag{4}$$

$$i(t) = C dv_C / dt \implies v_C(t) = \frac{1}{C} \int i dt$$

(5)

Figure 1. Model of a RL series dipole

The RLC series dipole is modelled by the scheme illustrated in figure 2.

Figure 2. Model of a RLC series dipole

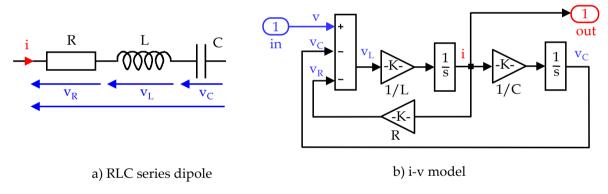

#### 2.3. RC parallel dipole

The variation of the voltage across the dipole is governed by equation (6).

$$i(t) = C \frac{dv}{dt} + v(t) / R \implies v(t) = \frac{1}{C} \int (i(t) - v(t)/R) dt$$

(6)

The RC parallel dipole is modelled by the scheme illustrated in figure 3.

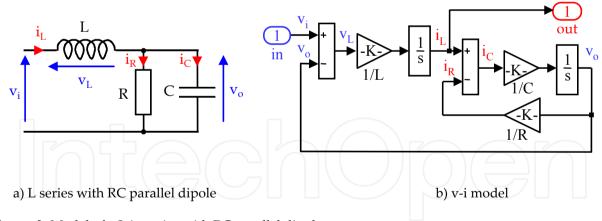

#### 2.4. L in series with RC parallel dipole

In a L in series with RC parallel dipole, the variation of the current through the inductance is governed by equation (7) and the variation of the voltage across the capacity is governed by equation (8).

$$v_i(t) = v_o(t) + L \frac{di_L}{dt} \implies i_L(t) = \frac{1}{L} \int (v_i(t) - v_o(t)) dt$$

(7)

$$i_L(t) = i_R(t) + C \frac{dv_o}{dt} \implies v_o(t) = \frac{1}{C} \int \left( i_L(t) - i_R(t) \right) dt \tag{8}$$

$$i_R(t) = v_o(t)/R \tag{9}$$

The L in series with RC parallel dipole is modelled by the scheme illustrated in figure 4.

Figure 3. Model of a RC parallel dipole

Figure 4. Model of a L in series with RC parallel dipole

#### 3. DC-DC converter model in Simulink

This part will be dedicated to the DC-DC converter modelling with Simulink. The input generator is a DC voltage source and the output generator is also a DC voltage source. The output voltage is always smoothed by a capacitor. Only the non-isolated DC-DC converters are studied in this paragraph. The switches are assumed ideal, as well as passive elements (L, C)

#### 3.1. Buck converter

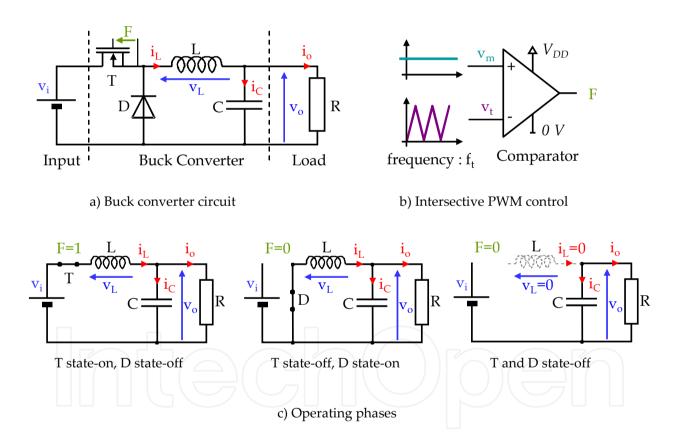

#### 3.1.1. Operating phases

The buck converter circuit is illustrated in figure 5a. The most common strategy for controlling the power transmitted to the load is the intersective Pulse Width Modulation (PWM). A control voltage v<sub>m</sub> is compared to a triangular voltage v<sub>t</sub>. The triangular voltage v<sub>t</sub> determines the switching frequency ft. The switch T is controlled according to the difference v<sub>m</sub> – v<sub>t</sub> (figure 5b). Three operating phases are counted (figure 5c):

- T state-on and D state-off

- T state-off and D state-on

- T and D state-off

Figure 5. Buck converter

The variation of the current through the capacitor C is governed by equation (10). The variation of the voltage across the capacity is governed by equation (11). Equation (12) describes the variation of the voltage across the inductance which depends on the operating phase. F is a logical variable equal to one if v<sub>m</sub> is greater than or equal to v<sub>t</sub>, F equal to zero if vm is less than vt. Sign(iL) is also a logical variable which is equal to one if iL is positive, sign (iL) equal to zero if iL is zero.

$$i_{C}(t) = i_{L}(t) - i_{o}(t) = C \frac{dv_{o}}{dt}$$

(10)

$$v_o(t) = \frac{1}{C} \int i_C(t) \, dt = \frac{1}{C} \int \left( i_L(t) - i_o(t) \right) dt \tag{11}$$

$$v_{L}(t) = (v_{i}(t) - v_{o}(t)) * F - v_{o}(t) * \overline{F} * sign(i_{L})$$

(12)

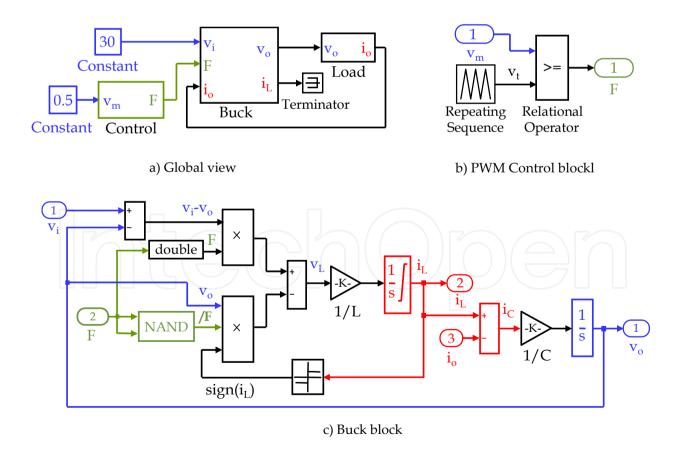

#### 3.1.2. Open-loop buck converter

Simulink model of the open-loop buck converter is shown in figure 6a. The Buck block is illustrated in figure 6c. Equation (12) is modelled by blocks addition, multiplication and logic. The structure of the converter requires a current in necessarily positive or zero. Also, the inductance current is modelled by an integrator block that limits the minimum value of in to zero.

The PWM control block is illustrated in figure 6b.

In the case of a resistive load, the load block is constituted by a gain block (value 1/R).

Figure 6. Buck converter described in Simulink

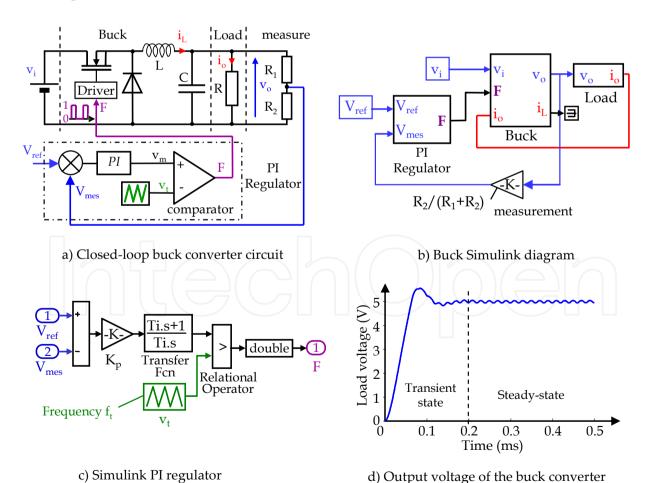

#### 3.1.3. Closed-loop buck converter

A closed-loop buck converter circuit is illustrated in figure 7a. The measurement of the output voltage is realized by 2 resistances R1 and R2. The regulation is achieved by a PID controller. Simulink model of the closed loop converter is shown in figure 7b. Simulink PID control block is illustrated in figure 7c.

The parameters used for the closed-loop simulation are:

$V_i = 12 V$  $L = 300 \mu H$  $C = 5 \mu F$  $R = 3 \Omega$  $f_t = 50 \text{ kHz}$  $R_1 = 10 \text{ k}\Omega$  $R_2 = 10 \text{ k}\Omega$ Output voltage measurement: PID block:  $K_p = 10$  $T_i = 0.2 \text{ ms}$

The voltage reference was fixed to 2.5 V. The simulation of the closed-loop buck converter is illustrated in figure 7d. The list of configuration parameters used for is:

Start time: 0 Stop time: 0.5 e-3 Type: Variable-step Solver: ode15s (stiff/NDF) Max step size: 1e-6 Relative tolerance: 1e-3 Min step size: auto absolute tolerance: auto

**Figure 7.** Modeling a closed loop DC / DC converter

In steady-state,  $V_{ref} = V_{mes} = 2.5 \text{ V}$ . From figure 7a, we deduce the theoretical value of  $V_0$ :

$$V_o|_{steady-state} = \frac{R_1 + R_2}{R_2} V_{ref} = 5 V$$

(13)

Simulation is in good agreement with theoretical value. From figure 7d, we deduce that the transient state last roughly 0.2 ms.

#### 3.2. Boost converter

#### 3.2.1. Operating phases

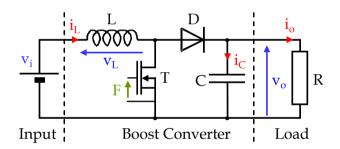

The boost converter circuit is illustrated in figure 8a. The principle of the switch control is described in figure 5b Three operating phases are counted (figure 8c):

- T state-on and D state-off

- T state-off and D state-on

- T and D state-off

The variation of the voltage across the inductance L (equation 14) and the current through the capacity (equation 15) depend on the operating phase.

$$v_L(t) = v_i(t) * F + (v_i(t) - v_o(t)) * \overline{F} * sign(i_L)$$

$$\tag{14}$$

$$i_C(t) = -i_o(t) * F + i_L(t) * \overline{F} * sign(i_L) = C \frac{dv_o}{dt}$$

(15)

$$v_o = \frac{1}{C} \int i_C(t) dt = \frac{1}{C} \int \left( -i_o(t) \cdot F + i_L \cdot \overline{F} \cdot sign(i_L) \right) dt$$

(16)

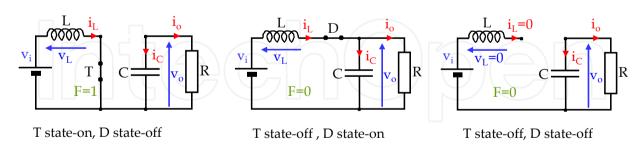

#### 3.2.2. Open-loop operation

Simulink model of a open-loop boost converter is shown in figure 9a. The Boost block is illustrated in figure 9b. Equation (14), (15) and (16) are modeled by addition blocks, multiplication blocks and logic blocks. The structure of the converter requires a current in necessarily positive or zero. Also, the inductance current is modeled by an integrator block that limits the minimum value of it to zero.

The PWM control block is illustrated in figure 6b.

In the case of a resistive load, the load block is constituted by a gain block (value 1/R).

Simulation example:

The parameters used for of an open-loop simulation are:

$$V_i$$

= 12 V  $L$  = 200 μH  $C$  = 50 μF  $R$  = 5  $\Omega$   $f_t$  = 50 kHz Control blok:  $V_{t \text{ max}}$  = 1 V  $V_{t \text{ min}}$  = -1 V  $V_m$  = 0

The simulation of the open-loop boost converter is illustrated in figure 9c. The list of configuration parameters used is:

Start time: 0 Stop time: 7 e-3

Type: Variable-step Solver: ode15s (stiff/NDF) Max step size: 1e-6 Relative tolerance: 1e-3 Min step size : auto absolute tolerance: auto

Knowing that  $v_t$  varies from -1 V to +1 V and  $v_m = 0$ , we deduce that the duty cycle  $\alpha$  is equal to 0.5. In steady-state, we deduce theoretical value of V<sub>o</sub>:

$$V_o\big|_{steady-state} = \frac{V_i}{\alpha} = 24 \ V \tag{17}$$

Simulation is in good agreement with theoretical value. From figure 9c, we deduce that the transient state last roughly 2.5 ms.

#### a) Boost converter circuit

b) Operating phases

Figure 8. Boost converter

Figure 9. Boost converter described in Simulink

#### 4. DC-AC converter model in Simulink

An inverter is a DC - AC power converter. This converter obtains AC voltage from DC voltage. The applications are numerous: power backup for the computer systems, variable speed drive motor, induction heating... In most cases, the dead times introduced into the control of the switches do not change the waveform of the inverter.

This paragraph is dedicated to the simulation of a three-phase inverter without taking into account the dead times introduced into the control of the switches.

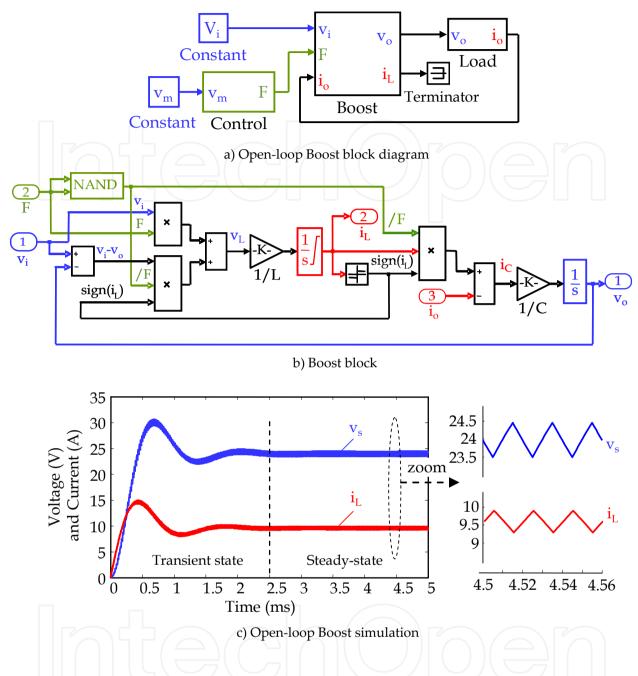

#### 4.1. Electrical circuit

A variable speed drive for AC motor is shown in figure 10. It consists on a continuous voltage source and a three-phase inverter feeding an AC motor.

In order to simplify the modelling, the electrical equivalent circuit of the AC motor is described by an inductance LM in series with a resistance RM. The motor runs with delta connection of the stator.

Figure 10. Electrical circuit

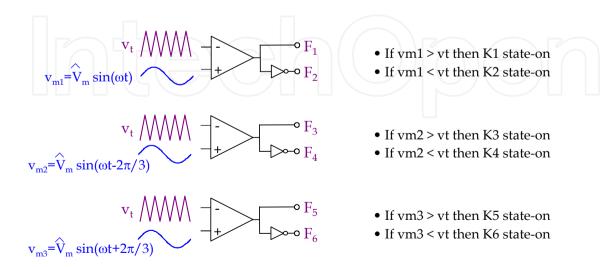

There are many strategies for controlling the switches. The most common control strategy is the intersective PWM. Its principle is reminded in figure 11. The switch control signals are generated by comparing three sinusoidal voltages (modulating) which are phase-shifted through  $2\pi/3$  [rad] with a same triangular voltage waveform (carrier).

Figure 11. Three phase PWM control

Knowing the conduction intervals of the switches, it is then possible to determine the waveform of different voltages and currents.

The line to neutral voltage  $v_{10}$ ,  $v_{20}$  et  $v_{30}$  are dependent on the state of the switches. Examples:

$K_1$  state-on and  $K_2$  state-off:  $v_{10} = + V_{DC}$   $K_1$  state-off and  $K_2$  state-on:  $v_{10} = 0$   $K_3$  state-on and  $K_4$  state-off:  $v_{20} = + V_{DC}$   $K_5$  state-off and  $K_4$  state-on:  $v_{20} = 0$   $K_5$  state-off and  $K_6$  state-on:  $v_{30} = 0$

The phase-phase voltage can be deduce from the line to neutral voltage:

$$u_{12} = v_{10} - v_{20} \tag{18}$$

$$u_{23} = v_{20} - v_{30} \tag{19}$$

$$u_{31} = v_{30} - v_{10} \tag{20}$$

The input current ii is deduced from the current of switches K<sub>1</sub>, K<sub>3</sub> and K<sub>5</sub>:

$$i_i = i_{K1} + i_{K3} + i_{K5} = F_1 \cdot i_1 + F_3 \cdot i_2 + F_5 \cdot i_3$$

(21)

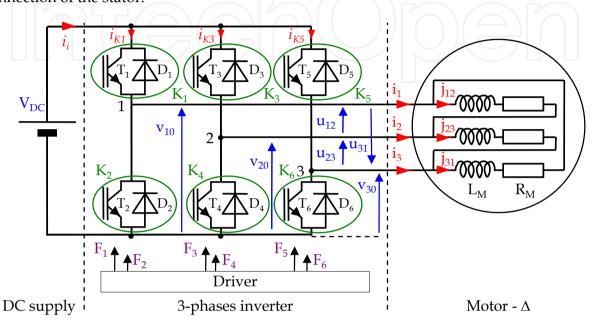

#### 4.2. Simulink model

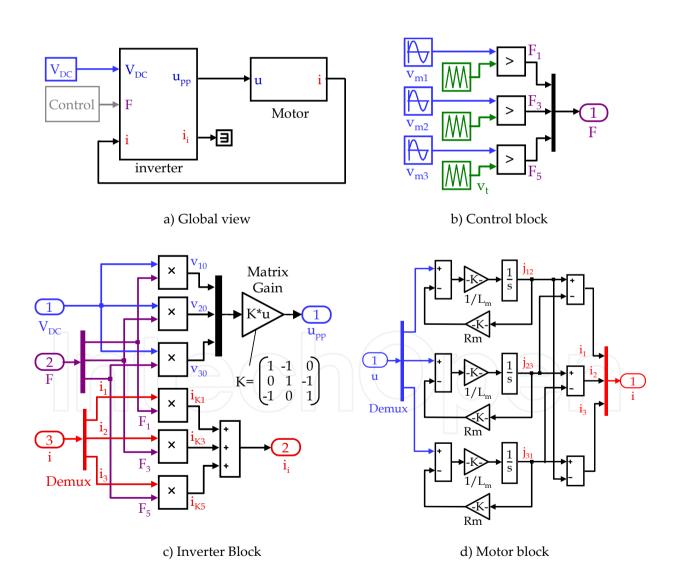

Simulink model of the three-phase inverter is shown in figure 12a. The control block is illustrated in figure 12b. It models a three phases PWM control. The inverter block is illustrated in figure 12c.

In the case of a resistive load, the load block is constituted by a gain block (value 1/R).

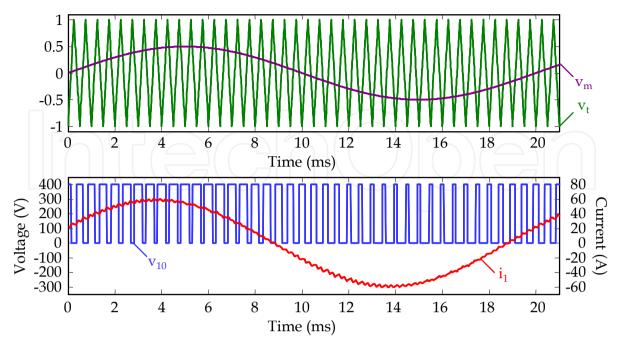

#### 4.3. Simulation example

The parameters used for of an open-loop simulation are:

The simulation of the open-loop three-phase inverter is illustrated in figure 13. The list of configuration parameters used is:

Start time: 0 Stop time: 1.5

Type: Variable-step Solver: ode15s (stiff/NDF)

Max step size: 1e-5

Min step size: auto

Solver: ode15s (stif/ND)

Relative tolerance: 1e-3

absolute tolerance: auto

The relation between the amplitude of the sinusoidal voltage and the triangular voltage determines the maximum value of the fundamental line-line voltage of the inverter:

$$U_{\text{max}} = \frac{\sqrt{3}}{2} \frac{V_{m \text{ max}}}{V_{t \text{ max}}} V_{DC} = \frac{\sqrt{3}}{2} \frac{0.5}{1} 400 = 173 V$$

(22)

Neglecting the current harmonics, the maximum value of the line current is deduced from equation (22):

$$I_{1 \text{ max}} = \sqrt{3} J_{12 \text{ max}} = \frac{\sqrt{3} \cdot U_{\text{max}}}{\sqrt{R_M^2 + (L_M 2 \pi f_m)^2}} = \frac{\sqrt{3} \cdot 173}{\sqrt{4^2 + (10^{-2} 2 \pi 50)^2}} = 59 \text{ A}$$

(23)

Simulations are in good agreement with theoretical values.

Figure 12. Three phase inverter

Figure 13. Simulation example of a three-phase inverter with PWM control

#### 5. Modeling and simulation of diode rectifiers

Three-phase AC to DC converters are widely used in many industrial power converters in order to obtain continuous voltage using a classical three-phase AC-line. These converters, when they are used alone or associated for specific applications, can present problems due to their non-linear behaviour. It is then important to be able to model accurately the behaviour of these converters in order to study their influence on the input currents waveforms and their interactions with the loads (classically inverters and AC-motors).

Several studies have shown the importance to have tools to simulate the behaviour of complex power electronics systems (Ladoux et al., 2005), (Qijun et al. 2007), (Zuniga-Haro & Ramirez, 2009) and several methods have been also presented in order to reduce the simulation time or to improve the precision. Although constant topology methods have been developed (Araujo et al., 2002), variable topology methods seem to be very suitable for simulation of power-electronics converters (Terrien et al., 1999).

In this chapter, an original and simple method is developed to model and simulate AC-DC converters taking into account overlap phenomenon with continuous and discontinuous conduction modes using Matlab-Simulink. The diodes are assumed ideal ( $v_d = 0$  when the diode is state-on,  $i_d = 0$  when the diode is state-off)

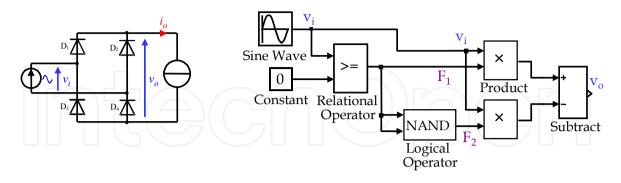

If the electrical network is considered as ideal (no line inductance) and the conduction is maintained continuous, (id>0), the modelling of the converters can be realised very simply by a functional approach (commutation functions) where the switches are opened or closed. An example is presented in figure 14.

$$v_0 = F_1 \cdot v_i - F_2 \cdot v_i$$

With :  $F_1 = 1$  if  $v_i > 0$  and  $F_1 = 0$  if  $v_i < 0$   $F_2 = 0$  if  $v_i > 0$  and  $F_2 = 1$  if  $v_i < 0$

a) Electrical circuit

b) Simulink equivalent circuit

**Figure 14.** Basic model of a single-phase rectifier.

In this chapter, the proposed approach is completely different from the approach based on commutation functions. It permits to simulate accurately the commutation in the six-pulse AC-DC converter, even under unbalanced supply voltages (the influence of voltages unbalances on AC harmonic magnitudes currents has been demonstrated (de Oliveira & Guimaraes, 2007) or line impedances conditions.

The overlap phenomenon and the unbalance of line impedances can be taken into account by modifying the commutation functions to correspond to the real behaviour of the rectifiers in these conditions. Indeed, the commutations are not instantaneous. Several contributions have already been proposed in scientific literature to refine the modelling of rectifiers. Most of these contributions show good simulation results but the analytical models used are complex and not reflecting precisely the real behaviour of the converter (Hu & Morrison, 1997), (Arrillaga et al., 1997). Some methods have been developed in order to model and simulate power factor corrected single-phase AC-DC converters (Pandey et al., 2004).

#### 5.1. Electrical model

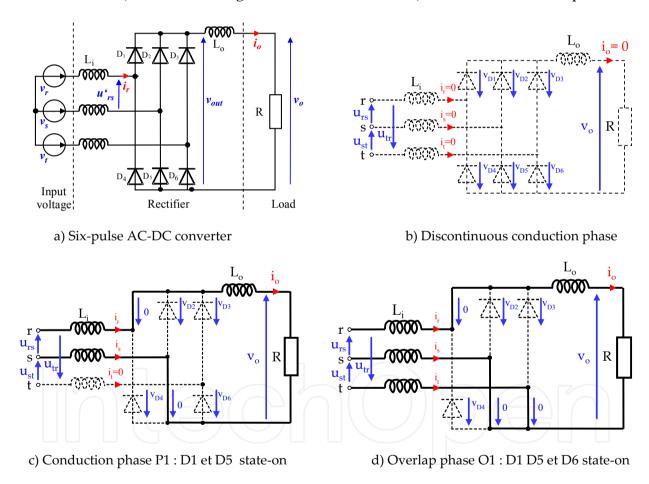

The six-pulse AC-DC converter is illustrated in figure 15a. Inductances Li characterize the line inductances and Lo characterizes the output inductance. The AC-DC converter modelling is based on the variable topology approach. The diodes are modelled by an ideal model which traduces the state of the switch:

- $v_D = 0$  when the diode is state-on:

- iD = 0 when the diode is state-off.

There are 13 operating phases:

1 phase of discontinuous conduction mode (P<sub>0</sub>)

All the diodes are state-off (figure 15b)

- 6 phases of classical conduction P<sub>1</sub> to P<sub>6</sub> (figure 15c)

$P_1$ :  $D_1$  and  $D_5$  state-on  $P_2$ :  $D_1$  and  $D_6$  state-on  $P_3$ :  $D_2$  and  $D_6$  state-on

$P_4: D_2$  and  $D_4$  state-on  $P_5: D_3$  and  $D_4$  state-on  $P_6: D_3$  and  $D_5$  state-on

- 6 phases of overlap O<sub>1</sub> to O<sub>6</sub> (figure 15d)

$O_1: D_1$ ,  $D_5$  and  $D_6$  state-on  $O_2: D_1$ ,  $D_2$  and  $D_6$  state-on  $O_3: D_2$ ,  $D_4$  and  $D_6$  state-on

$O_4: D_2$ ,  $D_3$  and  $D_4$  state-on  $O_5: D_3$ ,  $D_4$  and  $D_5$  state-on  $O_6: D_1$ ,  $D_3$  and  $D_5$  state-on

For an operating phase, we determinate the di/dt through each inductance (Li and Lo) and the voltage across each diode. In order to simplify results presentation, we consider that the line is balanced (same RMS voltages and line inductances Li) and have no resistive part.

Figure 15. Six-pulse diode rectifier.

Naturally, the method is equivalent under unbalanced conditions but the mathematical expressions of the different variables are more complex.

As an example, we will consider the following succession of phases: P<sub>0</sub>, P<sub>1</sub>, O<sub>1</sub>, P<sub>2</sub>, O<sub>2</sub>, P<sub>3</sub>...:

To shift from phase  $P_0$  (diodes state-off) to phase  $P_1$  ( $D_1$   $D_5$  state-on), the voltage across diodes  $D_1$  and  $D_5$  have to be equal to zero.

To shift from phase P<sub>1</sub> (D<sub>1</sub> D<sub>5</sub> state-on) to overlap phase O<sub>1</sub> (D<sub>1</sub> D<sub>5</sub> D<sub>6</sub> state-on), the voltage across the diode D<sub>6</sub> has to be equal to zero.

To shift from overlap phase O<sub>1</sub> (D<sub>1</sub> D<sub>5</sub> D<sub>6</sub> state-on) to phase P<sub>2</sub> (D<sub>1</sub> D<sub>6</sub> state-on), the current through the diode D<sub>5</sub> has to be equal to zero.

And so forth ...

#### 5.1.1. Discontinuous conduction mode

This mode corresponds to the case where  $i_0 = 0$  (figure 15b). In this case, all diodes are opened. Equation (24) describes this mode.

$$\frac{di_r}{dt} = \frac{di_s}{dt} = \frac{di_t}{dt} = 0 \tag{24}$$

#### 5.1.2. Continuous conduction mode

Let's take example of the continuous conduction mode P<sub>1</sub>. From the figure 15c, we can write equations (25), (26) and (27):

$$\frac{di_{r}}{dt} = -\frac{di_{s}}{dt} = \frac{di_{o}}{dt} = \frac{u_{rs} - v_{o}}{2L_{i} + L_{o}}$$

(25)

$$\frac{di_t}{dt} = 0 (26)$$

$$v_{D6} = u_{st} \frac{L_i}{2L_i + L_o} (u_{rs} - v_o)$$

(27)

We obtain the di/dt corresponding to the other continuous conduction modes by making circular permutations of indexes. For example, for conduction mode P2: D1 and D6 are stateon. The indexes s and t are permuted as presented below:

$$\frac{di_r}{dt} = -\frac{di_t}{dt} = \frac{di_o}{dt} = \frac{u_{\rm rt} - v_o}{2 L_i + L_o}$$

(28)

$$\frac{di_s}{dt} = 0 (29)$$

#### 5.1.3. Overlap phases

Let's take example of the overlap phase O<sub>1</sub>. From the figure 15c, we can write equations (30) and (31):

$$\frac{di_{r}}{dt} = \frac{di_{o}}{dt} \tag{30}$$

$$i_s + i_t = -i_0 \iff -\frac{di_s}{dt} - \frac{di_t}{dt} = \frac{di_o}{dt}$$

(31)

The expression of the di/dt as a function of the device parameters is more complicated to obtain here than in the case of a classical operating phase. Equations have been detailed in (Batard et al., 2007) and the final result is recalled below:

$$\frac{di_{r}}{dt} = \frac{di_{o}}{dt} = \frac{1}{3L_{i} + 2L_{o}} \left[ u_{rs} + u_{rt} - 2v_{o} \right]$$

(32)

$$\frac{di_{s}}{dt} = \frac{1}{3L_{i} + 2L_{o}} \left( -\frac{2L_{i} + L_{o}}{L_{i}} u_{rs} + \frac{L_{i} + L_{o}}{L_{i}} u_{rt} + v_{o} \right)$$

(33)

$$\frac{di_{t}}{dt} = \frac{1}{3L_{i} + 2L_{o}} \left( \frac{L_{i} + L_{o}}{L_{i}} u_{rs} - \frac{2L_{i} + L_{o}}{L_{i}} u_{rt} + v_{o} \right)$$

(34)

We obtain the di/dt corresponding to the other overlap modes by making circular permutations of indexes. For example, for overlap mode O<sub>2</sub>: D<sub>1</sub>, D<sub>2</sub> and D<sub>6</sub> are state-on. The indexes r and t are permuted and the sign of v<sub>s</sub> and di<sub>0</sub>/dt are changed:

$$\frac{di_{r}}{dt} = \frac{1}{3L_{i} + 2L_{o}} \left( \frac{L_{i} + L_{o}}{L_{i}} u_{ts} - \frac{2L_{i} + L_{o}}{L_{i}} u_{tr} - v_{o} \right)$$

(35)

$$\frac{di_{s}}{dt} = \frac{1}{3L_{i} + 2L_{o}} \left( -\frac{2L_{i} + L_{o}}{L_{i}} u_{ts} + \frac{L_{i} + L_{o}}{L_{i}} u_{tr} - v_{o} \right)$$

(36)

$$\frac{di_{t}}{dt} = -\frac{di_{o}}{dt} = \frac{1}{3L_{i} + 2L_{o}} \left[ u_{ts} + u_{tr} + 2v_{o} \right]$$

(37)

#### 5.2. Simulink model

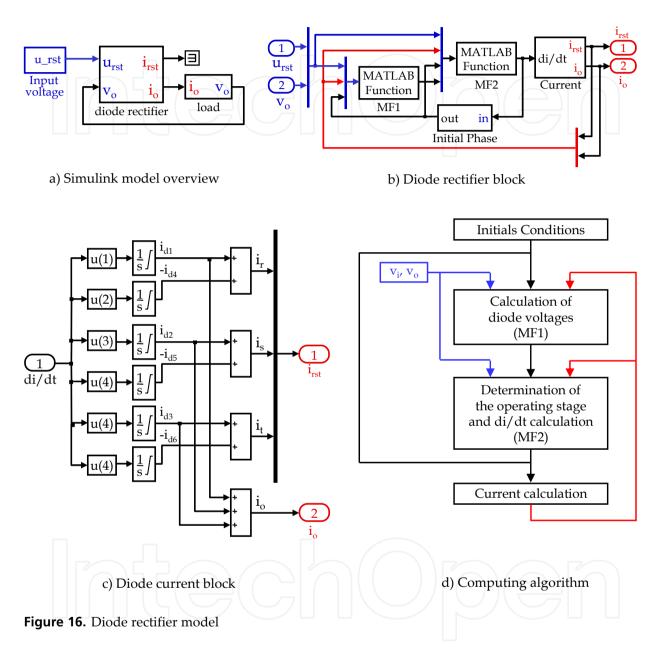

The simulink model of the six-pulse diode rectifier is illustrated in figure 16a. The resistive load is modelled as a gain. The internal structure of the diodes rectifier block is presented in figure 16b. Four different blocks can be seen on this scheme.

The first one called MF1 is a Matlab function which computes each diode voltage. The inputs of this block are the initial phase and the three-phase network voltages.

The second one called MF2 is also a Matlab function which computes the new operating phase and each inductance di/dt. Its computing algorithm is shown in figure 16d. The new operating phase depends on the initial phase, the diode voltages and currents.

The third, called "Initial Phase" extract the operating phase of the MF2 block, this operating phase becomes the initial phase of the next calculation step (the Simulink block "memory" is used).

The Current block computes each diode current which permits to obtain the DC current and the line currents.

The internal structure of the Current block is shown in figure 16c. The originality of our approach is the calculation of the values of each diode current with the values of di/dt of inductances Li and Lo. We use then six integrator blocks (one for each diode). The integrator blocks are set to limit their minimal output value to zero (lower saturation limit), this feature permits to avoid the problem of accurate determination of the instant when diodes currents reach to zero.

It is then possible to determinate the output current of the rectifier ( $i_0 = i_{D1} + i_{D2} + i_{D3}$ ) and the input line currents ( $i_r = i_{D1} - i_{D4}$ ,  $i_s = i_{D2} - i_{D5}$ ,  $i_t = i_{D3} - i_{D6}$ ).

#### 5.3. Experimental validation

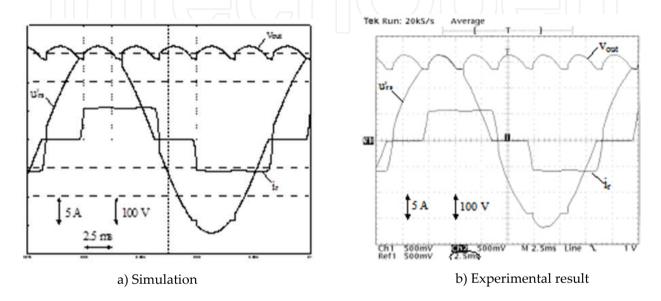

Simulations and experimental waveforms related to figure 15 are shown in figure 17. The simulation parameters are adjusted as follows:

$$U_{RMS} = 230 \text{ V}$$

;  $R = 58 \Omega$ ;  $L_i = 800 \mu\text{H}$ ;  $L_o = 800 \text{ mH}$

It can be seen that the simulated waveforms are very close to the experimental ones. The overlap interval  $v_1$  is equivalent for simulation and experimental results ( $v_1 \cong 0.7$  ms).

Figure 17. Comparison of Simulation and Experimental Waveforms in a six-pulse diode rectifier

The list of configuration parameters used for Matlab simulation is:

Start time: 0 Stop time: 0.2s Solver: ode15s (stiff/NDF) Type: Variable-step Max step size: 1e-4 Relative tolerance: 1e-5

Min step size: auto absolute tolerance: auto

Using a PC with an Intel core 2 duo CPU running at 2.19 GHz with 1 Go de RAM, the simulation time was 4 s.

This model has also been tested with a load constituted of an inverter and an induction machine. The results of this test have validated operations for discontinuous conduction mode. For the same configuration parameters, the simulation time was 5 s.

### 6. Modeling and simulation of thyristor rectifiers

The Simulink model of the controlled rectifier is very close to the Simulink model of the diode rectifier. Only the condition to turn the thyristor on is different to the condition to turn the diode on. For an ideal thyristor, it is recalled that the thyristor turn-on if its voltage is positive and if a current pulse is sent to the gate.

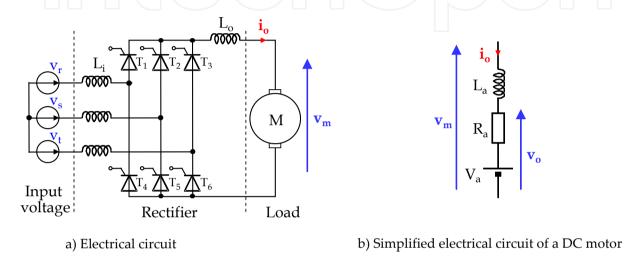

To illustrate the modelling of controlled rectifier with Simulink, let's look at one of the principles of speed control of DC machines.

#### 6.1. Electrical model

Let us consider the electrical scheme presented on figure 18a. It represents a DC motor fed by a six-pulse rectifier. The electrical equivalent circuit of the DC motor is described by an inductance La in series with a resistance Ra in series with an induced voltage Va which characterizes the electromotive force, as illustrated in figure 18b.

Figure 18. Controlled rectifier with inductive load

The thyristor are modelled by an ideal model which traduces the state of the switch:

- $V_T = 0$  when the thyristor is state-on

- $I_T = 0$  when the thyristor is state-off

Similar to the diode rectifier, there are 13 operating phases to describe:

1 phase of discontinuous conduction mode (P<sub>0</sub>)

All the thyristor are state-off

6 phases of classical conduction P<sub>1</sub> to P<sub>6</sub> (figure 15c)

P<sub>1</sub>: T<sub>1</sub> and T<sub>5</sub> state-on P<sub>2</sub>: T<sub>1</sub> and T<sub>6</sub> state-on P<sub>3</sub>: T<sub>2</sub> and T<sub>6</sub> state-on

P<sub>4</sub>: T<sub>2</sub> and T<sub>4</sub> state-on P<sub>5</sub>: T<sub>3</sub> and T<sub>4</sub> state-on P<sub>6</sub>: T<sub>3</sub> and T<sub>5</sub> state-on

6 phases of overlap O1 to O6 (figure 15d)

$O_1: T_1, T_5$  and  $T_6$  state-on  $O_2: T_1, T_2$  and  $T_6$  state-on  $O_3: T_2, T_4$  and  $T_6$  state-on

$O_4: T_2$ ,  $T_3$  and  $T_4$  state-on  $O_5: T_3$ ,  $T_4$  and  $T_5$  state-on  $O_6: T_1$ ,  $T_3$  and  $T_5$  state-on

The different operating phases are illustrated in figure 15. The equations that governs an operating phase are the same whatever we work on a diode rectifier or a controlled rectifier.

#### 6.2. Simulink model

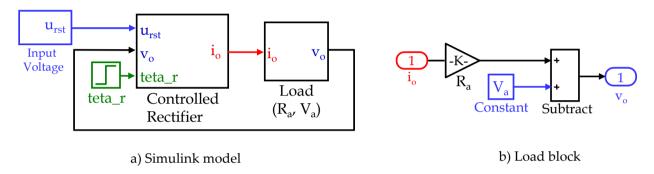

The simulink model of the controlled rectifier with inductive load is presented in figure 19. It consists of four blocks:

- Input Voltage block characterizes the mains supply,

- teta\_r block models the thyristor control,

- Controlled rectifier block computes the different operating phases.

- The load block represents the motor resistance Ra and the induced voltage Va.

The motor inductance  $L_a$  is regrouped with the output line inductance  $L_o$  to have a single output inductor  $L_{oeq}$ .

Figure 19. Simulink model of the controlled rectifier with inductive load

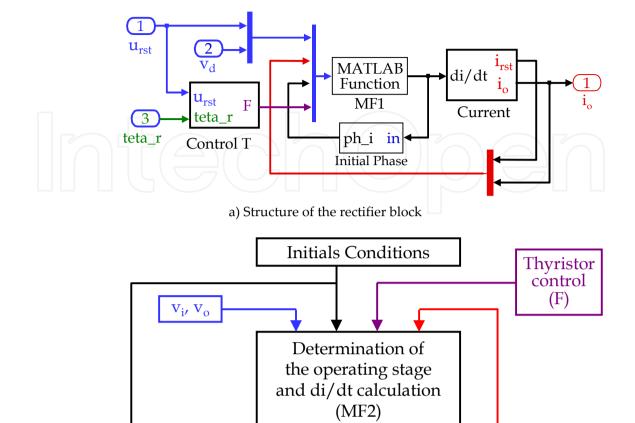

#### 6.2.1. Internal structure of the rectifier block

The structure of the rectifier block is presented on figure 20a. Four different blocks can be seen on this scheme: the first one called "Control T" is used for the control of the thyristor gate. The second one called MF1 is used to compute the inductances state and voltage. The third called Current computes inductances currents. Then, the Initial Phase block computes the initial state for next computing phase.

The computing algorithm has been created in accordance with figure 20b. For each computing step, the new operating phase is calculated. This phase is a function of the initial phase, the sign of the inductance currents and the diode voltages. For each operating phase, the value of each inductance di/dt is calculated and permits to know the diodes currents with the integrator function.

The current block is strictly identical to the current block shown in figure 16.

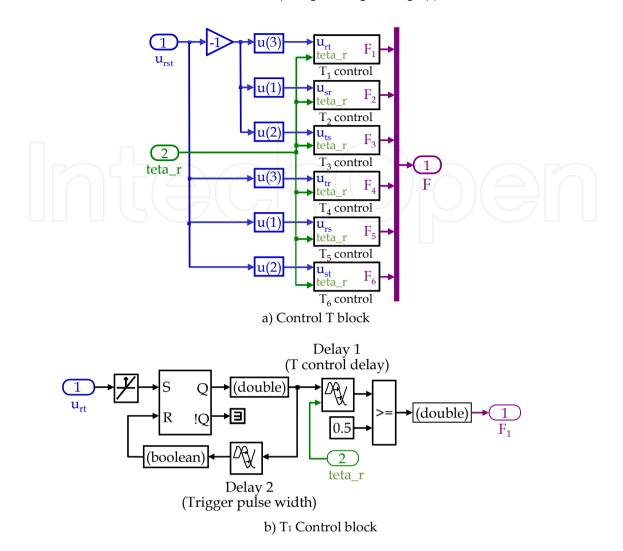

#### *6.2.2. Thyristor control*

The control device for thyristor  $T_1$  is presented in figure 21. The switch-on of  $T_1$  is delayed of  $\theta_r$  after  $u_{rt}$  has reached to zero (block "Delay 1"). The control thus carried out is a pulse train (the width of a pulse is computed by block "Delay 2").

The same principle is applied to the other thyristor.

b) Computing algorithm

Current calculation

**Figure 20.** Structure of the rectifier block

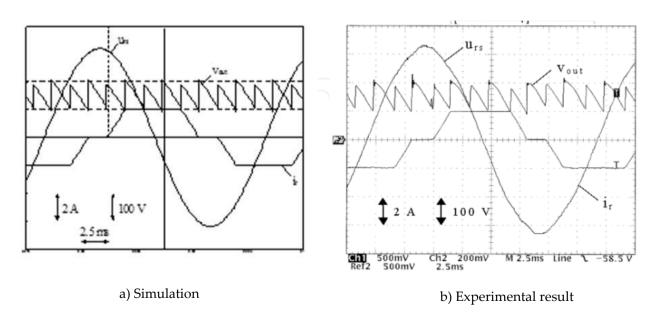

#### 6.3. Experimental validation in continuous conduction mode

Simulations and experimental waveforms related to the electrical circuit presented in figure 18 are shown in figure 22. The simulation parameters are adjusted as follows:

$$U_{RMS} = 230 \text{ V}$$

;  $R_a = 4 \Omega$ ;  $V_a = 145 \text{ V}$ ;  $L_i = 800 \mu\text{H}$ ;  $L_{oeq} = 800 \text{ mH}$

The list of configuration parameters used for Matlab simulation is:

Start time: 0 Stop time: 0.2s

Solver: ode15s (stiff/NDF) Type: Variable-step

Max step size: 1e-4 Relative tolerance: 1e-5

Min step size: auto absolute tolerance: auto

Figure 21. Control of thyristor T<sub>1</sub>

Figure 22. Comparison of Simulation and Experimental Waveforms

We can see that simulation results are in good agreement with experimental waveforms. The overlap delays are equivalent for simulation and experimental results.

#### 7. Conclusion

This chapter has shown that it is possible to simulate many electrical power converters only using Simulink toolbox of Matlab, thus avoiding the purchase of expensive and complex dedicated software. The simulation method is based on the variable topology approach where switching conditions of semiconductor are realized by switching functions.

The first part of this chapter is dedicated to the modelling of linear loads: RL series, RLC series and L in series with RC parallel dipoles are considered. The second part deals with the simulation of DC-DC converters. The buck converter is first studied: after describing the operating phases, open-loop and closed-loop models are presented. A simulation is realised for closed-loop model showing good agreement with theoretical values. The third part shows how to model three-phases DC-AC converters. The electrical circuit and his complete Simulink model are presented and simulation results on RL series load with PWM control are shown. The fourth part presents the modelling of a six-pulse AC-DC converter which is frequently used in industrial applications. The complete model of this converter and his Simulink equivalent circuit are accurately described taking into account overlap phenomenon. A simulation result on RL series load is presented and compared to experimental result. The similarity of the two results shows the validity of the proposed model. The fifth part extends the method to controlled rectifier. The structure studied here is a six-pulse thyristor rectifier feeding a DC motor. The difference with the diode rectifier is presented with the introduction of a thyristor control block in the simulation. Simulations results are showed in continuous condition mode and are in good agreement with experimental results.

Many of the results presented in this chapter are computed with short simulation times (few seconds). This can be achieved thanks to the simplicity of the proposed method. The power electronics converters presented are used alone but the method can be easily extended to cascaded devices allowing the simulation of complex power electronic structures such as, for example, active filters with non-linear loads.

#### Author details

Christophe Batard, Frédéric Poitiers, Christophe Millet and Nicolas Ginot Lunam University - University of Nantes, UMR CNRS 6164, Institut d'Electronique et de Télécommunications de Rennes (IETR), France

#### 8. References

Ladoux, P.; Postiglione, G.; Foch, H.; & Nuns, J.; "A Comparative Study of AC/DC Converters for High-Power DC Arc Furnace," IEEE Trans. Indus. Electron., vol. 52, no. 3, pp. 747-757, June 2005.

- Qijun, P.; Weiming, M.; Dezhi, L.; Zhihua, Z. & Jin, M.; "A New Critical Formula and Mathematical Model of Double-Tap Interphase Reactor in a Six-Phase Tap-Changer Diode Rectifier," IEEE Trans. Indus. Electron., vol. 52, no. 1, pp 479-485, Feb. 2007.

- P. Zuniga-Haro, J. M. Ramirez, "Multi-pulse Switching Functions Modeling of Flexible AC Transmission Systems Devices", Electric Power Components and Systems, Volume 37, Issue 1 January 2009, pages 20 – 42.

- R. E. Araujo, A. V. Leite and D. S. Freitas, "Modelling and simulation of power electronic systems using a bond graph formalism," Proceedings of the 10th Mediterranean Conference on Control and Automation - MED2002 Lisbon, Portugal, July 9-12, 2002.

- F. Terrien, M. F. Benkhoris and R. Le Doeuff, "An Approach for Simulation of Power Electronic Systems," *Electrimacs'* 99, Saint Nazaire, France, vol. 2, pp 201-206.

- S. E. M. de Oliveira and J. O. R. P. Guimaraes, "Effects of Voltage Supply Unbalance on AC Harmonic Current Components Produced by AC/DC Converters", IEEE Trans. on Power Delivery, vol. 22, no. 4, pp. 2498-2507, Oct. 2007.

- L. Hu and R. E. Morrison "The use of modulation theory to calculate the harmonic distorsion in HVDC systems operating on an unbalanced supply," IEEE Trans. on Power Delivery., vol. 12, no. 2, pp. 973-980, May 1997, Letters to editor.

- J. Arrillaga, B. C. Smith, N. R. Watson and A. R. Wood, "Power system harmonic analysis," ed John Wiley & Sons, 1997.

- A. Pandey, D. P. Kothari, A. K. Mukerjee, B. Singh, "Modelling and simulation of power factor corrected AC-DC converters", International Journal of Electrical Engineering Education, Volume 41, Issue 3, July 2004, pp 244-264.

- C. Batard, F. Poitiers and M. Machmoum, "An Original Method to Simulate Diodes Rectifiers Behaviour with Matlab-Simulink Taking into Account Overlap Phenomenon," IEEE International Symposium on Industrial Electronics 2007, ISIE 2007, pp 971-976, Vigo, Spain, 4-7 June 2007