We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

186,000

200M

Our authors are among the

TOP 1% most cited scientists

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

### Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

### A dynamically configurable discrete event simulation framework for many-core chip multiprocessors

Christopher Barnes and Jaehwan John Lee Indiana University Purdue University Indianapolis U.S.A.

#### 1. Introduction

#### 1.1 Background

Processor simulation is often a cornerstone in the research of new processor concepts and the education of computer architecture students. Simulators are used by researchers to validate architecture designs and explore new concepts before actual implementation. Educators use simulators to elucidate concepts in computer architecture through hands-on exercises and demonstrations. To be useful for both researchers and educators, simulators must be flexible, easy to use, easy to understand, and fast.

Simulation speed and configurability are two important aspects in the design of processor simulators. In the past, fast simulations were typically made with a monolithic design and were written to simulate a particular architecture. However, this approach required a complete understanding of the source code before the user could deviate from the original design. To overcome this drawback, some simulators embraced a more modular design, while others attempted to provide some customizability in the simulator by integrating and using Architecture Description Languages (ADLs) to describe its functionality. This approach is easier but still requires the user to undergo a lengthy learning curve to begin generating useful results.

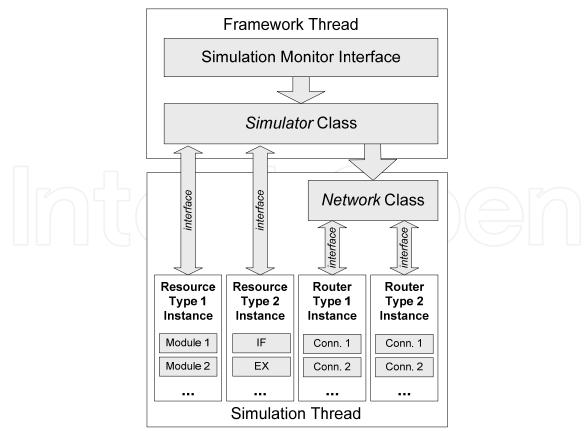

As the industry moves toward merging many different, highly specialized processor resources on one physical chip, there is a need for a highly configurable discrete event simulation environment for the study of heterogeneous processor designs. Introduced in this chapter is Mhetero, a novel simulation framework that enables users to easily construct and perform discrete event simulations that meet this need.

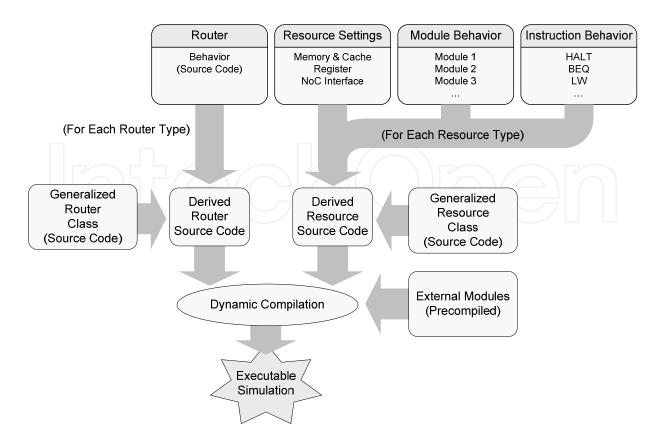

Our simulation framework addresses the need for fast as well as configurable simulations by taking advantage of the dynamic compilation capabilities of the Microsoft's .NET development library in two ways. First, we use dynamic compilation to produce simulations based on configuration information gathered through an easy-to-use GUI. The entire process is a seamless and user-friendly experience, meaning that the user does not

leave the framework to execute external compilers, write source code, or edit configuration files. Second, the simulations produced by the framework are compiled to an intermediate language (Compiling to MSIL, 2010), resulting in quick compilation time as well as execution speeds matching that of other compiled .NET programs. While the overall performance of C# does not match that of C++, there are numerous advantages of utilizing C# for scientific computing (Gilani, 2004), which are leveraged in our framework. Moreover, the framework's design is open and modular, allowing simulation designers to produce any sort of simulator that they may desire, even simulations extending beyond the tasks associated with a typical processor simulator. Although here we describe the techniques used in the design of Mhetero, the techniques are also applicable to other types of discrete event simulators.

Mhetero's simulation infrastructure is similar to other discrete event/time simulators with a few notable differences that facilitate processor simulation. First, instead of using a single, global event queue, Mhetero maintains several, separate event queues each modeling a communication channel between any two entities/modules of simulation. Second, instead of activating modules when certain events occur, entities/modules are activated during each cycle and these modules can then choose to process corresponding events immediately or after a specified number of cycles ensuring causality and synchronism between events in the simulation (Lee & Vincentelli, 1998). Hence, Mhetero's simulation infrastructure can be categorized as a synchronous, discrete time-simulation infrastructure which by definition itself is a discrete event simulation infrastructure (Lee & Vincentelli, 1998). As a result, the framework is not only an interesting and powerful alternative to other discrete event simulators but also a useful tool for computer architecture researchers, educators, and students.

In this chapter, we will discuss the design and construction of our simulation framework. We will begin by reviewing some of the previous work in the area of computer architecture simulation. We then discuss our configuration interface (Sections 2 and 4), dynamic compilation technique (Section 3), and intra-resource communication (Section 4). Finally, we will discuss several experiments that were conducted to verify the framework's design (Section 5).

#### **1.2 Previous Work**

Over the past several decades a considerable amount of research has been done in the area of computer architecture simulation. SimpleScalar (SimpleScalar LLC., 2010) and its variations have been used mostly for single processor simulation and research while the SimpleScalar multiprocessor version (Univ. of Minnesota, 2010), GEMS (Martin, et al, 2005), RSIM (Pai, et al, 1997), VASA (Wallin, et al, 2005), and WWT-II (Mukherjee, et al, 1997) (as well as its earlier versions) have been used mainly for multicore or chip-multiprocessor (CMP) simulation. While these simulators are very fast, they are not intended to produce retargetable simulations; i.e., these simulators are monolithic and cannot simulate other architectures beyond the originally intended architecture. Other simulators such as Simics (Magnusson, et al., 2002), Bochs (Bochs, 2010), and GxEmul (GXEmul, 2010) are full-system simulators for both single and multiprocessor simulation. These simulators are typically

used for the development and testing of software on various platforms, and are also not designed to be easily retargetable.

A previous approach to retargetable simulators is investigated through the use of computer Architecture Description Languages (ADLs) such as Expression (Halambi, et al, 1999), LISA (Zivojnovic, et al, 1996), nML (Freericks, 1991), and RCPN (Reshadi & Dutt, 2005). These tools have been proposed primarily for automatic generation of computer architecture simulators. Although these tools produce retargetable simulators, their respective ADLs can often be difficult for new users to learn. Additionally, the generation of simulators is typically a disjointed and error-prone process that depends on external compilers and programs to function.

Asim (Emer, et al., 2002), a framework for modeling the performance of a processor (e.g., timing delays and signal propagation delays), most closely resembles Mhetero as it is a retargetable simulation framework that segments functional units into modules and includes two graphical tools for generating and viewing configuration files. However, Asim includes a seperate controller program used to execute simulations. On the contrary, Mhetero builds on the concept of using a single unified GUI for both configuration and simulation, creating a seamless environment. This approach, enabled by the techniques described in this chapter, allows the user to focus on developing their simulations without being burdened by the inner workings of the simulator's configuration.

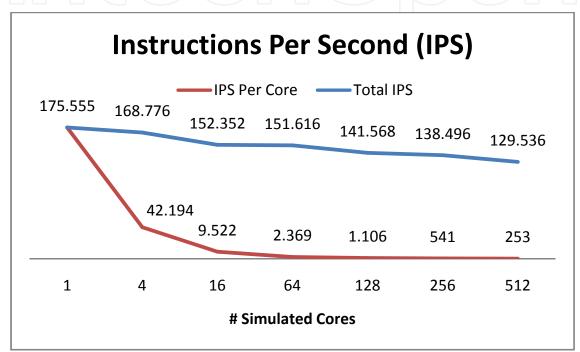

Our simulation framework is built to minimize the difficulties associated with retargetable simulators by providing an easy-to-use GUI intended to offer a minimal learning curve. Additionally, simulators built by our framework are compiled using a technique that is completely concealed from the user, avoiding any compiler configuration concerns. Finally, simulators generated by our framework are capable of being competitive with other major simulators in terms of instructions per second. The performance of the resulting simulations is addressed in Sections 3.7 and 5.5.

#### 1.3 Definitions

Before we proceed with the explanation of our simulation framework, we will take a moment to explain some of the terminology used throughout this chapter.

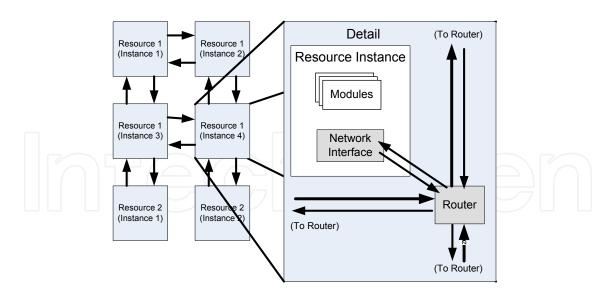

*Resources* represent any high level component in a simulated system such as a processor core, I/O, or memory. Resources can perform any sort of behavior that the simulation designer wishes. Note that the network is treated separately from a resource by the framework, and is explained in detail in Section 4.

*Modules* represent functional units within a resource, such as processor stages, branch predictors, and forwarding units.

*Simulation designer* is the user who is using the simulation framework for the purpose of producing or revising a processor simulator.

*Configurability* refers to the process of creating or customizing a new simulator by changing the settings (e.g., cache configuration) and source code of modules, resources, and routers in the simulation configuration.

#### 2. Resource Configuration Interface

#### 2.1 Overview

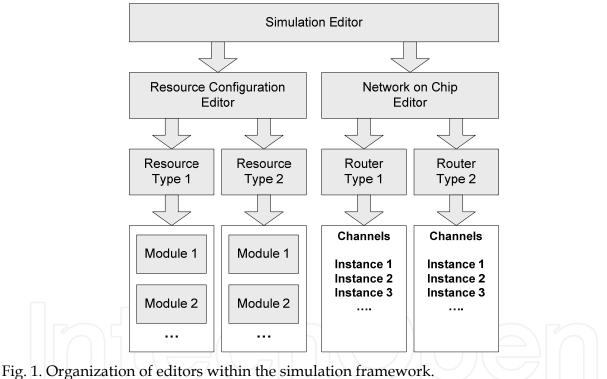

Option-based or text-based configuration of processor simulators can often be a confusing and difficult task for novice and expert users. This process typically requires the user to learn a new programming language or data format, and can require external, third party tools. To improve the configuration process, our framework allows users to completely configure their simulator in a Microsoft Windows GUI, making the learning curve minimal to non-existent. Discussed in this section are the various editors that can be used by the simulation designer to configure their simulations. Figure 1 depicts the organization of the editors for the design and configuration of simulations.

rig. 1. Organization of eurors within the simulation mane

#### 2.2 Simulation Editor

The *Simulation Editor*, the first editor that users encounter, acts as a gateway to the Resource and Network-on-Chip (NoC) Configuration Editors. Simulation configurations are composed of multiple types of resources and networks; therefore, this layer is necessary to allow users to choose either editing existing resources and networks, or defining new ones. Once the user selects a resource or network, its respective editor is initiated for the user to modify its functionality. The remainder of Section 2 details the Resource Configuration Editor, and the NoC Configuration Editor is discussed in Section 4.

#### 2.3 Resource Configuration Editor (RCE)

The *Resource Configuration Editor (RCE)* is the central location for editing the function or structure of a resource type. Within the RCE, there are many tabs that enable users to modify every aspect of the resource type, including instructions, registers, memory, cache, data flow, and behavioral logic. Figure 2 shows the RCE interface. Several of the more simple tabs are discussed in this subsection, and the remaining tabs are described in Sections 2.4 – 2.7.

| asic Configuration Registers<br>Modules (Stages and Function | Modules Module Communication Instruction Types Instructions Memory & Cache NoC Interface                                                                           |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Modules (Stanes and Function                                 |                                                                                                                                                                    |

| modules (stages and ranctorn                                 | al Units)<br>Module Configuration                                                                                                                                  |

| Module Name                                                  | Module Name Memory                                                                                                                                                 |

| Fetch                                                        | Execution Order 4 + Auto Create None -                                                                                                                             |

| Decode                                                       |                                                                                                                                                                    |

| Execute                                                      | Source Code External Modules                                                                                                                                       |

| Memory                                                       | if(EX2MEM == null) return;                                                                                                                                         |

| Writeback                                                    | f(EX2MEM.nop)return;                                                                                                                                               |

| Branch Predictor                                             | MEM2WB.originPC = EX2MEM.originPC;<br>MEM2WB.org = EX2MEM.nop;<br>MEM2WB.vaid = true;<br>MEM2WB.vai = EX2MEM.rd;<br>MEM2WB.rt = EX2MEM.rt;<br>if(IEX2MEM.nop)<br>{ |

Fig. 2. A screenshot of the RCE Interface.

The *Basic Configuration* tab contains fields for the name of the resource type, the number of instances, and the applications to execute on each instance of the resource. Users are able to choose a default program that will run on all instances, and/or choose particular programs to run on specific instances. For example, to implement a master/slave distributed processing application, two programs could be used. The master program, executing on one resource instance, would be used to aggregate the results of the slave resources, running a different program.

The *Registers* tab provides an interface for the user to specify the register names, number of registers, and data types. The *Instruction Types* tab allows the user to specify the instruction format which is used to disassemble the resource's program for debugging purposes. The

*NoC Interface* allows the user to specify the input and output queues, queue size, and data type for the resource's network interface.

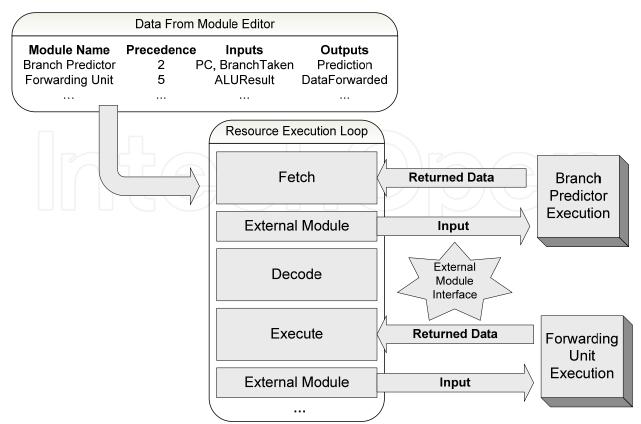

#### 2.4 Module Editor

Modules are a core concept to the extendibility and configurability of the framework. A set of modules forms a resource. Modules can represent stages or components such as branch predictors, data forwarding units, hazard detection units, or any sort of experimental unit. The modularity of the framework facilitates completely configurable simulations, enabling users to conceive of any sort of chip resource. Moreover, modules allow the user to easily extend the functionality of their simulations by defining a new module and assigning it a position in the resource's execution loop. The newly defined module will become a part of the simulation in its next execution.

The module editor (shown in Figure 2) allows the user to input the module's name, execution precedence (i.e., order), and a section of C# source code describing the module's behavior into the framework. The module's behavioral source code has access to all of the inputs and outputs to the module, as well as the resource's memory and registers.

External modules can also be linked to the resource in this tab. The user can choose a precompiled Dynamic-Link-Library (DLL) file, the name of the class to instantiate, and the variable name of the instantiated class (which may be referenced by other behavioral source code). External modules give the user complete control over the modules' implementation, including the ability to define additional functions, classes, and variables that will be available to other modules in the resource. Details on how external modules are linked to the resource are given in Section 3.5.

#### 2.5 Module Communication

Under the *Module Communication* tab, the user can describe data channels that connect one module to another as the resource is executed. The user must specify the source and destination modules, channel name, and variables to be included in the data channel. During the compilation process, these channels are combined into data structures that are available as variables to the module's behavioral source code. A module should read its available inputs and act upon them, as well as produce valid outputs, if necessary. The management of communication data between modules is handled by the framework through the use of *Queues* (MSVC Dev. Center, 2010).

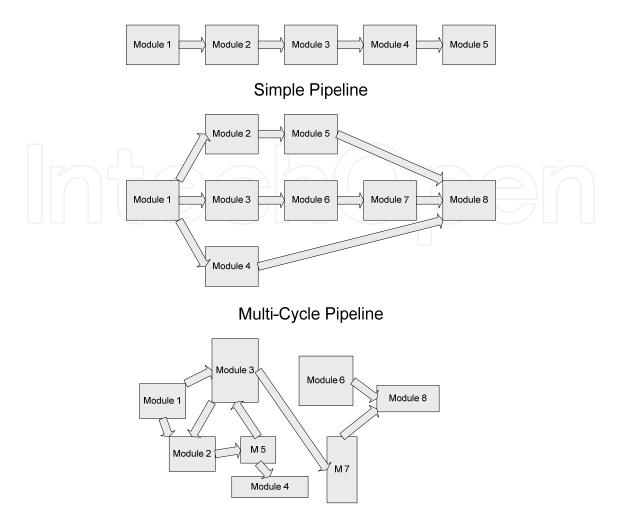

Module communication combined with the module's execution precedence allows the user to design versatile resources such as a pipelined execution unit. The open architecture of our framework allows users to specify arbitrary pipeline designs as shown in Figure 3.

Arbitrary Configuration

Fig. 3. Potential pipeline configurations.

#### 2.6 Instructions

The *Instructions* tab provides access to the instructions that are implemented in the resource. Here, users can add, delete, or edit instructions. Instructions have an associated name, op code, and instruction format type (which are specified in the *Instruction Types* tab). The C# source code that describes the behavior of the instruction is also entered here. If desired, the instruction source code may be used to automatically generate execution stage source code during compilation (detailed in Section 3.3).

#### 2.7 Memory and Cache

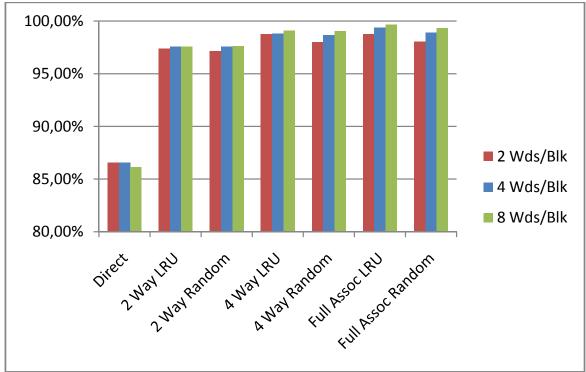

The *Memory & Cache* tab enables the user to specify the size and type of the data and instruction memory as shown in Figure 4. The user may specify single or multi-level cache systems with various configurations. The framework supports Direct Mapped, Set Associative, and Fully Associative cache types, as well as Least Recently Used (LRU) and random replacement schemes. The user may also specify the cache size and latencies of each cache level.

| asic Configuration Registers Modules Module Communication Instruction Types Instructions Memory & Cache NoC Interface Memory & Cache Memory & Cache Memory Configuration Data Memory Type Unsigned Integer 64 Bit  Instr. Memory Type Unsigned Integer 32 Bit  # of Words  3000  # of Words  100  # of Words  100  # of Words  Data Position  Cache Configuration  Level Type Replacement Sets Blocks/Set Words/Blk Latency Size  1  Vords  Set Associative LRU  II28  Memory Acache Level Delete Cache Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Memory & Cache<br>Memory Configuration<br>Data Memory Type Unsigned Integer 64 Bit Instr. Memory Type Unsigned Integer 32 Bit<br># of Words 3000 * # of Words 100 *<br>Latency (Cycles) 10 *<br>Instruction Position 0 * (Word)<br>Data Position 75 * (Word)<br>Cache Configuration<br>Level Type Replacement Sets Blocks/Set Words/Blk Latency Size<br>1 * Direct Mapping * LRU * 32 * 1 * 4 * 0 1024 B<br>2 * Set Associative * LRU * 128 * 1 * 4 * 20 4 Ho                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | onfig  | guration Edit             | or (RC  | E)         |         |        |            |            |          |                |          | 174          |                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------|---------|------------|---------|--------|------------|------------|----------|----------------|----------|--------------|-----------------------|

| Data Memory Type Unsigned Integer 64 Bit   # of Words   3000   # of Words   10   # of Words   11   # of Words   11   # of Words   12   # of Words   13   # of Words   14   # of Words   15   # of Words   16   17   # of Words   18   # of Words   # of Words <td>Memory Configuration<br/>Data Memory Type       Unsigned Integer 64 Bit       Instr. Memory Type       Unsigned Integer 32 Bit         # of Words       3000       #       # of Words       100       #         Latency (Cycles)       10       #       # of Words       100       #         Instruction Position       0       @       (Word)       10       #         Data Position       75       @       (Word)       #       #       0       1024 B         Cache Configuration       1       Palacement       Sets       Blocks/Set       Words/Blk       Latency       Size         1       Direct Mapping       LRU       32       1       4       0       1024 B         2       Set Associative       LRU       128       1       4       20       4 Wo</td> <td>asic Configura</td> <td>tion</td> <td>Registers /</td> <td>Module</td> <td>s Module</td> <td>Communi</td> <td>cation</td> <td>Instructio</td> <td>n Types</td> <td>Instruc</td> <td>tions</td> <td>Memory</td> <td>&amp; Cache No</td> <td>oC Interface</td> | Memory Configuration<br>Data Memory Type       Unsigned Integer 64 Bit       Instr. Memory Type       Unsigned Integer 32 Bit         # of Words       3000       #       # of Words       100       #         Latency (Cycles)       10       #       # of Words       100       #         Instruction Position       0       @       (Word)       10       #         Data Position       75       @       (Word)       #       #       0       1024 B         Cache Configuration       1       Palacement       Sets       Blocks/Set       Words/Blk       Latency       Size         1       Direct Mapping       LRU       32       1       4       0       1024 B         2       Set Associative       LRU       128       1       4       20       4 Wo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | asic Configura                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | tion   | Registers /               | Module  | s Module   | Communi | cation | Instructio | n Types    | Instruc  | tions          | Memory   | & Cache No   | oC Interface          |

| Data Memory Type Unsigned Integer 64 Bit   # of Words   3000   # of Words   10   Latency (Cycles)   10   Instruction Position   0   Image: Cache Configuration     Cache Configuration     Level   Type   Replacement   Sets   Blocks/Set   Words/Blk   Latency   Size   1   Direct Mapping   LRU   128   1   4     III     III     III     III     III     III     III     III     IIII     IIIII     IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Data Memory Type Unsigned Integer 64 Bit   # of Words 3000   10 +   # of Words 100   Latency (Cycles) 10   10 +   Instruction Position 0   75 +   (Word)   Cache Configuration   Level Type   Replacement Sets   Blocks/Set Words/Blk   Latency Size   1 Direct Mapping   LRU 128   1 4     *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | and the second se |        | ition                     |         |            |         |        |            |            |          |                |          |              |                       |

| Latency (Cycles) 10<br>Instruction Position 0<br>Data Position 75<br>(Word)<br>Cache Configuration<br>Cache Configuration<br>Level Type Replacement Sets Blocks/Set Words/Blk Latency Size<br>1 • Direct Mapping • LRU • 32 • 1 • 4 • 0 1024 B<br>2 • Set Associative • LRU • 128 • 1 • 4 • 20 4 100<br>4 • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Latency (Cycles) 10<br>Instruction Position 0<br>Data Position 75<br>(Word) Cache Configuration<br>Cache Configuration<br>Level Type Replacement Sets Blocks/Set Words/Blk Latency Size<br>1 • Direct Mapping • LRU • 32 • 1 • 4 • 0 1024 B<br>2 • Set Associative • LRU • 128 • 1 • 4 • 20 4 Kb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Data Memor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | у Тур  | e Unsign                  | ed Inte | ger 64 Bit |         | •      |            | Instr. Mer | nory Typ | be [           | Unsigned | Integer 32 B | 3it 👻                 |

| Instruction Position 0 Word)<br>Data Position 75 Word)<br>Cache Configuration<br>Level Type Replacement Sets Blocks/Set Words/Blk Latency Size<br>1 • Direct Mapping • LRU • 32 • 1 • 4 • 0 1024 B<br>2 • Set Associative • LRU • 128 • 1 • 4 • 20 4 Kb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Instruction Position 0 (Word)<br>Data Position 75 (Word)<br>Cache Configuration<br>Cache Configuration<br>Level Type Replacement Sets Blocks/Set Words/Blk Latency Size<br>1 • Direct Mapping • LRU • 32 • 1 • 4 • 0 1024 B<br>2 • Set Associative • LRU • 128 • 1 • 4 • 20 4 Kb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | # of Words                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | 3000                      |         |            |         |        |            | # of Word  | ds       | Ī              | 100      |              | *                     |

| Instruction Position 0 Word)<br>Data Position 75 Word)<br>Cache Configuration<br>Level Type Replacement Sets Blocks/Set Words/Blk Latency Size<br>1 • Direct Mapping • LRU • 32 • 1 • 4 • 0 1024 B<br>2 • Set Associative • LRU • 128 • 1 • 4 • 20 4 Kb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Instruction Position 0 (Word)<br>Data Position 75 (Word)<br>Cache Configuration<br>Cache Configuration<br>Level Type Replacement Sets Blocks/Set Words/Blk Latency Size<br>1 • Direct Mapping • LRU • 32 • 1 • 4 • 0 1024 B<br>2 • Set Associative • LRU • 128 • 1 • 4 • 20 4 Kb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Latency (Cy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | cles)  | 10                        |         | A.         |         |        |            | Latency (  | Cycles)  | -              | 10       |              | <b>4</b>              |

| Data Position       75       (Word)         Cache Configuration         Level       Type       Replacement       Sets       Blocks/Set       Words/Blk       Latency       Size         1 <ul> <li>Direct Mapping</li> <li>LRU</li> <li>32</li> <li>1</li> <li>4</li> <li>0</li> <li>1024 B</li> <li>2</li> <li>Set Associative</li> <li>LRU</li> <li>128</li> <li>1</li> <li>4</li> <li>20</li> <li>4 Kb</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Data Position       75       (Word)         Cache Configuration         Level       Type       Replacement       Sets       Blocks/Set       Words/Blk       Latency       Size         1       Direct Mapping       LRU       32       •       1       •       0       1024 B         2       •       Set Associative       •       LRU       •       128       •       1       •       4       •       0       4/46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Instruction P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ositio | n 0                       |         |            | (Word)  |        |            |            |          | n il           |          |              |                       |

| Cache Configuration          Level       Type       Replacement       Sets       Blocks/Set       Words/Blk       Latency       Size         1 <ul> <li>Direct Mapping</li> <li>LRU</li> <li>32</li> <li>1</li> <li>4</li> <li>0</li> <li>1024 B</li> <li>2</li> <li>Set Associative</li> <li>LRU</li> <li>128</li> <li>1</li> <li>4</li> <li>20</li> <li>4 Kb</li> <li>4</li> <li>4</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                  | Cache Configuration          Level       Type       Replacement       Sets       Blocks/Set       Words/Blk       Latency       Size         1 <ul> <li>Direct Mapping</li> <li>LRU</li> <li>32</li> <li>1</li> <li>4</li> <li>✓</li> <li>Set Associative</li> <li>LRU</li> <li>128</li> <li>1</li> <li>4</li> <li>20</li> <li>4 Kb</li> <li>4</li> <li></li></ul> | Data Positio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | 1000 (1200)               |         |            |         |        |            |            |          |                |          |              |                       |

| Level     Type     Replacement     Sets     Blocks/Set     Words/Blk     Latency     Size       1 <ul> <li>Direct Mapping</li> <li>LRU</li> <li>32</li> <li>1</li> <li>4</li> <li>0</li> <li>1024 B</li> <li>2</li> <li>Set Associative</li> <li>LRU</li> <li>128</li> <li>1</li> <li>4</li> <li>20</li> <li>4 Kb</li> <li>4</li> <li></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                    | Level         Type         Replacement         Sets         Blocks/Set         Words/Blk         Latency         Size           1 <ul> <li>Direct Mapping</li> <li>LRU</li> <li>32</li> <li>1</li> <li>4</li> <li>0</li> <li>1024 B</li> </ul> 1024 B     1020 B     1020 B     1024 B                                                                                                                                                                                                                            | Data Position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 91 S   | /5                        |         | 171        | (Word)  |        |            |            |          |                |          |              |                       |

| Level     Type     Replacement     Sets     Blocks/Set     Words/Blk     Latency     Size       1 <ul> <li>Direct Mapping</li> <li>LRU</li> <li>32</li> <li>1</li> <li>4</li> <li>0</li> <li>1024 B</li> <li>2</li> <li>Set Associative</li> <li>LRU</li> <li>128</li> <li>1</li> <li>4</li> <li>20</li> <li>4 Kb</li> <li>4</li> <li></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                    | Level         Type         Replacement         Sets         Blocks/Set         Words/Blk         Latency         Size           1 <ul> <li>Direct Mapping</li> <li>LRU</li> <li>32</li> <li>1</li> <li>4</li> <li>0</li> <li>1024 B</li> </ul> 1024 B     1020 B     1020 B     1024 B                                                                                                                                                                                                                            | C + C - F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 00000  |                           |         |            |         |        |            |            |          |                |          |              |                       |

| 1 <ul> <li>Direct Mapping</li> <li>LRU</li> <li>32</li> <li>1</li> <li>4</li> <li>0</li> <li>1024 B</li> <li>2</li> <li>Set Associative</li> <li>LRU</li> <li>128</li> <li>1</li> <li>4</li> <li>20</li> <li>4 Kb</li> <li>4</li> <li>4</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                | 1 <ul> <li>Direct Mapping</li> <li>LRU</li> <li>32</li> <li>1</li> <li>4</li> <li>0</li> <li>1024 B</li> <li>2</li> <li>Set Associative</li> <li>LRU</li> <li>128</li> <li>1</li> <li>4</li> <li>20</li> <li>4 Ko</li> </ul> <li>4</li>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | gurati |                           |         | -          | 90-92   |        |            |            |          |                |          |              |                       |

| 2 • Set Associative • LRU • 128 • 1 • 4 • 20 4 Hb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2 • Set Associative • LRU • 128 • 1 • 4 • 20 4 Kb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1_1    |                           |         | 8-         | 1       | 100000 |            |            |          | 1.1.5.4.50.715 |          | -            |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <pre></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -      | Contraction of the second | -       |            |         | -      |            |            |          |                |          | 1991         | and the second second |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        | Set Associati             | ve      | LUD        |         | 120    |            | 1          |          | 4              |          | 20           | 4 10                  |

| Add Cache Level Delete Cache Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Add Cache Level Delete Cache Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |                           |         |            |         | ,      | Π.         |            |          |                |          |              |                       |

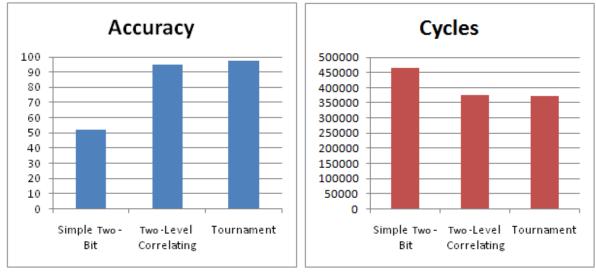

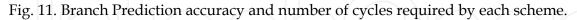

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |                           |         |            |         |        |            | ſ          | Add (    | Cache L        | .evel    | Delete       | Cache Level           |