# We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

6,900

186,000

200M

Downloads

154

Countries delivered to

Our authors are among the

TOP 1%

most cited scientists

12.2%

Contributors from top 500 universities

#### WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected.

For more information visit www.intechopen.com

# Low-Voltage Fully Differential CMOS Switched-Capacitor Amplifiers

Tsung-Sum Lee National Yunlin University of Science and Technology Taiwan (R.O.C.)

# 1. Introduction

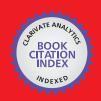

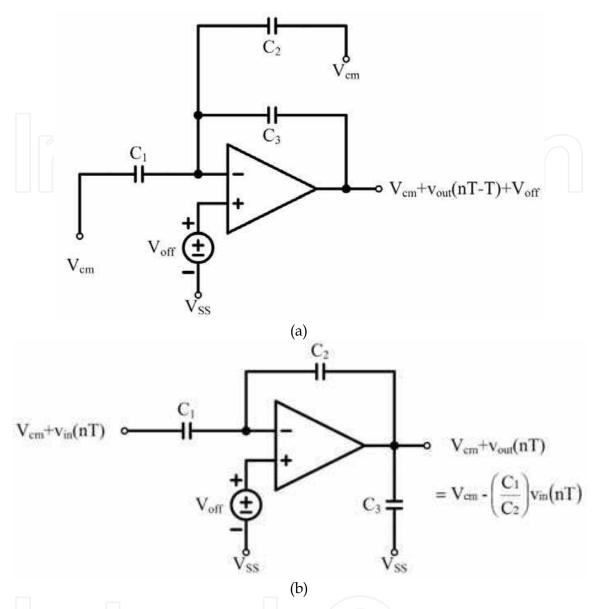

Analog signal amplification in discrete-time system can be performed by switched-capacitor amplifiers (Martin et al., 1987). Switched-capacitor amplifier has been used in the design of digital-to-analog converter (Yang & Martin, 1989). The schematic for the switched-capacitor amplifier is shown in Figure 1.

Fig. 1. A differential-to-single-ended CMOS switched-capacitor amplifier. Depending on the input-stage clock signals, the amplifier can be either noninverting (as shown) or inverting (input-stage clocks shown in parentheses).

Source: Advances in Solid State Circuits Technologies, Book edited by: Paul K. Chu, ISBN 978-953-307-086-5, pp. 446, April 2010, INTECH, Croatia, downloaded from SCIYO.COM

Assuming an infinite op amp gain, the output voltage at end of  $\phi_2$  is given by

$$V_{out}(nT) = \frac{C_1}{C_2} V_{in}(nT - \frac{T}{2}), \qquad (1)$$

irrespective of the op amp offset voltage. If the clock waveforms shown in parentheses are used, then an inverting function is realized, and

$$V_{out}(nT) = -\frac{C_1}{C_2} V_{in}(nT), \qquad (2)$$

again independent of the op amp input offset voltage. During the reset phase  $(\phi_1)$ ,  $C_3$  is connected in feedback around the op amp which causes the output change only by the op amp input offset voltage. The switches are realized as CMOS transmission gate. For low supply voltages, a conductance gap begins to appear around the middle of the supply range (Crols & Steyaert, 1994). This means that under low-voltage operation, this configuration no longer works. Existing solutions of low-voltage operation of switched-capacitor circuits include using low threshold voltage process (Matsuya & Yamada, 1994), switched-opamp technique (Baschirotto & Castello, 1997; Cheung et al., 2001; Cheung et al., 2002; Cheung et al., 2003; Crols & Steyaert, 1994; Peluso et al., 1997; Peluso et al., 1998; Sauerbrey et al., 2002; Waltari & Halonen, 2001; Wu et al., 2007), opamp-reset switching technique (Chang, & Moon, 2003; Keskin et al., 2002; Wang &. Embabi, 2003), voltage multiplier (charge pump) technique (Nicollini et al., 1996; Rombouts et al., 2001), clock multiplier (clock booster) technique (Au & Leung, 1997; Rabii & Wooley, 1997), and bootstrapping switch technique (Abo & Gray, 1999; Dessouky & Kaiser, 2001; Park et al., 2004). First, the use of lowthreshold transistors involves special and high-cost technology (Matsuya & Yamada, 1994). The switched-opamp technique (Baschirotto & Castello, 1997; Cheung et al., 2001; Cheung et al., 2002; Cheung et al., 2003; Crols & Steyaert, 1994; Peluso et al., 1997; Peluso et al., 1998; Sauerbrey et al., 2002; Waltari & Halonen, 2001; Wu et al., 2007) and opamp-reset switching technique (Chang, & Moon, 2003; Keskin et al., 2002; Wang &. Embabi, 2003) can only be applicable to filters, delta-sigma modulators, and pipelined analog-to-digital converters. The main limitations of voltage multiplier (charge pump) technique (Nicollini et al., 1996; Rombouts et al., 2001) regards: the gate-oxide breakdown reliability, the need to supply a dc current to the op amps from the multiplied supply (this necessitates the use of an external capacitor, with additional cost), and the conversion efficiency of the charge pump (which is lower than 100%). The clock multiplier (clock booster) technique (Au & Leung, 1997; Rabii & Wooley, 1997) suffers from the technology limitation associated with the gate oxide breakdown. Device reliability can be assured in the bootstrapped switch technique (Abo & Gray, 1999; Dessouky & Kaiser, 2001; Park et al., 2004), owing to keeping the terminal-toterminal voltages of the MOSFET devices within the rated operating supply voltage of the technology. The bootstrapped switch provides a small, nearly constant input resistance. The switch linearity is also improved, and signal-dependent charge injections is reduced.

To improve the overall linearity, minimize the effect of common-mode interference and noise, the fully differential approach has obtained wider acceptance for accurate and/or high-speed signal processing. The switched-capacitor amplifier in (Martin et al., 1987) is a differential-to-single-ended design. A fully differential switched-capacitor amplifier using series compensation MOSFET capacitors has been presented in (Yoshizawa et al., 1999).

However its operating voltage is ±2.5-V. Consequently there is an increasing demand to extend these improvements to this circuit.

This chapter describes the design of two 1V fully differential CMOS switched-capacitor amplifiers in a standard CMOS technology using improved bootstrapped switches. In section 2, the circuit realization of these two switched-capacitor amplifiers is addressed. In section 3 the circuit design of low-voltage building blocks is described. Experimental results are presented in section 4 to support the ideas put forth in paper. Finally conclusion is given.

# 2. Circuit Description

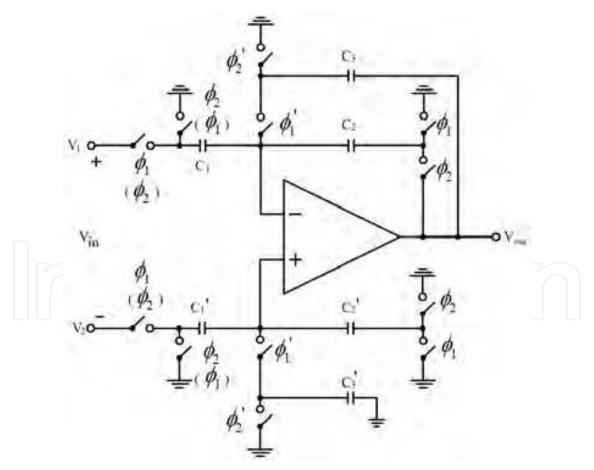

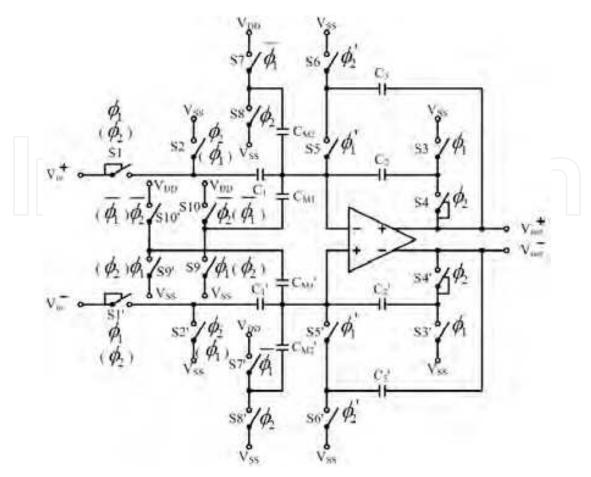

Fig. 2. First low-voltage fully differential CMOS switched-capacitor amplifier. Depending on the input-stage clock signals, the amplifier can be either noninverting (as shown) or inverting (input-stage clocks shown in parentheses).

Figure 2 shows the first low-voltage fully differential CMOS switched-capacitor amplifier based on improved bootstrapped switches described in section 3.2, where switches S1-S4 and S1'-S4' are matched improved bootstrapped switch pairs and switches S5-S6 and S5'-S6' are NMOS matched switch pairs. In order to minimize the number of improved bootstrapped switches, two analog reference voltages are used:  $V_{\rm SS}$  at the op amp input where a normal NMOS switch can be used to switch the lowest supply voltage, and a  $\frac{V_{\rm DD} + V_{\rm SS}}{2}$  common-mode voltage at the op amp output and the circuit input to maximize

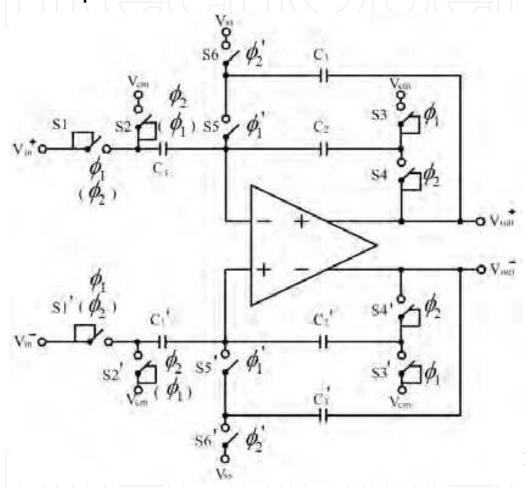

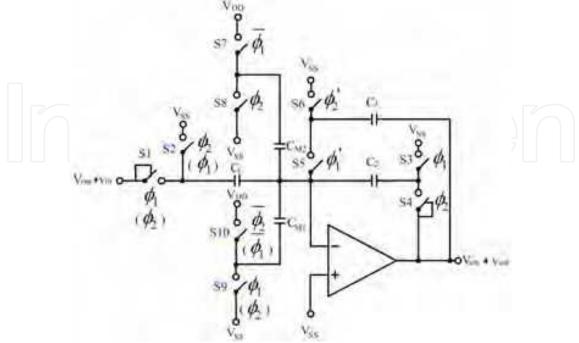

the signal swing. The improved bootstrapped switch is used to switch signals at this voltage level. Figure 3 is the single-ended version of Figure 2.

Fig. 3. Single-ended version of Fig. 2.

To see how this circuit operates, consider the inverting circuit during the reset phase ( $\phi_1$ ) and during valid output phase ( $\phi_2$ ), as shown in Figure 4. Then based on charge conservation principle we can write:

$$\begin{split} C_{1}(V_{SS}+V_{off}-V_{cm})+C_{2}(V_{SS}+V_{off}-V_{cm})\\ =C_{1}[V_{SS}+V_{off}-V_{cm}-v_{in}(nT)]+C_{2}[V_{SS}+V_{off}-V_{cm}-v_{out}(nT)]\;,\\ \text{or}\;\;v_{out}(nT)=-\frac{C_{1}}{C_{2}}v_{in}(nT)\;. \end{split} \tag{3}$$

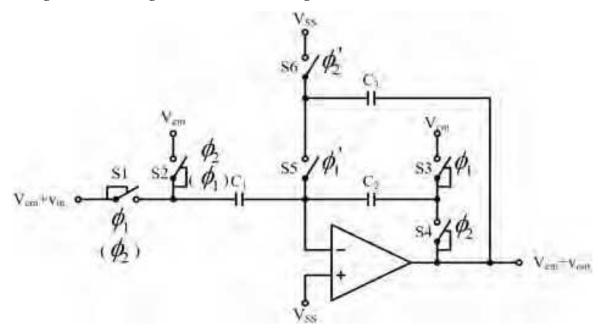

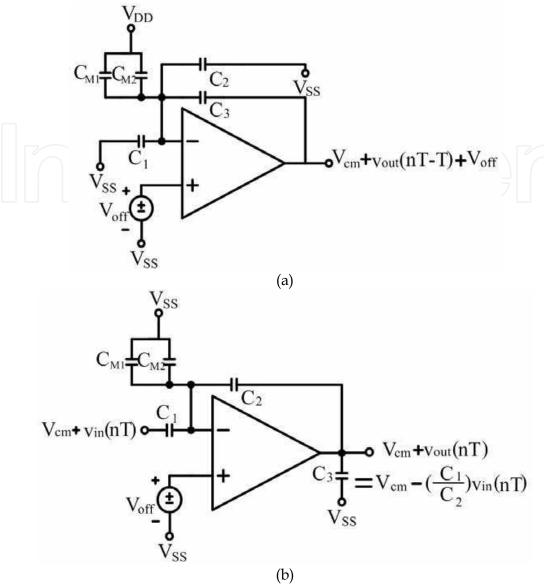

It should be noted that the clock waveforms with the primed superscripts change before the nonprimed waveforms in order to reduce nonlinearities due to charge injection. Another technique to further reduce the number of improved bootstrapped switches is shown in Figure 5, where switches S1 and S4 and S1' and S4' are matched improved bootstrapped switch pairs. Those switches connected to  $V_{SS}$  are realized with NMOS transistors, while those switches connected to  $V_{DD}$  are realized with PMOS transistors. In Figure 5 a single reference voltage at  $V_{SS}$  is used. However, the signal still varies around  $\frac{V_{DD} + V_{SS}}{2}$  at the circuit input as well as at the op amp output to preserve the maximum swing. The difference between the two reference voltages is compensated by injecting a fixed amount of charge at the op amp input using extra capacitor pairs  $C_{M1} = \frac{C_1}{2}$  and  $C_{M2} = \frac{C_2}{2}$  ( $C'_{M1} = \frac{C'_1}{2}$  and  $C'_{M2} = \frac{C'_2}{2}$ ) switching between  $V_{DD}$  and  $V_{SS}$  (Baschirotto & Castello, 1997). Figure 6 is the single-ended version of Figure 5.

Fig. 4. Single-ended CMOS switched-capacitor amplifier, (a) during reset phase ( $\phi_1$ ), (b) during valid output phase ( $\phi_2$ ).

To see how this circuit operates, consider the inverting circuit during the reset phase ( $\phi_1$ ) and during valid output phase ( $\phi_2$ ), as shown in Figure 7.

Then based on charge conservation principle we can write:

$$C_{1}(V_{SS} + V_{off} - V_{SS}) + C_{2}(V_{SS} + V_{off} - V_{SS}) + (C_{M1} + C_{M2})(V_{SS} + V_{off} - V_{DD})$$

$$= C_{1}[V_{SS} + V_{off} - V_{cm} - v_{in}(nT)] + C_{2}[V_{SS} + V_{off} - V_{cm} - v_{out}(nT)]$$

$$+ (C_{M1} + C_{M2})(V_{SS} + V_{off} - V_{SS})$$

or  $v_{out}(nT) = -\frac{C_{1}}{C_{2}}v_{in}(nT)$ . (4)

Fig. 5. Second low-voltage fully differential CMOS switched-capacitor amplifier. Depending on the input-stage clock signals, the amplifier can be either noninverting (as shown) or inverting (input-stage clocks shown in parentheses).

Fig. 6. Single-ended version of Fig. 5.

Fig. 7. Single-ended CMOS switched-capacitor amplifier, (a) during reset phase ( $\phi_1$ ), (b) during valid output phase ( $\phi_2$ ).

# 3. Low-voltage building blocks

In this section, the low-voltage circuit building blocks used in the two fully differential CMOS switched-capacitor amplifiers are discussed

#### **3.1 Op Amp**

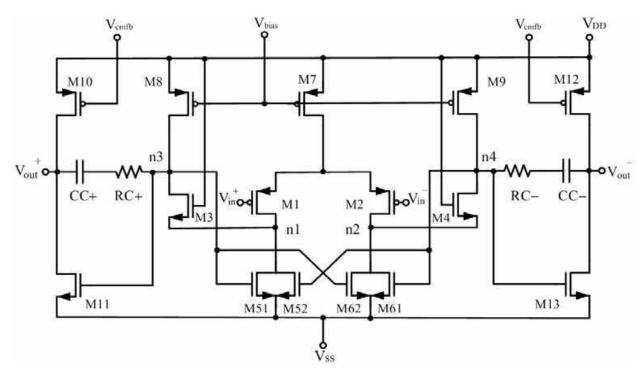

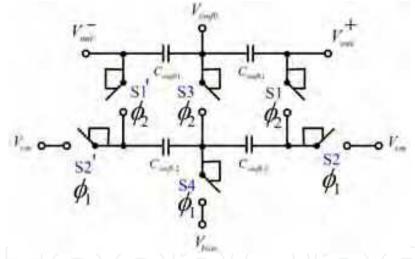

Figure 8 shows the used op amp. It is based on a fully differential folded-cascode p-type two-stage Miller-compensated configuration. The second stage is a common-source amplifier with active load which also allows a large output swing. In order to avoid the common-mode feedback (CMFB) circuit for the first stage, transistors *M51*, *M52*, *M61*, and *M62* are used, which is similar to (Waltari & Halonen, 1998). For the second stage, a simple passive switched-capacitor CMFB circuit, shown in Figure 9, is used. The improved bootstrapped switches are used to connect and disconnect the common-mode sensing capacitor.

Fig. 8. Low-voltage op amp.

Fig. 9. Common-mode feedback circuit for the low-voltage op amp.

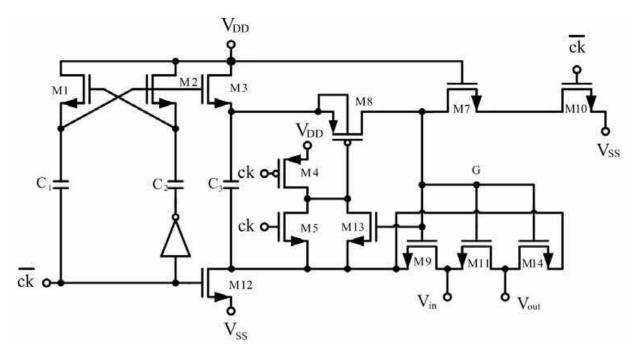

# 3.2 Improved bootstrapped switch

The improved bootstrapped switch shown in Figure 10 is utilized in the proposed circuit. The circuitry is improved version of that presented in (Abo & Gray, 1999). In the circuit presented in (Abo & Gray, 1999), the voltage at the drain side of the main switch M11 must be always higher than that at the source side at the switching moment to prevent the gatedrain voltage from exceeding  $V_{DD}$  during the turn-on transient. In order to overcome this limitation, an additional transistor M14 has been added on the drain side, such that the switch M11 becomes completely symmetrical. This bootstrapping circuit thus allows switch operation (transistor M11) from rail-to-rail while limiting all gate-source/drain voltages to  $V_{DD}$  avoiding any oxide overstress.

Fig. 10. Improved bootstrapped switch.

# 4. Experimental results

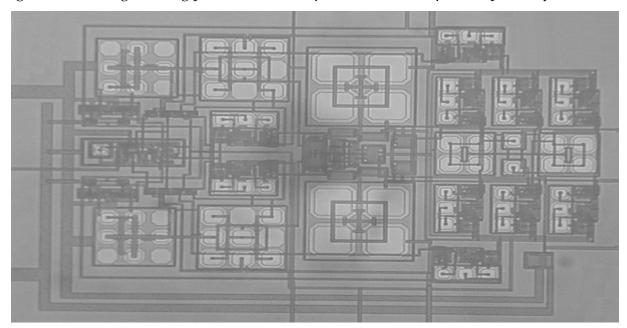

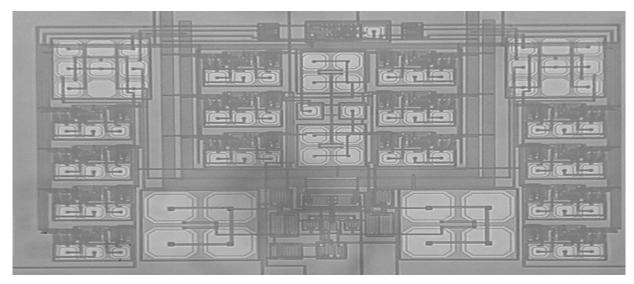

Based on the principles presented earlier, we have designed two 1-V fully differential CMOS switched-capacitor amplifiers. These two switched-capacitor amplifiers were operated with  $\pm 0.5$ -V. The capacitor sizes used were  $C_1$  =1.25-pF,  $C_2$  =0.25-pF, and  $C_3$  =0.25-pF, for a nominal gain of -5. The circuits of Figure 2 and Figure 5 were fabricated using a TSMC 0.35- $\mu$ m double-poly four-metal CMOS technology. Figure 11 and Figure 12 show the photomicrographs of Figure 2 and Figure 5, respectively. The chip areas of Figure 2 and Figure 5 excluding bonding pads are 414×278- $\mu$ m² and 460×330- $\mu$ m², respectively.

Fig. 11. Photomicrograph of Fig. 2.

Fig. 12. Photomicrograph of Fig. 5.

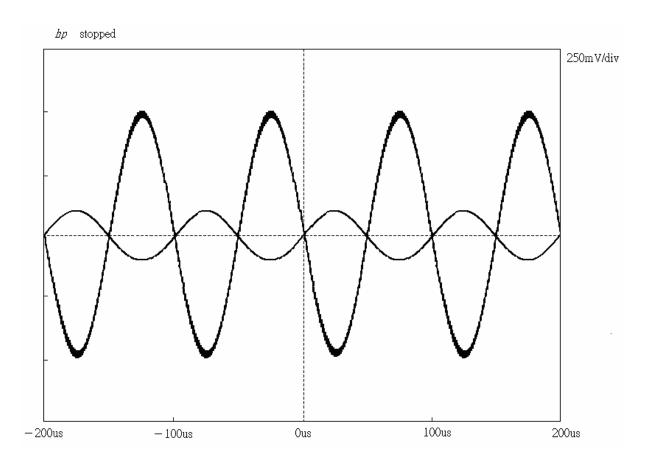

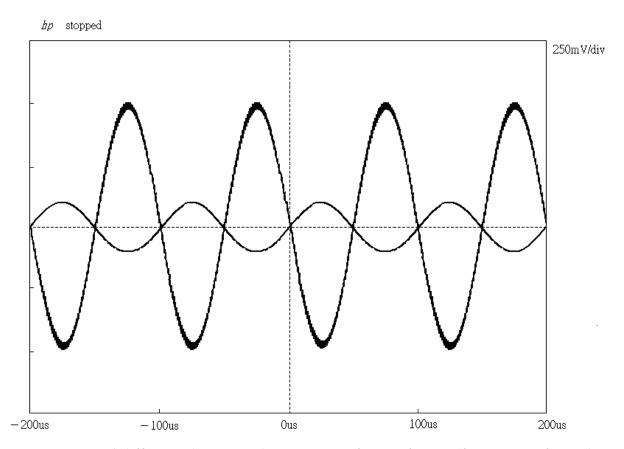

Two figures of the measured input/output waveforms for 0.2V peak-to-peak sinusoidal differential input signal are shown in Fig. 13 and Fig. 14, respectively. The input signal was at 10kHz whereas the clock signal was at 1MHz. It can be seen that the gain is very close to the nominal value of -5.

Fig. 13. Measured differential input and output waveforms of Fig. 2 ( $f_{clk}$ =1-MHz,  $f_{in}$ =10-kHz, sinusoidal differential input voltage=0.2- $V_{pp}$ ).

Fig. 14. Measured differential input and output waveforms of Fig. 5 ( $f_{clk}$ =1-MHz,  $f_{in}$ =10-kHz, sinusoidal differential input voltage=0.2- $V_{pp}$ )

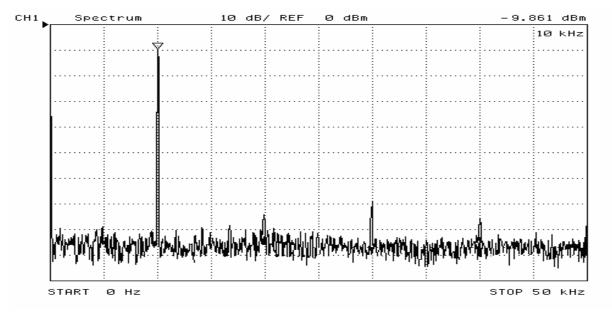

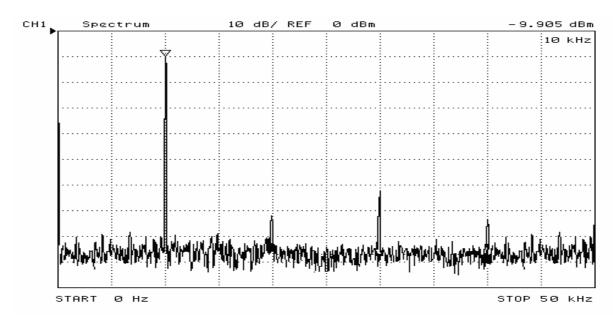

Fig. 15 and Fig. 16 show the resulting output spectrum. As shown in Fig. 15 and Fig. 16, the even-order harmonics have been largely attenuated by the fully differential topology and 59dB and 52dB spurious-free dynamic range (SFDR) are exhibited, respectively. The circuits of Fig. 2 and Fig. 5 dissipate 206.5 $\mu$ W and 206.6 $\mu$ W, respectively with a 1V power supply.

Fig. 15. Measured output spectrum of Fig. 2.

Fig. 16. Measured output spectrum of Fig. 5.

#### 5. Conclusion

Two fully differential CMOS 1-V switched-capacitor amplifiers have been described. Rail-torail operation of improved bootstrapped switches allows very low voltage robust switchedcapacitor designs in standard CMOS technologies while avoiding transistor gate oxide overstress. The circuits have been fabricated and all aspects of their performance have been confirmed.

## 6. References

- Abo , A. M. & Gray , P. R. (1999). A 1.5-V, 10-bit, 14.3-MS/s CMOS pipeline analog-to-digital converter, *IEEE J Solid-State Circuits*, May , vol. 34, pp. 599-606 ,ISSN: 0018-9200.

- Au, S. & Leung, B. H., (1997). A 1.95-V, 0.34-mW, 12-b sigma-delta modulator stabilized by local feedback loops, *IEEE J Solid-State Circuits*, March, vol. 32, pp. 321-328, ISSN: 0018-9200.

- Baschirotto, A. & Castello, R. (1997). A 1-V 1.8-MHz CMOS switched-opamp SC filter with rail-to-rail output swing, *IEEE J Solid-State Circuits*, December, vol. 32, pp. 1979-1986, ISSN: 0018-9200.

- Chang, D. Y. & Moon, U.-K. (2003). A 1.4-V 10-bit 25-MS/s pipelined ADC using opampreset switching technique, *IEEE J Solid-State Circuits*, August, vol. 38, pp. 1401-1404, ISSN: 0018-9200.

- Cheung, V. S.-L. et al. (2001). A 1-V CMOS switched-opamp switched-capacitor pseudo-2-path filter, *IEEE J Solid-State Circuits*, Jan. 2001, vol. 36, pp. 14-22, ISSN: 0018-9200.

- Cheung, V. S. L. et al. (2002). A 1-V 10.7-MHz switched-opamp bandpass ΣΔ modulator using double-sampling finite-gain-compensation technique, *IEEE J Solid-State Circuits*, October, vol. 37, pp. 1215-1225, ISSN: 0018-9200.

- Cheung V. S.-L et al. (2003). A 1-V 3.5-mW CMOS switched-opamp quadrature IF circuitry for Bluetooth receivers, *IEEE J Solid-State Circuits*, May., vol. 38, pp. 805-816, ISSN: 0018-9200.

- Crols, J. & Steyaert, M., (1994). Switched-opamp: an approach to realize full CMOS switched-capacitor circuits at very low power supply voltage, *IEEE J Solid-State Circuits*, August, vol. 29, pp. 936-942, ISSN: 0018-9200.

- Dessouky, M. & Kaiser, A. (2001). Very low-voltage digital-audio ΣΔ modulator with 88-dB dynamic range using local switch bootstrapping, *IEEE J Solid-State Circuits*, March, vol. 36, pp. 349-355, ISSN: 0018-9200.

- Keskin, M. et al. (2002). A 1-V 10-MHz Clock-Rate 13-Bit CMOS ΣΔ modulator using unity-gain-reset opamps, *IEEE J Solid-State Circuits*, July, vol. 37, pp. 817-824, ISSN: 0018-9200.

- Martin, K. et al. (1987). A differential switched-capacitor amplifier, *IEEE J Solid-State Circuits*, February, vol. 22, pp. 104-106, ISSN: 0018-9200.

- Matsuya, Y. & Yamada, J. (1994). 1-V power supply, low-power consumption A/D conversion technique with swing-suppression noise shaping, *IEEE J Solid-State Circuits*, December, vol. 29, pp. 1524-1530, ISSN: 0018-9200.

- Nicollini,G. A. et al. (1996). A -80dB THD, 4-Vpp switched capacitor filter for 1.5-V battery-operated systems, *IEEE J Solid-State Circuits*, August, vol. 31, pp. 1214-1219, ISSN: 0018-9200.

- Park, J.-B. et al. (2004). A 10-b 150-MSample/s 1.8-V 123-mW CMOS A/D converter with 400-MHz input bandwidth, *IEEE J Solid-State Circuits*, August, vol. 39, pp. 1335-1337, ISSN: 0018-9200.

- Peluso, V. et al. (1997), A 1.5-V 100-μW ΣΔ modulator with 12-b dynamic range using the switched-opamp technique, *IEEE J Solid-State Circuits*, July, vol. 32, pp. 943-952, ISSN: 0018-9200.

- Peluso, V. et al. (1998). A 900-mV low-power ΣΔ A/D converter with 77-dB dynamic range," *IEEE J Solid-State Circuits*, December, vol. 33, pp. 1887-1897, ISSN: 0018-9200.

- Rabii, S. & Wooley, B. A. (1997). A 1.8-V digital-audio sigma-delta modulator in 0.8-μm CMOS, *IEEE J Solid-State Circuits*, June, vol. 32, pp. 783-796, ISSN: 0018-9200.

- Rombouts, P. et al. (2001). A 13.5-b 1.2-V micropower extended counting A/D converter, "IEEE J Solid-State Circuits, February, vol. 36, pp. 176-183, ISSN: 0018-9200.

- Sauerbrey, J. et al. (2002). A 0.7-V MOSFET-only switched-opamp ΣΔ modulators in standard digital CMOS technology, *IEEE J Solid-State Circuits*, December, vol. 37, pp. 1662-1669, ISSN: 0018-9200.

- Waltari, M. & Halonen, K. A. I. (2001). 1-V 9-Bit pipelined switched-opamp ADC," *IEEE J Solid-State Circuits*, January, vol. 36, pp. 129-134, ISSN: 0018-9200.

- Waltari, M. & Halonen, K. (1998). Fully differential switched opamp with enhanced common-mode feedback, *Electron. Lett.*, November, vol. 34, no. 23, pp. 2181-2182, ISSN:0013-5194..

- Wang, L. &. Embabi S. H. K. (2003). Low-voltage high-speed switched-capacitor circuits without voltage bootstrapper, *IEEE J Solid-State Circuits*, August, vol. 38, pp. 1411-1415, ISSN: 0013-5194.

- Wu, P. Y. et al. (2007). A 1-V 100-MHS/s 8-bit CMOS Switched-Opamp Pipelined ADC Using Loading-Free Architecture, *IEEE J Solid-State Circuits*, April, vol. 42, pp. 730-738, ISSN:0013-5194.

- Yang, J. W. & Martin, K. W. (1989). High-resolution low-power D/A converter, *IEEE J Solid-State Circuits*, October, vol. 24, pp. 1458-1461, ISSN: 0013-5194.

- Yoshizawa, H. et al. (1999). MOSFET-only switched-capacitor circuits in digital CMOS technology," *IEEE J Solid-State Circuits*, June, vol. 34, pp. 734-747, ISSN: 0013-5194.

#### **Advances in Solid State Circuit Technologies**

Edited by Paul K Chu

ISBN 978-953-307-086-5

Hard cover, 446 pages

Publisher InTech

Published online 01, April, 2010

Published in print edition April, 2010

This book brings together contributions from experts in the fields to describe the current status of important topics in solid-state circuit technologies. It consists of 20 chapters which are grouped under the following categories: general information, circuits and devices, materials, and characterization techniques. These chapters have been written by renowned experts in the respective fields making this book valuable to the integrated circuits and materials science communities. It is intended for a diverse readership including electrical engineers and material scientists in the industry and academic institutions. Readers will be able to familiarize themselves with the latest technologies in the various fields.

### How to reference

In order to correctly reference this scholarly work, feel free to copy and paste the following:

Tsung-Sum Lee (2010). Low-Voltage Fully Differential CMOS Switched-Capacitor Amplifiers, Advances in Solid State Circuit Technologies, Paul K Chu (Ed.), ISBN: 978-953-307-086-5, InTech, Available from: http://www.intechopen.com/books/advances-in-solid-state-circuit-technologies/low-voltage-fully-differential-cmos-switched-capacitor-amplifiers

# INTECH open science | open minds

#### InTech Europe

University Campus STeP Ri Slavka Krautzeka 83/A 51000 Rijeka, Croatia Phone: +385 (51) 770 447

Fax: +385 (51) 686 166 www.intechopen.com

### InTech China

Unit 405, Office Block, Hotel Equatorial Shanghai No.65, Yan An Road (West), Shanghai, 200040, China 中国上海市延安西路65号上海国际贵都大饭店办公楼405单元

Phone: +86-21-62489820 Fax: +86-21-62489821 © 2010 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the <u>Creative Commons Attribution-NonCommercial-ShareAlike-3.0 License</u>, which permits use, distribution and reproduction for non-commercial purposes, provided the original is properly cited and derivative works building on this content are distributed under the same license.