We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

186,000

200M

Our authors are among the

TOP 1% most cited scientists

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

### Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

## Chapter Industrial Silicon Solar Cells

Mehul C. Raval and Sukumar Madugula Reddy

### Abstract

The chapter will introduce industrial silicon solar cell manufacturing technologies with its current status. Commercial p-type and high efficiency n-type solar cell structures will be discussed and compared so that the reader can get a head-start in industrial solar cells. A brief over-view of various process steps from texturing to screen-printed metallization is presented. Texturing processes for mono-crystalline and multi-crystalline silicon wafers have been reviewed with the latest processes. An over-view of the thermal processes of diffusion and anti-reflective coating deposition has been presented. The well-established screen-printing process for solar cell metallization is introduced with the fast-firing step for sintering of the contacts. I-V testing of solar cells with various parameters for solar cell characterization is introduced. Latest developments in various processes and equipment manufacturing are also discussed along with the expected future trends.

**Keywords:** silicon, solar cells, manufacturing, multi-crystalline, mono-crystalline, texturing

#### 1. Introduction

Photovoltaics are an important renewable energy source which has grown rapidly from 8 GW in 2007 to 400 GW in 2017 [1]. Along with the increasing demand, the PV system costing has also dropped significantly from 35.7  $W_p$  in 1980 to 0.34  $W_p$  in 2017 accelerating its adoption [2]. Silicon (Si) which is an important material of the microelectronics industry has also been the widely used bulk material of solar cells since the 1950s with a market share of >90% [2]. The chapter will introduce the typical steps for manufacturing commercial silicon solar cells. A brief history of solar cells and over-view of the type of silicon substrates along with the different solar cell architecture will be introduced in Sections 2 and 3. Subsequently, the wet-chemistry and high temperature steps used in fabrication will be described in Sections 4 and 5. Section 6 will discuss about the metallization process along with typical characterization parameters for commercial solar cells. Finally, future roadmap and expected trends will be discussed in the concluding section.

#### 2. Evolution of solar cells

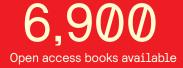

The 'photovoltaic effect' literally means generation of a voltage upon exposure to light. The phenomenon was first observed by the French physicist Edmund Becquerel on an electrochemical cell in 1839, while it was observed by British scientists W.G. Adams and R.E. Day on a solid-state device made of selenium in 1876 [3]. From the 1950s onwards, there was rapid progress in the performance of commercial solar cells from <1% to >23% [2] and silicon has been the 'work-horse' of the photovoltaic industry since then. The evolution of silicon solar cells is shown in **Figure 1**.

The first silicon solar cells demonstrated by Russell Ohl of Bell Laboratories during 1940s were based on natural junctions formed from impurity segregation during the recrystallization process [3]. The cells had an efficiency of <1% due to lack of control over the junction location and the quality of the silicon material. The nomenclature for naming the regions (p-type: side which is illumination and n-type: other side) given by Ohl are since then being used for the solar cell naming conventions.

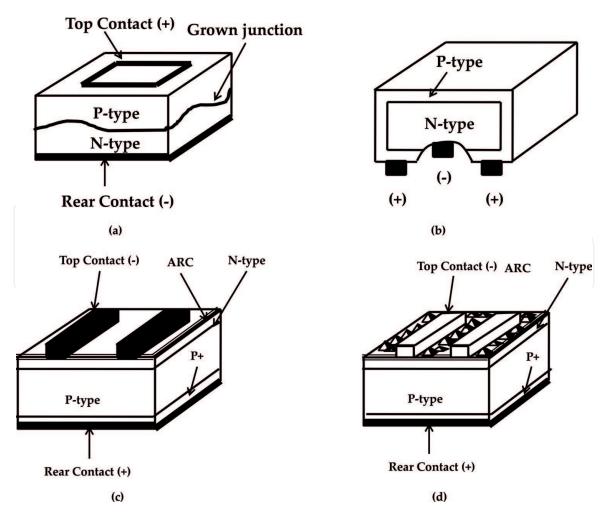

During the 1950s, there was rapid development in the high-temperature diffusion process for dopants in silicon. Person, Fuller and Chaplin of Bell Laboratories demonstrated a 4.5% efficient solar cell with lithium-based doping, which improved to 6% with boron diffusion. The solar cell had a 'wrap-up' around structure (**Figure 1(b)**) with both contacts on back side to avoid shading losses, but led to higher resistive losses due to the wrap-around structure. By 1960, the cell structure evolved to as shown in **Figure 1(c)**. Since the application was for space explorations, high resistivity substrate of 10  $\Omega$  cm was used to have maximum radiation resistance. Vacuum evaporated contacts were used on both sides, while a silicon monoxide coating was used as an anti-reflective coating (ARC) on the front-side (FS) [3].

In early 1970s it was found that having sintered aluminum on the rear-side improved the cell performance by forming a heavily doped interface known as the 'back-surface field (Al-BSF)' and gettering of the impurities [3]. The Al-BSF reduces recombination of the carriers on the rear-side and hence improves the voltage and the long-wavelength spectral response. Implementation of finer and closely

#### Figure 1.

Evolution of silicon solar cells. (a) 1941: Solar cell reported with grown-in junction, (b) 1954: Solar cell p-n junction formed with dopant diffusion, (c) 1970: Violet cell with Aluminum back-surface field, (d) 1974: Black cell with chemically textured surface [3].

spaced fingers reduced the requirement on the junction doping and eliminated the dead layer. An ARC of titanium dioxide  $(TiO_x)$  was used and its thickness was selected to reduce the reflection for shorter wavelengths and gave a violet appearance to the solar cells. Further improvement was made by texturing the wafers using anisotropic etching of (100) wafers to expose the (111) surfaces. The texturing led to improved light-trapping and gave the cells a dark velvet appearance. The improved cell architecture is shown in **Figure 1(d)**. In 1976, Rittner and Arndt demonstrated terrestrial solar cells with efficiencies approaching 17% [3].

The passivated emitter solar cell (PESC) achieved a milestone of 20% efficiency in 1984–1986. The metal/silicon contact area was only 0.3% in PESC cells, while a double layer ARC of ZnS/MgF<sub>2</sub> was used in both cell structures. In 1994, passivated emitter rear locally diffused (PERL) cell with an efficiency of 24% were demonstrated [3]. As compared to the PESC cell, the PERL cell had inverted pyramids on FS for better light-trapping and oxide-based passivation on both sides. Oxide passivation layer on the rear-side also improved the internal reflectance of the long wavelength and hence the spectrum response.

In addition to the evolving solar cell architectures, there has also been continuous development in the manufacturing domain in terms of increased throughput, improved process-steps and reduced costs. A brief over-view of the manufacturing of Si substrates and various types of solar cells is given in the next section.

#### 3. Commercial silicon solar cell technologies

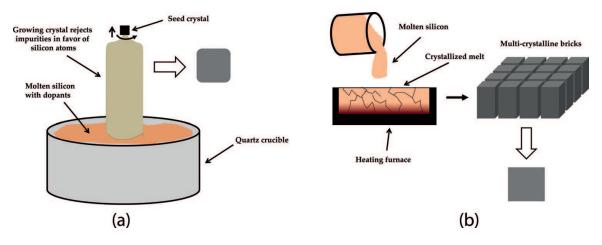

Si is the second most abundant material on earth after oxygen and has been widely used in the semiconductor industry. Metallurgical grade silicon (Mg-Si) of 98% purity is obtained by heating quartz (SiO<sub>2</sub>) with carbon at high temperatures of 1,500-2,000 [4]. Mg-Si is further purified to obtain solar grade silicon chunks of 99.99% purity. The refined solar grade Si chunks are then processed further to obtain mono-crystalline and multi-crystalline forms of Si ingots, which are a large mass of silicon. In mono-crystalline Si, the atoms are arranged in the same crystal orientation throughout the material. For solar cells, (100) orientation is preferred as it can be easily textured to reduce the surface reflection [5]. Multi-crystalline Si, as the name suggest has multiple grains of Si material with different orientations, unlike the mono-crystalline substrates. Mono-crystalline material have higher minority carrier lifetime compared to multi-crystalline Si and hence higher solar cell efficiencies for a given solar cell technology.

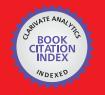

The Czochralski (Cz) method for making mono-crystalline Si ingots is illustrated in **Figure 2(a)**. High purity molten silicon with dopant is maintained above the melting point and then a seed crystal is pulled at a very slow rate to obtain an ingot of as large as 300 mm in diameter and 2 m in length [6]. The molten silicon can be doped with either p-type or n-type dopants to obtain the specific type of mono-crystalline Si ingot of up to 200 kg [2]. Wafers sawn from the ingots have circular edges and hence the shape is called a 'psuedo square'. Multi-crystalline silicon ingots are made by melting high purity Si and crystallizing them in a large crucible by directional solidification process [7] as demonstrated in **Figure 2(b)**. The process does not have a reference crystal orientation like the Cz process and hence forms silicon material of different orientations. Currently the multi-crystalline Si ingots weigh >800 kg [2] which are then cut into bricks and wafers are sawn further. Current size of mono-crystalline and multi-crystalline wafers for solar cell fabrication is 6 inch × 6 inch. The area of the mono-crystalline wafers will be little less due to the pseudo-square shape. The most widely used base material for making solar cells is boron doped p-type Si substrates. N-type Si substrates for also used

for making high efficiency solar cells, but have additional technical challenges like obtaining uniform doping along the ingot compared to p-type substrates.

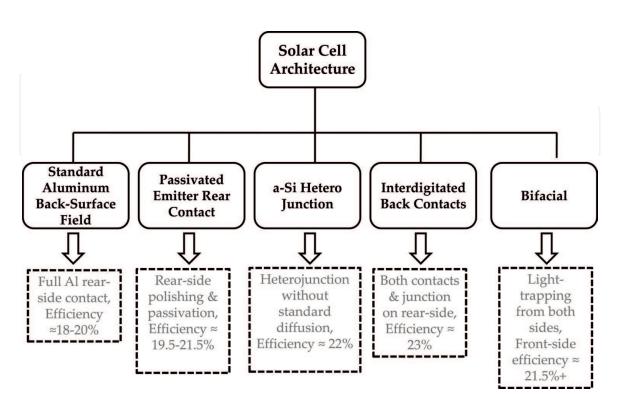

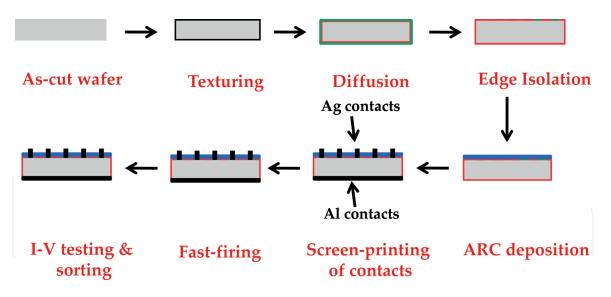

A broad classification of different types of solar cells along with efficiency ranges is shown in **Figure 3**. The standard aluminum back-surface field (Al-BSF) technology is one of the most common solar cell technology given its relatively simple manufacturing process. It is based on full rear-side (RS) Al deposition by screen-printing process and formation of a p<sup>+</sup> BSF which helps repel the electrons from the rear-side of p-type substrate and improve the cell performance. The manufacturing flow for Al-BSF solar cells is shown in **Figure 4**. The standard design of commercial solar cells is with grid-pattern FS and full area RS contacts.

The passivated emitter rear contact (PERC) solar cell improves on the Al-BSF architecture by addition of rear-side passivation layer to improve rear-side passivation and internal reflection. Aluminum-oxide is a suitable material for RS passivation with average solar cell efficiencies nearing 21% obtained in production [8]. An existing

Figure 2.

Illustration of (a) Cz process for mono-crystalline ingots and (b) directional solidification process for multicrystalline ingots.

**Figure 3.** Broad classification of different types of solar cell.

**Figure 4.** Manufacturing flow of Al-BSF solar cells.

Al-BSF solar cell line can be upgraded to PERC process by two additional tools (RS passivation layer deposition and laser for localized contact opening on the RS).

The remaining three cell architectures are mainly higher efficiency technologies based on n-type Si substrates. The a-Si heterojunction solar cell has a-Si layers on the FS and RS of n-type Si substrate to form 'heterojunctions' unlike the conventional high temperature diffusion-based p-n junction. Such technology allows processing at lower temperatures, but is very sensitive to the quality of the surface interfaces. a-Sibased heterojunction solar cell was commercially manufactured by Sanyo Electric, which is now taken over by Panasonic [9]. In the interdigitated back contact (IBC) solar cell design, both contacts are present on the rear-side eliminating the FS contact shading losses. Typically for IBC solar cells, the junction will also be located on the rear-side. One of the early manufacturers of the high efficiency n-type IBC solar cell is SunPower Corporation [10]. Bifacial cells, as the name suggests can capture light from both sides of the solar cells. This entails that the rear-side also has a grid-pattern contacts to enable light collection. An example of the bifacial technology is the BiSON solar cell developed and commercialized by ISC, Konstanz [11]. It should be noted that the indicated classification is not an exhaustive list of various other types of solar cell architectures which are in R&D phase, close to commercialization or already being manufactured. The subsequent sections will give an over-view of the process steps for manufacturing of Al-BSF solar cells.

#### 4. Wet-chemistry processes for solar cell fabrication

Wet-chemistry-based treatment is an important step in solar cell processing for saw damage removal (SDR) for the as-cut wafers, texturing of the surface to increase the absorption of incoming solar radiation and edge isolation after the diffusion process. As discussed in the previous section, there are mainly mono-crystalline and multi-crystalline silicon wafers used for fabrication of solar cells. The wet-chemistrybased processing for the respective types of wafers will be discussed ahead.

#### 4.1 Texturing of mono-crystalline silicon wafers

As indicated in Section 2, the development of solar cells started primarily with mono-crystalline wafers and hence employed well-established methods from the domain of microelectronics. Alkaline anisotropic etching based on KOH/NaOH

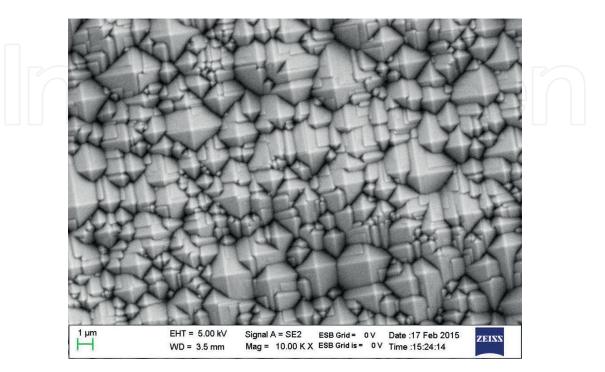

is used for pyramidal texturing of mono-crystalline wafers. An as-cut monocrystalline wafer has a weighted average reflectance of >30% (over wavelength of 300–1,200 nm) which reduces to 11–12% after the texturing process. Typical morphology of an alkaline textured surface is shown in **Figure 5**. The anisotropic etching solution etches the (100) surface of the wafers to expose the (111) faces which have a higher density of silicon atoms and hence a slower etch rate compared to the (100) faces. This results in formation of random pyramid structures which form an angle of 54.7° with respect to the wafer surface.

Typical parameters for the alkaline texturing process are shown in **Table 1**. It should be noted that the values of various parameters are indicative and are not to be taken as absolute as there are a variety of additive manufacturers in the market. Isopropyl alcohol (IPA) was initially used as an additive in the texturing solution, which is not involved in the etching reaction, but acts as a wetting agent to improve the homogeneity of texturing process by preventing the  $H_2$  bubbles (generated during the reaction) adhering to the silicon surface [12]. However by 2010, IPA was gradually replaced with alternative additives due to drawbacks like unstable concentration as the bath temperature is close to the boiling point of IPA (82.4°C), high costs, high consumption, health hazards and explosiveness [12]. Many groups have published development work to replace IPA with alternate additives to overcome the disadvantages of IPA, increase the process window and reduce the surface reflectance [12–16]. Additives also reduce the processing time to <10 minutes and increases the bath life to >100 runs.

The texturing process of the mono-crystalline wafers is typically performed in a 'batch' which implies that the wafers are loaded in a carrier with slots to hold the wafers (100 slots in a carrier) and then the batch is processed sequentially in baths for texturing, cleaning, treatment steps to remove the organic residue and metal contamination and drying the processed wafers. The carriers are typically coated with PVDF which has very good resistance to various chemicals, abrasion and mechanical wear and tear. Typical carrier for mono-crystalline wafers handling is shown in **Figure 6**. The batch texturing tool has dedicated baths for each step with dosing tanks for chemicals used in the bath. The tool processes many carriers simultaneously and can reach a throughput of >6,000 wafers/h with processing of four carriers at the same time.

**Figure 5.** *Typical surface morphology of an alkaline textured mono-crystalline wafer.*

| Process                  | KOH/IPA | KOH/additive<br><3 |  |  |

|--------------------------|---------|--------------------|--|--|

| КОН (%)                  | 3       |                    |  |  |

| IPA (%)                  | 6       | _                  |  |  |

| Additive (%)             | _       | <2                 |  |  |

| Process temperature [°C] | >80     | 70–100             |  |  |

| Pyramid size [µm]        | 5–12    | 2–7                |  |  |

| Process time [min]       | 30–40   | 5–10               |  |  |

| Organic content [wt%]    | 4-10    | <1.0               |  |  |

| Boiling point [°C]       | 83      | >100               |  |  |

| Bath lifetimes           | <15     | >100               |  |  |

#### Table 1.

Process parameters for IPA-based and additive-based alkaline texturing of mono-crystalline wafers.

**Figure 6.** *Carriers for loading wafers in the batch tool. Source: RCT solutions GmbH.*

#### 4.2 Texturing of multi-crystalline silicon wafers

Multi-crystalline wafers offer a cost advantage compared to the mono-crystalline wafers and hence have been more widely adopted. However, the alkaline chemistry used for texturing mono-crystalline wafers does not work well for multi-crystalline wafers due to the presence of different grain orientations. An alternative acidic chemistry based on HF and HNO<sub>3</sub> was developed to remove the saw damage and texture the multi-crystalline wafers simultaneously [17, 18]. The acidic solution-based texturing operates at temperatures below room temperature and hence leads to

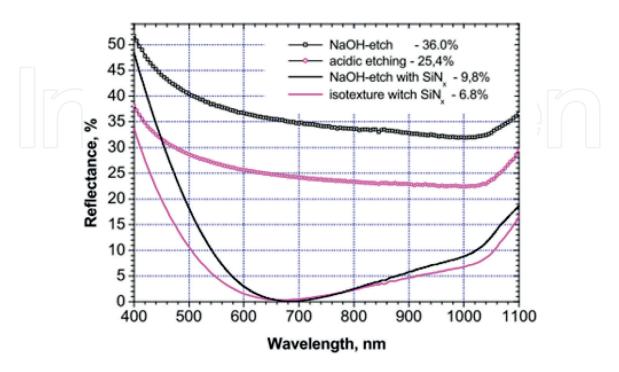

reduced reaction gas emission, little heat generation, higher stability of the etching solution and better control of the etch rate [18]. A comparison of alkaline texturing and acidic texturing process for multi-crystalline wafers is shown in **Figure 7**.

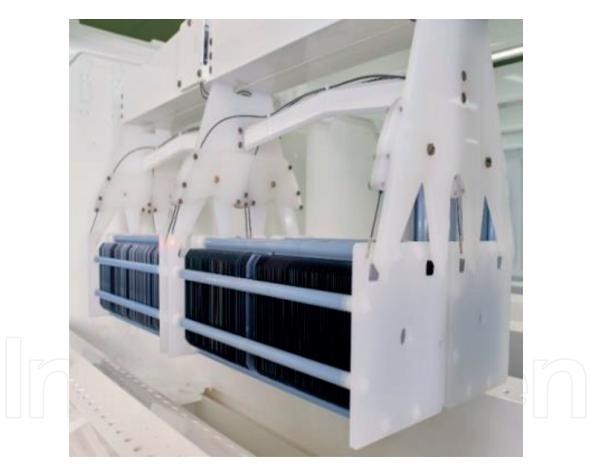

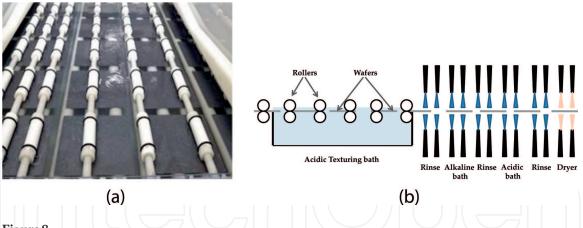

The acidic texturing process of multi-crystalline wafer can be done in significantly reduced time compared to the alkaline texturing process and hence can be implemented in an 'inline' configuration where the wafers are passed through rollers immersed in the etching bath. A representative image of an inline process along with the typical acidic texturing process is shown in **Figure 8**. For a five lane configuration, the inline tool can have a throughput of up to 4,000 wafers/h. It is important to note that the wafer surface facing down in the etching solution is textured better than the top-side and is the 'sunny-side' for further processing. The acidic texturing process leads to formation of porous silicon on the textured surface which absorbs light and also increases the surface recombination [18]. Hence the porous silicon is removed using a dilute alkaline solution. Subsequently, an acidic clean (HF + HCl) is performed to remove oxides and metal contamination from the wafer surfaces.

It is important to note that the acidic texturing process discussed above is suitable for the slurry-wire sawn (SWS) multi-crystalline wafers. In the past few years, diamond-wire sawing (DWS) process has replaced the slurry-wire-based cutting due to process and economic advantages [19]. The saw damage of the SWS multicrystalline wafers is more than the DWS wafers, which have deep straight grooves and a much more smoother surface than the slurry-wire sawn wafers [19]. The saw damage for the SWS wafers plays an important role for initiating the texturing process, which does not occur for the DWS wafers.

Various methods have been proposed to texture DWS multi-crystalline wafers and are summarized in **Table 2** [20]. By tuning the various methods, reflectance of close to 0% can be obtained and hence the term 'black silicon' has been used for the texturing process of DWS multi-crystalline wafers. RIE was the first method for making black silicon and uses sulfur hexaflouride (SF<sub>6</sub>) to react with Si and gases like Cl<sub>2</sub> and O<sub>2</sub> for passivating and limiting the reaction [20]. Recently, commercial multi PERC solar cells with average efficiency of 21.3% have been demonstrated with RIE-based

#### Figure 7.

Comparison of alkaline and acidic texturing for multi-crystalline wafers. Reflectance curves after deposition of SiN<sub>x</sub>:H are also showed for comparison [17].

Figure 8.

(a) Representative inline process with five lanes and (b) acidic texturing process flow for multi-crystalline wafers.

| Method                                      | Reagents                                                                                                                              | Mask                 | Catalyst | Minimum<br>reflectance (%) |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------|----------------------------|

| Reactive ion etching (RIE)                  | SF <sub>6</sub> /O <sub>2</sub> , SF <sub>6</sub> /Cl <sub>2</sub> /O <sub>2</sub> , SF <sub>6</sub> /O <sub>2</sub> /CH <sub>4</sub> | None                 | None     | 4.0                        |

| Plasma immersion ion<br>implantation (PIII) | SF <sub>6</sub> /O <sub>2</sub>                                                                                                       | None                 | None     | 1.8                        |

| Laser irradiation                           | CCl <sub>4</sub> , C <sub>2</sub> Cl <sub>3</sub> F <sub>3</sub> , SF <sub>6</sub> , Cl <sub>2</sub> , N <sub>2</sub> , air           | None                 | None     | 2.5                        |

| Plasma etching                              | SF <sub>6</sub>                                                                                                                       | Ag nano<br>particles | None     | 4.2                        |

| Metal-assisted chemical<br>etching (MACE)   | AgNO <sub>3</sub> /HF/HNO <sub>3</sub>                                                                                                | None                 | Ag, Au   | 0.3                        |

| Electrochemical etching                     | HF, EtOH,H <sub>2</sub> O                                                                                                             | None                 | None     | <5.0                       |

#### Table 2.

Various methods for texturing diamond-wire sawn multi-crystalline wafers [20].

texturing process [21]. However, since RIE is a vacuum-based process the throughput is low as compared to a typical inline process and also additional pre-processing and post-processing is required to remove the saw damage and damage due to ion-bombardment, respectively. A variant of the RIE method which does not require vacuum or plasma has been implemented in a commercial tool [22].

One of the approaches for texturing DWS multi-crystalline wafers is to upgrade the existing acidic texturing-based chemistry with additives [23–25]. Such an approach can potentially have a lower CoO compared to the MACE-based approach [23]. Reflectance of such an additive-based approach has been demonstrated to be similar to the conventional isotexturing solution with solar cell efficiency of 18.7% for the Al-BSF-based structure [24].

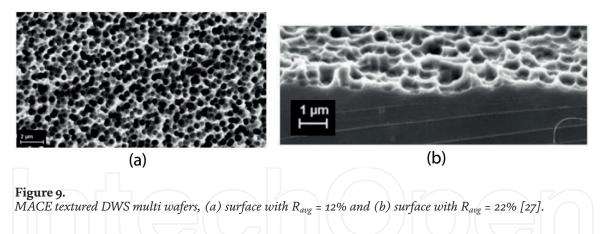

MACE-based texturing is similar to the conventional acidic etching method with an additional step of catalytic metal deposition. The process flow consists of SDR, catalyst metal deposition, chemical etching and post-treatment. Efficiencies of 19.2% have been obtained for commercial multi Al-BSF cells using batch-type MACE texturing process [26]. Inline-type MACE-based commercial tool has been demonstrated with the possibility to tune the reflectance in the range of 12–23% and obtain average efficiency for Al-BSF and PERC structure of 18.8 and 20.2%, respectively [27]. Representative images of textured surface based on MACE process are shown in **Figure 9**. The cost of ownership (CoO) of the inline MACE process is potentially lower compared to the batch-based MACE process with scope to reduce it further by recycling Ag from the texturing bath [27].

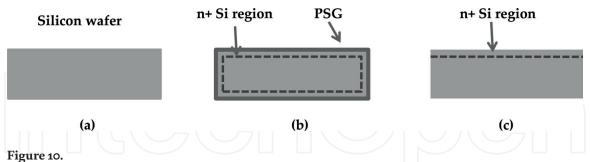

#### 4.3 Wet-chemistry-based edge isolation

The emitter region in a solar cell is fabricated by a high temperature diffusion process (to be discussed in sections ahead). During the diffusion process, phosphor silicate glass (PSG) is deposited on the wafer which should be removed before deposition of the ARC layer. As depicted in **Figure 10**, after the diffusion step, the n-type region is also present on the edges and the rear-side of the wafer. The n-type layer on edges and the rear-side will short-circuit the emitter with the base substrate and hence it is important to etch these regions and isolate the emitter on the FS from the base substrate as depicted in **Figure 10**(c).

The edge isolation process can be performed in an inline manner similar to the texturing process discussed in the previous section. The exception in this case is that the chemical should etch only the rear-side and edges without interacting with the FS. A representative image of the edge isolation process is shown in **Figure 11**. It is important to note that the rollers are present only on the bottom-side to avoid any contact of the etching solution with the front-side. The subsequent steps after the RS etching are similar to those in the inline texturing machine.

Processing of silicon wafer after diffusion and edge isolation (a) Textured silicon wafer, (b) Diffused silicon wafer, (c) Diffused silicon wafer after edge-isolation.

#### **Figure 11.** *Representative image of solar cell in an inline edge-isolation bath.*

#### 5. Thermal processes for solar cell fabrication

High temperature processes form a vital part of solar cell fabrication. Examples of such processes are forming the p-n junction by diffusion, firing of screen-printed contacts, activating surface passivation layers or annealing process induced defects. The section glimpses the basic physics of emitter diffusion process and plasma enhanced chemical vapor deposition (PECVD).

#### 5.1 Emitter diffusion

Emitter diffusion is one of the crucial thermal steps in the industrial solar cell fabrication. The n-type emitter of the crystalline p-type silicon solar cells is formed by phosphorus (P) diffusion. In the diffusion process, the Si wafers are sent in a furnace and exposed at 800–900°C to phosphoryl chloride (POCl<sub>3</sub>) and  $O_2$  which results in PSG deposition on the Si wafer surfaces. This step is called as pre-deposition, where the PSG [28] acts as a source of phosphorus (P) dopants to diffuse into the Si wafer. The next step is drive-in, where the supply of dopant gases is disconnected and P from the PSG layer diffuses further into the Si wafer. Hannes et al. [29] illustrates for the optimum process feasibility for photovoltaic applications, three different effects have to be considered. Firstly, the in-diffusion of P from the PSG and its presence in electrically active and inactive states in the Si wafer, which increases Shockley-Read-Hall (SRH) recombination. Secondly, the gettering of impurities into the Si layer towards the PSG layer. Finally, the metal contact formation with the P-doped Si emitter draws out the generated power.

The diffusion process is quantified by sheet resistance which depends on the depth of p-n junction and P concentration profile. The sheet resistance has units of  $\Omega$ /cm (commonly measured as  $\Omega$ / $\Box$ ) and is measured using a four-point probe system. The definition of sheet resistance is illustrated in Eq. (1).

$$R = \frac{\rho l}{A} = \frac{\rho l}{W * D} = \frac{\rho}{D} = \rho_{sheet}$$

(1)

where *R* = resistance of a rectangular section ( $\Omega$ );  $\rho$  = resistivity ( $\Omega$  cm); *l* = length of the rectangular section (cm); *A* = area of the rectangular section (cm<sup>2</sup>); *W* = width of the rectangular section (cm); *D* = depth of the rectangular section (cm) and  $\rho_{sheet}$  = resistance for given depth (*D*) when l = W ( $\Omega/\Box$ ).

The earlier values of emitter sheet resistance were  $30-60 \ \Omega/\Box$  with p-n junction depths of >400 nm and high P surface concentration. With improvements in the front-side silver (Ag) contacting paste, the emitter sheet resistance is now in the range of  $90-110 \ \Omega/\Box$  with junction depth of around 300 nm and lower P surface concentration. Shifting to larger sheet-resistance allows to capture more light in the UV and blue spectrum, while also reducing the surface recombination to improve the V<sub>oc</sub>. It should be noted that the diffusion process occurs on the FS (directly exposed to the gases) and also on the edges and RS. If the edge isolation process is not carried out (as discussed in Section 4.3), the emitter will be short-circuited with the substrate.

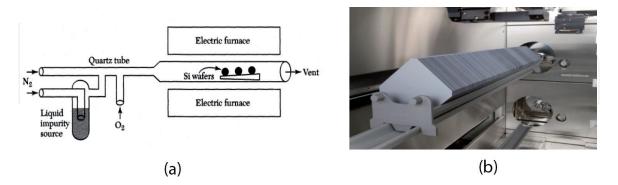

**Figure 12** shows the POCl<sub>3</sub> diffusion process in a closed quartz-tube system. POCl<sub>3</sub> is a liquid source supplied to the process tube by bubbling it with a carrier gas  $N_2$ . By mixing  $O_2$  with the POCl<sub>3</sub>, there will be an epitaxial growth of PSG layer as indicated in Eq. (2) [30].

$$4POCl_3 + 3O_2 \rightarrow 2P_2O_5(PSG) + 6Cl_2$$

(2)

At the Si surface,  $2P_2O_5$  is reduced to elemental phosphorus during the drive-in step as shown in Eq. (3) [30].

$$2P_2O_5 + 5Si \rightarrow 4P + 5SiO_2 \tag{3}$$

Chlorine which is a by-product during the pre-deposition cleans the wafers and quartz-tube by forming complexes with metals. PSG is used as source for driving in the P atoms into Si surface. During the drive-in process,  $POCl_3$  is switched off and only  $O_2$  is added to build up a thin oxide layer beneath the PSG to enhance the diffusion of P atoms into Si surface.

Inside the diffusion tube there are five heating zones as illustrated in **Figure 13**. The zones are:

- Loading zone (LZ)—area from where the wafers are loaded into the tube.

- Center loading zone (CLZ)—area between the loading zone and centre zone.

- Center zone (CZ)—center area of the tube.

- Center gas zone (CGZ)—area between the centre zone and gas zone.

- Gas zone (GZ)—area from where the gases move out through the exhaust.

Typically the temperatures of each heating zone are adjusted to obtain equal emitter sheet resistance for all wafers across the boat.

Environment of diffusion process should be very clean and hence quartz material is used for the tubes. Cleanliness of the tubes and loading-area maintenance also affects the process results. Since in gas-phase diffusion there is no residue in the tube, it results in a cleaner process. By half pitch loading in the low pressure (LP) conditions [31], the throughput can be increased. Commonly 1,000 wafers are loaded in a single tube and with five diffusion tubes in a batch-type diffusion system, a throughput of up to 3,800 wafers/h can be achieved for solar cell manufacturing.

#### Figure 12.

(a) Schematic representation of the batch-type diffusion process and (b) representative image of a batch-type diffusion equipment. Source: centrotherm GmbH.

**Figure 13.** *Heating zones inside the diffusion tube.*

An inline diffusion system where the wafers are transported on a belt with phosphoric acid as the source of P dopants was also used in commercial production [32]. However, compared to the inline process, the batch process is more clean, effective and efficient. For n-type solar cells or advanced solar cells concepts like PERT, the p-type batch diffusion is based on boron (B) dopant sources like boron tribromide (BBr<sub>3</sub>) [33, 34].

#### 5.2 Anti-reflective coating (ARC) deposition

A bare Si surface reflects >30% of the light incident. As discussed in Section 4, the texturing process improves the light-capturing. It is desirable to reduce the reflectance further which is obtained by depositing an ARC layer. TiO<sub>x</sub> was one of the earliest material to be used as an ARC layer for solar cells, however since it could not provide adequate surface passivation it was eventually replaces by SiN<sub>x</sub>:H [37]. Thermally grown silicon oxide (SiO<sub>2</sub>) was also employed as the passivating material in the record breaking passivated emitter rear locally diffused (PERL) cells [37]. High thermal budget and long process time made SiO<sub>2</sub>-based passivation unsuitable for mass-production of solar cells [37]. A comprehensive review of various ARC and passivating material for solar cell applications is discussed in [37].

The plasma enhanced chemical vapour deposition (PECVD) process is suitable for depositing an ARC layer of  $SiN_x$ :H which not only reduces the reflection but also passivates the front-side n-type emitter and the bulk thus improving the solar cell efficiency [36, 37]. A schematic of a batch-type PECVD system is shown in **Figure 14**. The wafers are loaded in a graphite boat with the front-sides facing each other. An RF plasma based on process gases ammonia (NH<sub>3</sub>) and silane (SiH<sub>4</sub>) operating at a temperature of 400–450°C deposit the hydrogenated SiN<sub>x</sub>:H layer as per Eq. (4) [35]. The hydrogen incorporated in the SiN<sub>x</sub>:H film diffuses into the bulk during the firing step (discussed in next section) and passivates the dangling bonds to improve the solar cell performance [36, 37].

$$3SiH_4 + 2NH_3 + N_2 \rightarrow Si_3N_4 + 9H_2 \tag{4}$$

The refractive index (RI) of the  $SiN_x$ :H film is controlled by the ratio of  $SiH_4$ / NH<sub>3</sub> gas, while the thickness depends on the deposition duration. The  $SiN_x$ :H-based ARC can minimize the reflection for a single wavelength and the wavelength-thickness is given by [38],

$t = \frac{\lambda_0}{4n_1}$ (5)

where *t* = thickness of the SiN<sub>x</sub>:H ARC layer,  $\lambda_0$  = wavelength of incoming light and  $n_1$  = refractive index of the SiN<sub>x</sub>:H layer.

Based on the relationship, the ARC is also called as a 'quarter wavelength ARC'. For solar cells, the RI and thickness are selected to minimize the reflection at a wavelength of 600 nm as it is the peak of the solar spectrum. The thickness and RI of the ARC is selected to be the geometric mean of materials on either side, i.e., glass/air and Si. The typical thickness of the SiN<sub>x</sub>:H ARC is 80–85 nm with RI of 2.0–2.1 giving the solar cell a color of blue to violet blue. A representative image of textured multi-crystalline solar cell deposited with SiN<sub>x</sub>:H is shown in **Figure 15(a)**, while the variation of SiN<sub>x</sub>:H color based on its thickness is shown in **Figure 15(b)**. It is important to note that there is a dependence on the surface texture and ARC color for given deposition parameters. There is a variety of solar modules where the color of the solar cells is darker unlike the typical blue color. A typical ARC

(a) Schematic diagram of batch-type PECVD process for SiN<sub>x</sub>:H deposition and (b) graphite boat for loading Si wafers in the PECVD furnace.

Figure 15.

(a) Representative image of  $SiN_x$ :H coated multi-crystalline solar cell, (b) variation of  $SiN_x$ :H layer based on its thickness.

deposition stage in a solar cell manufacturing line consists of two PECVD systems, each with four tubes and a throughput of up to 3,500 wafers/h.

$SiN_x$ :H is not suitable for passivating p-type Si and hence dielectrics like  $Al_2O_3$  are used for RS passivation for cell architecture like PERC cells [8] or for p-type emitters in n-type solar cells. For PERC solar cells, the  $Al_2O_3$  passivating layer is capped by a  $SiN_x$ :H to protect it from the Al-paste during the firing process and also serve as an internal reflector for the long wavelength light. Commercial PECVD and atomic layer deposition (ALD)-based systems are available for depositing  $Al_2O_3$  with throughput of up to 4,800 wafers/h [39].

#### 6. Metallization and solar cell characterization

#### 6.1 Screen-printing-based metallization

The last processing step for solar cell fabrication is the FS and RS metallization to draw out the power with minimum resistive losses. Ag is a good contact material for the n-type emitter, while Al makes a very good contact with the p-type substrate. A combination of Ag/Al paste is used to print pads on the RS to facilitate interconnection of solar cells in a module. Screen-printing is a simple, fast and continuously evolving process for solar cell metallization.

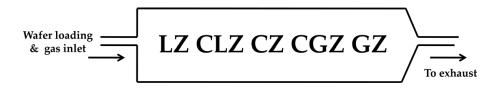

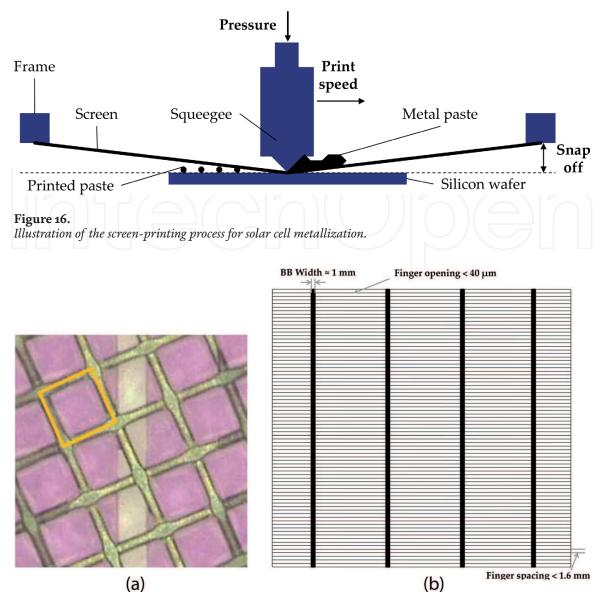

A schematic representation of the screen-printing process is shown in **Figure 16**. The screens have an emulsion coated stainless steel mesh with openings as per the desired metallization pattern as illustrated in **Figure 17(a)**.

Figure 17.

(a) Mesh-emulsion screen with finger opening for FS Ag printing [40] and (b) representative FS metallization pattern.

The metal paste is spread over the screen via the flood and the squeegee movement that deposits the paste on the solar cell based on the screen-pattern. Snapoff is the distance the screen and the solar cell. The squeegee pressure and the snap-off distance are the critical parameters that determine the paste lay down and geometry of the Ag FS fingers.

Typical paste lay down for Ag/Al RS pads, RS Al and FS Ag are 35–45 mg, 1.1–1.4 g and 100–120 mg, respectively for a 6 inch Al-BSF multi-crystalline solar cell. An illustrative Ag FS metallization pattern is shown in **Figure 17(b)**. The Ag finger opening has reduced to below 30  $\mu$ m, while application of 5 bus-bar is being increasingly adopted now. With such screen parameter and good paste lay down, consistent FF of >80% should be obtained for the Al-BSF solar cells with an optical shading loss of <6%.

#### 6.2 Drying and fast firing of metallization pastes

The metallization pastes consist of metal powder, solvents and organic binders. In case of FS Ag paste, the paste also contains glass-frit while etches the SiN<sub>x</sub>:H layer and makes contact with the n-type emitter [41]. The metal pastes

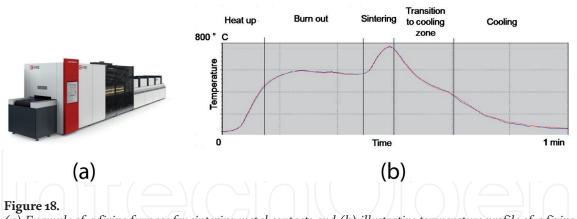

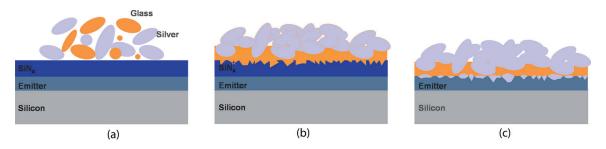

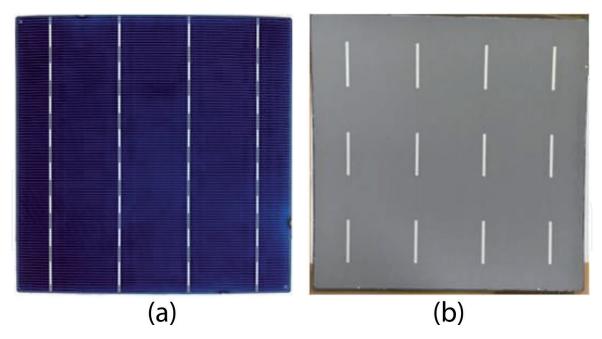

are dried after printing and finally they are sent through a fast-firing furnace for sintering and form the RS Al-BSF and FS Ag contact. An example of such a fast-firing furnace with the temperature profile is shown in **Figure 18**. The FS Ag finger sintering process is illustrated in **Figure 19**. When the solar cell passes through the fast-firing furnace, the organic binders are burnt, followed by melting of the glass frit and finally formation of Ag crystallites contacting the n-type emitter. The firing profile needs to be tuned based on the specific types of metallization pastes and emitter diffusion profile. As an example, the firing peak temperature could be low to not form a good ohmic contact on the FS, while a too high temperature can lead to diffusion of Ag through the junction and shunting of the p-n junction. Image of a complete multi-crystalline Al-BSF solar cell is shown in **Figure 20**.

#### 6.3 Plating-based front-side metallization

The costing of various factors in solar cell processing have decreased over the years, while the contribution of front Ag is still the most significant [42]. Significant amount of work has been done to replace Ag by alternate metal like copper (Cu) which has a conductivity value of very close to that of Ag and also offers a potential significant cost advantage [43, 44]. Cu has high diffusivity and solubility in Si and hence a barrier-layer like nickel (Ni) is deposited on Si prior to Cu plating [42]. Light-induced plating (LIP) which is derived from conventional plating utilizes the photovoltaic effect of light to plate the desired metal and has many advantages compared to conventional plating [43, 44].

(a) Example of a firing furnace for sintering metal contacts and (b) illustrative temperature profile of a firing furnace. Source: centrotherm GmbH.

#### Figure 19.

Illustration of the firing process. (a) Burning out of the organic binders, (b) melting of glass frit which etches the SiN<sub>x</sub>:H and (c) Ag crystallite formation at the emitter interface.

#### Figure 20.

(a) FS of a complete solar cell and (b) RS of a complete solar cell.

Ni-Cu-based front-side metallization requires an additional front-side ARC patterning step unlike the Ag paste-based metallization and in most cases also an additional Ni sintering step to reduce the contact resistance and have good adhesion of the metal stack [42]. Commercial DWS cut mc-Si solar cells based on Ni-Cu-Ag plated stack have been demonstrated with finger width of 22  $\mu$ m, aspect-ratio of close to 0.5 and similar efficiency as that of reference screen-printed Ag-based solar cells [45].

Continuous improvement in the Ag FS pastes along with simplicity, reliability and high throughput of the screen-printing process has made it difficult for Ni-Cubased metallization to compete with Ag-based FS metallization. However, high solar cell efficiency concepts like bifacial heterojunction solar cells, where Cu can be directly plated onto the transparent conducting oxide, the plating process is simplified and requires only a single tool [39]. Similarly, high efficiency concepts which require reduced amount of metal can achieve the same using plating-based metallization [42, 46].

#### 6.4 I-V testing and characterization of solar cells

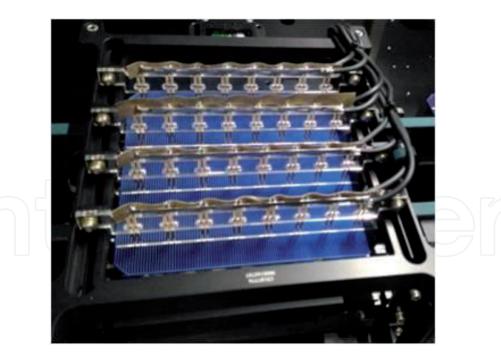

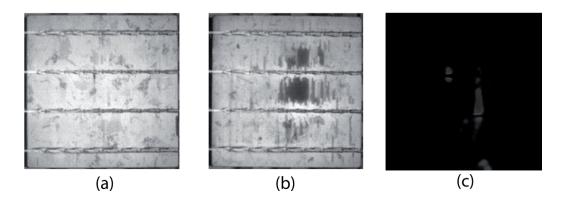

The final step is I-V testing of the complete solar-cells as per the standard test conditions (STC), i.e., AM 1.5G, 1000 W/m<sup>2</sup> with a Class AAA solar simulator. An example of FS probing of solar cell is shown in **Figure 21**. The typical parameters obtained from the I-V tester are indicated in **Table 3**. I-V testers have many characterization parameters which can be helpful for diagnosis of solar cell defects. Representative electroluminescence (EL) and thermal IR image of a solar cell with some defects are shown in **Figure 22(a)**–(**c**). An EL image of a good solar cell with uniform intensity is shown in **Figure 22(a)**, while for a solar cell in which the FS fingers are not printed uniformly, a darker contrast can be seen in **Figure 22(b)**. **Figure 22(c)** shows a thermal IR image of a solar cell with a localized shunt which has been formed during one of the processing steps. In the end, the solar cells are sorted in different efficiency bins based on the selected classification.

**Figure 21.** *I-V measurement FS probing for solar cell characterization.*

| Parameter               | Comments                                                                      |  |

|-------------------------|-------------------------------------------------------------------------------|--|

| V <sub>oc</sub> (V)     | Good mc-Si Al-BSF solar cells have a value of >0.635 V                        |  |

| I <sub>sc</sub> (A)     | Good mc-Si Al-BSF solar cells have a value of >9.0 A                          |  |

| FF (%)                  | Good mc-Si Al-BSF solar cells have a value of >80%                            |  |

| Efficiency (%)          | Good mc-Si Al-BSF solar cells have a value of >18.6%                          |  |

| V <sub>mpp</sub> (V)    | Corresponding voltage at the maximum power point                              |  |

| I <sub>mpp</sub> (A)    | Corresponding current at the maximum power point                              |  |

| R <sub>s</sub> (Ω)      | Good mc-Si Al-BSF solar cells have a value of <1.5 m $\Omega$                 |  |

| R <sub>sh</sub> (Ω)     | Good mc-Si Al-BSF solar cells have a value of >100 $\Omega$                   |  |

| I <sub>rev</sub> (A)    | Reverse current at a voltage of $-12$ V should be <0.5 A for good solar cells |  |

| FS BB-BB resistance (Ω) | Resistance measured between the BB's on the FS                                |  |

| RS BB-BB resistance (Ω) | Resistance measured between the BB's on the RS                                |  |

#### Table 3.

Parameters for characterization of a solar cell obtained from I-V measurement.

Figure 22.

(a) EL image of a good solar cell, (b) EL image of a solar cell with non-uniformity in Ag finger printing and (c) thermal IR image of a solar cell indicating presence of localized shunts.

#### 7. Future trends

DWS has become the standard for mono-crystalline wafers, while it is expected to have a market share of >80% by 2022 for multi-crystalline wafers [2]. SWS for multi-crystalline wafers is expected to phase-out by that time. With DWS, the kerf loss would also become <80  $\mu$ m by 2022, which would in turn reduce the poly-Si consumption per wafer below 15 g. 3BB design for front-contacts are expected to phase-out by 2020 with 50% share for 5BB design. With continuous improvements in Ag pastes and screens, the FS finger width is projected to reduce to 30  $\mu$ m by 2022. Wet-chemical processing tools have crossed throughput of 8,000 wafers/h in 2018 and would touch 9,000 wafers/h by 2020. Thermal processing equipments have reached throughput of 5000 wafers/h in 2018 and expected to cross 7,000 wafers/h by 2020. The metallization and I-V testing/sorting section is expected to have a throughput of >7,000 wafers/h by 2022.

Al-BSF-based cell technology which has a market share of >60% in 2018 is expected to reduce to <20% by 2025. With more emphasis on high efficiency solar cells concepts, share of PERC technology is expected to be >50% by 2022. Production efficiency of Mono PERC is expected to be >22% by 2022, while for multi PERC it should touch 21% by the same time. An important aspect related to multi-PERC is the mitigation of LeTID-based problem to minimize the loss of efficiency after installations of the modules in the field. Si HJ cells with efficiencies of >22% in 2018 after expected to reach stable efficiency of 23% by 2020, with a market share of around 10% by 2022. High efficiency bifacial cells with an additional advantage of tapping the solar radiation from the rear-side is expected to have a market share of 20% by 2022. N-type back contact solar cells are expected to cross 24% efficiency by 2020.

#### 8. Conclusions

Si solar cells have become an important part of the renewable energy domain over past decades with matured manufacturing technologies. P-type multicrystalline wafers have become the main-stay for solar cell production. However, with higher efficiency and decreasing production costs, mono-crystalline solar cells have also gained a significant share and are expected to compete closely with multi-crystalline wafers in the near future. For standard Al-BSF technology, 19 and 20% has become the bench-mark for multi-crystalline and mono-crystalline solar cells, respectively. Mono-PERC and multi-PERC cells have reached stabilized efficiencies of 21.5 and 20%, respectively. In addition, PERC also provides a simpler approach for bifacial solar cells by having a grid pattern on the RS instead of the full area contact. High efficiency n-type and bifacial solar cells have a market-share of <10% which is expected to increase in the future. The manufacturing technologies have matured considerably over the past few years with further improvements to increase the throughput.

#### Acknowledgements

The authors would like to thank the colleagues from RCT Solutions GmbH from whom some of the contents for the chapter have been taken. Mehul C. Raval would like to thank colleague Jim Zhou for the discussions regarding black silicon texturing.

# Intechopen

## IntechOpen

#### **Author details**

Mehul C. Raval\* and Sukumar Madugula Reddy RCT Solutions GmbH, Konstanz, Germany

\*Address all correspondence to: mehul.c.raval@iitb.ac.in

#### **IntechOpen**

© 2019 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

#### References

[1] Renewables 2018 Global Status Report. REN21. 2018

[2] International Technology Roadmap for Photovoltaic (2017) including maturity report 2018. 9th ed. 2018

[3] Wenham SR, Green MA. Silicon solar cells. Progress in Photovoltaics: Research and Applications. 1996;4:

3-33. DOI: 10.1002/(SICI)

1099-159X(199601/02)4:1%3C3::AID-PIP117%3E3.0.CO;2-S

[4] PVEDUCATION.ORG. Available from: https://www.pveducation.org/ pvcdrom/manufacturing/refiningsilicon [Accessed: 10 December 2018]

[5] PVEDUCATION.ORG. 2018. Available from: https://www. pveducation.org/pvcdrom/ manufacturing/single-crystallinesilicon [Accessed: 10 December 2018]

[6] PVEDUCATION.ORG. 2018. Available from: https://www. pveducation.org/pvcdrom/ manufacturing-si-cells/czochralskisilicon [Accessed: 10 December 2018]

[7] Kim JM, Kim YK. Growth and characterization of 240 kg multicrystalline silicon ingot by directional solidification. Solar Energy Materials and Solar Cells. 2004;81: 217-224. DOI: 10.1016/j.solmat.

2003.11.020

[8] Huang H, Lv J, Bao Y, Xuan R, Sun S, Sneck S, et al. 20.8% industrial PERC solar cell: ALD Al2O3 rear surface passivation, efficiency loss mechanisms analysis and roadmap to 24%. Solar Energy Materials and Solar Cells. 2017;**161**:14-30. DOI: 10.1016/j. solmat.2016.11.018

[9] Panasonic. Available from: https:// www.panasonic.com/global/corporate/ technology-design/technology/hit.html [Accessed: 16 December 2018] [10] Sun Power Corporation. Available from: https://us.sunpower.com/ why-sunpower/maxeon-solar-cells/ [Accessed: 16 December 2018]

[11] Lossen J, Buchholz F, Comparotto C, Eisert S, Libal J, Mihailetchi VD, et al. From lab to fab: Bifacial n-type cells entering industrial production. In: Proceedings of 31st EU PVSEC; Hamburg. 2015. pp. 965-968

[12] Chen G, Kashkoush I, Nemeth D, Rieker J, Danel A. Development of IPAfree texturing processes in advanced solar cell fabrication. In: Proceedings of 29th EU PVSEC; Amsterdam. 2014. pp. 1096-1099

[13] Strinitz F, Schoerg F, Fuerst M, El Jaouhari A, Kuehnlein H. Fast alkaline texturing process for high throughput PERC solar cell manufacturing. In: Proceedings of 33rd EU PVSEC; Brussels. 2017. pp. 955-959

[14] Moynihan M, O'Connor C, Barr B, Tiffany S, Braun W, Allardyce G, et al. IPA free texturing of mono-crystalline solar cells. In: Proceedings of 25th EU PVSEC; Valencia. 2010. pp. 1332-1336

[15] Wefringhaus E, Helfricht A. KOH/surfactant as an alternative to KOH/IPA for texturisation of monocrystallin silicon. In: Proceedings of 24th EUPVSEC; Hamburg. 2009. pp. 1860-1862

[16] George M, Bohling D, Treichel H, Goldstein A, Kern W, Potter BG Jr. Investigation of biodegradable texturing chemistries for crystalline Si. In: Proceedings of 27th EU PVSEC; Frankfurt. 2012. pp. 1105-1108

[17] Hauser A, Melnyk I, WefringhausE, Delahaye F, Vilsmeier G, FathP. Acidic texturisation of MC-SI usinga high throughput in-line prototypesystem with no organic chemistry. In:

Proceedings of 19th EU PVSEC; Paris. 2004. pp. 1094-1097

[18] Hauser A, Melnyk I, Fath P, Narayanan S, Roberts S, BrutonTM. A simplified process for isotropic texturing of MC-SI. In: Proceedings of WCPEC-3; Osaka. 2003. pp. 1447-1450

[19] Cao F, Chen K, Zhang J, Ye X, Li J, Zou S, et al. Next-generation multicrystalline silicon solar cells: Diamondwire sawing, nano-texture and high efficiency. Solar Energy Materials & Solar Cells. 2015;**141**:132-138. DOI: 10.1016/j.solmat.2015.05.030

[20] Hsu C-H, Wu J-R, Lu Y-T, Flood DJ, Barron AR, Chen L-C. Fabrication and characteristics of black silicon for solar cell applications: An overview. Materials Science in Semiconductor Processing. 2014;**25**:2-17. DOI: 10.1016/j. mssp.2014.02.005

[21] Ye Q, Wang W, Dong J, Wei W, Yang Y, Cai W, et al. Industrially feasible

PERC cells on diamond wire sawing multi-crystalline silicon wafers textured by RIE towards 21.62% efficiency.

In: Proceedings of 35th EU PVSEC;

Brussels; 2018. pp. 401-405

[22] Nines Photovoltaics. 2018. Available from: http://nines-pv.com/adetechnology/ [Accessed: 03 December 2019]

[23] Richter M, Straub B, Plettig M, Pediatitakis A, Sander B, Queisser S, et al. Metal-free inline texturing for effective light trapping on DW mc-Si. In: Proceedings of 11th SNEC. Shanghai; 2017

[24] Schmitt C, Zhou B, Straub B, Burgenmeister B, Pediaditakis A, Sander B-U, et al. Metal-free texturing for diamond-wire-sawn multi-crystalline silicon (DWS-mc). In: Proceedings of 35th EU PVSEC; Brussels. 2018

[25] Black Silicon 4th Generation-Nanjing Nascien New Material Co., Ltd. In: Proceedings of 3rd Black Silicon Forum; 2018

[26] Status and application of black silicon technology-Canadian Solar Inc. In: Proceedings of 3rd Black Silicon Forum; 2018

[27] Jooss W, Melnyk I, Jung-König J, Teppe A, Werling T, Voigt O, et al. Development and optimization of a novel inline black silicon texturing process for increased solar cell performance. In: Proceedings of 33rd EU PVSEC; Amsterdam. 2017. pp. 368-372

[28] Wolf SWA, Kimmerle A. Status and perspective of emitter formation by POCl3-diffusion. In: Proceedings of 31st EU PVSEC; Munich. 2015. pp. 414-419

[29] Wagner H, Dastgheib-Shirazi A, Min B, Morishige AE, Steyer M, Hahn G, et al. Optimizing phosphorus diffusion for photovoltaic applications: Peak doping, inactive phosphorus, gettering, and contact formation. Journal of Applied Physics. 2016;**119**:185704. DOI: 10.1063/1.4949326

[30] Air Products and Chemical, Inc. Process guidelines for using phosphorous oxychloride as an N-type silicon dopant. 2016

[31] Dastgheib-Shirazi A, Steyer M, Micard G, Wagner H, Altermatt PP, Hahn G. Relationships between diffusion parameters and phosphorus precipitation during the POCl<sub>3</sub> diffusion process. Energy Proedia. 2013:**38:**254-262. DOI: 10.1016/j.egypro.2013.07.275

[32] Voyer C, Buettner T, Bock R, Biro D, Preu R. Microscopic homogeneity of emitters formed on textured silicon using in-line diffusion and phosphoric acid as the dopant source. Solar Energy Materials & Solar Cells. 2009;**93**:932-935. DOI: 10.1016/j. solmat.2008.11.061

[33] Mihailetchi VD, Coletti G, Komatsu Y, Geerligs LJ, Kvande R, Arnberg L, et al. Large area and screen printed N-type silicon solar cells with efficiency exceeding 18%. In: Proceedings of 23rd EU PVSEC; Valencia. 2008. pp. 1036-1039

[34] Richter A, Horteis M, Benick J, Henneck S, Hemle M, Glunz SW. Towards industrially feasible high-efficiency n-type Si solar cells with boron diffused front side emitter-combining firing stable Al<sub>2</sub>O<sub>3</sub> passivation and fine line printing. In: Proceedings of 35th PVSC; Honolulu, Hawaii. 2010

[35] PVEDUCATION.ORG. 2019. Available from: https://www. pveducation.org/pvcdrom/ manufacturing-si-cells/ anti-reflection-coatings

[36] Bonilla RS, Hoex B, Hamer P, Wilshaw PR. Dielectric surface passivation for silicon solar cells: A review. Physica Status Solidi A: Applications and Materials Science. 2017;**214**(7):1700293. DOI: 10.1002/ pssa.201700293

[37] Soppe W, Rieffe H, Weeber A. Bulk and surface passivation of silicon solar cells accomplished by silicon nitride deposited on industrial scale by microwave PECVD. Progress in Photovoltaics: Research and Applications. 2005;**13**:551-569. DOI: 10.1002/pip.611

[38] PVEDUCATION.ORG. 2019. Available from: https://www. pveducation.org/pvcdrom/design-ofsilicon-cells/anti-reflection-coatings [Accessed: 29 January 2019]

[39] Chunduri SK, Schmela M. PERC solar cell technology report. Taiyang news. 2017

[40] Zhang Y, Zhang L, Jiang L, Song L, Guo C, Dua V, et al. Knotless screen printing for crystalline silicon solar cells. In: Proceedings of 7th Workshop on Metallization; Konstanz. 2017

[41] Lin C-H, Tsai S-Y, Hsu S-P, Hsieh M-H. Investigation of Ag-bulk/glassyphase/Si heterostructures of printed Ag contacts on crystalline Si solar cells. Solar Energy Materials & Solar Cells. 2008;**92**:1011-1015. DOI: 10.1016/j. solmat.2008.02.032

[42] Lennon A, Flynn S, Young T, Nampalli N, Edwards M, Evans R, et al. Addressing perceived barriers to the adoption of plated metallisation for silicon photovoltaic manufacturing. In: Proceedings of 52nd Annual Conference of the Australian Solar Council; Melbourne. 2014

[43] Raval MC, Solanki CS. Review of Ni-Cu based front side metallization for c-Si solar cells. Journal of Solar Energy.

2013;2013:Article ID 183812. DOI: 10.1155/2013/183812

[44] Lennon A, Yao Y, Wenham S. Evolution of metal plating for silicon solar cell metallisation. Progress in Photovoltaics: Research and Applications. 2013;**21**:1454-1468. DOI: 10.1002/pip.2221

[45] Fox S, Jie X, Wu H, Burschik J, Bay N, Crouse K, et al. Pilot production of high efficient metal catalyzed textured diamond wire sawn mc-Si solar cells combined with nickel-copper plated front contact processing. In: Proceedings of 33rd EU PVSEC; Amsterdam. 2017. pp. 362-367

[46] Cornagliotti E, Russell R, Tous L, Uruena A, Duerinckx F, Aleman M, et al. Bifacial n-PERT cells (Bi-PERT) with plated contacts for multi-wire interconnection. In: Proceedings of 32nd EU PVSEC; Munich. 2016. pp. 420-425