We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

186,000

200M

Our authors are among the

TOP 1% most cited scientists

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

## Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

### Self-Aligned π-Shaped Source/Drain Ultrathin SOI MOSFETs

Yi-Chuen Eng and Jyi-Tsong Lin National Sun Yat-Sen University, Department of Electrical Engineering 70, Lienhai Road, Kaohsiung 80424, Taiwan, R.O.C.

#### 1. Introduction

In this chapter, we shall study the short-channel characteristics of <u>self-aligned II-shaped</u> source/drain ultrathin silicon-on-insulator metal-oxide semiconductor <u>field-effect</u> <u>transistor</u> (SA-IIFET). The only difference between conventional and proposed <u>ultrathin</u> <u>silicon-on-insulator</u> (UTSOI) transistors is that a path from the <u>source/drain</u> (S/D) to the <u>silicon</u> (Si) substrate is created and called the <u>S/D</u> <u>tie</u> (SDT). Thus, UTSOI <u>metal-oxide</u> <u>semiconductor field-effect</u> <u>transistor</u> (MOSFET) thermal performance can be enhanced drastically by opening up the SDT rather than increasing Si body thickness.

Although the path between S/D and Si substrate has degraded the device properties slightly, the short-channel characteristics of SA-пFET are within acceptable limits due to the existence of <u>UT</u> <u>body</u> (UTB). After changing the S/D structure in the proposed SOI transistor, the <u>n</u>-channel enhancement-type <u>MOS</u>FET (NMOS) current drive gets improved accordingly. Furthermore, the effects of self-heating on SA-пFET performance can be reduced greatly. This is ascribed to the fact that the forms of additional leakage paths truly help dissipate the heat generated by the thermal vibrations of the crystalline lattice phonons. For these reasons, quasi-SOI devices are strong contenders for future <u>complementary MOS</u> (CMOS) technology.

The objectives of this chapter are to describe the physical structure of the <u>**II**</u>-shaped <u>S</u>/<u>**D**</u> ( $\Pi$ -S/D) transistor and its process, to give an understanding of why SDT design must use, and to discuss the short-channel characteristics compared with those of a conventional UTSOI. By the end of this chapter, the reader should be able to know the importance of the design of SDT.

#### 2. Structure and process of the SA-nFET

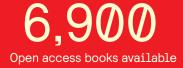

Figure 1 shows the physical structure of the SA- $\Pi$ FET. Observe that the SDT has a length  $L_{SDT}$  and a location which is determined by the length of <u>**Si**</u> **<u>n</u>itride** (SiN)  $L_{SP}$ , two important parameters of the SA- $\Pi$ FET.

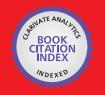

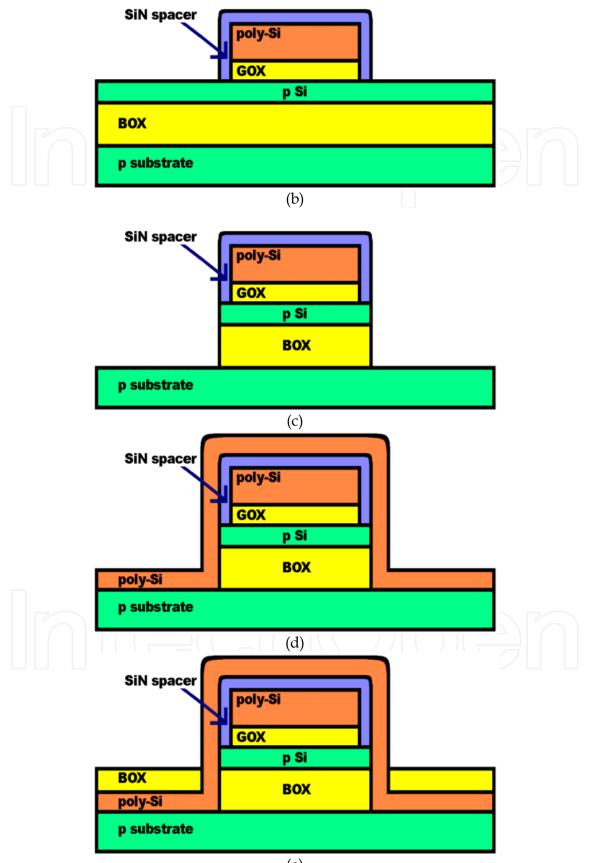

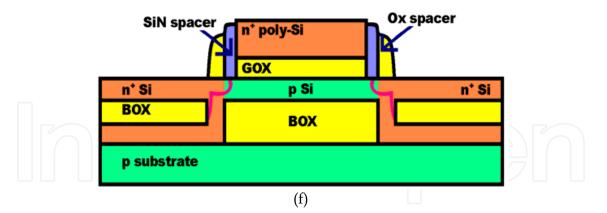

A simplified description of the fabrication of a SA- $\Pi$ FET is as follows (see Fig. 2(a)–(f)). The SOI wafer structure is used to make  $\Pi$ -S/D transistors, which has a Si layer located on top of the **<u>buried oxide</u>** (BOX) and a **<u>bulk Si</u>** (bulkSi) substrate layer located below the oxide insulating layer. The final Si layer thickness is obtained by thermal oxidation and etching down to 5 nm. A channel implantation process is first performed with **boron difluoride** (BF<sub>2</sub>), 2.3 KeV, 1.15×10<sup>12</sup> cm<sup>-2</sup>. Following this, device isolation is achieved using a traditional

Source: Micro Electronic and Mechanical Systems, Book edited by: Kenichi Takahata, ISBN 978-953-307-027-8, pp. 572, December 2009, INTECH, Croatia, downloaded from SCIYO.COM

**<u>shallow trench isolation</u>** (STI) approach. A gate insulator of **Si dioxide** (SiO<sub>2</sub>) is thermally growth and a **<u>poly</u>crystalline-Si** (poly-Si) layer as a gate electrode deposited by using the **<u>chemical vapor deposition</u>** (CVD) process is then formed. In order to form a  $\Pi$ -S/D scheme, the layer of SiN as hard mask is deposited by CVD. After the patterning of the gate stack (see Fig. 2(a)), a SiN layer for forming the spacer is deposited and etched back, as shown in Fig. 2(b). The sidewall spacer hard mask is used for etching Si and BOX, respectively (see Fig. 2(c)). A layer of poly-Si is deposited as SDT shown in Fig. 2(d). After the deposition and planarization of the SiO<sub>2</sub> layer, the etching process is performed in order to form a BOX layer under the source and drain regions (see Fig. 2(e)). The poly-Si layer is deposited, patterned, and etched to create the active region of the S/D, as shown in Fig. 2(f). Next, the S/D implantation process is carried out by **<u>arsenic</u>** (As), 10 KeV, 2.1×10<sup>14</sup> cm<sup>-2</sup>. **<u>Rapid</u> thermal <u>annealing</u> (RTA) process is followed to activate the dopants and repair the lattice damage that is caused by the implantation process. Finally, a conventional SOI fabrication flow can be used for <u><b>back-end-of-line**</u> (BEOL) processing.

The simulation parameters are  $T_{BOX} = 40$  nm,  $T_{BOI} = 50$  nm,  $T_{S/D} = T_{Si} = 5$  nm, and  $T_{GOX} = 1.4$  nm for the  $\Pi$ -S/D. Various gate lengts  $L_G$  ( $L_{CH} - 9$  nm) of 10 nm ~ 70 nm were investiaged. Notice that all the parameters of the UTSOI NMOS are equivalent to those of the  $\Pi$ -S/D NMOS, expect that the  $T_{BOX}$  is equal to the  $T_{BOI}$  (= 50 nm).

www.intechopen.com

(e)

Fig. 2. The SA-ITFET fabrication process [1], [2]; (a) gate patterning, (b) SiN spacer formation, (c) Si/BOX etch with a SiN mask, (d) poly-Si deposition, (e) formation of BOX, and (f) S/D poly-Si deposition and formation by CMP and wet etching.

#### 3. Electrical characteristics of the SA-nFET

In this section, we study the physical and electrical characteristics of the SA- $\Pi$ FET. It should be clear that the design of SDT is important for scaled  $\Pi$ -S/D transistors. In order to control the <u>short-channel effects</u> (SCEs), a conventional UTSOI MOSFET is considered as a strong contender for replacing the position of the bulkSi in near future [3]. However, note that because the SOI family of devices has a BOX layer (which is underneath the active region), the self-heating is undesirable for the performance due to lattice scattering. As device dimensions decrease, the self-heating is more pronounced. Hence the importance of SDT in the conventional UTSOI MOSFET is growing owing to self-heating.

#### I<sub>DS</sub>-V<sub>GS</sub> characteristics of the SA-⊓FET

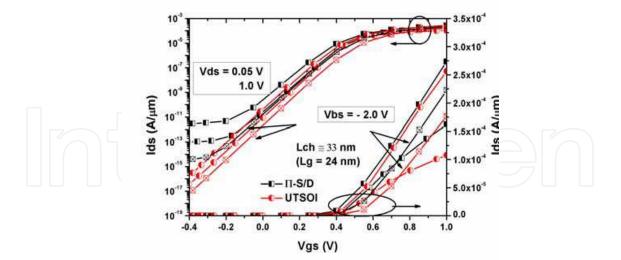

Figure 3 shows the drain current  $I_{DS}$  versus gate voltage  $V_{GS}$  characteristic curves of the SA-IIFET compared with a conventional UTSOI FET. Obviously, the leakage current of a conventional UTSOI FET is lower than that of the SA-IIFET. This means that an (SDT) additional path appended becomes an encumbrance to the UTSOI NMOS, resulting in increased p-n junction leakage current. However, the short-channel such as <u>drain-induced</u> <u>barrier lowering</u> (DIBL) and <u>subthreshold swing</u> (S.S.) characteristics of SA-IIFET are within acceptable limits because of the presence of UTB. Replacing the conventional UTSOI MOSFET S/D structure with an SDT results in the slight performance degradation in the proposed SOI transistor, but the results can get accepted.

#### Short-channel effects in ⊓-S/D transistors

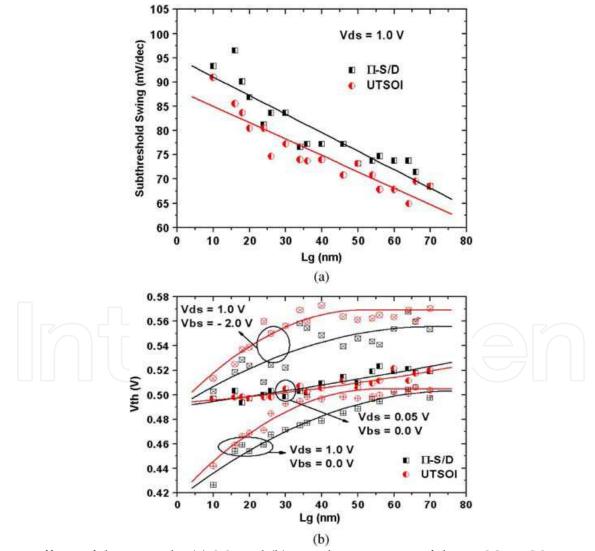

As shown in Fig. 4, the dependence of S.S. and **threshold voltage** ( $V_{\text{TH}}$ ) on **gate length** ( $L_{\text{G}}$ ) for both  $\Pi$ -S/D and UTSOI devices is compared. It is obvious in Fig. 4a that the conventional UTSOI MOSFET having a  $L_{\text{SDT}} = 0$  nm exhibits low S.S. values. On the contrary, our proposed UTSOI structure having a  $L_{\text{SDT}} = 10$  nm shows how the S.S. is slightly degraded. The reason is that for the  $\Pi$ -S/D NMOS, the SDT provides additional paths for high electric field from the drain side to influence the channel, which leads to S.S. degradation. Fortunately, the results are within acceptable limits (< 100 mV/dec at  $L_{\text{G}} = 10$  nm). Fig. 4b

Fig. 3. Comparison of  $I_{DS}$ - $V_{GS}$  curves between two transistors  $\Pi$ -S/D and UTSOI.

Fig. 4. Effects of the  $L_G$  on the (a) S.S. and (b)  $V_{TH}$  characteristics of the UTSOI MOSFET w/ and w/o additional SDT.

shows the impact of  $L_{\rm G}$  on  $V_{\rm TH}$ . (The intersection of the maximum and minimum slope lines in the log( $I_{\rm DS}$ )- $V_{\rm GS}$  characteristic curves was used to extract the  $V_{\rm TH}$ .) The  $V_{\rm TH}$  is found to decrease with decrease in  $L_{\rm G}$  mainly due to increased charge sharing [4]. It can be seen in figure that the saturation  $V_{\rm TH}$  roll-off is worse than linear  $V_{\rm TH}$ . When a **substrate bias** ( $V_{\rm BS}$ ) of – 2.0 V is applied, the  $V_{\rm TH}$  is increased, in comparison with  $V_{\rm BS}$  equal to 0 V. Apparently, the  $V_{\rm TH}$  roll-off behavior of the  $\Pi$ -S/D transistor is quite similar to UTSOI transistor, since both devices have the same Si channel thickness.

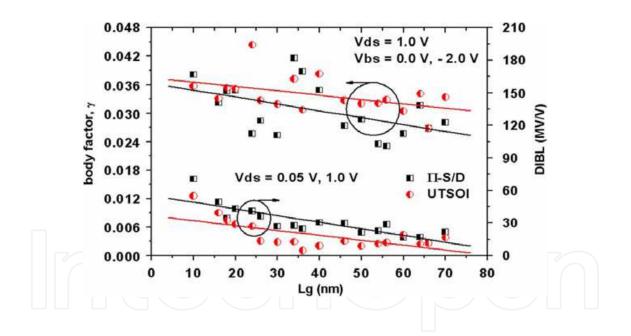

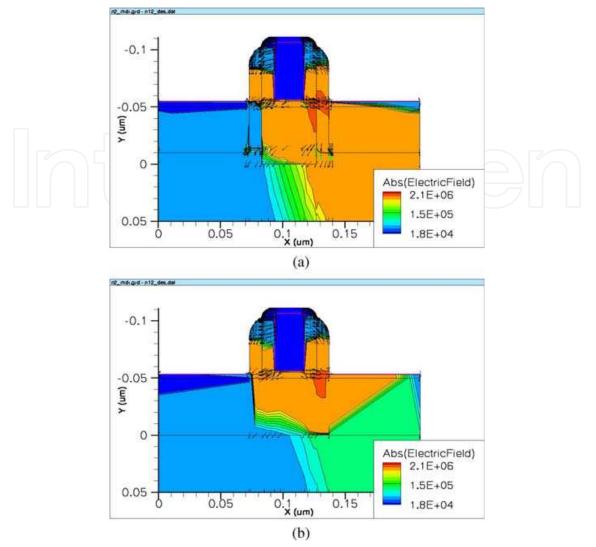

Figure 5 shows the impact of  $L_{\rm G}$  on body factor  $\gamma$  and DIBL. The  $\gamma$  was extracted using the method described in [5] ( $\gamma = |\Delta V_{\rm TH,SAT}/\Delta V_{\rm BS}|$ ), which is the shift of the  $V_{\rm TH,SAT}$  caused by the change in the  $V_{\rm BS}$ , whereas DIBL is the difference between  $V_{\rm TH,LIN}$  and  $V_{\rm TH,SAT}$ . The decrease of the  $L_{\rm G}$  leads to large values of  $\gamma$  and DIBL. This is because the short  $L_{\rm G}$  has less control over the channel region, thereby increasing the **S/D subthreshold off-state leakage current** ( $I_{\rm sd,leak}$ ). For short channel, the  $V_{\rm BS}$  has a large effect on  $V_{\rm TH,SAT}$ . Consequently, the application of  $V_{\rm BS}$  in  $V_{\rm TH,SAT}$  results in a large  $\gamma$  for short-channel devices. The DIBL of the  $\Pi$ -S/D NMOS is slightly larger than the UTSOI NMOS, as in the case of the S.S. shown in Fig. 4a. The DIBL is similarly impacted by the increased penetration of the fringing fields from the drain region (see Fig. 6).

Fig. 5. Effects of the  $L_G$  on the  $\gamma$  and DIBL characteristics of the UTSOI MOSFET w/ and w/o additional SDT.

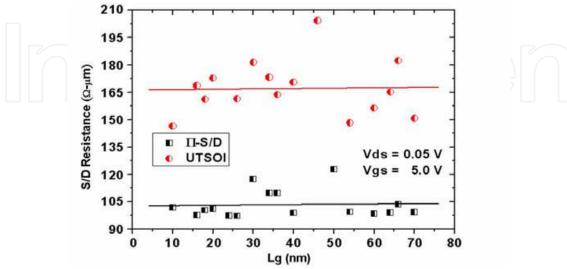

Moreover, we find that the **effective parasitic series S/D resistance** ( $R_{S/D}$ ) for both devices, as shown in Fig. 7 does not decrease dramatically by reducing the  $L_G$ . Nevertheless, the  $\Pi$ -S/D transistor has a smaller  $R_{S/D}$  compared to a conventional UTSOI transistor, which implies that the SDT added to the UTSOI structure helps increase the drain current. Thus, the additional SDT mainly contributes the  $R_{S/D}$  value. Apparently, small  $R_{S/D}$  leads to high drain current.

Fig. 6. Contour plot of simulated electric field (in volts per centimeter) at  $V_{\text{DS}} = 4.0$  V and  $V_{\text{GT}}$  ( $V_{\text{GS}}-V_{\text{TH}}$ ) = 1.0 V for n-channel UTSOI MOSFET w/ and w/o additional SDT.  $L_{\text{G}} = 24$  nm.

Fig. 7. Effects of the  $L_G$  on the  $R_{S/D}$  characteristics of the UTSOI MOSFET w/ and w/o additional SDT.

#### Self-heating effects in ⊓-S/D transistors

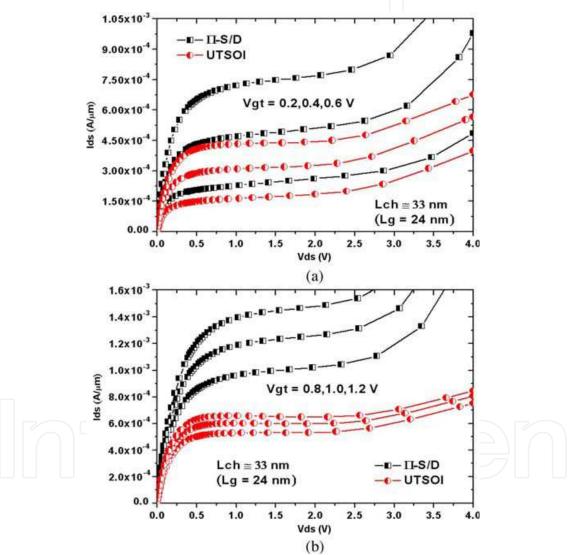

In order to investigate the thermal behavior of the  $\Pi$ -S/D and UTSOI devices, the curves in Fig. 8 compare the drain current  $I_{DS}$  versus drain-to-source voltage  $V_{DS}$  for various values of gate overdrive voltage  $V_{GT}$ . When the  $V_{GT}$  increases from 0.2 V to 1.2 V, the drain-source saturation current  $I_{DS}$  also increases in both types of transistors. In addition, a self-heating induced negative differential output conductance is observed for only the UTSOI-FET. The electron mobility decreases when the local lattice temperature increases due to effects of self-heating. The SDT is shown to overcome self-heating issues. The  $\Pi$ -S/D structure not only obtains high  $I_{DS}$  but also reduces the **self-heating effects** (SHEs). An interesting observation is that the reliability of the UTSOI MOSFET can be improved by the addition of an SDT.

Fig. 8. Comparison of  $I_{DS}$ - $V_{DS}$  curves between two transistors  $\Pi$ -S/D and UTSOI.

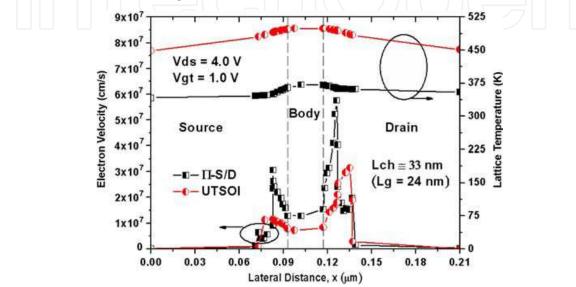

To probe the physical mechanisms involved for improved thermal performance of the  $\Pi$ -S/D structure, electron velocity and lattice temperature profiles for the  $\Pi$ -S/D and UTSOI are shown in Fig. 9. It should be noticed that the generated electron-hole pair will flow through the SDT, leading to a symmetric lattice temperature near the edges of both the source and drain regions. Moreover, this is due to the fact that the Si channel is thin enough,

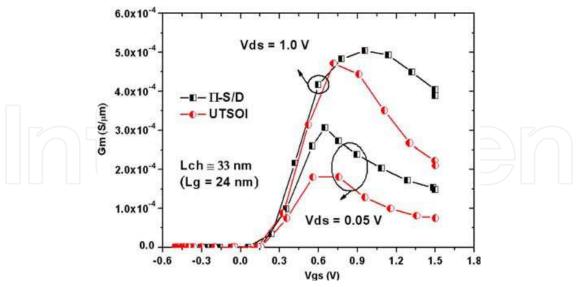

the generated hole carriers can flow into the ground terminal only through its source region, resulting in symmetric lattice temperature near the edges of both the source and drain regions. Since the SDT exists only in the  $\Pi$ -S/D NMOS, the SDT is to construct additional pathways to link Si substrate, which helps diminish the SHEs caused by the thermal vibrations. The two additional pathways can quickly disperse the heat generation in Si body, resulting in a higher electron velocity and better  $G_{\rm M}$ - $V_{\rm GS}$  characteristics, as shown in Fig. 10. For a UTSOI MOSFET, the mobility decreases as the lattice temperature increases; this implies that the reduced electron velocity and decreased transconductance are inevitable due to self-heating.

Fig. 9. Comparison of electron velocity and lattice temperature profiles between two transistors  $\Pi$ -S/D and UTSOI.

Fig. 10. Comparison of  $G_{M}$ - $V_{GS}$  curves between two transistors  $\Pi$ -S/D and UTSOI.

In this chapter, we demonstrate a new self-aligned  $\Pi$ -shaped S/D UTSOI MOSFET that reduces device self-heating but without losing the desirable electrical characteristics. According to simulation results, we find that although the  $\Pi$ -S/D structure appears to be less advantageous in terms of the charge sharing between the gate and the S/D diffusion

regions, the source-drain current is enhanced. Additionaly, the thermal stability of the  $\Pi$ -S/D NMOS are improved because the additional SDT increases the heat conductin area.

#### 4. Summary

A novel UTSOI with SDT MOSFET ( $\Pi$ -S/D transistor) is proposed, in order to reduce selfheating errors. A path from the S/D to the Si substrate is created and called SDT that which does not significantly degrade the UTSOI MOSFET characteristics due to UTB usage. Self-heating can be reduced greatly due to the presence of the SDT. The heat generated by thermal vibration of the atoms can be quickly dissipated via SDT. Furthermore, the shortchannel characteristics of <u>fully depleted</u> (FD) SOI MOSFET with SDT, such as DIBL and S.S., are not significantly degraded or impacted because the BOX layer is directly under the UTB channel region.

#### 5. References

- [1] Yi-Chuen Eng, Jyi-Tsong Lin, Po-Hsieh Lin, Hau-Yuan Huang, Shiang-Shi Kang, Kung-Kai Kao, Jeng-Da Lin, Yi-Ming Tseng, and Ying-Chieh Tsai, "Self-aligned ⊓-shaped Source/Drain Ultra-thin SOI MOSFETs," in Proc. 26th Int. Conf. Microelectronics, p.499, 2008.

- [2] Jyi-Tsong Lin, Yi-Chuen Eng, Hau-Yuan Huang, Shiang-Shi Kang, Po-Hsieh Lin, Kung-Kai Kao, Jeng-Da Lin, Yi-Ming Tseng, Ying-Chieh Tsai, and Hung-Jen Tseng, "Short-Channel Characteristics of Self-Aligned Π-Shaped Source/Drain Ultrathin SOI MOSFETs," IEEE Trans. Electron Dev., ED-55, 1480 (2008).

- [3] International Technology Roadmap for Semiconductors. (2007). [Online]. Available: www.itrs.net.

- [4] Donald A. Neamen, An Introduction to Semiconductor Devices, 1st ed. New York: McGraw-Hill, 2005.

- [5] Toshiro Hiramoto and Toshiharu Nagumo, "Multi-Gate MOSFETs with Back-Gate Control," in *Proc. IEEE Int. Conf. Integer. Circuit Des. Technol.*, p.80, 2006.

- [6] User's Manual, 2004. ISE-TCAD.

#### Micro Electronic and Mechanical Systems Edited by Kenichi Takahata

ISBN 978-953-307-027-8 Hard cover, 386 pages Publisher InTech Published online 01, December, 2009 Published in print edition December, 2009

This book discusses key aspects of MEMS technology areas, organized in twenty-seven chapters that present the latest research developments in micro electronic and mechanical systems. The book addresses a wide range of fundamental and practical issues related to MEMS, advanced metal-oxide-semiconductor (MOS) and complementary MOS (CMOS) devices, SoC technology, integrated circuit testing and verification, and other important topics in the field. Several chapters cover state-of-the-art microfabrication techniques and materials as enabling technologies for the microsystems. Reliability issues concerning both electronic and mechanical aspects of these devices and systems are also addressed in various chapters.

#### How to reference

In order to correctly reference this scholarly work, feel free to copy and paste the following:

Yi-Chuen Eng and Jyi-Tsong Lin (2009). Self-Aligned π-Shaped Source/Drain Ultrathin SOI MOSFETs, Micro Electronic and Mechanical Systems, Kenichi Takahata (Ed.), ISBN: 978-953-307-027-8, InTech, Available from: http://www.intechopen.com/books/micro-electronic-and-mechanical-systems/self-aligned-shaped-source-drain-ultrathin-soi-mosfets

# INTECH

open science | open minds

#### InTech Europe

University Campus STeP Ri Slavka Krautzeka 83/A 51000 Rijeka, Croatia Phone: +385 (51) 770 447 Fax: +385 (51) 686 166 www.intechopen.com

#### InTech China

Unit 405, Office Block, Hotel Equatorial Shanghai No.65, Yan An Road (West), Shanghai, 200040, China 中国上海市延安西路65号上海国际贵都大饭店办公楼405单元 Phone: +86-21-62489820 Fax: +86-21-62489821 © 2009 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the <u>Creative Commons Attribution-NonCommercial-ShareAlike-3.0 License</u>, which permits use, distribution and reproduction for non-commercial purposes, provided the original is properly cited and derivative works building on this content are distributed under the same license.