We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

186,000

200M

Our authors are among the

TOP 1% most cited scientists

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

### Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

### Carbon Nanotube Interconnect Technologies for Future LSIs

Mizuhisa Nihei, Akio Kawabata, Motonobu Sato, Tatsuhiro Nozue, Takashi Hyakushima, Daiyu Kondo, Mari Ohfuti, Shintaro Sato and Yuji Awano MIRAI-Selete Japan

#### 1. Introduction

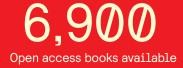

Carbon nanotubes (CNTs) are attractive as nanosize structural elements from which devices can be constructed by bottom-up fabrication. A CNT is a macromolecule of carbon and is made by rolling a sheet of graphite into a cylindrical shape. CNTs exhibit excellent electrical properties that include current densities exceeding 10<sup>9</sup> A/cm<sup>2</sup> and ballistic transport along the tube. Because of these factors, with their large electro-migration tolerance and low electrical resistance, CNTs can be used as nano-size wiring materials, and are thus becoming potential candidates for future LSI interconnects. Much effort has been made to produce CNT vias, which use bundles of MWNTs (multi-walled carbon nanotubes), as vertical wiring materials as shown in Figure 1. Sato et al. demonstrated low-resistance CNT vias employing a novel metallization technology, which used preformed catalyst metal particles, to grow dense MWNT-bundles by thermal chemical vapor deposition (CVD).

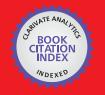

The advantage of CNT-bundles is their low resistance, which may be the solution to the problem of high resistance in scaled-down vias. As shown in Fig. 2, we estimated the resistance of a 50-nm-diameter via depending on the filling rate of CNTs in the via area. In this estimation we assumed that CNTs have the quantum resistance  $R_Q = h/4e^2 = 6.45 \text{ k}\Omega$  (conductance  $G_Q = 2G_{Q0} = 4e^2/h$ , which reaches the maximum conductance limit for ballistic transport in two channels of a CNT), that current flows through each shell of MWNTs, and that there is no dependence of ballistic transport on CNT length. In order to lower the

Source: Solid State Circuits Technologies, Book edited by: Jacobus W. Swart, ISBN 978-953-307-045-2, pp. 462, January 2010, INTECH, Croatia, downloaded from SCIYO.COM

resistance of CNT vias, it is necessary to increase the nanotube's density, by decreasing its diameter. Regarding the electrical properties, CNTs consist of semiconductive CNTs as well as metallic types. Since the energy gap of a semiconductive CNT is inversely proportional to its diameter, smaller-diameter SWNTs may adversely influence the current conduction property. On the other hand, larger-diameter MWNTs seem to have a vanishing energy gap at room temperature. So, we are aiming at using metallic MWNTs with their ballistic transport properties as vias.

Fig. 2. Estimated resistance of 50-nm-diameter vias dependent on the filling rate of CNTs in a via hole for 1-nm-diameter SWNT, 3-nm-diameter 3-walled MWNT, and 5-nm-diameter 6-walled MWNT.

In this study, we demonstrated vertically scaled-down CNT via interconnects to clarify the current conduction properties of MWNT-bundles grown using thermal CVD. Based on our investigation, the carrier transport is expected to be ballistic for scaled-down vias. The excellent tolerance of CNT vias to a high current density was also demonstrated.

#### 2. Experimental

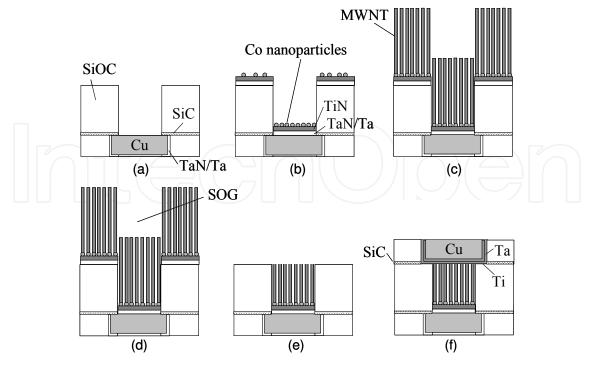

As schematically shown in Fig. 3, we proposed CNT damascene processes to integrate scaled-down CNT vias with Cu interconnects. The processes were mostly compatible with conventional Cu interconnects. Briefly, a substrate with a Cu interconnect covered by a dielectric layer was first prepared. The dielectric layer was SiOC with k = 3.0 or k = 2.6. Via holes with a diameter of 160 nm were made using conventional photolithography followed by dry etching. A TaN/Ta barrier layer and a TiN contact layer were deposited by physical vapor deposition (PVD). Because CNTs do not need barrier layers, it is favourable to deposit these metals except the sidewall of the via hole. Size-controlled Co particles with an average diameter of about 4 nm were then deposited using a catalyst nano-particles deposition system. Previously we grew CNTs selectively in via holes, but all over the substrate in our new damascene process. For MWNT growth using the thermal CVD system, a mixture of C<sub>2</sub>H<sub>2</sub> and Ar at 1 kPa was used as the source gas. The substrate temperature ranged from 400 °C to 450 °C. The chemical mechanical polishing (CMP) process we used is as follows:

Fig. 3. CNT damascene via process: (a) Via hole formation on bottom Cu interconnect, (b) TaN/Ta barrier layer, TiN contact layer and Co catalyst nanoparticle formation, (c) MWNT growth, (d) SOG coating, (e) CMP Planarization, and (f) Top Cu interconnect formation.

the samples were coated with the spin-on glass (SOG) in order to hold the CNTs during the CMP process. CNTs were polished on the TiN layer on a SiOC layer with a conventional IC1000 pad and silica slurry under pressures of 2 psi (13.8 kPa) for 240 sec. Then, the TiN and TaN/Ta layers were polished with conventional barrier-metal CMP slurry. After polishing, the substrate was slightly wet-etched using buffered HF solution. Finally, the Ti top contact layer, Ta barrier layer and Cu wire were connected to CNT vias by PVD without subsequent annealing.

#### 3. Results and discussion

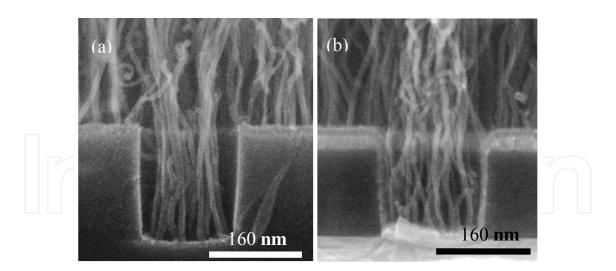

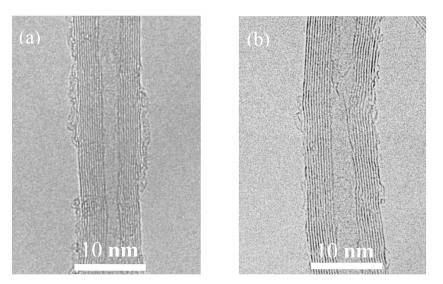

Figures 4(a) and (b) are the cross-sectional scanning electron microscopy (SEM) images of CNT vias fabricated with growth temperatures of 450 °C and 400 °C. We can see in the images that CNTs grown at 400 °C are a little less straight than those at 450 °C, suggesting CNTs at 400 °C are a little more defective.

To further investigate the quality of CNTs, we performed transmission electron microscopy (TEM) analyses, whose results are shown in Fig. 5. The TEM images indicate that CNTs grown at either temperature are of high quality. However, CNTs at 400 °C appear to be a little more defective.

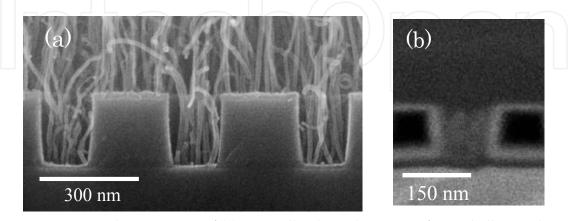

Figure 6(a) shows a cross-sectional SEM image of CNTs formed all over the substrate, having 160-nm diameter via holes, at the growth temperature of 450 °C. We succeeded in growing vertically-aligned MWNTs with a diameter of 10 nm, a shell number of 7 and a density of 3x10<sup>11</sup> cm<sup>-2</sup>. Figure 6(b) shows a cross-sectional SEM image of CNT vias after CMP planarization. MWNT-bundles were successfully polished under pressures as low as those in the conventional Cu/low-k CMP process. Although SOG is filled well with MWNTs inside the 160-nm-diameter via hole, the filling factor of CNT in via is still low in this study.

Fig. 4. Cross-sectional SEM image of the 160-nm-diameter CNT growth temperature (a) 450  $^{\circ}\text{C}$  and (b) 400  $^{\circ}\text{C}$ .

Fig. 5. TEM image of the CNT growth temperature (a) 450 °C and (b) 400 °C.

Fig. 6. Cross-sectional SEM image of (a) vertically aligned MWNTs formed all over the substrate, having 160-nm-diameter via holes, and (b) 160-nm-diameter CNT vias after CMP planarization.

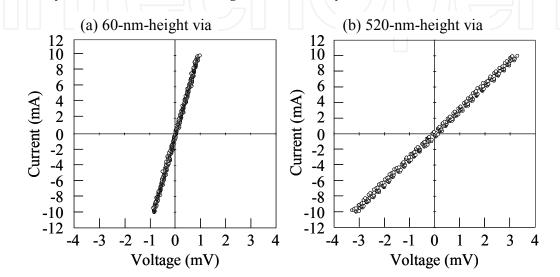

We measured the via resistance of 2800-nm-diameter CNT vias with a four-point probe using Kelvin patterns. Figures 7(a) and (b) show the current-voltage characteristic on the low-bias region for the via height of 60 nm and 520 nm, respectively. For both cases, the current increased linearly depending on the voltage, and good ohmic contacts were achieved between the MWNT-bundle and the TiN contact layer. We summarized the electrical properties of 2800-nm-diameter CNT vias for a via height of 60 nm and 520 nm in Table I. The obtained resistance of 0.05  $\Omega$  for 60-nm-height 2800-nm-diameter vias is the lowest value ever reported. The most important point of the result is that the via resistance decreased by about 84% as the via height decreased by about 89%.

Fig. 7. Current-voltage characteristic of the 2800-nm-diameter CNT vias with a via height of (a) 60 nm and (b) 520 nm.

| Sample | Diameter<br>(nm) | Height<br>(nm) | Resistance<br>(Ω) | Resistivity<br>(μΩcm) | Transport<br>property |

|--------|------------------|----------------|-------------------|-----------------------|-----------------------|

| #1     | 2800             | 60             | 0.05              | -                     | Ballistic             |

| #2     | 2800             | 520            | 0.32              | 379                   | Ohmic                 |

Table 1. Summary of electrical properties for CNT vias. The CNT density of 3x10<sup>11</sup> cm<sup>-2</sup> corresponds to the filling rate of 24%. The diameter and the shell number are 10 nm and 7, respectively. The shell number which contributes to the current conduction was estimated from the assumption of the quantum resistance.

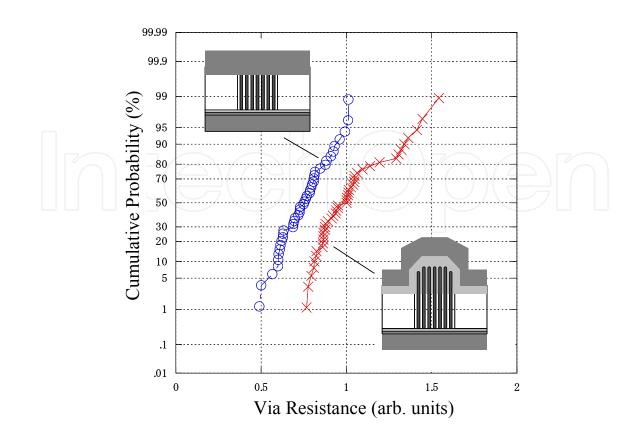

Figure 8 shows via resistance distributions of the 2000-nm-diameter CNT vias with and without CMP planarization. The average via resistance of the sample with CMP decreased by about 25% compared with that without CMP. The scattering for the distribution of the sample with CMP is also smaller than that without CMP. We speculated that cutting the CNT bundles short by CMP could increase the number of electrical contacts between MWNT tips and the top metal electrode, because as-grown CNT bundles have an unfavorable worse uniformity in length.

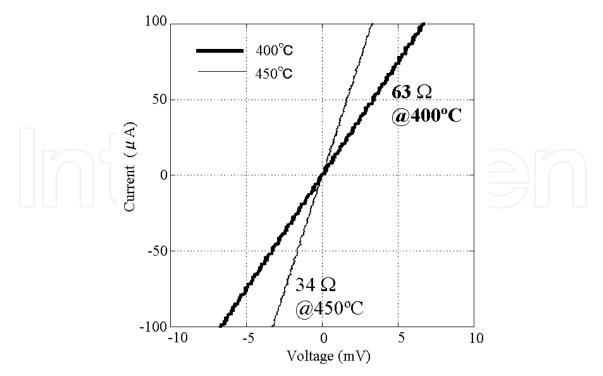

We also measured the resistance of 160-nm-diameter CNT vias with a four-point probe using Kelvin patterns. Figure 9 shows the current-voltage characteristics on the low-bias region. It was found that the resistance depended on the growth temperature. The via

Fig. 8. Via resistance depending on the top metal contacts with and without CMP planarization.

Fig. 9. Current-Voltage characteristics of the 160-nm-diameter CNT via grown at (a) 450  $^{\circ}$ C and (b) 400  $^{\circ}$ C.

resistance was 34  $\Omega$  for a growth temperature of 450 °C, and 64  $\Omega$  for 400 °C. Since the site density of the CNTs was similar for both temperatures, we speculate that the difference in resistance may have been caused by the difference in the CNT quality.

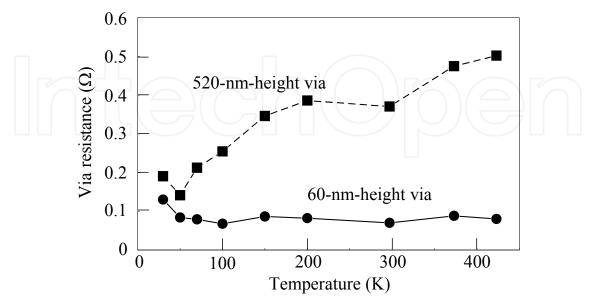

To investigate the transport mechanism, we measured the temperature dependence of the via resistance as shown in Fig. 10. The 520-nm-height vias shows the linear decrease of the resistance by decreasing the temperature. This characteristic is ohmic, which has been attributed to electron-phonon scattering. The corresponding resistivity of 379  $\mu\Omega$ cm was obtained for 520-nm-height CNT vias, which are of the same order of magnitude as the value of CVD-tungsten (W) plugs (100-210  $\mu\Omega$ cm). On the other hand, the resistance of 60-nm-height vias was independent of temperatures as high as 423 K, which suggests that the carrier transport is ballistic.

In order to estimate the electron mean free path  $\lambda_{CNT}$  of ballistic transport, we assumed the quantum resistance  $R_Q$ . The CNT via resistance  $R_{Via}$  is given by (1), where  $R_C$  is the imperfect metal-CNT contact resistance,  $n_{CNT}$  is the number of shells which contributed to the current conduction and H is the via height

$$R_{Via} = \frac{R_C + R_{CNT}}{n_{CNT}} \tag{1}$$

where

$$\begin{split} R_{CNT} &= R_Q = \frac{h}{4e^2} \dots if \ H \ll \lambda_{CNT} \\ &= H \cdot \frac{R_Q}{\lambda_{CNT}} = H \cdot \left[\frac{h}{4e^2}\right] \cdot \frac{1}{\lambda_{CNT}} \dots if \ H > \lambda_{CNT} \end{split}$$

Assuming the imperfect contact resistance  $R_C$  is as low as 0.5 k $\Omega$ , we estimated that the shell number of 7 contributed as a current conduction channel.

Fig. 10. Temperature dependence of the via resistance for the 60-nm and 520-nm-height CNT via.

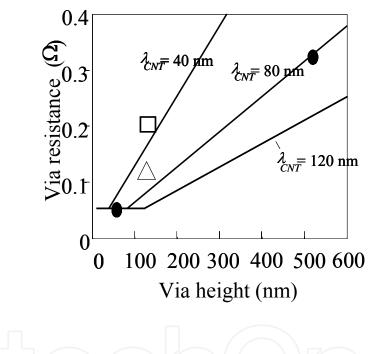

Figure 11 shows the via resistance as a function of the via height. The filled circles show the previous results for 2800-nm-diameter vias with a growth temperature of 450 °C. The solid lines indicate the via resistance calculated assuming various electron mean free paths. An solid rectangle or triangle indicates the current result normalized to a diameter of 2800 nm. As can be seen in the figure, the current result for 450 °C falls on the line for an electron mean free path of 80 nm, the same as the previous data. This seems reasonable considering the growth temperature for the previous data was also 450 °C. On the other hand, the resistance for 400 °C falls on the line for an electron mean free path of 40 nm, which suggests the quality of CNTs grown at 400 °C is not as high as that at 450 °C, as also speculated from the SEM and TEM results. We therefore currently work on synthesizing higher-quality CNTs at 400 °C or lower.

Fig. 11. Via resistance dependence as a function of the via height.

Solid line: the via resistance calculated assuming various electron mean free paths.

•: 2800-nm-diameter via 450 °C growth, △: 160-nm-diameter via 450 °C growth, □: 160-nm-diameter via 400 °C growth.

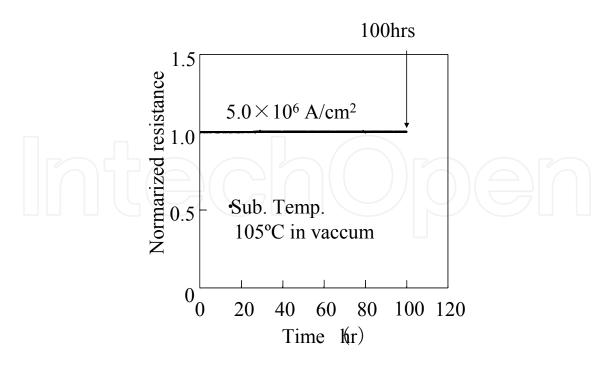

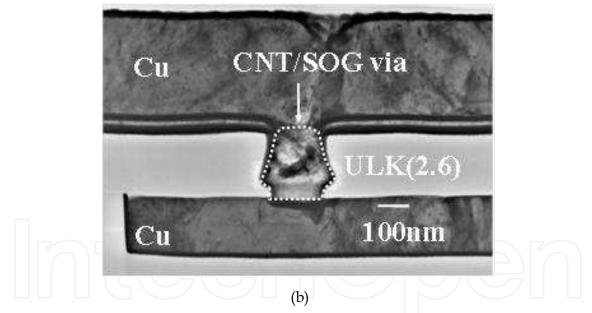

The stability of the via resistance under an electric current with a density of  $5.0 \times 10^6$  A/cm<sup>2</sup> is shown in Fig. 12(a). The via diameter and growth temperature were 160 nm and 400 °C, respectively. The dielectric layer was made of SiOC with k = 2.6. The measurement was performed at 105 °C in a vacuum. The resistance remained stable even after running the electric current for 100 hrs. This indicates that the CNT via is robust over a high-density current as we expect. The cross-sectional TEM image of the via is shown in Fig. 12(b). The via shape looks deformed, but this was caused by high-energy electrons during the TEM observation.

(a)

Fig. 12. (a) EM characteristics at 105 °C in a vacuum and (b) cross-sectional TEM image of the CNT via.

#### 4. Conclusion

In this chapter, we report our trials of using bundles of CNTs with their ballistic transport properties as via interconnects of LSIs. We proposed CNT damascene processes to integrate scaled-down CNT vias with Cu interconnects. Moreover, we demonstrated vertically scaled-down MWNTs via interconnects to clarify the current conduction properties of MWNTs-bundles.

We fabricated a CNT via interconnect and evaluated its electrical properties and robustness over a high-density current. We found that the CNT via resistance was independent of temperatures, which suggests that the carrier transport is ballistic. From the via height dependence of the resistance, the electron mean free path was estimated to be about 80 nm, which is similar to the via height predicted for hp32-nm technology node. This indicates that it will be possible to realize CNT vias with ballistic conduction for hp32-nm technology node and beyond. It was also found that a CNT via was able to sustain a current density as high as  $5.0 \times 10^6$  A/cm<sup>2</sup> at 105 °C for 100 hours without any deterioration.

#### 5. Acknowledgments

We would like to thank Prof. M. Hirose and Dr. H. Watanabe of MIRAI-Selete, and Dr. N. Yokoyama at Fujitsu Laboratories Ltd. for their support and useful suggestions. This work was completed as part of the MIRAI Project supported by NEDO.

#### 6. References

- Awano, Y.; Sato, S.; Kondo, D.; Ohfuti, M.; Kawabata, A.; Nihei, M.; Yokoyama, N. (2006) *phys. stat. sol.,* (a) 203, pp. 3611

- Banerjee, K.; Im, S.; Srivastava, N. (2006) Proceedings of 1st International Conference on Nano-Networks

- Coiffic, J. C. ; Fayolle, M.; Maitrejean, S. ; Foa Torres, L. E. F. ; and Le Poche, H. (2007) *Appl. Phys. Lett.*, vol. 91, pp. 252107

- Coiffic, J. C.;, Fayolle, M.; Le Poche, H.; Maitrejean, S.; Olivier, S. (2008) *Proceedings of IEEE International Interconnect Technology Conference*, pp. 153

- Cho, H.; Koo, K. -H.; Kapur, P.; Saraswat, K. C. (2007) Proceedings of IEEE International Interconnect Technology Conference, pp. 135

- Hoenlein, W. (2001) *Proceedings of International Microprocesses & Nanotechnology Conference*, p. 76

- Horibe, M.; Nihei, M.; Kondo, D.; Kawabata, A.; Awano, Y. (2004) *Jpn. J. Appl. Phys.*, Vol. 43, pp. 6499

- Horibe, M.; Nihei, M.; Kondo, D.; Kawabata, A.; Awano, Y. (2004) *Jpn. J. Appl. Phys.*, Vol. 43, pp. 7337

- Horibe, M.; Nihei, M.; Kondo, D.; Kawabata, A.; Awano, Y. (2005) *Jpn. J. Appl. Phys.*, Vol. 44, pp. 5309

- Iijima, S. (1991) Nature, Vol. 354, pp. 56

- Katagiri, M.; Sakuma, N.; Suzuki, M.; Sakai, T.; Sato, S.; Hyakushima, T.; Nihei, M.; and Awano, Y. (2008) *Jpn. J. Appl. Phys.*, vol. 47, pp. 2024

- Katagiri, M.; Yamazaki, Y.; Sakuma, N.; Suzuki, M.; Sakai, T.; Wada, M.; Nakamura, N.; Matsunaga, N.; Sato, S.; Nihei, M.; and Awano, Y. (2009) Proceedings of IEEE International Interconnect Technology Conference, pp. 44

- Kawabata, A.; Sato, S.; Nozue, T.; Hyakushima, T.; Norimatsu, M.; Mishima, M.; Murakami, T.; Kondo, D.; Asano, K.; Ohfuti, M.; Kawarada, H.; Sakai, T.; Nihei, M.; Awano, Y. (2008) *Proceedings of IEEE International Interconnect Technology Conference*, pp. 237

- Kitsuki, H.; Saito, T.; Yamada, T.; Fabris, D.; Jameson, J. R.; Wilhite, P.; Suzuki, M, Yang, C.

Y. (2008) Proceedings of IEEE International Interconnect Technology Conference, pp. 43

- Kong, J.; Yenilmez, E.; Tombler, T. W.; Kim, W.; Dai, H. (2001) *Phys. Rev. Lett.*, Vol. 87, pp. 106801

- Kreupl, F.; Graham, A. P.; Liebau, M.; Duesberg, G. S.; Seidel, R.; Unger, E. (2004) Proceedings of IEEE International Electron Device Meeting, pp.683

- Li, J.; Ye, Q.; Cassell, A.; Koehne, J.; Hg, H. T.; Han, J.; and Meyyappan, M. (2003) Proceedings of IEEE International Interconnect Conference, pp.271

- Liu, K.; Avouris, Ph.; Martel, R.; Hsu, W. K. (2001) Phys. Rev. B, Vol. 63, pp. 161404

- Milne, W. I.; Wang, X.; Zhang, Y.; Haque, S.; Kim, S. M.; Udrea, F.; Robertson, J.; Teo, K. B. K. (2008) *Proceedings of IEEE International Interconnect Conference*, pp. 105

- Naeemi, A.; Sarvari, R.; and Meindl, J. D. (2004) *Proceedings of IEEE International Electron* Devices Meeting, pp. 699

- Naeemi, A.; Meindl, J. D. (2008) *Proceedings of IEEE International Interconnect Conference*, pp. 183

- Nihei, M.; Kawabata, A.; and Awano, Y. (2003) Jpn. J. Appl. Phys., Vol. 42, pp. L721

- Nihei, M.; Kawabata, A.; Awano, Y. (2004) Jpn. J. Appl. Phys., Vol. 43, pp. 1856

- Nihei, M.; Kondo, D.; Kawabata, A.; Sato, S.; Shioya, H.; Sakaue, M.; Iwai, T.; Ohfuti, M.; Awano, Y. (2005) Proceedings of IEEE International Interconnect Technology Conference, pp. 234

- Nihei, M.; Kawabata, A.; Kondo, D.; Horibe, M.; Sato, S.; Awano, Y. (2005) *Jpn. J. Appl. Phys.*, Vol. 44, pp. 1626

- Nihei, M.; Kawabata, A.; Horibe, M.; Kondo, D.; Sato, S.; Awano, Y. (2005) *Materials for Information Technology*, Springer publisher, 978-1-85233-941-8, Germany, pp. 315

- Nihei, M.; Kawabata, A.; Hyakushima, T.; Sato, S.; Nozue, T.; Kondo, D.; Shioya, H.; Iwai, T.; Ohfuti, M.; Awano, Y. (2006) *Proceedings of International Conference on Solid State Devices and Materials*, pp. 140

- Nihei, M.; Hyakushima, T.; Sato, S.; Nozue, T.; Norimatsu, M.; Mishima, M.; Murakami, T.; Kondo, D.; Kawabata, A.; Ohfuti, M.; Awano, Y. (2007) *Proceedings of IEEE International Interconnect Technology Conference*, pp. 204

- Ngo, Q.; Cassell, A.M.; Austin, A.J.; Jun Li; Krishnan, S.; Meyyappan, M.; Yang, C.Y. (2006) IEEE Electron Device Lett., Vol. 27, pp. 221

- Sato, S.; Nihei, M.; Mimura, A.; Kawabata, A.; Kondo, D.; Shioya, H.; Iwai, T.; Mishima, M.; Ohfuti, M.; Awano, Y. (2006) *Proceedings of IEEE International Interconnect Technology Conference*, pp. 230

- Sato, S.; Kawabata, A.; Kondo, D.; Nihei, M.; Awano, Y. (2005) *Chem. Phys. Lett.*, Vol. 402, pp. 149

- Srivastava, N.; Joshi, R. V.; Banerjee, K. (2005) Proceedings of IEEE International Electron Devices Meeting, pp. 257

- Yao, Z.; Kane, C. L.; Dekker, C. (2000) Phys. Rev. Lett., Vol. 84, pp. 2941

- Yamazaki, Y.; Sakuma, N.; Katagiri, M.; Suzuki, M.; Sakai, T.; Sato, S.; Nihei, M.; Awano, Y. (2008) *Appl. Phys. Express*, vol. 1, pp. 034004

Yokoyama, D.; Iwasaki, T.; Ishimaru, K.; Sato, S.; Hyakushima, T.; Nihei, M.; Awano, Y.; Kawarada, H. (2008) *Jpn. J. Appl. Phys.*, vol. 47, pp. 1985

Wei, B. Q.; Vajtai, R.; and P. M. Ajayan, P. M. (2001) Appl. Phys. Lett., vol. 79, pp. 1172

Solid State Circuits Technologies Edited by Jacobus W. Swart

ISBN 978-953-307-045-2 Hard cover, 462 pages **Publisher** InTech **Published online** 01, January, 2010 **Published in print edition** January, 2010

The evolution of solid-state circuit technology has a long history within a relatively short period of time. This technology has lead to the modern information society that connects us and tools, a large market, and many types of products and applications. The solid-state circuit technology continuously evolves via breakthroughs and improvements every year. This book is devoted to review and present novel approaches for some of the main issues involved in this exciting and vigorous technology. The book is composed of 22 chapters, written by authors coming from 30 different institutions located in 12 different countries throughout the Americas, Asia and Europe. Thus, reflecting the wide international contribution to the book. The broad range of subjects presented in the book offers a general overview of the main issues in modern solid-state circuit technology. Furthermore, the book offers an in depth analysis on specific subjects for specialists. We believe the book is of great scientific and educational value for many readers. I am profoundly indebted to the support provided by all of those involved in the work. First and foremost I would like to acknowledge and thank the authors who worked hard and generously agreed to share their results and knowledge. Second I would like to express my gratitude to the Intech team that invited me to edit the book and give me their full support and a fruitful experience while working together to combine this book.

#### How to reference

In order to correctly reference this scholarly work, feel free to copy and paste the following:

Mizuhisa Nihei, Akio Kawabata, Motonobu Sato, Tatsuhiro Nozue, Takashi Hyakushima, Daiyu Kondo, Mari Ohfuti, Shintaro Sato and Yuji Awano (2010). Carbon Nanotube Interconnect Technologies for Future LSIs, Solid State Circuits Technologies, Jacobus W. Swart (Ed.), ISBN: 978-953-307-045-2, InTech, Available from: http://www.intechopen.com/books/solid-state-circuits-technologies/carbon-nanotube-interconnect-technologies-for-future-lsis

#### InTech Europe

University Campus STeP Ri Slavka Krautzeka 83/A 51000 Rijeka, Croatia Phone: +385 (51) 770 447 Fax: +385 (51) 686 166 InTech China

Unit 405, Office Block, Hotel Equatorial Shanghai No.65, Yan An Road (West), Shanghai, 200040, China 中国上海市延安西路65号上海国际贵都大饭店办公楼405单元 Phone: +86-21-62489820 Fax: +86-21-62489821

www.intechopen.com

# IntechOpen

## IntechOpen

© 2010 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the <u>Creative Commons Attribution-NonCommercial-ShareAlike-3.0 License</u>, which permits use, distribution and reproduction for non-commercial purposes, provided the original is properly cited and derivative works building on this content are distributed under the same license.

## IntechOpen