We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

185,000

200M

Our authors are among the

TOP 1% most cited scientists

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

## Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

# Selective Epitaxy of Group IV Materials for CMOS Application

Guilei Wang, Henry H. Radamson and Mohammadreza Kolahdouz

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/intechopen.76244

#### Abstract

As the International Technology Roadmap for Semiconductors (ITRS) demands an increase of transistor density in the chip, the size of transistors has been continuously shrunk. In this evolution of transistor structure, different strain engineering methods were introduced to induce strain in the channel region. One of the most effective methods is applying embedded SiGe as stressor material in source and drain (S/D) regions by using selective epitaxy. This chapter presents an overview of implementation, modeling, and pattern dependency of selective epitaxy for S/D application in CMOS. The focus is also on the wafer in and ex situ cleaning prior to epitaxy, integrity of gate, and selectivity mode.

Keywords: selective epitaxy, SiGe, RPCVD, CMOS

#### 1. Introduction

Selective epitaxy of SiGe material is considered as one of the most important steps in the CMOS processing. This type of growth method was already discovered and highlighted in the 1990s with a focus on optimizing the growth parameters to improve the layer quality of Si/SiGe multi-layers [1–4]. The outcome of the initial works showed that {113} and {110} facet planes were mostly dominant, whereas other facet planes, e.g., {119} and {018}, could also appear at certain growth conditions. The activation energy for the growth rate on facet planes (Rhkl) was also calculated for growth temperature of 700–850°C. No significant change in the activation energy of deposition on {hkl} surfaces compared to (100) one was observed showing a similar kinetic growth ruled over these facet planes [1].

© 2018 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

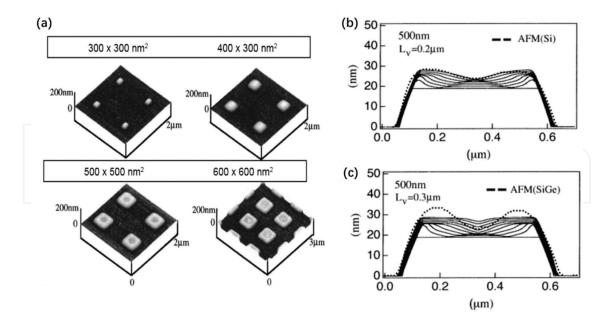

The facet formation results in a pileup shape at the edge of the epi-layer close to the oxide (see **Figure 1a–c**) [5–7]. The reason behind forming this pile shape is the diffusion of incoming Si or Ge atoms on the faceted surface is higher than those on the (001) surface at the central part of the oxide opening. This means that the molecules may move toward the central part, and if their diffusion length at a certain growth temperature is shorter than the opening size, a pileup shape is formed.

More detailed studies about facet formation showed the existence of chlorine during the epitaxy is the main factor dominating the growth rate for both Si and SiGe; however, the formation of the facets is correlated with the growth conditions and pattern geometry.

The application of SiGe as embedded layer source and drain (S/D) of pMOS was presented in year 2000 when (S/D) junctions were formed by a dry etch followed by the growth of highly B-doped SiGe [8]. This idea arose attention since no dopant implantation and post annealing for activation were necessary when the in situ doping of SiGe layer could provide high-quality epi-layers.

Later, the embedded SiGe layers were used as stressor material in the S/D regions to create uniaxial strain in the channel region. As the result of induced strain, carrier mobility in the channel is significantly improved. For the first time, Si<sub>0.83</sub>Ge<sub>0.17</sub> layers were integrated by Intel in 90 nm technology node in 2003 [9], and since that year, the Ge content (or strain amount) was continuously increased in each new coming technology node up to 45% in 22 nm technology node [10, 11]. During this evolution of CMOS, a revolutionary design was introduced when the planar type of transistors was abandoned and three-dimensional (3D) transistors were implemented [12]. Such nanoscale 3D transistors were initially called Tri-Gate, but later

**Figure 1.** (a) AFM pictures of 6 nm selectively grown SiGe on 18 nm Si buffer layers grown at 740°C. The oxide layer has been removed and SiGe layers are in mesa shape. (b) and (c) show the cross section of simulated and the experimental cross-sectional profile (dotted line) for Si and SiGe layers, respectively [5].

this notation was changed to FinFETs to merge with the other groups' suggestion. In these transistors, selective epitaxy of SiGe layer was used to raise the S/D regions.

A drawback with selective epitaxy growth is that the SiGe layer profile is dependent on shape, size, and density of the oxide openings of S/D in a chip. This problem affects also the B concentration in SiGe since the incorporation of B is dependent on both the growth rate and the Ge content [13–21].

SiGe as channel material has been also proposed in the SiGe/Si vertical nanowire transistors when the lateral downscaling will finally reach the end of technology roadmap. In order to have a full control on the carrier transport in the channel region, gate-all-around (GAA) design has been proposed [22].

#### 2. Chemical vapor deposition (CVD) technique

In the semiconductor industry, there are many different materials need to be grown during the device processing. CVD is also a process in which gaseous chemical precursors have chemical reactions on the wafer surface and deposit a layer of solid thin film. The rest of the by-products that are in gas phase can be easily pumped and leave the reaction surface. Among these CVD deposited thin films, SiGe is a key material, which offers the applications in a wide range of CMOS devices.

CVD is practiced in a variety of types, which are classified by the operating pressure:

- 1. Atmospheric pressure CVD (APCVD)—CVD at atmospheric pressure

- 2. Reduced-pressure CVD (RPCVD)—CVD at torr pressure

- 3. Low-pressure CVD (LPCVD)—CVD at mTorr pressure

- 4. Ultrahigh vacuum CVD (UHVCVD)—CVD at  $10^{-8}$  torr pressure

Among these CVD techniques, RPCVD has shown the highest output, and it is accepted by semiconductor industry for epitaxy of Si and SiGe films for IC mass production.

For RPCVD, several precursors are available in the market for the Si growth such as silane  $(SiH_4)$ , dichlorosilane  $(SiH_2Cl_2)$ , trichlorosilane  $(SiHCl_3)$ , tetrachlorosilane  $(SiCl_4)$ , disilane  $(Si_2H_6)$ , and trisilane  $(Si_3H_8)$ . Germane  $(GeH_4)$  and digermane  $(Ge_2H_6)$  are the common sources for Ge to grow Si<sub>1-x</sub>Ge<sub>x</sub>. The most commonly used precursors for p- and n-type doping are diborane  $(B_2H_6)$ , phosphine  $(PH_3)$ , and arsine  $(AsH_3)$ , respectively. As $(GeH_3)_3$  is a gas source which is also used for n-type doping of SiGe layers at low growth temperature. These sources are usually diluted in H<sub>2</sub>. For Sn growth, SnD<sub>4</sub> and SnCl<sub>4</sub> are the most practical and common sources [23]. Methylsilane  $(SiH_3CH_3)$  is widely used for carbon doping in Si and SiGe layers. Meanwhile, HCI and Cl<sub>2</sub> are the precursors used as the etch reactant to obtain the selectivity during the selective process.

#### 3. Ex- and in-situ cleaning

The wafer cleaning process before the epitaxy has an important role for the epitaxy quality. The purpose of epitaxy is to duplicate the substrate atomic columns in deposition of a layer. Therefore, the presence of SiO<sub>2</sub>, carbon and polymer residuals has to be removed from the Si surface [24].

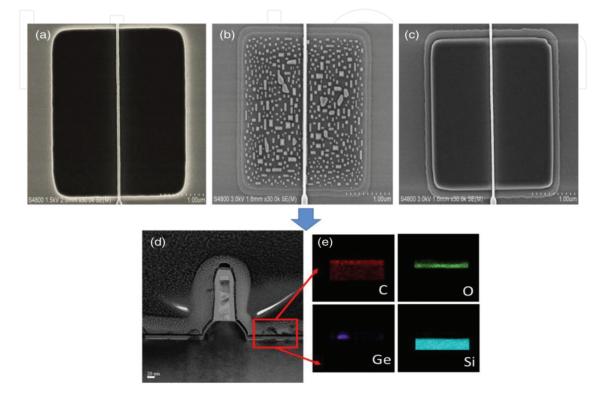

As an example, **Figure 2** shows the micrographs of the samples prior and after the SiGe selective epitaxy. The presence of carbon residuals on Si surface is commonly formed during the plasma dry etch of oxide openings. The SiGe epitaxial layer can be only grown on the clean surfaces of Si, and the growth occurs through nucleation as shown in **Figure 2b** and **d**. The TEM EDS mapping analysis from the cross section of S/D areas in **Figure 2e** confirms the presence of carbon and oxygen residuals on the initial Si surface. Meanwhile, a standard chemical cleaning will remove all undesired impurities, and a two-dimensional SiGe layer could be grown successfully as shown in **Figure 2c** [25]. There are many different cleaning methods for Si wafers as following:

SPM: H<sub>2</sub>SO<sub>4</sub> + H<sub>2</sub>O<sub>2</sub> (4:1)

DHF: HF + DIW (1–2%)

HPM:  $HCl + H_2O_2 + DIW$  (1:1:6)

APM:  $NH_4OH + H_2O_2 + DI - H_2O$  (1:1:5)

where DIW stands for deionized water. A diluted hydrofluoric acid in DIW (1% DHF) removes the native oxide, and the wafers are ready to be placed in the load locks of epi-reactor [26].

Later, an in situ cleaning in RPCVD reactor is required to remove the native oxide on the exposed Si surface. This process usually occurs at high temperature such as 1000–1100°C for monitoring Si wafers; meanwhile, for the patterned substrates, this is remarkably at lower temperatures (850–950°C).

SiGe material is grown in a recess in S/D regions in nanoscale transistors. The recess is formed by wet etch, and its shape can be rounded, sigma, or trapeze, and then the in situ is needed not only in removing the contaminants from the Si surface but also in preserving the recess shape. High annealing treatment results in Si loss and affects the recess shape. This is due to the thermal mismatch between Si and SiO<sub>2</sub> where Si reflows in the recess region. Si loss is a critical problem for the short-channel length transistors.

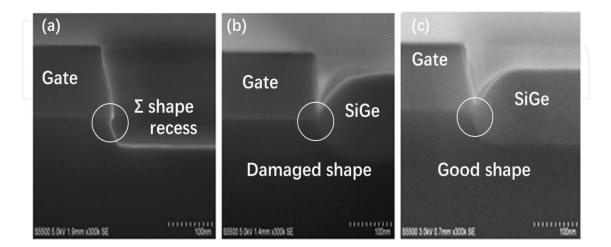

In conclusion, an appropriate low annealing temperature is sought to have a trade-off between all these requirements. **Figure 3** shows the results of in situ experiments on the quality of epilayers and the recess shape at different annealing temperatures. In these experiments, 800°C for 7 min is recognized as the minimum temperature (and enough annealing time) to preserve the shape and improve the high quality of epi-layer [27].

The in situ annealing for three-dimensional (3D) transistors, e.g., FinFET, becomes more critical where the Si fin is small and any damage has a significant effect on the transistor performance.

High-quality SiGe is required to be selectively grown on the S/D to induce the strain into the channel. Before the growth, the surface of Si fin has to be free of native oxide or any residual of impurities [28].

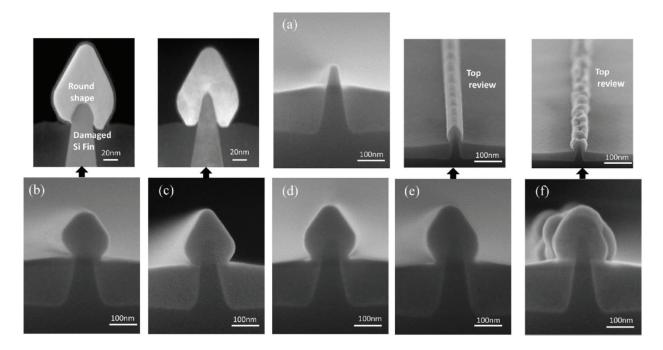

**Figure 4a** shows the HRTEM cross-sectional image of as-processed Si fin. Then the prepared samples were baked at different temperatures ranging from 740 to 825°C prior to epitaxy [29].

**Figure 2.** HRSEM images showing cross section of a planar transistor with 22 nm gate length (a) prior to SiGe growth and after SiGe epitaxy (b) with poorly cleaned Si surface and (c) with cleaned Si surface and (d) TEM cross section of sample in (b) and (e) TEM EDX mapping of sample in (b) [25].

**Figure 3.** SEM images showing cross section of different prebaking condition samples (a) prior to prebaking, (b) prebaking temperature at 825°C, and (c) prebaking temperature at 800°C.

**Figure 4.** HRTEM and SEM cross-sectional images of the Si fins with different prebaking temperatures as follows: (a) the processed Si fin and annealed at (b) 825°C, (c) 800°C, (d) 780°C, (e) 760°C, and (f) 740°C [29].

**Figure 4b** reveals a serious damage on Si fin shape where the height of the fin has been shrunk and the top of the fin became rounded. Although the shape of Si fins was changed, SiGe layer could still be grown with reasonable quality. The irregularity of Si fins' shape at high temperature annealing was originated from Si migration and thermal mismatch between Si and SiO<sub>2</sub>. Therefore, the lower baking temperature is chosen. The samples with 800 and 780°C prebaking in **Figure 4c** and **d**, respectively, had also high-quality Si fins and SiGe layers.

In general, an appearance for a successful SiGe growth is that the shape for layer coverage over the Si fin should be symmetric. The symmetry is important since it determines the uniformity of strain over the Si fins. Among the micrographs, **Figure 4e** has symmetric feature of SiGe layer, but this degrades by lowering the prebaking temperature to 760°C. **Figure 4f** shows that the surface roughness is the worst when the baking temperature is at 740°C. It is believed that asymmetric shape is a result of the residual native oxide remained on the surface of Si fins.

#### 4. Gate integrity: HCI selectivity

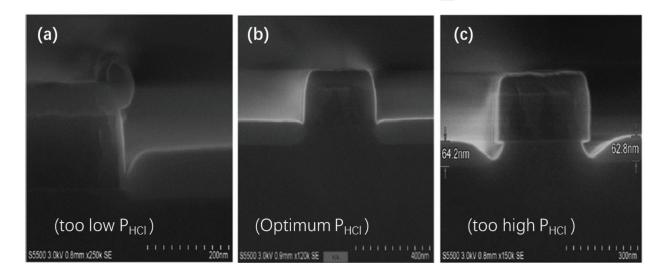

The other importance of SiGe S/D epitaxy is selectivity of the growth. In the patterned structure, the surface of the gate sidewall consists of both oxide and nitride, which makes it difficult to obtain a selective growth, especially on the nitride spacer surface. However, in the worst case, at the top corners of the gate (poly-Si) would appear a "mushroom"-shaped deposition, which is difficult to be removed. To solve this issue and obtain a completely selective growth furthermore, HCl amount during the selective growth is needed. **Figure 5** shows the cross-sectional images from SiGe S/D with long channel gates. When the HCl partial pressure is 50 mTorr, small SiGe nuclides are formed, and ploy-SiGe with a mushroom shape appeared on the top of gate sidewall (**Figure 5a**). **Figure 5b** shows how the selectivity is improved by optimizing HCl partial pressure to 65 mTorr. Based on the previous reports, the high amount of HCl results in higher Ge content and lower growth rate in SiGe epitaxy. It has also demonstrated that an increase of HCl partial pressure reduces the pattern dependency behavior of the growth. However, as **Figure 5c** shows, a ditch forms in vicinity to the gate sidewall when HCl amount is further increased to 80 mTorr. One reason of the non-planar filling of SiGe in S/D regions is due to the (311) facets close to oxide where the growth rate of SiGe on crystal direction (100) is higher than (311).

**Figure 5.** Cross-sectional SEM images of the gate and S/D regions after the SiGe growth when HCl partial pressures were (a) 50 mTorr, (b) 65 mTorr, and (c) 80 mTorr [25].

**Figure 6.** Cross-sectional SEM images of Si fin/SiGe samples when HCl partial pressures were the following: (a) 50 mTorr, (b) 60 mTorr, and (c) 70 mTorr [30].

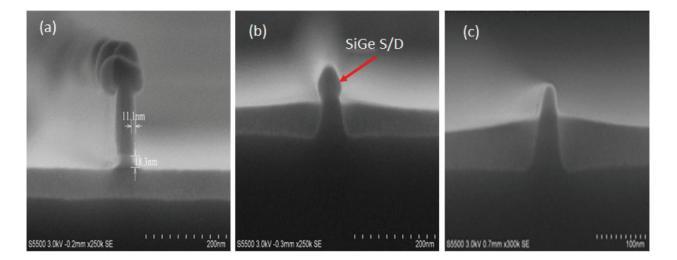

Optimizing HCl partial pressure for 3D FinFETs is a more sensitive task. **Figure 6a–c** shows the SEM images from SiGe/Si fins grown with different HCl partial pressures. As the HCl amount is not enough (50 mTorr) and "mushroom" defects occur on the top of gate sidewalls (**Figure 6a**). However, when the amount of HCl was enhanced to 60 mTorr, a good selectivity for SiGe epitaxy could be achieved (**Figure 6b**). As shown in **Figure 6c**, further increase of HCl partial pressure to 70 mTorr leads to the case when the etch rate is higher than the growth rate resulting in no depositions on the Si fins (**Figure 6c**).

#### 5. Pattern dependency of selective epitaxy

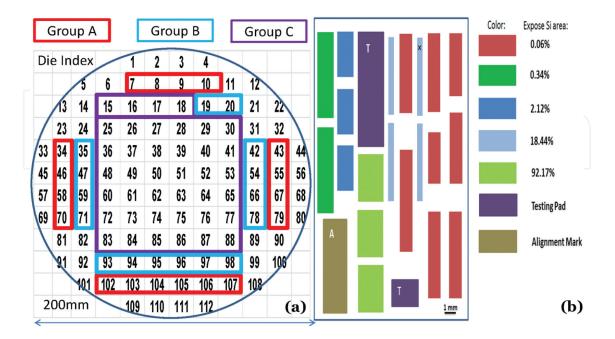

In order to provide a broad knowledge about the local and global pattern dependency, an example is pointed out here when the SiGe layers were grown selectively on S/D regions in transistors with 22 nm gate length [31]. **Figure 7a** shows a schematic of an 8-inch Si wafer containing 112 processed chips. The chips contain arrays of different transistor sizes (or coverage of exposed Si area varies) as shown in **Figure 7b**. This layout has been repeated for all the chips over the wafer.

In this figure, the blue cross marks illustrate the position of a transistor in the chip where the electrical measurements were done in all 112 chips. According to performance of transistors, at least three groups of chips (A, B, and C) with similar electrical characteristics (poor, good, and excellent) over the wafer were distinguished.

The Ge content in SiGe layers in transistors in A, B, and C groups was estimated to be 38, 40, and 35%, respectively by using energy-dispersive spectroscopy (EDS) technique. The growth

**Figure 7.** (a) The schematic picture of an 8-inch test wafer with 112 chips where three groups were marked after the performance of transistors. **Figure 7** (b) shows the layout of one chip where the exposed Si areas are nonuniform, and they are illustrated in different colors [31].

rate of SiGe was 0.58, 0.62, and 0.51 nm/s for transistors A, B, and C, respectively. The variation of Ge content and the growth rate affected also the threading dislocation density (TDD) in A, B, and C group transistors where TDD was estimated to be  $3 \times 10^9$ ,  $1 \times 10^9$ , and  $1 \times 10^8$  /cm<sup>2</sup>, respectively. The amount of TDD is also related to strain relaxation in the epi-layers.

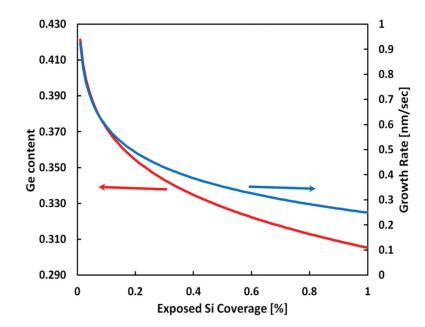

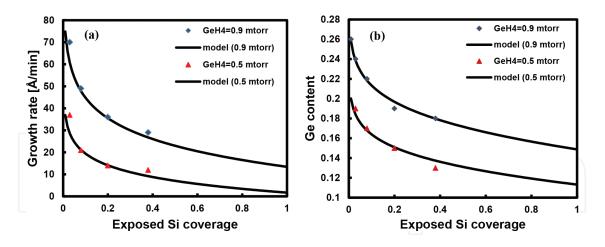

A more detailed information about the pattern dependency versus layout variation is demonstrated in **Figure 8**. The curves indicate that when the density of transistor arrays decreases, then both Ge content and the growth rate increase. The change of layer profile will directly affect the electrical characteristics of the transistor in the chip.

The transistor characteristics provide the data of  $V_{sat}$ ,  $I_{onv}$ ,  $I_{off}$ , drain-induced barrier lowering (DIBL) and carrier mobility as shown in **Table 1** [31].

Figure 8. The calculated SiGe profiles for different exposed Si coverages [31].

| Transistor<br>group | Chip | Measured<br>Ge content | VTsat (V)<br>V <sub>DD</sub> = 1 V | I <sub>on</sub> (μΑ/μm) | I <sub>off</sub> (nA/μm) | DIBL (mV) | Mobility<br>(cm <sup>2</sup> /Vs) |

|---------------------|------|------------------------|------------------------------------|-------------------------|--------------------------|-----------|-----------------------------------|

| A                   | 8    | 55                     | -0.46                              | 263                     | 0.34                     | 75.4      | 24                                |

|                     | 9    | 0.38                   | -0.54                              | 111                     | 0.24                     | 91.3      | 13                                |

|                     | 10   |                        | -0.56                              | 86                      | 0.47                     | 112       | 9                                 |

| В                   | 71   |                        | -0.39                              | 407                     | 0.82                     | 101       | 36                                |

|                     | 82   | 0.40                   | -0.39                              | 420                     | 0.86                     | 90        | 37                                |

|                     | 92   |                        | -0.39                              | 405                     | 0.65                     | 96        | 35                                |

| С                   | 27   |                        | -0.32                              | 598                     | 4.8                      | 115       | 65                                |

|                     | 38   | 0.35                   | -0.30                              | 618                     | 9.8                      | 123       | 71                                |

|                     | 50   |                        | -0.28                              | 619                     | 10.2                     | 119       | 75                                |

**Table 1.** A summary of electrical data for three transistor groups A, B, and C.

It is well known that the presence of misfit dislocations is a sign of strain relaxation in the epilayer. In **Table 1**, transistors in group C have the best electrical performance compared to the others since the Ge content is lowest as well as the defect density. For example, the mobility values are remarkably high for this group.

It is important to emphasize here that the transistor profile is not optimized in all these groups; therefore, the electrical values are not impressive, but only the pattern dependency of epitaxy was in the interest of the discussions.

#### 6. Kinetics of SiGe selective growth

The serious problem with integration of selective epitaxy growth is pattern dependency. The origin of pattern dependency behavior is the nonuniform consumption of reactant gas molecules over the patterned wafer [13–19, 21, 31]. The kinetics of growth is explained by gas molecules move in a laminar flow over the wafer forming boundaries [32].

In CVD, the gas steam through the reactor quartz is under a friction force with the stationary susceptor/substrate, creating stagnant gas boundaries during the gas flow. Gas molecules diffuse/are being attracted downward through the gas boundaries toward the susceptor and finally are consumed on the Si wafer. The length of the attraction force on the gas molecules over the wafer was estimated in the range of 10–15 mm for a total pressure of 20–40 torr in the CVD reactor [33].

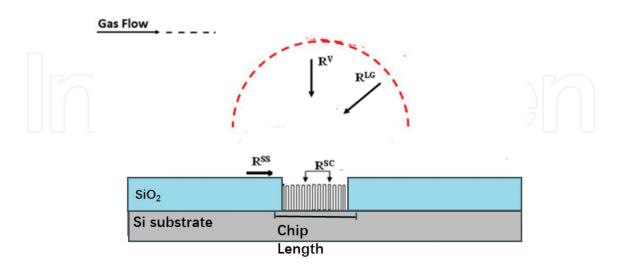

**Figure 9** illustrates a schematic view of the gas kinetics. In this figure, the black arrows illustrate the direction of molecule movement toward the exposed Si areas (transistor arrays in a chip) of a patterned substrate.

Figure 9. Schematic view of gas flow in different directions over a chip containing planar transistors.

The gas molecules are moved in four possible directions toward the exposed Si areas in a patterned substrate and contribute to the selective epitaxy growth as follows:

- **a.** Vertically in gas phase  $(\mathbb{R}^{V})$

- **b.** Laterally in gas phase (R<sup>LG</sup>)

- **c.** Surrounding oxide (or nitride) surface between the chips (R<sup>55</sup>)

- **d.** Oxide surface between the openings within a chip  $(\mathbb{R}^{\mathbb{RC}})$

The total growth rate (R<sub>Tot</sub>) can be written as a sum of contributions from incoming molecules from all four directions as follows:

$$R_{\text{Tot}} = R_{\text{Si}}^{\text{V}} + R_{\text{Si}}^{\text{LG}} + R_{\text{Si}}^{\text{SS}} + R_{\text{Si}}^{\text{SC}} + R_{\text{Ge}}^{\text{V}} + R_{\text{Ge}}^{\text{LG}} + R_{\text{Ge}}^{\text{SS}} + R_{\text{Ge}}^{\text{SC}} - R_{\text{E}}^{\text{V}} - R_{\text{E}}^{\text{LG}} - R_{\text{E}}^{\text{SS}} - R_{\text{E}}^{\text{SC}}$$

(1)

In Eq. (1), R<sup>SS</sup> and R<sup>SB</sup> are changed due to layout variation of the chip, and they are the main components behind the pattern dependency behavior.

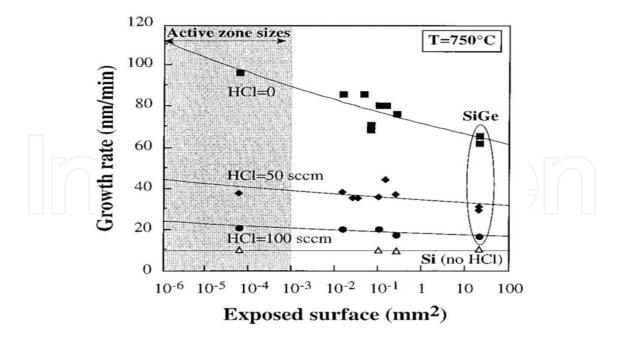

Many studies have tried to decrease the pattern dependency by optimizing the growth parameters e.g., applying high HCl partial pressure or low total pressure during epitaxy [34]. The effect of high HCl is to terminate the lateral components in Eq. (1). The success to reduce the pattern dependency by increasing HCl partial pressure is good; however, it is not effective to eliminate the pattern dependency problem. This method demands high HCl partial pressure which leads to very low growth rate as shown in **Figure 10**.

**Figure 10.** Growth rate of SiGe vs. exposed areas in the chip for the growth at 750°C. The precursor parameters for SiGe growth were the following: (Ge/Si) g = 0.0125, DCS = 200 sccm, and HCl = 0, 50, and 100 sccm [34].

Another method to decrease pattern dependency is proposed to increase the hydrogen carrier gas as well as apply low growth pressure. In this way the number of atoms coming laterally is decreased, but high hydrogen gas demands a better safety of the epi-tool [21].

There is another approach to deal with pattern dependency where an empirical model calculates the layer profile of SiGe and later the layout can be modified for a uniform deposition over the chip or wafer. Such a model has to calculate the components in Eq.(1) where diffusion, adsorption, and desorption of atoms during epitaxy have to considered.

#### 7. Modeling of SiGe selective growth

One of the early works for modeling of Si epitaxy was presented by Meng Tao et al. [35]. The scaffold of the model is based on Maxwell distribution function for the molecules impinging to a surface during epitaxy. In this case, in epitaxy the number of the reactant molecules/unit time (*dn*) with an activation energy in an interval of ( $E_A$ ,  $E_A + dE_A$ ) incoming to a unit area according to Eq. (2):

$$dn = 8\pi N_m \left(\frac{1}{2\pi m_m k_b T}\right)^{\frac{3}{2}} m_m E_A exp\left(-\frac{E_A}{k_b T}\right) dE_K$$

(2)

where  $N_m$  and  $m_m$  are the number of molecules/unit volume and are the mass of the reactant molecules in the gas. Si growth is the simplest epitaxy where dichlorosilane (SiCl<sub>2</sub>) is used as precursor. For SiH<sub>2</sub>Cl<sub>2</sub> epitaxy, the chemical reactions occur through Cl dissociation and are written as follows:

$$SiH_2Cl_2(g) \rightarrow SiCl_2 + H_2(g)$$

(R1)

$$SiCl_2 \rightarrow SiCl + Cl$$

(R2)

The growth rate can be calculated by integrating Eq. (2), and it is obtained by:

$$R = \frac{n}{N_0} = \beta \frac{\left(1 - \theta_{H(Si)} - \theta_{Cl(Si)}\right)}{N_0} \frac{P_{SiH_2Cl_2}}{\left(2\pi m_{SiH_2Cl_2} k_b T\right)^{\frac{1}{2}}} \left(\frac{E_{SiH_2Cl_2}}{k_b T} + 1\right) \exp\left(-\frac{E_{SiH_2Cl_2}}{k_b T}\right)$$

(3)

where  $\beta$  is a unitless constant and  $\theta$ ,  $P_{SiH_2Cl_2}$ , m, N<sub>0</sub>, and  $E_{SiH_2Cl_2}$  are the coverage of hydrogen or chlorine on Si surface, partial pressure of DCS, molecular mass of DCS, number of Si atoms in a unit volume of crystal, and activation energy for the growth, respectively.

For selective epitaxy in the presence of HCl, the growth rate is decreased, and it can be:

$$R_T = R_{Si}^V - R_E^V \tag{4}$$

Experimental results show that the etch rate is not linearly dependent on HCl partial pressure  $(P_{HCl})$  parameter and it has a sublinear relationship  $(P_{HCl})$ . This behavior could be referred

to the fact that all chlorine atoms may not participate during the etch process. Therefore, Eq. (3) is modified as follows:

$$R_{T} = \beta \frac{\left(1 - \theta_{H(Si)} - \theta_{Cl(Si)}\right)}{N_{0}} \frac{P_{SiH_{2}Cl_{2}}}{(2\pi m_{SiH_{2}Cl_{2}}k_{b}T)^{\frac{1}{2}}} \left(\frac{E_{SiH_{2}Cl_{2}}}{k_{b}T} + 1\right) \exp\left(-\frac{E_{SiH_{2}Cl_{2}}}{k_{b}T}\right) \\ \times -\frac{\gamma}{N_{0}} \frac{P_{HCl}^{0.596}}{(2\pi m_{HCl}k_{b}T)^{\frac{1}{2}}} \left(\frac{E_{Etching}}{k_{b}T} + 1\right) \exp\left(-\frac{E_{Etching}}{k_{b}T}\right)$$

(5)

where  $\gamma$  is a unitless S constant which relates to the HCl molecule distribution in the CVD chamber. The activation energy of etching part is estimated to be 37.5 Kcal/mol. This value lies between 22 and 44 Kcal/mol which is the needed energy to break one or two Si-Si bonds.

For the growth of SiGe layers in the presence of HCl,  $GeH_4$  precursor has been introduced into the CVD chamber. In this case, Eq. (4) should be written as follows:

$$R_T = R_{Si}^V + R_{Ge}^V - R_E^V \tag{6}$$

The SiGe epitaxy is significantly different than Si epitaxy, since the presence of Ge atoms increases the growth rate.

The growth rate is increased due to two reasons; at first, the activation energy for SiGe deposition is lowered when Ge is added during epitaxy. The activation energy for Ge is 0.61 eV compared to 2.08 eV for Si, and for SiGe, this value should lie between Si and Ge ones. At second, the presence of Ge increases the available sites (or dangling bond sites) on the Si surface owing to increase of desorption energy of hydrogen and chlorine from Si surface. In this case, Si atoms can easily find the available sites and bind to the lattice, and therefore the growth rate is increased. The above reasons make the SiGe growth more complicated than Si, and therefore Eq. (6) cannot simply be used for SiGe epitaxy. In this case, a coefficient "m" is implemented, and the revised equation for SiGe growth in the presence of HCl is given by:

$$R_T = R_{Si/Si}^V + R_{Ge/Si}^V + m R_{Ge/Si}^V - R_E^V$$

(7)

The full form of equation for the SiGe growth rate can be obtained from:

$$R_{T} = -\beta \frac{\left(1 - \theta_{H(Si)} - \theta_{Cl(Si)}\right)}{N_{0}} \frac{P_{GeH_{4}}}{\left(2\pi m_{SiH_{2}Cl_{2}}k_{b}T\right)^{\frac{1}{2}}} \left(\frac{E_{SiH_{2}Cl_{2}on Si}}{k_{b}T} + 1\right) \exp\left(-\frac{E_{SiH_{2}Cl_{2} on Si}}{k_{b}T}\right) + \chi \frac{(1 + m)\left(1 - \theta_{H(Si)} - \theta_{Cl(Si)}\right)}{N_{0}} \frac{P_{GeH_{4}}}{\left(2\pi m_{GeH_{4}}k_{b}T\right)^{\frac{1}{2}}} \left(\frac{E_{GeH_{4}on Si}}{k_{b}T} + 1\right) \exp\left(-\frac{E_{GeH_{4}on Si}}{k_{b}T}\right)$$

(8)

$$\times -\frac{\gamma}{N_{0}} \frac{P_{HCl}^{0.596}}{\left(2\pi m_{HCl}k_{b}T\right)^{\frac{1}{2}}} \left(\frac{E_{Etching}}{k_{b}T} + 1\right) \exp\left(-\frac{E_{Etching}}{k_{b}T}\right)$$

where  $\chi$  is a constant which depends on the gas property. In above equation, the m coefficient is estimated to be 2 for growth temperatures 600–725°C [36].

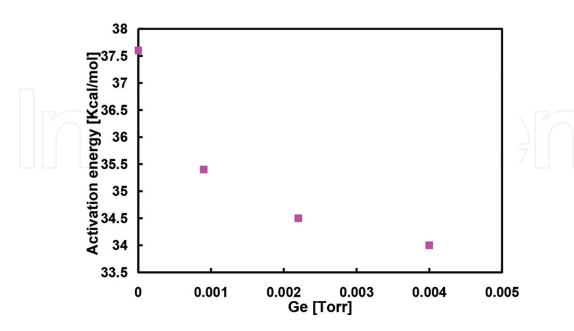

A series of input parameters, e.g., Ge, Si, and HCl partial pressures, can be inserted in Eq. (8), and the etch rates during SiGe epitaxy can be extracted [37]. The experimental data show Arrhenius curves, and the activation energy can be obtained from the slope of these curves. The results show that the activation energy is decreased with increasing Ge partial pressures as shown in **Figure 11**. This outcome could be predicted since the strength of atomic bond in Si matrix becomes weaker with increasing Ge content (or strain).

The dependence of activation energy to Ge partial pressure is expressed as:

$$E_{\text{Etching}} = E_{a, \text{Etching}(\text{Si})} e^{-12.535 P_{\text{GeH}_4}}$$

(9)

where  $E_{a,Etching(Si)}$  is the activation energy for etch of Si. It is worth mentioning here that the activation energy in **Figure 11** differs from the previously reported values to etch SiGe bulk materials [38]. This difference in activation energies can be explained by the fact that the energies to etch SiGe in bulk form and during SiGe epitaxy are entirely different processes.

The Ge content, x in  $Si_{1-x}Ge_x$  layers, can be obtained from Ge and Si partial pressures using the following [16]:

$$\frac{x^2}{1-x} = \sigma \left( \frac{P_{GeH_4} - (1-\eta)P_{HCl}}{P_{SiH_2Cl_2} - \eta P_{HCl}} \right)$$

(10)

where  $\sigma$  is a constant which links to chemical reactions in CVD reactor and  $\eta$  is a reaction rate coefficient which lies in a range between 0.9 and 1 depending on HCl partial pressure. The experimental data demonstrate that  $\eta$  is 1 when HCl partial pressure is lower than DCS partial pressure; otherwise it is ~0.9 for higher HCl pressures. The constant  $\sigma$  is related to adsorption and desorption of the main species during CVD, and it is written in the following equation below:

Figure 11. Activation energy vs. Ge partial pressures for etch part during SiGe epitaxy.

Selective Epitaxy of Group IV Materials for CMOS Application 55 http://dx.doi.org/10.5772/intechopen.76244

$$\sigma = \frac{k_{a, GeH_2} \times k_{d, H}}{k_{a, SiCl_2} \times k_{d, Cl}} = Aexp\left(\frac{E}{kT}\right)$$

(11)

The adsorption energy difference ( $E_{a,SiCl2}-E_{a,GeH2}$ ) is ~0.1 eV [39], and the desorption energy difference is ~0.48 eV [40]. Then, the total activation energy is valued to 0.58 eV which is close to the derived energy value (0.697 eV) [37].

Until now, the vertical components in Eq. (1) have been discussed and calculated. The lateral components can be derived in the same way when these parameters are used for the patterned substrates [37]. A few assumptions have to be considered in order to make the calculations easier. At first, it is defined that a wafer has a global pattern when the chip layout is uniform and it is repeated over the entire wafer.

At second, the HCl partial pressure has to be enough to ensure the selectivity of the growth.

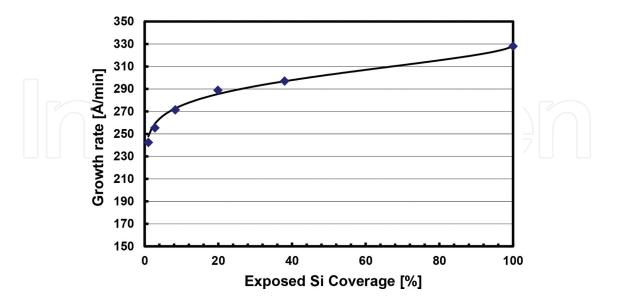

The results from Si deposition on patterned substrate have demonstrated that the growth rate is decreased when the coverage of the exposed Si areas becomes smaller. **Figure 12** demonstrates the growth rate from five globally patterned wafers with different exposed areas. The figure confirms the behavior of Si epitaxy is different than SiGe epitaxy [41, 42].

This discrepancy is due to the presence of  $R_{HCl}^{SC}$  in Eq. (1), which is formed through the lateral diffusion of Cl atoms on the oxide surface in a fully selective mode. The contribution of this component was found to be inversely related to the exposed Si areas:

$$P_{HCl}^{SC} = AP_{HCl} \ln\left(\frac{1}{c}\right) \tag{12}$$

**Figure 12.** Growth rate vs. coverage of exposed Si for five different globally patterned wafers in total pressure of 20 torr. The  $P_{DCS}$  and  $P_{HCI}$  were 120 and 20 mTorr, respectively [37].

where c stands for the coverage of exposed Si areas of the chip and A is a parameter that depends on which type of mask is used for isolation material. Thus, Eq. (15) can be reformulated as follows:

$$R_{T} = \beta \frac{\left(1 - \theta_{H(Si)} - \theta_{Cl(Si)}\right)}{N_{0}} \frac{P_{SiH_{2}Cl_{2}}}{(2\pi m_{SiH_{2}Cl_{2}}k_{b}T)^{\frac{1}{2}}} \left(\frac{E_{SiH_{2}Cl_{2}on Si}}{k_{b}T} + 1\right) \exp\left(-\frac{E_{SiH_{2}Cl_{2}on Si}}{k_{b}T}\right) \\ \times -\frac{\gamma}{N_{0}} \frac{P_{HCl}^{0.596}}{(2\pi m_{HCl}k_{b}T)^{\frac{1}{2}}} \left(\frac{E_{Etching}}{k_{b}T} + 1\right) \exp\left(-\frac{E_{Etching}}{k_{b}T}\right) - \frac{\gamma}{N_{0}} \frac{(AP_{HCl}\ln(1/c))_{HCl}^{0.596}}{(2\pi m_{HCl}k_{b}T)^{\frac{1}{2}}} \left(\frac{E_{Etching}}{k_{b}T} + 1\right)$$

(13)

$$\times \exp\left(-\frac{E_{Etching}}{k_{b}T}\right)$$

For SiGe epitaxy, GeH<sub>4</sub> precursor is introduced to the reactant gases which increases the Cl desorption, and therefore, the lateral diffusion of Cl becomes minor [43].

In a similar way, the later component for Ge atoms on the oxide surface  $P_{Ge}^{SC}$  can be written as:

$$P_{Ge}^{SC} = BP_{GeH_4} \ln\left(\frac{1}{c}\right) \tag{14}$$

where B is a parameter similar to Eq. (15) which is dependent on the mask material and c is the exposed Si coverage of the chip. Due to the lateral diffusion of Ge atoms on the oxide surface, an activation energy of 0.1 eV is added to the activation energy of the growth. In this case, the total growth rate for SiGe epitaxy is written as:

$$R_{T} = \beta \frac{\left(1 - \theta_{H(Si)} - \theta_{Cl(Si)}\right)}{N_{0}} \frac{P_{GeH_{4}}}{\left(2\pi m_{SiH_{2}Cl_{2}k_{b}}T\right)^{\frac{1}{2}}} \left(\frac{E_{SiH_{2}Cl_{2}on Si}}{k_{b}T} + 1\right) \exp\left(-\frac{E_{SiH_{2}Cl_{2} on Si}}{k_{b}T}\right) + \chi \frac{\left(1 + m\right)\left(1 - \theta_{H(Si)} - \theta_{Cl(Si)}\right)}{N_{0}} \frac{P_{GeH_{4}}}{\left(2\pi m_{GeH_{4}}k_{b}T\right)^{\frac{1}{2}}} \left(\frac{E_{GeH_{4}on Si}}{k_{b}T} + 1\right) \exp\left(-\frac{E_{GeH_{4}on Si}}{k_{b}T}\right) + \chi \frac{\left(1 + m\right)\left(1 - \theta_{H(Si)} - \theta_{Cl(Si)}\right)}{N_{0}} \frac{\left(BP_{GeH_{4}}\ln\left(\frac{1}{c}\right)\right)}{\left(2\pi m_{GeH_{4}}k_{b}T\right)^{\frac{1}{2}}} \left(\frac{E_{GeH_{4}on Si} + 0.1eV}{k_{b}T} + 1\right) \exp\left(-\frac{E_{GeH_{4}on Si} + 0.1eV}{k_{b}T}\right) - \frac{\gamma}{N_{0}} \frac{P_{HCl}^{0.596}}{\left(2\pi m_{HCl}k_{b}T\right)^{\frac{1}{2}}} \left(\frac{E_{Etching}}{k_{b}T} + 1\right) \exp\left(-\frac{E_{Etching}}{k_{b}T}\right)$$

(15)

The lateral contribution of Ge on the oxide surface has to be considered in the composition in Eq. (12) as well, and therefore the equation is modified as:

$$\frac{x^2}{1-x} = \sigma exp\left(\frac{0.7eV}{k_bT}\right) \left(\frac{P_{GeH_4} + (BP_{GeH_4}\ln(1/c)) - (1-\eta)P_{HCl}}{P_{SiH_2Cl_2} - \eta P_{HCl}}\right)$$

(16)

**Figure 13a** and **b** show the experimental and calculated outcomes for the SiGe selective epitaxy. A good agreement between the experimental data and the calculated one is observed for patterned wafers.

**Figure 13.** (a) Growth rate vs. chip exposed Si coverage and (b) Ge content vs. chip exposed Si coverage for SiGe layers grown at 20 torr on wafers with different global patterns. The applied  $P_{SiH2Cl2}$  and  $P_{HCl}$  were 60 and 20 mTorr, respectively [37].

Until now, all calculations were for chips in wafers with global layout which in fact is an ideal case; however, for many cases, the layout of chips is nonuniform. When the layout varies the gas consumption over, the chip (wafer) becomes nonuniform. The part of chip with largest exposed area would attract stronger the surrounding atoms toward itself compared to the other part of the chip. This means that there is an interaction between different areas in the chip where the growth rate at part of the chip with highly exposed Si area ( $R_{Trap}$ ) has an influence in neighboring parts ( $R_{surr}$ ). The interaction range between two individual parts is denoted " $\tau$ (c)" where parameter "c" stands for exposed Si coverage in the chip. Then the growth rate of any part of chip which is located at a distance d (R(d)) can be written according to this interaction theory as follows [19]:

$$R(d) = R_{Trap} + \left(R_{Surr} - R_{Trap}\right) \left(1 - \exp\left(\frac{-d}{\tau(c)}\right)\right)$$

(17)

Parameter " $\tau$ " depends on the exposed coverage of the chip since the dangling bonds are creating an attraction force which drags the gas molecules.

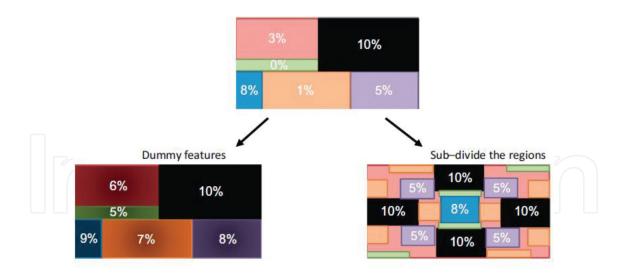

Therefore, the gas consumption has to be uniformly over the chip in order for growth rate to be uniform. In this case, the trap parts have to be distributed over the chip and not isolated. As an example, **Figure 14** shows a nonuniform chip with six regions with exposed Si coverage areas of 0, 1, 3, 8, and 10%. At first, the trap regions are identified as 8 and %10 in this chip since the coverage is highest. Later, the interaction length between the six areas has to be calculated mutually. The condition for uniform gas consumption over this chip can be achieved either by inserting dummy features or by subdividing the trap areas over the chip or both methods.

The modeling of SiGe selective growth for advanced chip layout inaugurates a new window for chipmakers to deposit epi-layers with high quality and high uniformity over the wafer.

Figure 14. Design of chip layout to obtain uniform SiGe deposition.

#### 8. Strain mechanism in group IV materials

Strain is a mechanical deformation which is resulted when a crystal with a lattice mismatch is epitaxially deposited on a substrate. The crystal of the deposited material has to align to the substrate, and as a result, the crystal is deformed. Strain is categorized in two types depending on whether the direction of the applied force is inward (compressive strain) or outward (tensile strain). Therefore, the strain is a hidden energy in the crystal which affects the electrical, mechanical, and optical properties of the semiconductor. Compressive strain, which is generated by SiGe layers by using selective epitaxy, has been the core discussion in this book chapter. Compressive strain is applied in pMOS to increase the hole mobility in the channel.

In general, the mobility is defined as:

$$\mu = \frac{q < \tau >}{m^*} \tag{18}$$

where m<sup>\*</sup> stands for the effective mass and  $\tau$  expresses the scattering time for the carriers [11].

The compressive strain splits the heavy and light hole (HH and LH) bands and changes the curvature of these bands. The latter effect is directly related to the decrease of effective mass for holes, whereas the first effect decreases the holes' scattering between the HH and LH bands. Both these effects have direct impact on  $< \tau >$  and m\* [11].

Other ways to describe the transport properties in the channel of transistor in the presence of compressive strain piezoresistance coefficients are commonly calculated. These coefficients are expressed in respect to mobility's fractional variations as:

$$\Delta \mu/\mu \approx |\pi//\sigma// + \pi_{\perp}\sigma_{\perp}| \tag{19}$$

where  $\sigma_{\perp}$  and  $\sigma_{\prime\prime}$  are the transverse and longitudinal stresses and  $\pi_{\prime\prime}$  and  $\pi_{\perp}$  denote for the piezoresistance coefficients in longitudinal and transverse directions. The piezoresistance coefficients can also be written in form of the three fundamental coefficients  $\pi$ 11,  $\pi$ 12, and  $\pi$ 44 [44].

The recent results have demonstrated that compressive strain along <110> has highest piezoresistance coefficients for both (001) and (110) wafers. As a result, <110> channel direction has been mainly applied for industrial applications [45, 46].

### Author details

Guilei Wang<sup>1,2</sup>\*, Henry H. Radamson<sup>1,2,3</sup> and Mohammadreza Kolahdouz<sup>4</sup>

\*Address all correspondence to: wangguilei@ime.ac.cn

1 Key Laboratory of Microelectronics Devices and Integrated Technology, Institute of Microelectronics, Chinese Academy of Sciences, Beijing, People's Republic of China

2 University of Chinese Academy of Sciences, Beijing, People's Republic of China

3 KTH Royal Institute of Technology, Stockholm, Sweden

4 Thin Film Laboratory, Electrical and Computer Engineering Department, University of Tehran, Tehran, Iran

#### References

- [1] Vescan L, Grimm K, Dieker C. Facet investigation in selective epitaxial growth of Si and SiGe on (001) Si for optoelectronic devices. Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena. 1998;16(3):1549-1554

- [2] Dutartre D, Talbot A, Loubet N. Facet propagation in Si and SiGe epitaxy or etching. ECS Transactions. 2006;**3**(7):473

- [3] Drowley CI, Reid GA, Hull R. Model for facet and sidewall defect formation during selective epitaxial growth of (001) silicon. Applied Physics Letters. 1988;**52**:546

- [4] Aoyama T, Ikarashi T, Miyanaga K, Tatsumi T. Facet formation mechanism of silicon selective epitaxial layer by Si ultrahigh vacuum chemical vapor deposition Sf02. Journal of Crystal Growth. 1994;136:349-354

- [5] Kawaguchi K, Usami N, Shiraki Y. Formation of relaxed SiGe<sup>®</sup> lms on Si by selective epitaxial growth. Thin Solid Films. 2000;**369**:126-129

- [6] Ohtsuka M, Suzuki A. Modeling of molecular-beam epitaxy and metalorganic vaporphase epitaxy on nonplanar surfaces. Journal of Applied Physics. 1993;73:7358

- [7] Xiang Q, Li S, Wang D, Wang KL, Couillard JG. Interfacet mass transport and facet evolution in selective epitaxial growth of Si by gas source molecular beam epitaxy. Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures. 1996;14:2381

- [8] Gannavaram S, Pesovic N, Ozturk MC. Low Temperature (<800C) Recessed Junction Selective Silicon-Germanium SourceDrain Technology for sub-70 nm CMOS. Electron Devices Meeting. IEDM Technical Digest. IEEE International 2000. p. 437; 2000

- [9] Ghani T, Armstrong M, Auth C, Bost M, Charvat P, Glass G, Hoffiann T, Johnson K, Kenyon C, Klaus J, McIntyre B, Mistry K, Murthy A, Silberstein M, Sivakumar S, Smith P, Zawadzki K, Thompson S, Bohr M. A 90 nm High Volume Manufacturing Logic Technology Featuring Novel 45 nm Gate Length Strained Silicon CMOS Transistors. Electron Devices Meeting, 2003. IEDM Technical Digest. IEEE International; 2003. pp. 978-980

- [10] Packan P, Al E. High Performance 32 nm Logic Technology Featuring 2nd Generation High-k + Metal Gate Transistor. Electron Devices Meeting. (IEDM). 2009, p. 1

- [11] Radamson HH, Thylen L. Monolithic Nanoscale Photonics-Electronics Integration in Silicon and Other Group 1V Elements; September 1, 2014. Elsevier Science & Technology. San Diego, CA, USA: Elsevier

- [12] Radamson HH, Zhang Y, He X, Cui H, Li J, Xiang J, Liu J, Gu S, Wang G. The challenges of advanced CMOS process from 2D to 3D. Applied Sciences. 2017;7(10):1047

- [13] Hallstedt J, Kolahdouz M, Ghandi R, Radamson H, Wise R. Pattern dependency in selective epitaxy of B-doped SiGe layers for advanced metal oxide semiconductor field effect transistors. Journal of Applied Physics. 2008;103:0549071-0549077

- [14] Fellous C, Romagna F, Dutartre D. Thermal and chemical loading effects in non selective Si/SiGe epitaxy. Materials Science and Engineering B. 2002;89:323-327

- [15] Kolahdouz M, Hallstedt J, Khatibi A, Ostling M, Wise R, Riley DJ, Radamson H. Comprehensive evaluation and study of pattern dependency behavior in selective epitaxial growth of B-doped SiGe layers. IEEE Transactions on Nanotechnology. 2009;8:291-297

- [16] Kolahdouz M, Maresca L, Ostling M, Riley D, Wise R, Radamson H. New method to calibrate the pattern dependency of selective epitaxy of SiGe layers. Solid-State Electronics. 2009;53:858-861

- [17] Hartmann JM, Abbadie A, Vinet M, Clavelier L, Holliger P, Lafond D, Semeria MN, Gentile P. Growth kinetics of Si on fullsheet, patterned and silicon-on-insulator substrates. Journal of Crystal Growth. 2003;257:19-30

- [18] Loo R, Wang G, Souriau L, Lin JC, Takeuchi S, Brammertz G, Caymax M. Epitaxial Ge on standard STI patterned Si wafers: High quality virtual substrates for Ge pMOS and III/V nMOS. ECS Transactions. 2009;25(7):335-350

- [19] Kolahdouz M, Ghandi R, Hallstedt J, Osling M, Wise R, Wejtmans H, Radamson H. The influence of Si coverage in a chip on layer profile of selectively grown Si1–xGex layers using RPCVD technique. Thin Solid Films. 2008;517:257-258

- [20] Ghandi R, Kolahdouz M, Hallstedt J, Wise R, Wejtmans H, Radamson H. Effect of strain, substrate surface and growth rate on B-doping in selectively grown SiGe layers. Thin Solid Films. 2008;517:334-336

- [21] Loo R, Caymax M. Avoiding loading effects and facet growth key parameters for a successful implementation of selective epitaxial SiGe deposition for HBT-BiCMOS and high-mobility hetero-channel pMOS devices. Applied Surface Science. 2004;**224**:24-30

- [22] Yakimets D, Eneman G, Schuddinck P, Bao TH, Bardon MG, Raghavan P, Veloso A, Collaert N, Mercha A, Verkest D, et al. Vertical GAAFETs for the ultimate CMOS scaling. IEEE Transactions on Electron Devices. 2015;62:1433-1439

- [23] Radamson HH, Kolahdouz M. Selective epitaxy growth of Si 1-x Ge x, layers for MOSFETs and FinFETs[J]. Journal of Materials Science Materials in Electronics. 2015; 26(7):4584-4603

- [24] Bühler J, Steiner F-P, Baltes H. Silicon dioxide sacrificial layer etching in surface micromachining. Journal of Micromechanics and Micro Engineering. 1997;7(1):R1-R13

- [25] Wang G, Luo J, Qin C, Liang R, Xu Y, Liu J, et al. Integration of highly strained SiGe in source and drain with HK and MG for 22 nm bulk PMOS transistors. Nanoscale Research Letters. 2017;12(1):123

- [26] Abbadie A, Hartmann J-M, Holliger P, Semeria MN, Besson P, Gentile P. Low thermal budget surface preparation of Si and SiGe. Applied Surface Science. 2004;225(1–4):256-266

- [27] Wang G, Moeen M, Abedin A, Kolahdouz M, Luo J, Qin CL, Zhu HL, Yan J, Yin H, Li J, et al. Optimization of SiGe selective epitaxy for source/drain engineering in 22 nm node complementary metal-oxide semiconductor (CMOS). Journal of Applied Physics. 2013; 114:123511

- [28] Wang G, Abedin A, Moeen M, Kolahdouz M, Luo J, Guo Y, et al. Integration of highlystrained sige materials in 14 nm and beyond nodes finfet technology. Solid State Electronics. 2015;103:222-228

- [29] Wang G, Qin C, Yin H, Luo J, Duan N, Yang P, et al. Study of SiGe selective epitaxial process integration with high-k and metal gate for 16/14 nm nodes FinFET technology. Microelectronic Engineering. 2016;163:49-54

- [30] Radamson HH, Luo J, Qin CL, Yin H, Zhu HL, Zhao C, et al. Optimization of selective growth of sige for source/drain in 14nm and beyond nodes FinFETs. International Journal of High Speed Electronics & Systems. 2017;26(01n02):1740003

- [31] Wang G, Moeen M, Abedin A, et al. Impact of pattern dependency of SiGe layers grown selectively in source/drain on the performance of 22 nm node pMOSFETs. Solid-State Electronics. 2015;114:43-48

- [32] Knutson KL, Carr RW, Liu WH, Campbell SA. A kinetics and transport model of dichiorosilane chemical vapor deposition. Journal of Crystal Growth. 1994;**140**:191-204

- [33] Newman AJ, Krishnaprasad PS, Ponczak S, Brabant P. Modeling and Model Reduction for Control and Optimization of Epitaxial Growth in a Commercial Rapid Thermal Chemical Vapor Deposition Reactor. Technical Report 98–45. Institute for Systems Research; 1998

- [34] Bodnar S, de Berranger E, Bouillon P, Mouis M, Skotnicki T, Regolini JL. Selective Si and SiGe epitaxial heterostructures grown using an industrial low-pressure chemical vapor deposition module. Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures. 1997;15:712

- [35] Tao M. Growth kinetics and reaction mechanism of silicon chemical vapour deposition from silane. Thin Solid Films. 1993;223:201-211

- [36] Kühne H. On a substituting, sticking and trapping model of CVD Si<sub>1-x</sub>Ge<sub>x</sub> layer growth. Journal of Crystal Growth. 1992;125:291-300

- [37] Kolahdouz M, Maresca L, Ghandi R, Khatibi A, Radamson HH. Kinetic model of SiGe selective epitaxial growth using RPCVD technique. Journal of the Electrochemical Society. 2011;158:H457

- [38] Bogumilowicz Y, Hartmann JM, Truche R, Campidelli Y, Rolland G, Billon T. Chemical vapour etching of Si, SiGe and Ge with HCl; applications to the formation of thin relaxed SiGe buffers and to the revelation of threading dislocations. Semiconductor Science and Technology. 2005;20:127-134

- [39] Ito S, Nakamura T, Nishikawa S. Reduced-pressure chemical vapor deposition. Applied Physics Letters. 1996;69:1098-1100

- [40] Hierlemann M, Werner C, Spitzer A. Equipment simulation of SiGe heteroepitaxy: Model validation by ab initio calculations of surface diffusion processes. Journal of Vacuum Science B. 1997;15:935

- [41] Radamson H, Kolahdouz M, Ghandi R, Hallstedt J. Selective epitaxial growth of B-doped SiGe and HCl etch of Si for the formation of SiGe:B recessed source and drain (pMOS transistors). Thin Solid Films. 2008;517:84-86

- [42] Kolahdouz M, Adibi PTZ, Farniya AA, Shayestehaminzadeh S, Trybom E, Di Benedetto L, Radamson H. Selective growth of B- and C-doped SiGe layers in unprocessed and recessed Si openings for p-type metal-oxide-semiconductor field-effect transistors application. Journal of The Electrochemical Society. 2010;157:H633

- [43] Suh KY, Lee HH. Ge composition in Si<sub>1-x</sub>Ge x films grown from SiH<sub>2</sub>Cl<sub>2</sub>/GeH<sub>4</sub> precursors. Journal of Applied Physics. 2000;88:4044-4047

- [44] Smith CS. Piezoresistance effect in germanium and silicon. Physical Review. 1954;94(1):42

- [45] Giles MD, Armstrong M, Auth C, Cea SM, Ghani T, Hoffman T, et al. Understanding Stress Enhanced Performance in Intel 90 nm CMOS Technology[C]//VLSI Technology, 2004. Digest of Technical Papers; 2004. pp. 118-119

- [46] Ghani T, Thompson SE, Bohr M, et al. A 90 nm high volume manufacturing logic technology featuring novel 45 nm gate length strained silicon CMOS transistors. In: IEDM Technical Digest; San Francisco, 2003. pp. 11.6.1-11.6.3

IntechOpen