We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

186,000

200M

Our authors are among the

TOP 1% most cited scientists

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

# Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

## Band Gap Modulated Tunnel FET

Brinda Bhowmick and Rupam Goswami

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/intechopen.76098

#### Abstract

This chapter presents bandgap-modulated tunnel field effect transistor (TFET) and discusses its simulation and modeling. A geometry of TFET, the heterojunction TFET, is considered, and different electrical parameters are discussed using Technology Computer Aided Design (TCAD) tool. The effect of the heterojunction on the characteristics is observed through the variations in the length and mole fraction of the pocket layer adjacent to the source. An analytical model is further presented for gate-drain underlap TFET using 2-D Poisson equation and Kane's interband tunneling model. The results are validated with the output from the TCAD tool.

Keywords: heterojunction TFET, TCAD, analytical model, subthreshold swing, tunneling

## 1. Introduction

Tunnel field effect transistor (TFET) is an asymmetrical gated p-i-n device. Unlike thermionic conduction in metal-oxide-semiconductor FETs (MOSFETs), its working principle is based on a band-to-band tunneling (BTBT) mechanism [1, 2]. This amendment results in a reduced sub-threshold swing (SS), low off-state leakage currents, and less short-channel effects. Recently, numerous structural and material designs of TFETs have been proposed with an objective to achieve improvement in subthreshold swing (SS) and off current. A few of them are bandgap-engineered TFETs [3], graphene nanoribbon TFETs [4], gate-engineered TFET [5], and strained silicon-germanium TFETs [6]. Double-gate TFET [7], dual-material gate TFET [8], hetero-gate dielectric TFET [9], and heterojunction TFETs [10] have also been investigated for improved electrical parameters of TFET. Generally, TFETs have a very low current as compared to ITRS requirement. In order to get a high ON current, a high-k gate dielectrics are preferred. High-k gate dielectrics causes improved capacitive coupling between the gate and the source-channel tunnel junction, resulting in an increased current in TFET. Moreover, to decline the effective oxide

© 2018 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

thickness at the tunnel junction, high-k gate oxide is used so that the gate-tunneling current can be reduced. Actually, due to these reasons, the recent trend is to use high-k materials as a better replacement of the conventional  $SiO_2$  (silicon dioxide). On the other hand, it causes a significant ambipolar current. The gate-drain underlap structure in association with heterojunction can be adopted to diminish ambipolar current [2]. A silicon-germanium (SiGe) layer is used at the tunnel junction so that bandgap and tunnel width can be modulated. Electrical parameters have been investigated for various Ge-mole fractions.

Technology Computer Aided Design (TCAD) simulation is a complex iterative mathematical process, and hence various analytical models have been proposed in order to develop a better understanding of the physics-based principles of TFETs and obtain results not constrained by computational time [11]. A number of analytical models based on Poisson equation have been proposed in the study for different geometries [12–14]. In this chapter, a mole fraction-dependent model has been proposed and validated.

This chapter is organized as follows: first, the heterojunction gate-drain underlap tunnel is discussed, and in the second section, the electrical parameters of the heterojunction gate-drain underlap tunnel FET (UL-HTFET) is investigated with the help of TCAD simulation. The third section discusses the physics-based compact model and the validation of the model with simulated results. In the last section, the effect of temperature on the electrical parameters is investigated.

## 2. Heterojunction gate-drain underlap tunnel FET

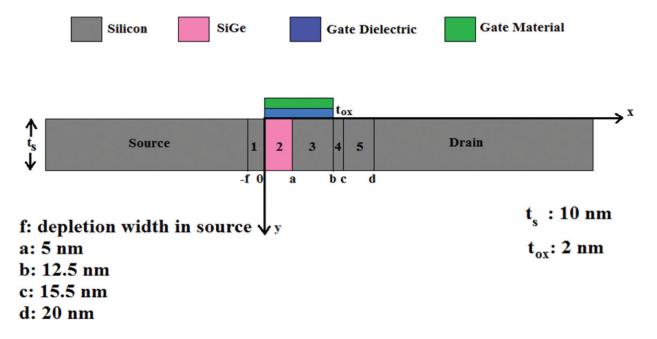

A 2-D structure of the proposed UL-HTFET is shown in **Figure 1**. Here, a p + source and n + drain with an intrinsic channel and a  $\delta p$  + Si<sub>1-x</sub>Ge<sub>x</sub> layer at the source-channel tunnel junction are present. The  $\delta p$  + layer can be replaced by a  $\delta n$  + layer too.

Figure 1. A 2-D geometry of the device (UL-HTFET).

The effect of germanium mole fraction on the UL-HTFET is investigated. Aluminum with work function (4.1 eV) is considered as the gate material. The proposed device spans across a total length of 100 nm with a length of the channel equal to 20 nm. The  $\delta p$  + Si<sub>1-x</sub>Ge<sub>x</sub> layer extends from the source-channel junction up to 1 nm into the channel under the gate. The various doping concentrations are used such as source,  $10^{21}$  cm<sup>-3</sup>; drain, 5 ×  $10^{19}$  cm<sup>-3</sup>;  $\delta p$  + layer,  $10^{18}$  cm<sup>-3</sup>; and intrinsic region,  $10^{16}$  cm<sup>-3</sup>. In n-channel, the operation of TFET positive gate and drain voltages is applied with respect to the source. Here, voltage at the source is considered as the reference voltage.

The tunnel FET works on the principle of band-to-band tunneling. Here, SiGe layer is added at the channel near the source-channel junction to enhance the on-current.

## 3. Simulated results of UL-HTFET

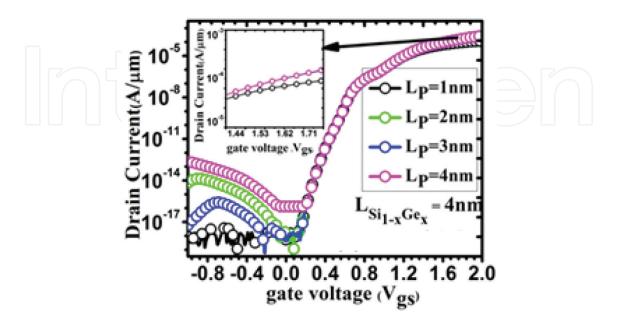

**Figure 2** shows the  $I_{ds}$ - $V_{gs}$  characteristics of the Si/Ge heterojunction UL-HTFET at different lengths of  $L_p$ . When the HTFET is turned on, it shows very high on-current due to the effective bandgap narrowing at the interface of source-channel junction. The  $I_{ds}$ - $V_{gs}$  curves are mainly dependent on n + -doped pocket length ( $L_p$ ) as shown in **Figure 2**; as  $L_p$  gets longer, the effective area for tunneling width is extended for HTFET. However, the low off-state current in UL-HTFET (9.205 × 10<sup>-20</sup> A/µm) when  $L_p$  is less than 2 nm, and this indicates that the ambipolar-tunneling effect at drain channel is suppressed. When  $L_p$  is 2 nm, as observed, the tunneling width becomes extremely thin to concede tunneling current at  $V_{gs} = -0.5$  V. This tunneling current interrupts UL-HTFET device performance at off-state. The low  $I_{off}$  can be achieved at  $L_p = 1$  and 2 nm, and  $I_{on}$  is greatly higher at  $L_p = 4$  nm in TFET. Therefore, an optimum  $L_p$  can be located at 1 nm where high ion is achieved and the leakage is suppressed as shown in  $I_{ds}$ - $V_{gs}$  characteristics.

Figure 2. Transfer characteristics for varying  $L_p$  lengths at  $V_{ds}$  = 0.7 V.

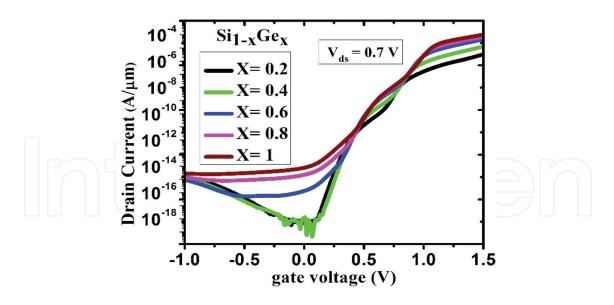

Figure 3.  $I_d$ - $V_{gs}$  characteristics of UL-HTFET with varying Ge-mole fractions.

In **Figure 3**, the I<sub>d</sub>-V<sub>gs</sub> characteristics of the UL-HTFET is shown. The mole fraction of SiGe layer is varied. With germanium mole fraction of 0.4, the best  $I_{on}/I_{off}$  ratio has been achieved  $(10^{12})$ . For Ge-mole fractions below 0.5, the device exhibits a better ratio. As the mole fraction increases beyond 0.5, the properties of the n + layer align more with those of germanium than of silicon. With an increase in mole fraction greater than 0.4, the on-current increases but the increase in off-current is more. This is due to an effective band bending at the source-channel tunnel junction by which the tunnel width can be modulated. For a reduced tunnel width in ON state ( $V_{gs} = 1 \text{ V}$ ), more ON current is achieved. However, at OFF state, the current is due to thermionic emission as the tunnel current is insignificant.

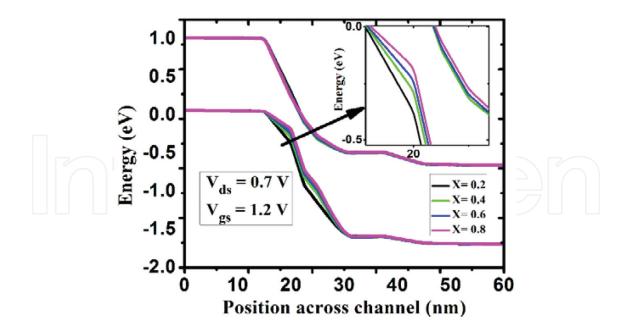

The energy band diagram is plotted at different mole fractions at ON state ( $V_{ds} = 0.7 V$ ,  $V_{gs} = 1.2 V$ ) shown in **Figure 4**. It is observed that at 0.8-mole fraction of germanium, the ON current is more. With an increase in Ge-mole fraction, the tunnel width reduces and hence enhanced ON current is achieved. In the inset of **Figure 4**, the variation of valence band with mole fraction is shown. The conduction band variation is insignificant with mole fraction.

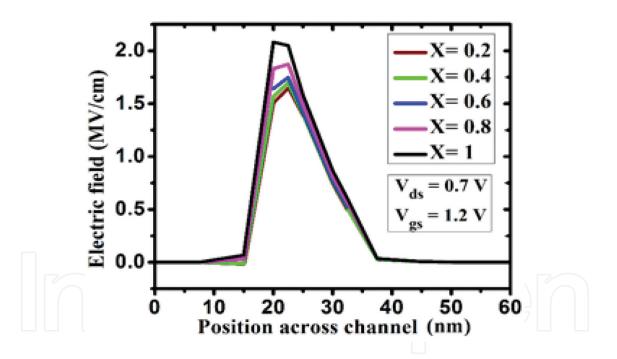

In **Figure 5**, the electric field is shown at different mole fractions. The peak electric field is observed around 20-nm length along the lateral direction. This is the source-channel tunnel junction. A high electric field at this location is due to the presence of a large tunnel barrier. With the increased mole fraction (at x = 1), a highest peak is observed, and hence tunneling probability will increase and be responsible for the increased current in ON state.

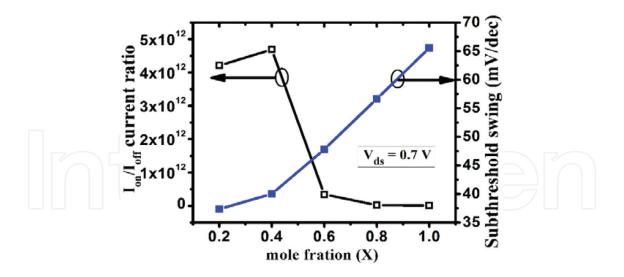

The ON/OFF current ratio and the subthreshold swing are shown in **Figure 6**. The best  $I_{ON}/I_{OFF}$  ratio is achieved for Ge-mole fraction of 0.3. In TFETs, an abrupt  $I_d$ - $V_{gs}$  plot is obtained where the subthreshold swing varies with gate voltage. Therefore, two types of SS [15] are defined in TFETs: one is the average SS and the other is known as point SS. The average SS is defined mathematically as

$$SSav = (V_T - V_{OFF}) / [\log (I_T) - \log (I_{OFF})]$$

$$\tag{1}$$

Figure 4. Energy band diagram at ON state.

Figure 5. Electric field along the channel length in UL-HTFET.

where  $V_T$  is the threshold voltage and  $V_{OFF}$  is the value of gate voltage at which the drain current just begins to take off.  $I_T$  and  $I_{OFF}$  are the drain currents at the respective voltages. Point SS, on the other hand, is the minimum SS at any point on the I<sub>d</sub>-V<sub>gs</sub> plot. The plot of average SS for different Ge-mole fractions is shown in **Figure 6**. A remarkable average SS (37 mV/dec) is achieved at 0.2 Ge-mole fraction.

Figure 6. ON and OFF current ratios ( $I_{ON}/I_{OFF}$ ) and subthreshold swing (SS) versus Ge-mole fraction.

#### 4. Development of analytical model for UL-HTFET

#### 4.1. 2-D Poisson equation-based model

In regions 1–4 of **Figure 1**, the 2-D Poisson's equation is considered and the 1-D Poisson's equation is solved on region 5 due to the absence of gate overlap. The following assumptions have been considered while modeling [12–16]:

- 1. No trap charges are considered.

- 2. There are no immobile charges in gate dielectric.

- **3.** Gate leakage current is zero.

- 4. Source-channel and channel-drain depletion regions do not have any kind of mobile charges.

In regions I–IV, the 2-D Poisson's equation is given as follows:

$$\frac{\partial^2 \Psi_i(x,y)}{\partial x^2} + \frac{\partial^2 \Psi_i(x,y)}{\partial y^2} = \frac{qN_i}{\varepsilon_i}$$

(2)

where the subscript i = 1, 2, 3, 4 corresponding to regions 1, 2, 3, or 4.

$\Psi_i(x, y)$ ,  $N_i$ , and  $\varepsilon_i$  are the two-dimensional potential, doping concentration, and permittivity of the semiconductor material, respectively, in the respective four regions.

The 2-D potential is approximated as parabolic along the depth of the device. So, the assumption for the 2-D potential is considered as

$$\Psi_i(x,y) = C_{0i}(x) + C_{1i}(x)y + C_{2i}(x)y^2$$

(3)

where  $C_{0i}(x)$ ,  $C_{1i}(x)$ , and  $C_{2i}(x)$  are coefficients that are functions of mole fraction.

In each of the four regions, three vertical boundary conditions must be satisfied to confirm the continuity of potential and electric field at the gate insulator–semiconductor interface (y = 0) and at the lowermost part of the device ( $y = t_s$ )

$$\Psi_{i}(x,0) = \Psi_{si}(x)$$

$$\frac{\partial \Psi_{i}(x,0)}{\partial y} = \frac{\varepsilon_{i}}{\varepsilon_{ox}t_{ox}} \{\Psi_{si}(x) - v_{i}\}$$

$$\frac{\partial \Psi_{i}(x,t_{s})}{\partial y} = 0$$

(4)

where  $\Psi_{si}(x)$  is the surface potential,  $\mathcal{E}_{ox}$  is the permittivity of gate dielectric,  $t_{ox}$  is the gate dielectric thickness, and  $v_i = V_{GS} - V_{fbi}$ . The gate voltages with respect to source and the flatband voltage are represented by  $V_{GS}$ , and  $V_{fbi}$ , respectively. The bandgap  $E_{Gi}$  is a function of Ge-mole fraction in Si<sub>1-x</sub>Ge<sub>x</sub> expressed as a linear interpolation of the bandgaps of Si ( $\sim$  1.10 eV) and Ge ( $\sim$  0.66 eV):

$$E_{Gi} = 1.10 - 0.34x \tag{5}$$

Using the boundary conditions of Eq. (4), we obtain the coefficients of Eq. (3) as follows:

$$C_{0i} = \Psi_{si}(\mathbf{x})$$

$$C_{1i} = \frac{\varepsilon_i}{\varepsilon_{ox} t_{ox}} \{ \Psi_{si}(\mathbf{x}) - \mathbf{v}_i \}$$

$$C_{2i} = \frac{\varepsilon_i}{2\varepsilon_{ox} t_{ox} t_s} \{ v_i - \Psi_{si}(\mathbf{x}) \}$$

(6)

Using the coefficients of Eq. (6) in the polynomial in Eq. (3), the 2-D Poisson's equation can be expressed as

with

$$k_i = \sqrt{\frac{\varepsilon_{ox}}{\varepsilon_i t_{ox} t_s}}$$

and  $\xi_i = \frac{qN_i}{\varepsilon_i k_i^2} - v_i$ .

Eq. (7) has a solution of the form:

$$\Psi_{si}(x) = A_i e^{+k_i x} + B_i e^{-k_i x} - \xi_i \tag{8}$$

The surface potentials for regions I–IV of the device are represented by Eq. (8). For region V, we apply 1-D Poisson's equation:

$$\frac{\partial^2 \Psi_5(x)}{\partial x^2} = \frac{qN_5}{\varepsilon_5}$$

(9)

to get

$$\Psi_5(x) = \Psi_{s5}(x) = \frac{qN_5}{\varepsilon_5} x^2 + C_1 x + C_2$$

(10)

The coefficients  $A_1$ ,  $B_1$ ,  $A_2$ ,  $B_2$ ,  $A_3$ ,  $B_3$ ,  $A_4$ ,  $B_4$ ,  $C_1$ , and  $C_2$  must satisfy the boundary conditions for the continuity of surface potential and electric field in the five regions:

$$\Psi_{s1}(-f) = -\left(\frac{kT}{q}\right)\ln\left(\frac{N_s}{n_{i1}}\right)$$

$$\Psi_{s1}(0) = \Psi_{s2}(0)$$

$$\frac{\partial\Psi_{s1}(0)}{\partial x} = \frac{\partial\Psi_{s2}(0)}{\partial x}$$

$$\Psi_{s2}(a) = \Psi_{s3}(a)$$

$$\frac{\partial\Psi_{s2}(a)}{\partial x} = \frac{\partial\Psi_{s3}(a)}{\partial x}$$

$$\Psi_{s3}(b) = \Psi_{s4}(b)$$

$$\frac{\partial\Psi_{s3}(b)}{\partial x} = \frac{\partial\Psi_{s4}(b)}{\partial x}$$

$$\Psi_{s4}(c) = \Psi_{s5}(c)$$

$$\frac{\partial\Psi_{s4}(c)}{\partial x} = \frac{\partial\Psi_{s5}(c)}{\partial x}$$

$$\Psi_{s5}(d) = V_{DS} + \left(\frac{kT}{q}\right)\ln\left(\frac{N_d}{n_{i2}}\right)$$

(11)

where  $V_{DS}$  is the drain voltage with respect to source, and  $n_{i1}$  and  $n_{i2}$  are the intrinsic concentrations of the Si<sub>1-x</sub>Ge<sub>x</sub> layer and silicon, respectively. Here, *a*, *b*, *c*, *d*, and *-f* are the various positions along the channel at which the boundary conditions are applied. Their

values are mentioned in the inset of **Figure 1**. The width of the depletion region in the source is expressed as

$$f = \sqrt{\frac{2\varepsilon_1 |\xi_1 - \Psi_{ss}|}{q |N_1|}}$$

(12)

where

$$\Psi_{ss} = -\frac{kT}{q} \ln\left(\frac{N_s}{n_{i2}}\right)$$

Using Eqs. (8) and (10), the lateral electric field for the five regions is given as

$$E_{xi}=-k_i\big(P_ie^{k_ix}-Q_ie^{-k_ix}\big)$$

for i = 1, 2, 3, 4 corresponding to regions I, II, III, or IV.

and

$$E_{x5} = -\left(\frac{qN_5x}{\varepsilon_5} + C_1\right) \tag{13}$$

The vertical electric fields for the different regions are expressed using Eqs. (3) and Eq. (10) as

$$E_{yi} = -(a_{1i} + 2a_{2i}y) \tag{14}$$

for i = 1, 2, 3, 4 corresponding to regions I, II, III, or IV.

and

$$E_{y5} = 0$$

(15)

The drain current is calculated by integrating the band-to-band generation rate  $G_{BTBT}$  over the volume of the device

$$I_d = q \int G_{BTBT} dV \tag{16}$$

where

$$G_{BTBT} = A \frac{|E|^2}{\sqrt{E_{Gi}}} \exp\left(-B \frac{E_{Gi}^{1.5}}{|E|}\right)$$

(17)

where  $E = \sqrt{E_x^2 + E_y^2}$

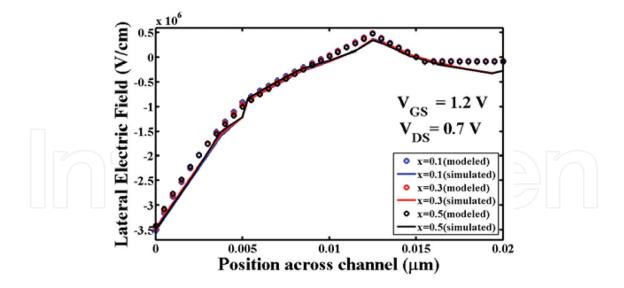

Figure 7. Variation of lateral electric field at the surface in the channel for different Ge-mole fractions.

#### 4.2. Validation of the analytical model

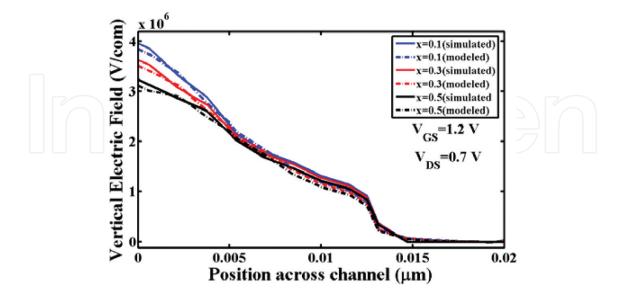

The developed analytical models are validated with simulation data from TCAD. **Figure 7** shows the plot of lateral electric field at the surface of the UL-HTFET in the channel region for different Ge-mole fractions of the silicon-germanium layer, at  $V_{GS} = 1.2 V$  and  $V_{DS} = 0.7 V$ . It has been seen that the modeled values match with the simulated values of lateral electric field except that a small mismatch in the field is observed at the position in the channel where the gate-channel overlap terminates.

Figure 8. Variation of vertical electric field at the surface in the channel for different Ge-mole fractions.

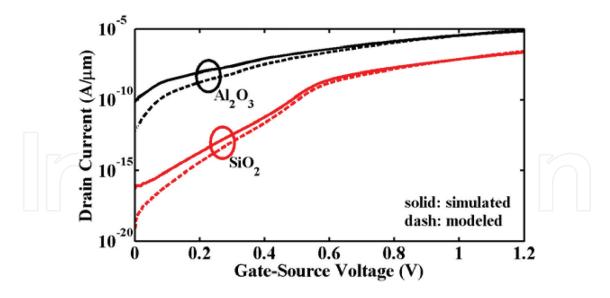

**Figure 9.**  $I_D$ - $V_{gs}$  characteristics at Ge-mole fraction equal to 0.5, gate voltage equal to 1.2 V, and drain voltage equal to 0.7 V.

A plot of vertical electric field at the surface of the device versus horizontal position in the channel region is shown in **Figure 8** for different values of Ge-mole fractions at a fixed drain voltage of 0.7 V and a gate voltage of 1.2 V. For all the cases, it has been observed that the modeled results closely approach the simulated results. The simulated vertical electric field is slightly different as compared to the modeled ones near the junction of silicon-germanium-silicon in the channel region; however, at other positions in the channel, there is a close match between the modeled and the simulated values of vertical electric field.

The variation of drain current with gate voltage has been computed and portrayed in **Figure 9**. There is a close match between the model and the simulated data.

## 5. Dependence of threshold voltage on temperature

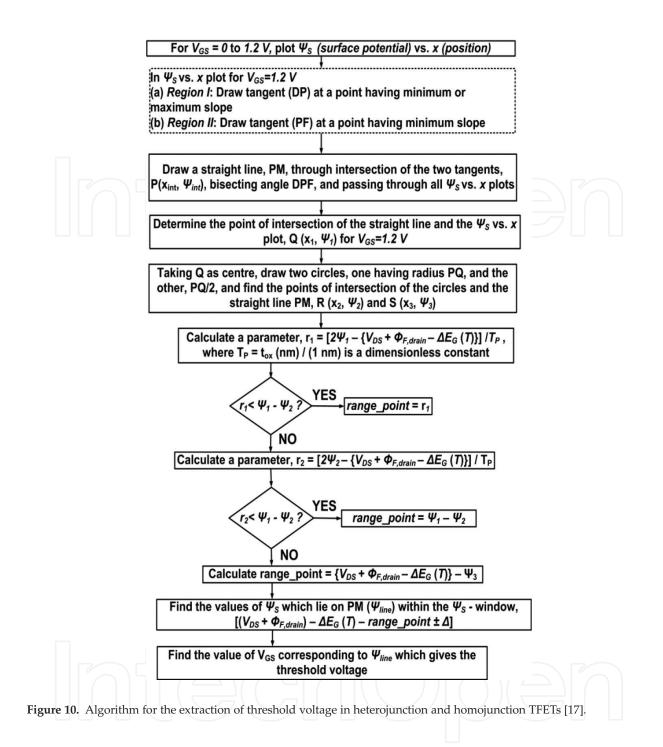

An algorithm for the extraction of threshold voltage in heterojunction TFET is presented in **Figure 10** [17]. The algorithm uses the analytical model of Section 4 to plot multiple curves of surface potential versus position for different gate voltages and fixed drain voltage. The advantage of this algorithm is that the procedure is completely computational, and the threshold voltage can be determined without deriving the transfer characteristics. Moreover, the method can be extended to fit different threshold voltage extraction methods by changing the fitting parameter [17].

The model takes into account the dependence of temperature. The method involves geometrical constructions on a plot of surface potential versus position and using mathematical parameters to define a variable *range\_point*.

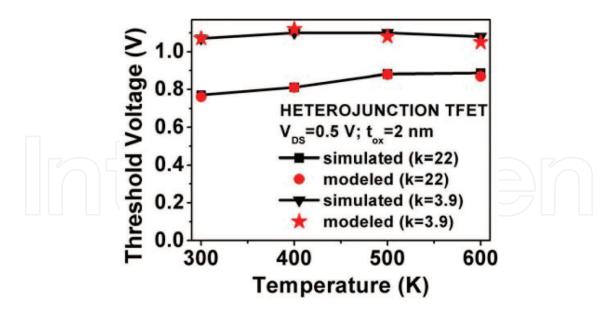

A plot of threshold voltage versus temperature is shown in **Figure 11**. The plot shows that for high-*k* gate dielectric TFET, the threshold voltage rises with an increase in temperature, whereas for low-*k* dielectric, the threshold voltage remains almost constant. The simulated values of threshold voltage have been derived using linear extrapolation method of determining threshold voltage. The method involves the construction of a tangent at the point on the

Figure 11. A plot of threshold voltage versus temperature for dielectric constants, 3.9 and 22.

transfer characteristics where the transconductance is maximum. The value at which the tangent intersects the gate voltage axis is taken to be the threshold voltage.

#### 6. Conclusion

This chapter has presented a comprehensive evaluation of a bandgap-modulated UL-HTFET. The simulation analyses have examined the different electrical parameters and their dependence on the pocket length, mole fraction of the SiGe layer, and gate voltage. An impressive on-off current ratio of >10<sup>12</sup> and a subthreshold swing less than 60 mV/dec are observed. An analytical model based on 2-D Poisson equation has been developed for the gate-drain underlap heterojunction TFET. The modeled values of surface potential, electric field, and drain current satisfy the results of the simulation. Furthermore, a temperature-dependent algorithm has been discussed to extract threshold voltage in heterojunction TFETs, and a validation has been presented for the plot of threshold voltage at different temperatures.

### Acknowledgements

The authors would like to acknowledge Computational Laboratory, Department of Electronics and Communication Engineering, National Institute of Technology Silchar, India, for supporting the work.

## Author details

Brinda Bhowmick<sup>1</sup>\* and Rupam Goswami<sup>2</sup>

\*Address all correspondence to: brindabhowmick@gmail.com

1 Department of Electronics and Communication Engineering, National Institute of Technology Silchar, Silchar, Assam, India

2 Kalinga Institute of Industrial Technology, Bhubaneswar, Odisha, India

## References

- [1] Choi WY, Park B-G, Lee JD, Liu T-JK. Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Letters. 2007;28(8): 743-745. DOI: 10.1109/led.2007.901273

- [2] Royer CL, Mayer F. Exhaustive experimental study of tunnel field effect transistors (TFETs): From materials to architecture. In: 10th International Conference on Ultimate Integration of Silicon 2009; 18–20 March 2009. Aachen: IEEE; 2009. pp. 53-56. DOI: 10.1109/ulis.2009.4897537

- [3] Ahish S, Sharma D, Kumar YBN, Vasantha MH. Performance enhancement of novel InAs/ Si hetero double-gate tunnel FET using Gaussian doping. IEEE Transactions on Electron Devices. 2016;63(1):288-295. DOI: 10.1109/ted.2015.2503141

- [4] Tamersit K, Djeffal F. Double-gate graphene nanoribbon field-effect transistor for DNA and gas sensing applications: Simulation study and sensitivity analysis. IEEE Sensors Journal. 2016;16(11):4180-4191. DOI: 10.1109/jsen.2016.2550492

- [5] Goswami R, Bhowmick B. An analytical model of drain current in a Nanoscale circular gate TFET. IEEE Transactions on Electron Devices. 2017;64(1):45-51. DOI: 10.1109/ TED.2016.2631532

- [6] Zhao Q-T, Richter S, Schulte-Braucks C, Knoll L, Blaeser S, Luong GV, et al. Strained Si and SiGe nanowire tunnel FETs for logic and analog applications. IEEE Journal of the Electron Devices Society. 2015;3(3):103-114. DOI: 10.1109/jeds.2015.2400371

- Boucart K, Ionescu A. Double gate tunnel FET with ultrathin silicon body and high-k gate dielectric. In: Proceedings of the European Solid-State Device Research Conference. 2006; 19–21 Sept. Vol. 2006. Montreux, Switzerland: IEEE; 2007. pp. 1725-1733. DOI: 10.1109/essder.2006.307718

- [8] Saurabh S, Kumar MJ. Novel attributes of a dual material gate Nanoscale tunnel fieldeffect transistor. IEEE Transactions on Electron Devices. 2011;58(2):404-410. DOI: 10.1109/ ted.2010.2093142

- [9] Choi WY, Lee W. Hetero-gate-dielectric tunneling field-effect transistors. IEEE Transactions on Electron Devices. 2010;**57**(9):2317-2319. DOI: 10.1109/ted.2010.2052167

- [10] Dewey G, Chu-Kung B, Boardman J, Fastenau JM, Kavalieros J, Kotlyar R, et al. Fabrication, characterization, and physics of III–V heterojunction tunneling Field Effect Transistors (H-TFET) for steep sub-threshold swing. International Electron Devices Meeting. 2011; 5–7 Dec. 2011. Washington, DC, USA: IEEE; 2012. p. 33.6.1-33.6.4. DOI: 10.1109/ iedm.2011.6131666

- [11] Synopsys. Sentaurus device user guide. Mountain view. In: CA. 2011

- [12] Bagga N, Sarkar SK. An analytical model for tunnel barrier modulation in triple metal double gate TFET. IEEE Transactions on Electron Devices. 2015;62(7):2136-2142. DOI: 10.1109/ted.2015.2434276

- [13] Dash S, Mishra G. A new analytical threshold voltage model of cylindrical gate tunnel FET (CG-TFET). Superlattices and Microstructures. 2015;86:211-220. DOI: 10.1016/j.spmi.2015. 07.049

- [14] Lee MJ, Choi WY. Analytical model of single-gate silicon-on-insulator (SOI) tunneling field-effect transistors (TFETs). Solid-State Electronics. 2011;63(1):110-114. DOI: 10.1016/j. sse.2011.05.008

- [15] Vishnoi R, Kumar MJ. Compact analytical drain current model of gate-all-around nanowire tunneling FET. IEEE Transactions on Electron Devices. 2014;61(7):2599-2603. DOI: 10.1109/ted.2014.2322762

- [16] Goswami R, Bhowmick B, Baishya S. Physics-based surface potential, electric field and drain current model of a  $\delta p^+ Si_{1-x}Ge_x$  gate–drain underlap nanoscale n-TFET. International Journal of Electronics. 2016;**103**(9):1566-1579. DOI: 10.1080/00207217.2016.1138514

- [17] Goswami R, Bhowmick B. A temperature-dependent surface potential-based algorithm for extraction of threshold voltage in homojunction TFETs. International Journal of Numerical Modelling: Electronic Networks, Devices and Fields. 2017 Jul. DOI: 10.1002/ jnm.2304

IntechOpen