### We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

6,900

186,000

200M

Download

154

Countries delivered to

Our authors are among the

**TOP 1%**

most cited scientists

12.2%

Contributors from top 500 universities

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected.

For more information visit www.intechopen.com

### **Emulator Circuits and Resistive Switching Parameters** of Memristor

Abdullah Yesil, Fatih Gül and Yunus Babacan

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/intechopen.71903

#### **Abstract**

Chua predicted the existence of the fundamental circuit element, which provides the linkage of flux  $(\phi)$  and charge (q). The new circuit element that is called memristor (memory + resistor) was demonstrated by Hewlett Packard (HP) researchers in 2008. Researchers focused on memristor fabrication, modeling, and its application with other circuit elements. Researchers could not find the commercially memristor devices in the market because of some fabrication difficulties. For this reason, researchers focused on the memristor modeling to analyze its characteristics with other circuit elements. This chapter presents a review of the general information of memristor and its device parameters. The chapter is continued with the details of memristor mathematical and SPICE models and memristor emulators based on the other circuit elements.

**Keywords:** memristor, memristor models, SPICE, memristor emulator, active circuit element-based memristors

#### 1. Introduction

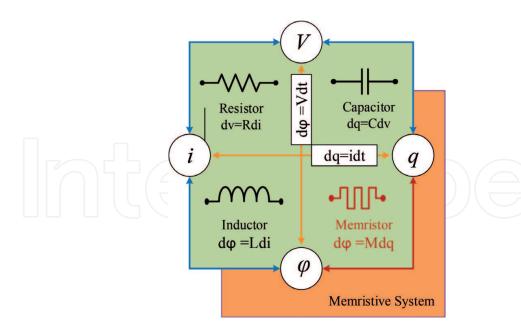

Both active circuit elements and passive circuit elements are used in circuit design, and the first circuit elements that come to mind are passive circuit elements: resistor, capacitor, and inductor. Resistor, capacitor, and inductor define the relationship between the voltage and current, voltage and charge, and current and flux, respectively. Leon Chua from the University of California (Berkeley) showed the missing relationship as shown in **Figure 1** between flux and current in 1971 and 1976 [1, 2].

At the same time, Chua called the missing circuit element as a memristor (memory + resistor) and presented the mathematical equations of the new circuit element. But the seminal paper

Figure 1. The fundamental two-terminal passive circuit elements.

Figure 2. The scanning tunneling microscope image of the memristor [4].

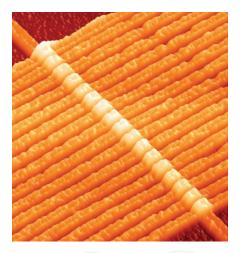

of Chua could not find attentions among the researchers because of the technical fabrication difficulties of the memristor. Therefore, researchers did not focus on the memristor and its application until its first fabrication of memristor by HP researchers in 2008 [3]. The first memristor is made from TiO<sub>2</sub> thin film and has crossbar structure as shown in **Figure 2**.

The HP research team also presented the mathematical model of TiO<sub>2</sub> memristor, and current-voltage relationship is defined by

$$V = [M(x_{1}, x_{2}, ... x_{n})]I$$

(1)

where V is the voltage and I is the current. Here, M is the resistance of memristor and memristance and depends on  $x_i$  state variables. Memristance which performs nonlinear characteristics depends on frequency and applied input signal. The  $TiO_2$  memristor consists of two

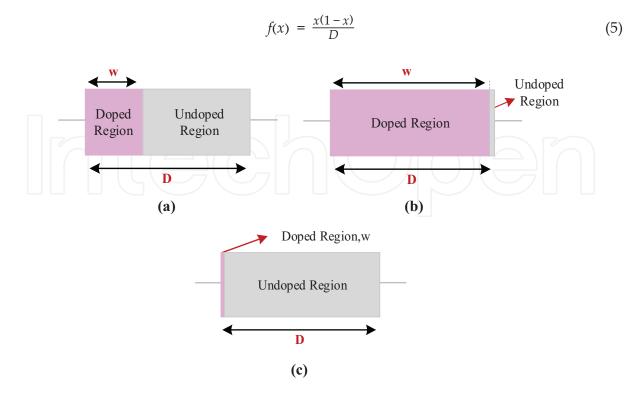

main structures which are named doped and undoped region as shown in **Figure 3**, and the memristance changes the ratios of the doped region and device thickness.

Memristor acts as a conductor if the thickness of the doped region becomes wide as shown in **Figure 3b**. Undoped region becomes wide as shown in **Figure 3c**, and memristor behaves as a high-resistance element when the input signal applied in an opposite direction.

Memristance is as below:

$$M(x) = \left[R_{ON}x + R_{OFF}(1-x)\right], \quad \left(x = \frac{w}{D}\right)$$

(2)

The change of the *x* value is depicted:

$$\frac{dx}{dt} = \frac{\mu_v R_{ON}}{D^2} i(t) \tag{3}$$

The  $\mu_v$  is the electron mobility, and w and D denote the doped area of memristor and thickness of the memristor, respectively. The resistances of the high and low dopant concentrations are symbolized with  $R_{ON}$  and  $R_{OFF}$ , respectively. Researchers added a function to the memristor mathematical model to take into account the nonlinear dopant effect [3, 5–7]. Equation (3) is rearranged as follows:

$$\frac{dx}{dt} = \frac{\mu_v R_{ON}}{D^2} i(t) f(x) \tag{4}$$

The first function which is called window function is presented by HP research team [3] as shown below:

**Figure 3.** Memristor (a) initial state, (b) low-resistance state, and (c) high-resistance state.

Figure 4. Window function presented by Wolf and Joglekar [5].

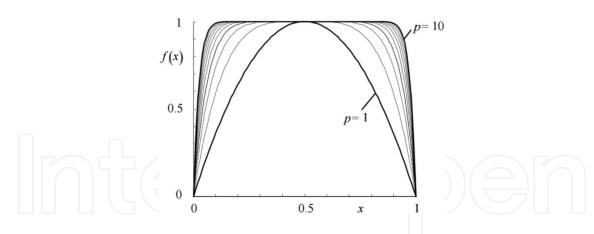

The HP model is linear and very simple; so Wolf and Joglekar [5] depicted the new window function as shown below:

$$f(x) = 1 - (2x - 1)^{2p} (6)$$

The function is starting to similar the rectangular shape when p-value becomes higher, namely, dopant drift is decreasing as shown in **Figure 4**.

Biolek et al. [6] modified the model of Wolf and Joglekar:

$$f(x) = 1 - (x - stp(-i))^{2p}$$

(7a)

$$stp(i) = \begin{cases} 1, i \ge 0 \\ 0, i < 0 \end{cases}$$

(7b)

The window function which is presented by Biolek is shown in **Figure 5**.

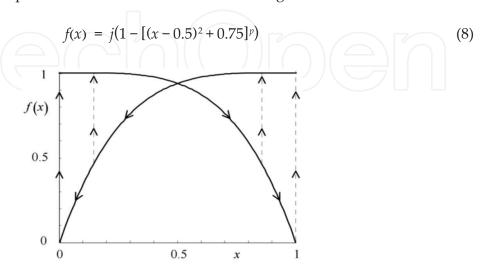

Prodromakis et al. [7] depict the versatile model as the following:

Figure 5. Window function presented by Biolek et al. [6].

Model function of Prodromakis et al. becomes higher than the value of 1 unlike previous window functions. The function depends on the various *p*-values shown in **Figure 6**.

Researchers suggested various mathematical memristor models such as nonlinear ion-drift model [8], Simmons' tunnel barrier model [9], and ThrEshold Adaptive Memristor (TEAM) model [10] different from the linear HP model. The chapter is continued with memristor device.

#### 2. Memristor switching device parameters

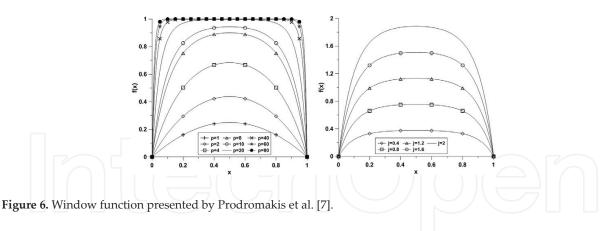

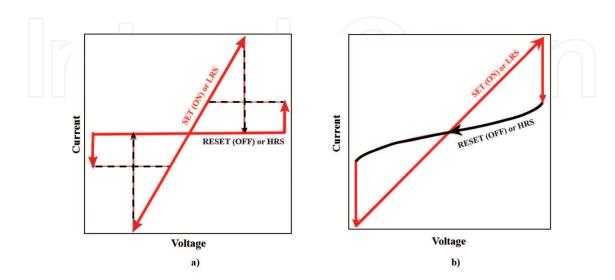

The pinched hysteresis loops serve as a fingerprint in the characterization of memristors [11] as shown in **Figure 7**. It is to say that, if any two-terminal device is showing pinched hysteresis loop, a memristor regardless of the device material is accepted. Resistive switching (or memristive behavior) in metal-oxide semiconductor was first observed by Hickmott in 1962, but it was interpreted as the current anomaly [12]. As in resistive switching devices, a typical pinched hysteresis loop is seen at the first and third quadrants of the current-voltage (I-V) curves [13]. Put differently, all memristors can be accepted as resistive switching devices regardless of the operating mechanisms and the device material [14].

**Figure 7.** (a) Schematic representation of a memristor device and (b) typical pinched hysteresis current-voltage loop of memristor devices.

#### 2.1. Active layer material and top/bottom electrode

The semiconductor-based memristor devices usually consist of an active layer sandwiched between a top and a bottom electrode (TE/BE) depicted in **Figure 7**. The first physical implementation of the memristor was achieved by HP labs using TiO<sub>2</sub> metal-oxide active layer [3]. After that, several physical memristor devices suggested the use of different materials and production methods. Most metal-oxide semiconductors exhibit memristor characteristics, including TiO<sub>2</sub>, ZnO, HfO<sub>2</sub>, VO<sub>2</sub>, TaO<sub>x</sub>, and so on [13, 15, 16]. There are two types of contact in semiconductor: one is of Schottky (rectifying), and the other one is ohmic. Several electrode materials can be used as TE or BE including Pt, Au, Ag, Al, etc. In one diode-one resistor (1D1R)-type memory cell memristor device, one of the electrodes must be a Schottky contact [17].

#### 2.2. Unipolar or bipolar operation

The unipolar and bipolar operation of memristor devices which are shown in **Figure 8** can be categorized in according with current-voltage characteristics. In unipolar operation characteristics depend only on the amplitude of the applied voltage, whereas bipolar operations are resolved by polarity and amplitude of the applied voltage [13]. Unipolar operation is more striking than bipolar operation in memristor switching devices, since it needs simple circuits. But then, bipolar operation has generally high uniformity and more endurance compared to unipolar operation [18].

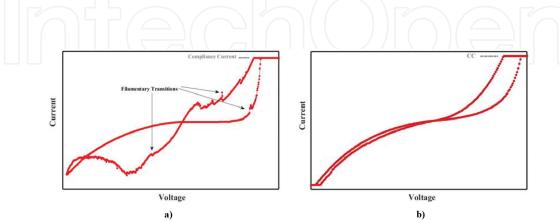

#### 2.3. Physical mechanism

There are two types of physical working mechanisms in the explanation of the time-dependent current-voltage characteristics, based on molecular or ionic models: the homogeneous interface type and the filamentary (conduction path) type [13, 16]. In the homogeneous type, the migration of oxygen vacancies as the majority carriers causes change of resistance. The filament-type mechanism is associated with the formation and rupture of conductive filaments

Figure 8. Typical current-voltage curves of memristor devices (a) unipolar and (b) bipolar.

in the active layer. Both types of mechanisms can be observed in the memristor devices as shown in **Figure 9** and depend on the material and fabrication methods [18].

#### 2.4. Operation current-voltage

It is well known that reversible switching between a low-resistance state (LRS) or ON (SET) and a high-resistance state (HRS) or OFF (RESET) can be achieved by applying a certain voltage [18]. Operation voltage is also an important value for CMOS or other device integrations for memristor devices. Another criterion for the memristor devices is the power consumption related to the operation current. With the aim of escape permanent damage from over current, the compliance or limit current (CC) must be set in both unipolar and bipolar operations [13]. The compliance current is also related to power consumption of a memristor device [19].

#### 2.5. ON/OFF ratio

The memristor has two states when used as a switching device: the high-resistance state (HRS) or OFF (RESET) state and the low-resistance state (LRS) or ON (SET) state [13]. The ON/OFF ratio defined as the proportion between resistances in HRS and LRS is some of the most important parameters when memristors are used as switching device [18].

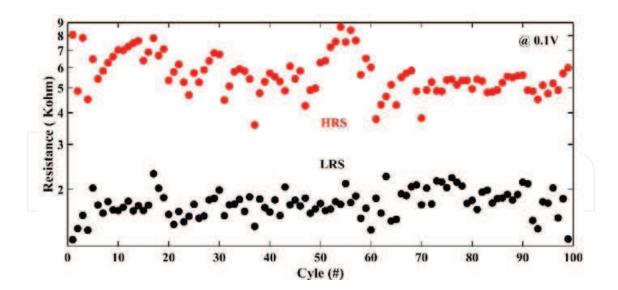

#### 2.6. Retention time and endurance

The time to hold ON/OFF state is an important criterion when memristor device used a resistive switching memory or ReRAM element [20]. It is expected that the memristor device's distribution of the HRS or LRS state which is shown in **Figure 10** has acceptable values besides its ON/OFF ratio [19]. Since the memory unit needs to be repeatedly read or written by the other control units, cycling endurance is one of the main importance of memristor-based memory devices [18].

Some of recent memristor devices which are composed of various materials are compared according to the some important parameters as shown in **Table 1** [19, 22–24]. The chapter is continued with memristor emulators based on the active circuit elements.

**Figure 9.** Typical current-voltage curves of memristor devices: (a) filamentary and (b) homogenous transitions on bipolar operation [19].

Figure 10. Typical endurance test of a memristor device @0.1 V for 100 cycles [21].

| Active layer material  | TE/BE | Operation mode | Operation<br>mechanism | Operation voltage | ON/OFF<br>ratio   | Retention time | Endurance | Ref. |

|------------------------|-------|----------------|------------------------|-------------------|-------------------|----------------|-----------|------|

| ZnO                    | Al/Al | Bipolar        | Homogenous             | -1.5 V/+1.5 V     | $5 \times 10^{1}$ | N/A            | 100       | [19] |

| $TiO_2$                | Al/Al | Bipolar        | Filamentary            | -3 V/+1.5 V       | $8 \times 10^2$   | N/A            | $10^{12}$ | [22] |

| HfO <sub>2</sub>       | Pt/Ti | Bipolar        | Filamentary            | -3.5 V/+2 V       | $10^{3}$          | $10^{4}$       | 1000      | [23] |

| ${\rm TaO}_{_{\rm x}}$ | Pt/Pt | Unipolar       | Filamentary            | -1.5 V/+1 V       | $10^{1}$          | N/A            | 1000      | [24] |

Table 1. Comparison table of some recent memristor devices.

#### 3. Memristor models and emulators

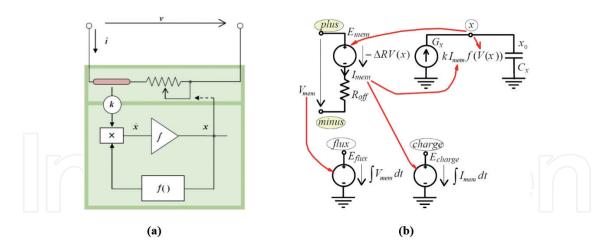

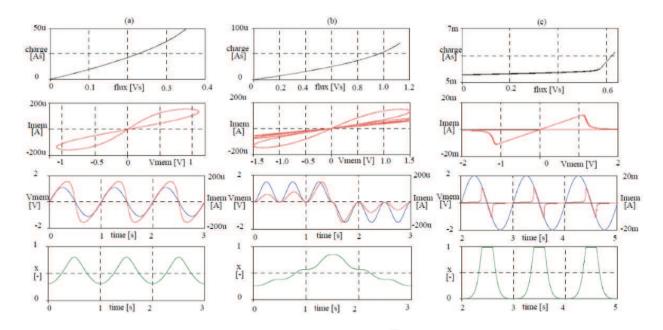

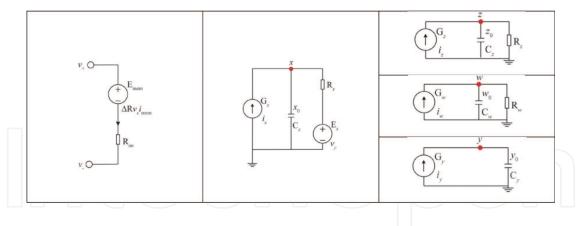

Many SPICE models and emulators are presented by researchers [6, 25–47]. The first and applicable memristor model has been presented by Biolek and co-workers [6]. This model takes into account the boundary conditions using window function, and the feedback-controlled integrator is used to implement memory effect of the memristor. The block diagram of memristor and its SPICE model is shown in **Figure 11**. All simulation results which are shown in **Figure 12** are completed using SPICE codes as shown below. Each curve is compatible with TiO<sub>2</sub> memristor, and boundary effects are taken into account (**Table 2**).

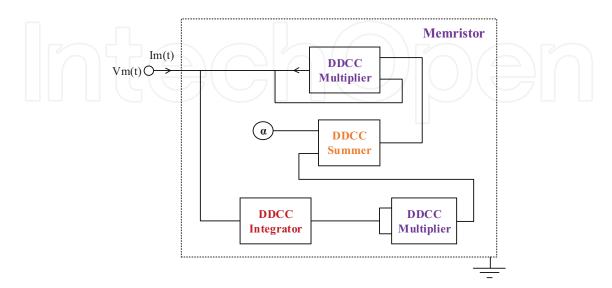

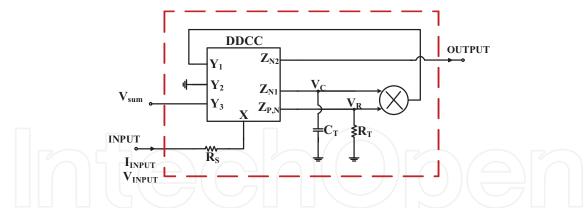

Researchers are not able to reach the memristor devices in the market because of some production problems of the memristor. For this reason, researchers focused on the designing of memristor emulators to use with other circuit elements. Yener and Kuntman reported full active device-based memristor emulator which is consisting of differential difference current conveyor (DDCC) [35]. The proposed grounded memristor emulator consists of four circuit blocks based on DDCC as shown in **Figure 13**. Furthermore, there are no experimental results; however, its SPICE simulation results are given.

Figure 11. (a) Block diagram and (b) SPICE model of the memristor [6].

Figure 12. Charge-flux, current-voltage, current-voltage-time, and x-time curves for memristor model [6].

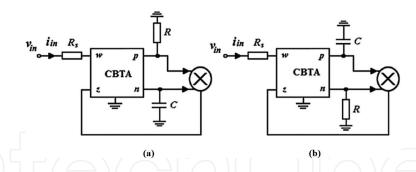

Another active circuit element-based grounded memristor emulator [36] has been implemented by using current backward transconductance amplifier (CBTA). This emulator consists of two different circuits such as decremental and incremental type given in **Figure 14**. Each memristor emulator is composed of a single CBTA, two resistors, one grounded capacitor, and single analog multiplier. In order to validate the feasibility of the presented memristor, only SPICE simulation results have been given.

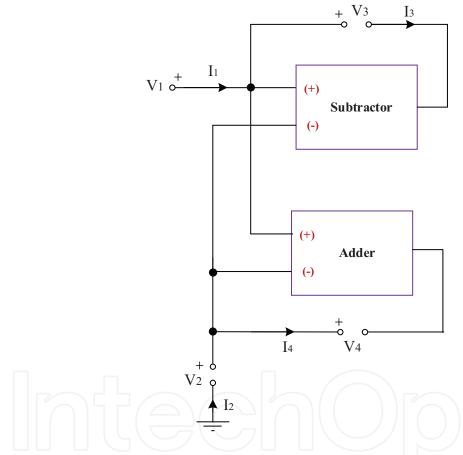

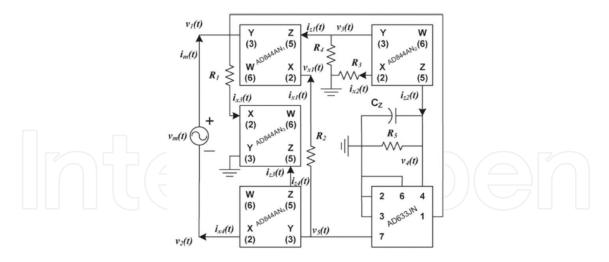

The generalized mutator structure based on adder and subtractor has been proposed by Minaei et al. [37]. As far as connection ports are concerned, the generalized structure employs memristor, meminductor, and memcapacitor without using analog multiplier. By selecting an inductor to port 3, a capacitor to port 4, and a nonlinear resistor such as a diode to port 1, the generalized structure given in **Figure 15** is utilized as memristor. Nonetheless, so as to verify the workableness of the presented structure, the SPICE simulation results are given.

\* HP Memristor SPICE Model \* RESISTIVE PORT OF THE MEMRISTOR \* \* For Transient Analysis only \*\*\*\*\*\*\*\*\* \* created by Zdenek and Dalibor Biolek Emem plus aux value =  $\{-I(Emem)*V(x)*(Roff-Ron)\}$ \*\*\*\*\*\*\* Roff aux minus {Roff} \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* \* Ron, Roff - Resistance in ON/OFF States \* Rinit - Resistance at T = 0\*Flux computation\* \_ \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* \* D - Width of the thin film \* uv - Migration coefficient Eflux flux 0 value =  $\{SDT(V(plus,minus))\}$ \*\*\*\*\*\*\*\*\*\*\*\* \* p - Parameter of the WINDOW-function \* for modeling nonlinear boundary conditions \*Charge computation\* \*\*\*\*\*\*\*\*\*\*\*\* \* x - W/D Ratio, W is the actual width \* of the doped area (from 0 to D) Echarge charge 0 value = {SDT(I(Emem))} \*\*\*\*\*\*\*\*\*\*\* .SUBCKT memristor Plus Minus PARAMS: \* WINDOW FUNCTIONS + Ron = 1 K Roff = 100 K Rinit = 80 K D = 10 N uv = 10F p = 1 \* FOR NONLINEAR DRIFT MODELING \* \*\*\*\*\*\*\*\*\*\*\*\*\*\* \* DIFFERENTIAL EQUATION MODELING \* \*window function, according to Joglekar \*\*\*\*\*\*\*\*\*\*\*\*\* .func  $f(x,p) = \{1-(2*x-1)^{(2*p)}\}$  $Gx \ 0 \ x \ value = \{I(Emem)*uv*Ron/D^2*f(V(x),p)\}$ \*proposed window function  $Cx \times 0.1 IC = \{(Roff-Rinit)/(Roff-Ron)\}$  $f(x,i,p) = \{1-(x-stp(-i))^2(2*p)\}$ Raux x 0 1T .ENDS memristor

**Table 2.** SPICE codes of modeled memristor [6].

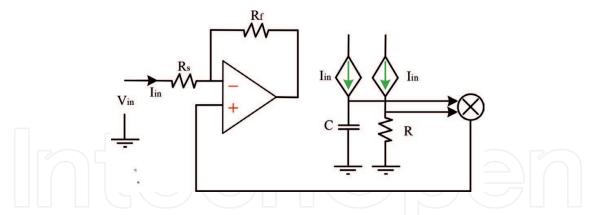

Kim and co-workers presented the active circuit element-based memristor emulator [38]. This circuit is also implemented on the bread board using discrete circuit elements that are ADL1116PAL for NMOS transistors, ADL1117PAL for PMOS transistors, TL082 for OPAMP, and AD633 for analog multiplier and passive elements. There are three important tasks to implement memristor emulator: memory effect, frequency-/voltage-dependent characteristics, and nonlinearity. Memory effect and frequency/voltage dependency characteristics are implemented by using a capacitor like many other previous emulator circuits. Nonlinear characteristic of the memristor is obtained using multiplier circuit block. But each used block gives rise to extra power dissipation and more complex circuit (Figure 16).

Figure 13. DDCC-based memristor emulator which is presented by Yener and Kuntman [35].

Figure 14. CBTA-based memristor emulator (a) decremental structure and (b) incremental structure [36].

Figure 15. Generalized mutator structure based on adder and subtractor [37].

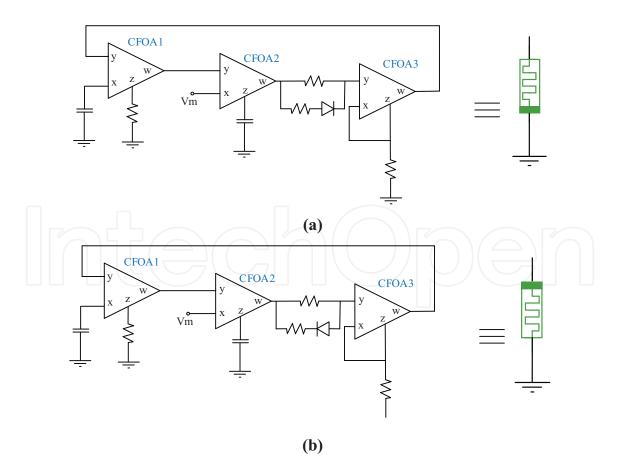

Another active circuit-based memristor emulators which are shown in **Figure 17** have been presented by Abuelma'atti and Khalifa [39]. Each emulator which is based on current-feed-back operational amplifier (CFOA) enjoys operating two different types like decremental and incremental memristor emulators. This situation is a disadvantage of the emulator besides its grounded structure. Each circuit comprises three CFOAs, four resistors, two capacitors, and germanium diode without using an analog multiplier. Nonlinear characteristic is provided by germanium diode. CFOA which is an active element is modeled by AD844 commercially available active devices, and experimental results have been investigated.

Figure 16. Voltage-controlled memristor emulator which is presented by Kim and co-workers [38].

Sánchez-López and Aguila-Cuapio proposed the charge-controlled memristor emulator circuit [40]. This circuit which is shown in **Figure 18** is grounded; hence, application areas of the presented memristor emulator are limited in circuit designs. Moreover, it is implemented with discrete circuit element such as AD844 and AD633 besides its disadvantages.

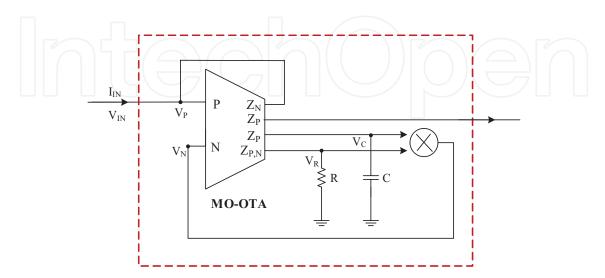

Babacan and co-workers presented new memristor emulator based on multi-output operational transconductance amplifier (OTA) [41]. This emulator shown in **Figure 19** is a derivative of the DDCC-based memristor emulator [42], but memristance value of this emulator

Figure 17. CFOA-based memristor emulator with (a) decremental and (b) incremental characteristic [39].

Figure 18. Memristor emulator based on AD844 [40].

can be adjusted by biasing current of the OTA. The change of the memristance value can be controlled by changing resistor (R) value. Average memristance value can be controlled using OTA-gm value because of the fact that OTA is used as controllable resistor by connecting the negative output terminal to the positive input terminal. In order to demonstrate the performance of OTA-based memristor emulator, both SPICE simulation results and experimental results have been performed. For experimental results, the memristor emulator is built using passive elements and commercially available active devices such as OPA860 for MO-OTA and AD633 for the analog multiplier.

Yesil and co-workers suggested only one DDCC-based memristor emulator which can be operated in high-frequency regions [42]. It is observed from **Figure 20** that the capacitor provides the memory effect and the multiplication of both capacitor and resistor voltages is connected to the Y terminal of the active device. The resistance of memristor emulator circuit decreases when the Z terminal of the DDCC device is chosen as positive terminal ( $Z_p$ ). Consequently, the circuit shows decremental memristor characteristics. For another state, an

Figure 19. OT-based memristor emulator which is presented by Babacan and co-workers [41].

Figure 20. DDCC-based memristor emulator which is presented by Yesil and co-workers [42].

incremental memristor can be obtained when the Z terminal of DDCC is chosen as negative terminal ( $Z_N$ ). This emulator consists of the third terminal ( $V_{sum}$ ) to provide the floating characteristic. Serial connected memristors split applied voltage such as resistor if these memristors carry out a voltage; accordingly, the third terminal is connected to the output terminal. Just as DDCC-based [35], CBTA-based [36], and adder-and-subtractor [37]-based memristor, the performance of [42] is confirmed by SPICE simulations results.

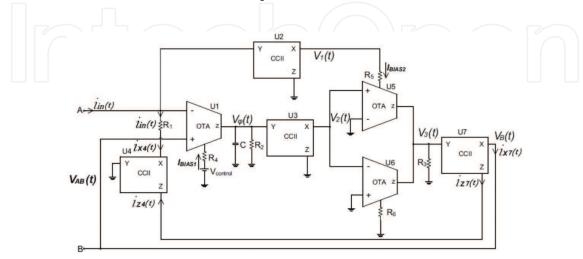

Sozen and Cam proposed new floating memristor emulator based on OTA and CCII as shown in **Figure 21** [43]. This emulator is made up of three OTAs, four CCIIs, and seven passive elements. Both SPICE simulation results and experimental results of the presented memristor emulator have been given to confirm its workableness and feasibility. Commercially available active devices CA3080 and AD844 have been utilized instead of OTA and CCII, respectively.

Sánchez-López et al. proposed second-generation current conveyor (CCII)-based flux-controlled memristor emulator which is shown in **Figure 22** [44]. The presented emulator comprises of four CCIIs, a multiplier circuit, five resistors, and single grounded capacitor. AD844 and AD633 are used instead of CCII and analog multiplier in the flux-controlled memristor emulator, respectively. So as to indicate the performance of flux-controlled memristor emulator, both SPICE simulation results and experimental results have been exhibited.

Figure 21. OTA- and CCII-based memristor emulator [43].

Figure 22. Floating flux-controlled memristor emulator based on CCII [44].

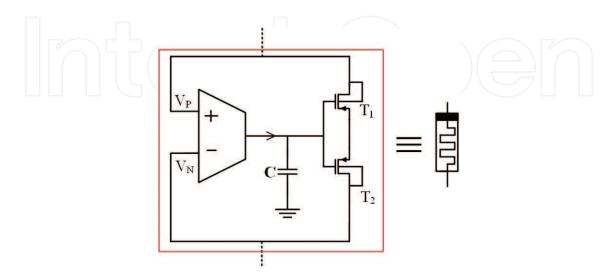

Babacan and Kacar suggested new memristor emulator which does not need any multiplication block as shown in **Figure 23** [45]. This emulator is also fully floating, namely, has two terminals, and input signal can be applied in both terminals. The nonlinearity is provided by transistors which are operated in the subthreshold region. The presented memristor emulator includes single-ended OTA, one grounded capacitor, and two PMOS transistors. Note that the bulk terminals of PMOS transistors are connected to drain terminals of relevant transistors.

The first memristor model which accounts for spike-timing-dependent plasticity (STDP) mechanism is proposed by Li and co-workers [46]. The model which is shown in **Figure 24** consists of five circuit models, and each model depends on the previous model so this model is complex and does not have any circuit implementation.

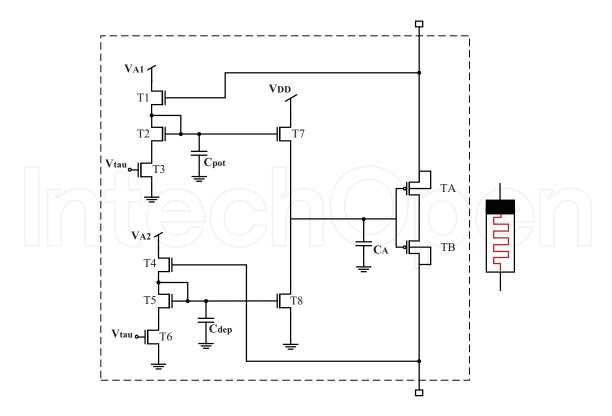

Babacan and Kacar suggested real-time fully floating memristor emulator which is accounted for synaptic activity [47]. Both memristive and STDP characteristics are obtained from the

Figure 23. Fully floating memristor emulator based on OTA [45].

Figure 24. Memristor model which is accounted for STDP mechanism [46].

circuit which is shown in **Figure 25**. It is observed from **Figure 25** that fully floating memristor emulator consists of a few numbers of MOS transistors and capacitors without using analog multiplier. Furthermore, STDP is experimentally demonstrated in memristive devices [48–50].

In summary, the comparison of the memristor emulator circuits is according to some important design parameters such as used circuit elements, electronically controllability, power supply value, etc. Each emulator has superior properties among the other emulators. Researchers can prefer appropriate emulator circuit for their memristor-based circuit designs (**Table 3**).

Figure 25. Memristor circuit which is accounted for STDP mechanism [47].

| Reference | No. of<br>floating<br>passive<br>elements | No. of active comp                           | No. of<br>grounded<br>passive<br>elements | Sim./exp | Electronically<br>controllable | Floating/<br>grounded<br>memristor<br>emulator | Power supply |

|-----------|-------------------------------------------|----------------------------------------------|-------------------------------------------|----------|--------------------------------|------------------------------------------------|--------------|

| [35]      | _                                         | 10 DDCCs, 8<br>transistors                   | 4 R, 1 C                                  | Sim.     | No                             | Grounded                                       | ±1.25 V      |

| [36]      | 1 R                                       | 1 CBTA, 1 multiplier                         | 1 R, 1 C                                  | Sim.     | No                             | Grounded                                       | ±0.9 V       |

| [37]      | 1 L, 1 C                                  | 1 adder and 1 subtractor                     | 1 D                                       | Sim.     | No                             | Grounded                                       | ±1.25 V      |

| [38]      | 1 R                                       | 2 OPAMPs, 1<br>multiplier, 10<br>transistors | 1 R, 1 C                                  | Both     | No                             | Grounded/<br>floating                          | ±5 V         |

| [39]      | 2 R, 1 D                                  | 3 CFOAs (AD844)                              | 2 R, 2 C                                  | Exp.     | No                             | Grounded                                       | NA           |

| [40]      | 1 R                                       | 1 CCII(AD844), 1<br>multiplier (AD633)       | 1 C                                       | Both     | No                             | Grounded                                       | ±10 V        |

| [41]      | _                                         | 1 MO-OTA, 1<br>multiplier                    | 1 R, 1 C                                  | Both     | Yes                            | Grounded                                       | ±1.25 V/±5 V |

| [42]      | 1 R                                       | 1 DDCC, 1 multiplier                         | 1 R, 1 C                                  | Sim.     | No                             | Floating                                       | ±1.5         |

| [43]      | 3 R                                       | 3 OTAs, 4 CCIIs                              | 3 R, 1 C                                  | Both     | Yes                            | Floating                                       | ±15          |

| [44]      | 2 R                                       | 4 CCIIs (AD844), 1<br>multiplier (AD633)     | 3 R, 1 C                                  | Both     | No                             | Floating                                       | ±10 V        |

| [45]      | _                                         | 1 OTA, 2 transistors                         | 1 C                                       | Sim.     | No                             | Floating                                       | ±1 V         |

| [47]      | _                                         | 10 transistors                               | 3 C                                       | Sim.     | No                             | Floating                                       | _            |

**Table 3.** Comparison of memristor emulator circuits.

#### 4. Conclusion

In this chapter, memristor devices, models, and emulators have been referred. Memristors have nonlinear characteristics; therefore, high-order mathematical equations should be used to create a mathematical model of the memristor. Active circuit elements are essential to build memristor emulators because of the fact that active elements are versatile and suitable for nonlinear circuit element designs. Nowadays, memristors can exhibit different characteristics when they are fabricated using various materials. Important characteristics such as switching mechanism, synaptic behavior, and operating frequency region are directly depending on the memristor structure. Hence, there is an essential to implement various models and circuits to emulate real memristors. Some emulator circuits exhibit hard-switching characteristics, other emulators exhibit smooth-switching characteristics, or some emulators account for spike-timing-dependent plasticity mechanism.

As a result, researchers are not able to reach real memristor easily so all emulator models and circuits are important to exhibit real memristors. Memristors are ultradense devices

and consume very low energy; that is why it is not only important to emulate real emulator. Researchers need also emulator circuits which have minimum energy consumption and simple structure.

#### **Author details**

Abdullah Yesil<sup>1</sup>, Fatih Gül<sup>2</sup> and Yunus Babacan<sup>3\*</sup>

- \*Address all correspondence to: yunusbabacan@gmail.com

- 1 Department of Naval Architecture and Marine Engineering, Bandirma Onyedi Eylul University, Balikesir, Turkey

- 2 Department of Software Engineering, Gumushane University, Gumushane, Turkey

- 3 Department of Electrical and Electronic Engineering, Erzincan University, Erzincan, Turkey

#### References

- [1] Chua LO. Memristor-the missing circuit element. IEEE Transactions on Circuit Theory. 1971;18:507-519. DOI: 10.1109/TCT.1971.1083337

- [2] Chua LO, Kang SM. Memristive devices and systems. Proceedings of the IEEE. 1976; 64:209-223. DOI: 10.1109/PROC.1976.10092

- [3] Strukov DB, Snider GS, Stewart DR, Williams RS. The missing memristor found. Nature. 2008;453:80-83. DOI: 10.1038/nature06932

- [4] William RS. How we found the missing Memristor. IEEE Spectrum. 2008;**45**:29-35. DOI: 10.1109/MSPEC.2008.4687366

- [5] Wolf SJ, Joglekar YN. The elusive memristor: Properties of basic electrical circuits. European Journal of Physics. 2009;**30**:1-24. DOI: 10.1088/0143-0807/30/4/001

- [6] Biolek Z, Biolek D, Biolkova V. Spice model of memristor with nonlinear dopant drift. Radioengineering. 2009;**18**:210-214

- [7] Prodromakis T, Peh BP, Papavassiliou C, Toumazou C. A versatile memristor model with nonlinear dopant kinetics. IEEE Transactions on Electron Devices. 2011;58:3099-3105. DOI: 10.1109/TED.2011.2158004

- [8] Lehtonen E, Laiho M. CNN using memristors for neighborhood connections. In: 12th International Workshop on Cellular Nanoscale Networks and Their Applications (CNNA). 2010. pp. 1-4. DOI: 10.1109/CNNA.2010.5430304

- [9] Pickett D. Switching dynamics in titanium dioxide memristive devices. Applied Physics. 2009;**106**:74508-74514. DOI: 10.1063/1.3236506

- [10] Kvatinsky S, Friedman EG, Kolodny A, Weiser UC. TEAM: Threshold adaptive memristor model. IEEE Transactions on Circuits and Systems I: Regular Papers. 2013;60:211-221. DOI: 10.1109/TCSI.2012.2215714

- [11] Adhikari SP, Sah MP, Kim H, Chua LO. Three fingerprints of memristor. IEEE Tran sactions on Circuits and Systems I: Regular Papers. 2013;60:3008-3021. DOI: 10.1109/TCSI.2013.2256171

- [12] Hickmott TW. Low-frequency negative resistance in thin anodic oxide films. Journal of Applied Physics. 1962 Sep;33(9):2669-2682

- [13] Sawa A. Resistive switching in transition metal oxides. Materials Today. 2008;**11**:28-36. DOI: 10.1016/S1369-7021(08)70119-6

- [14] Chua L. Resistance switching memories are memristors. Applied Physics A: Materials Science & Processing. 2011;**102**:765-783. DOI: 10.1007/s00339-011-6264-9

- [15] Lim EW, Ismail R. Conduction mechanism of valence change resistive switching memory: A survey. Electronics. 2015;4:586-613. DOI: 10.3390/electronics4030586

- [16] Strukov DB, Kohlstedt H. Resistive switching phenomena in thin films: Materials, devices, and applications. MRS Bulletin. 2012;37:108-114. DOI: 10.1557/mrs.2012.2

- [17] Huang CH, Huang JS, Lin SM, Chang WY, He JH, Chueh YL. ZnO1–x nanorod arrays/ZnO thin film bilayer structure: From homojunction diode and high-performance memristor to complementary 1D1R application. ACS Nano. 2012 Sep 6;6(9):8407-8414

- [18] Ielmini D. Resistive switching memories based on metal oxides: Mechanisms, reliability and scaling. Semiconductor Science and Technology. May 2016;**31**(6):063002

- [19] Gul F, Efeoglu H. ZnO and ZnO1–x based thin film memristors: The effects of oxygen deficiency and thickness in resistive switching behavior. Ceramics International. 2017;43(14):10770-10775. DOI: 10.1016/j.ceramint.2017.05.090

- [20] Akinaga H, Shima H. Resistive random access memory (ReRAM) based on metal oxides. Proceedings of the IEEE. 2010 Dec;98(12):2237-2251

- [21] Gul F, Efeoglu H. Bipolar resistive switching and conduction mechanism of an Al/ZnO/Al-based memristor. Superlattices and Microstructures. 2017 Jan 31;101:172-179

- [22] Boratto MH, Ramos RA, Congiu M, Graeff CF, Scalvi LV. Memristive behavior of the SnO<sub>2</sub>/TiO<sub>2</sub> interface deposited by sol–gel. Applied Surface Science. 2017 Jul 15;**410**:278-281

- [23] He W, Sun H, Zhou Y, Lu K, Xue K, Miao X. Customized binary and multi-level HfO<sub>2-x</sub>-based memristors tuned by oxidation conditions. Scientific Reports. 2017;7:10070

- [24] Lian X, Wang M, Rao M, Yan P, Yang JJ, Miao F. Characteristics and transport mechanisms of triple switching regimes of TaOx memristor. Applied Physics Letters. 2017 Apr 24; 110(17):173504

- [25] Benderli S, Wey TA. On SPICE macromodelling of TiO<sub>2</sub> memristors. Electronics Letters. 2009;**45**:377-379. DOI: 10.1049/el.2009.3511

- [26] Zhang Y, Zhang X, Yu J. Approximated SPICE model for memristor. International Conference on Communications, Circuits and Systems, ICCCAS. 2009. pp. 928-931. DOI: 10.1109/ICCCAS.2009.5250371

- [27] Biolek D, Biolek Z, Biolkova V. SPICE modeling of memristive, memcapacitative and meminductive systems. Circuit Theory and Design. European Conference on IEEE. 2009. pp. 249-252. DOI: 10.1109/ECCTD.2009.5274934

- [28] Chen Y, Wang X. Compact modeling and corner analysis of spintronic memristor. In: International Symposium on Nanoscale Architectures. 2009. pp. 7-12. DOI: 10.1109/ NANOARCH.2009.5226363

- [29] Yang JJ, Strukov DB, Stewart DR. Memristive devices for computing. Nature Nanotechnology. 2013;8:13-24

- [30] Yakopcic C, Taha TM, Subramanyam G, Pino RE, Rogers S. A memristor device model. IEEE Electron Device Letters. 2011;**32**:1436-1438. DOI: 10.1038/nnano.2012.240

- [31] Williams RS, Pickett MD, Strachan JP. Physics-based memristor models. IEEE International Circuits and Systems (ISCAS). 2013. pp. 217-220. DOI: 10.1109/ISCAS.2013.6571821

- [32] Pershin Y, Di Ventra M. SPICE model of memristive devices with threshold. Radio-engineering. 2013;**22**(2):11-15

- [33] Babacan Y, Kacar F, Gurkan K. A spiking and bursting neuron circuit based on Memristor. Neurocomputing. 2016;**203**:86-91. DOI: 10.1016/j.neucom.2016.03.060

- [34] Mutlu R, Karakulak E. Emulator circuit of TiO<sub>2</sub> memristor with linear dopant drift made using analog multiplier. Electrical and Electronics and Computer Engineering (ELECO). 2010. pp. 380-384

- [35] Yener SC, Kuntman HH. Fully CMOS memristor based chaotic circuit. Radioengineering. 2014;23:1140-1149

- [36] Ayten UE, Minayi S, Sagbas M. Memristor emulator circuits using single CBTA. International Journal of Electronics and Communicatons (AEÜ). 2017;82:109-118. DOI: 10.1016/j.aeue.2017.08.008

- [37] Minaei S, Göknar IC, Yıldız M, Yuce E. Memstor, memstance simulations via a versatile 4-port built with new adder and subtractor circuits. International Journal of Electronics. 2015;102:911-931. DOI: 10.1080/00207217.2014.942890

- [38] Kim H, Sah MP, Yang C, Cho S, Chua LO. Memristor emulator for memristor circuit applications. IEEE Transactions on Circuits and Systems I: Regular Papers. 2012;**59**(10):2422-2431. DOI: 10.1109/TCSI.2012.2188957

- [39] Abuelma'atti MT, Khalifa ZJ. A new memristor emulator and its application in digital modulation. Analog Integrated Circuits Signal Process. 2014;80:577-584. DOI: 10.1007/s10470-014-0364-3

- [40] Sánchez-López C, Aguila-Cuapio LE. A 860 kHz grounded memristor emulator circuit. International Journal of Electronics and Communications (AEÜ). 2017;73:23-33. DOI: 10.1016/j.aeue.2016.12.015

- [41] Babacan Y, Yesil A, Kacar F. Memristor emulator with tunable characteristic and its experimental results. International Journal of Electronics and Communicatons (AEÜ). 2017;81:99-104. DOI: 10.1016/j.aeue.2017.07.012

- [42] Yesil A, Babacan Y, Kacar F. A new DDCC based memristor emulator circuit and its applications. Microelectronics Journal. 2014;45(3):282-287. DOI: 10.1016/j.mejo.2014.01.011

- [43] Sözen H, Çam U. Electronically tunable memristor emulator circuit. Analog Integrated Circuits and Signal Processing. 2016;89:655-663. DOI: 10.1007/s10470-016-0785-2

- [44] Sánchez-López C, Mendoza-López J, Aguila-Cuapio MA, Muñiz-Montero C. A floating analog memristor emulator circuit. IEEE Transactions on Circuits and Systems II: Express Briefs. 2014;61:309-313. DOI: 10.1109/TCSII.2014.2312806

- [45] Babacan Y, Kacar F. Floating memristor emulator with subthreshold region. Analog Integrated Circuits and Signal Processing. 2016;90:471-475. DOI: 10.1007/s10470-016-0888-9

- [46] Li Q, Serb A, Prodromakis T, Xu H. Memristor SPICE model accounting for synaptic activity dependence. PLoS One. 2015;10(3):1-12. DOI: 10.1371/journal.pone.0120506

- [47] Babacan Y, Kacar F. Memristor emulator with spike-timing-dependent-plasticity. AEU-International Journal of Electronics and Communications. 2017;73:16-22. DOI: 10.1016/j. aeue.2016.12.025

- [48] Jo SH, Chang T, Ebong I, Bhadviya BB, Mazumder P, et al. Nanoscale memristor device as synapse in neuromorphic systems. Nano Letters. 2010;10:1297-1301. DOI: 10.1021/ nl904092h

- [49] Berdan R, Xu HY, Li XH, Yu H, Liu YC, et al. Synaptic learning and memory functions achieved using oxygen ion migration/diffusion in an amorphous InGaZnO memristor.

Advanced Functional Materials. 2012;22:2759-2765. DOI: 10.1002/adfm.201103148

- [50] Li Y, Zhong Y, Xu L, Zhang J, Xu X, et al. Ultrafast synaptic events in a chalcogenide memristor. Scientific Reports. 2013;3:1619. DOI: 10.1038/srep01619

## IntechOpen

# IntechOpen