# We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

6,900

185,000

200M

Downloads

154

Countries delivered to

Our authors are among the

$\mathsf{TOP}\:1\%$

most cited scientists

12.2%

Contributors from top 500 universities

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected.

For more information visit www.intechopen.com

# A Reduced Switch Asymmetric Multilevel Inverter Topology Using Unipolar Pulse Width Modulation Strategies for Photovoltaic Application

Natarajan Prabaharan, Subramani Saravanan,

Amalorpavaraj Rini Ann Jerin and

Kaliannan Palanisamy

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/67863

#### **Abstract**

A new design of multilevel inverter configuration is proposed for reducing the component count and improving the quality of waveform in a photovoltaic system. The proposed configuration operates at the binary asymmetric condition for generating the large amount output voltage level with small amount harmonic distortion. Unipolar trapezoidal reference with triangular carriers is used for generating the desired switching pulses to generate the required output voltage level. The proposed configuration requires eight unipolar switches for generating the 31-level output voltage level with total harmonic distortion of 3.18% without using any filters. The value of %total harmonic distortion (THD) satisfies the IEEE 519 harmonic standard. Separate DC sources of proposed configuration are replaced by the array of photovoltaic panels for testing the configuration with the renewable energy source. The proposed configuration is tested with an experimental setup for proving the operation of it. Selected simulation and experimental results are shown for the verification of proposed configuration ability.

**Keywords:** multilevel inverter, pulse width modulation, trapezoidal waveform, reduced switch inverter

# 1. Introduction

The theory of multilevel inverter has been discussed over 30 years ago. The multilevel inverter (MLI) has many advantages when compared to conventional two-level inverter such as withstanding high voltage capability, lower harmonic distortion, lower switching losses, lower switching stress, and producing high quality of output voltage with better electromagnetic compatibility [1]. Due to that numerous advantages, the adoption of multilevel inverter has been tremendously expanded in the area of medium or high power and medium or high voltage application [2]. Generally, diode clamped multilevel inverter (DCMLI), flying capacitor multilevel inverter (FCMLI), and cascaded H-bridge multilevel (CHBMLI) are three remarkable traditional MLI topologies [3]. The drawback of conventional MLIs is the total number of components. The count of components is directly proportional to the number of levels. The balancing of voltage across DC bus capacitor in FCMLI and DCMLI is the difficult task. Also, the presence of clamping diodes and clamping capacitors in DCMLI and FCMLI, respectively, makes the circuit complex, costly and large size [4]. To overwhelm those drawbacks, numerous topologies for multilevel inverter have been introduced recently.

Reduced switch multilevel inverter configurations have their own advantages and disadvantages. In Refs. [5–20], the configurations require bidirectional switches for achieving the desired output voltage level. Utilizing of bidirectional switches increases, the total count of switches in those configurations, because the combination of two unipolar switches makes one bidirectional switch using the concept of emitter coupled to both switches. In Refs. [21–25], the transformers have utilized for generating the required output voltage level. The usage of a transformer in that configuration makes the system bulky, costly, less life span and requires more maintenance. The transformer is connected to the secondary side in series to achieve the required output voltage level. In Refs. [8, 10, 12, 14], configuration utilizes more diode and capacitors for generating the required output voltage level. The balancing of capacitor voltage is more important to achieve the particular level of the output voltage waveform.

In this chapter, the reduced switch configuration is proposed without any bidirectional switches and transformer. Therefore, the proposed configuration size and cost are considerably low. It requires only eight switches for generating the 31-level output voltage level with total harmonic distortion of 3.18%. Multicarrier unipolar trapezoidal reference with triangular carrier pulse width modulation technique is utilized for generating the switching pulses for the proposed configuration. The proposed configuration has a minimum number of conducting switches for generating per voltage level. Also, this configuration requires minimum power loss (switching loss + conduction loss) for a different number of levels when compared to other MLIs. Also, the proposed configuration is tested with the photovoltaic system for checking the ability of it.

The remaining section of this chapter is as follows: Section 2 describes the operation of proposed multilevel inverter configuration with an asymmetric condition. Section 3 describes with the multicarrier unipolar trapezoidal pulse width modulation with three different carriers such as phase disposition, alternative phase opposition and disposition and variable frequency. Section 4 describes with proposed multilevel inverter configuration integrated with the photovoltaic system. Section 5 describes with results and discussion of the proposed multilevel inverter. Section 6 ends with conclusion of this chapter.

# 2. Proposed multilevel inverter configurations

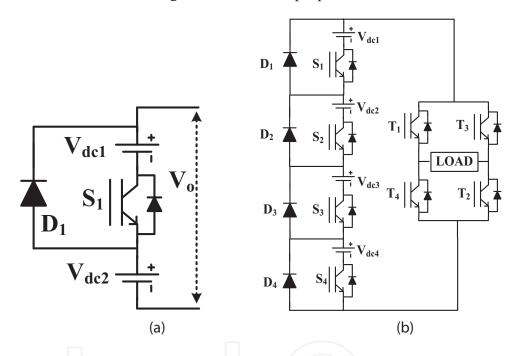

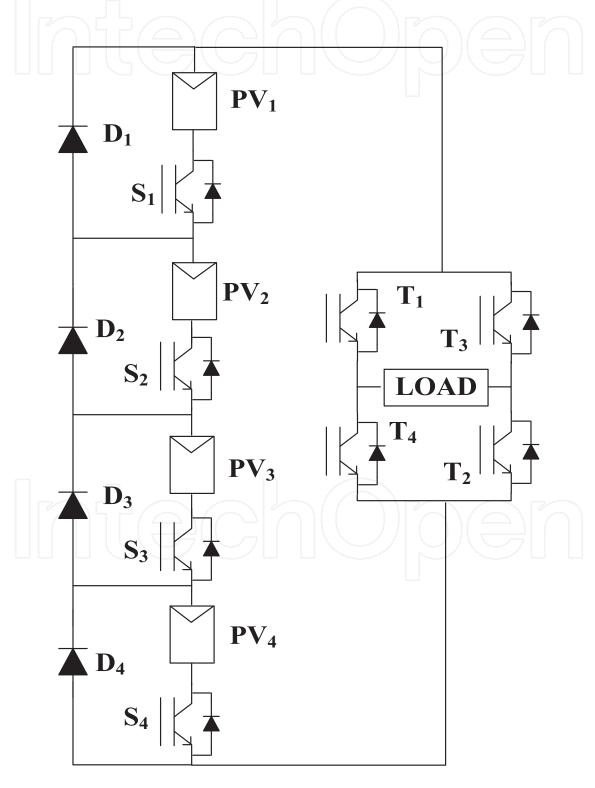

The proposed multilevel inverter configuration is the combination of power semiconductor switches and bypass diodes. **Figure 1a** shows the basic structure for the proposed MLI configuration. The bypass diode is connected in parallel with the combination of power semiconductor switch and DC voltage source. The basic structure has two different modes of operation. When the switch  $T_1$  is turned on, the  $V_{dc1}$  voltage appears across the diode D1. Therefore, the value of output voltage is  $2V_{dc}$  ( $V_{dc1} + V_{dc2}$ ). When the switch  $T_1$  is turned off, the bypass diode conducts to generate the  $V_{dc}$  output voltage. The higher number of levels can generate the cascading connection of proposed basic structure. Symmetric and asymmetric are the two different conditions of multilevel inverter for generating the output voltage level. Generally, symmetric multilevel inverter produces the minimum count of output voltage level when compared to an asymmetric multilevel inverter. **Figure 1b** shows the proposed multilevel inverter configuration

Figure 1. Proposed configuration. (a) Basic structure. (b) Proposed multilevel inverter configuration.

| Parameters               | Generalized formulas      |

|--------------------------|---------------------------|

| Value of DC sources      | $2^n$ where $n = 0, 1, 2$ |

| Ratio of DC sources      | 1: 2: 4: 8                |

| Number of switches       | k+4                       |

| Number of DC source      | k                         |

| Number of diodes         | k+4                       |

| Number of driver circuit | k+4                       |

| Number of level          | $2^{k+1}-1$               |

Table 1. Generalized formula for the different parameters in proposed multilevel inverter.

for generating the 31-level output voltage. The DC sources are assumed as an asymmetric condition in which binary sequence is adopted. The ratio of binary sequence is 1:2:4:8. The configuration is the combination of single phase H-Bridge inverter and reduced switch configuration. The reduced switch configuration contains the set of single DC source, switch and bypass diode is connected in series. **Table 1** shows the generalized formula for the proposed multilevel inverter configuration. **Table 2** shows the switching table for the proposed topology for generating the 31-level output voltage in both positive and negative polarity.

| Modes | Conducting switches and diodes                                                                      | Output<br>voltage | Modes | Conducting switches and diodes                                                                      | Output<br>Voltage |

|-------|-----------------------------------------------------------------------------------------------------|-------------------|-------|-----------------------------------------------------------------------------------------------------|-------------------|

| 1     | S <sub>1</sub> , D <sub>2</sub> , D <sub>3</sub> , D <sub>4</sub> , T <sub>1</sub> , T <sub>2</sub> | $V_{dc}$          | 1     | S <sub>1</sub> , D <sub>2</sub> , D <sub>3</sub> , D <sub>4</sub> , T <sub>3</sub> , T <sub>4</sub> | $-V_{dc}$         |

| 2     | S <sub>2</sub> , D <sub>1</sub> , D <sub>3</sub> , D <sub>4</sub> , T <sub>1</sub> , T <sub>2</sub> | $2V_{\rm dc}$     | 2     | S <sub>2</sub> , D <sub>1</sub> , D <sub>3</sub> , D <sub>4</sub> , T <sub>3</sub> , T <sub>4</sub> | $-2V_{dc}$        |

| 3     | S <sub>1</sub> , S <sub>2</sub> , D <sub>3</sub> , D <sub>4</sub> , T <sub>1</sub> , T <sub>2</sub> | $3V_{dc}$         | 3     | S <sub>1</sub> , S <sub>2</sub> , D <sub>3</sub> , D <sub>4</sub> , T <sub>3</sub> , T <sub>4</sub> | $-3V_{dc}$        |

| 4     | S <sub>3</sub> , D <sub>1</sub> , D <sub>2</sub> , D <sub>4</sub> , T <sub>1</sub> , T <sub>2</sub> | $4V_{dc}$         | 4     | S <sub>3</sub> , D <sub>1</sub> , D <sub>2</sub> , D <sub>4</sub> , T <sub>3</sub> , T <sub>4</sub> | $-4V_{dc}$        |

| 5     | S <sub>1</sub> , S <sub>3</sub> , D <sub>2</sub> , D <sub>4</sub> , T <sub>1</sub> , T <sub>2</sub> | $5V_{dc}$         | 5     | S <sub>1</sub> , S <sub>3</sub> , D <sub>2</sub> , D <sub>4</sub> , T <sub>3</sub> , T <sub>4</sub> | $-5V_{dc}$        |

| 6     | S <sub>2</sub> , S <sub>3</sub> , D <sub>1</sub> , D <sub>4</sub> , T <sub>1</sub> , T <sub>2</sub> | $6V_{dc}$         | 6     | S <sub>2</sub> , S <sub>3</sub> , D <sub>1</sub> , D <sub>4</sub> , T <sub>3</sub> , T <sub>4</sub> | $-6V_{dc}$        |

| 7     | S <sub>1</sub> , S <sub>2</sub> , S <sub>3</sub> , D <sub>4</sub> , T <sub>1</sub> , T <sub>2</sub> | $7V_{dc}$         | 7     | S <sub>1</sub> , S <sub>2</sub> , S <sub>3</sub> , D <sub>4</sub> , T <sub>3</sub> , T <sub>4</sub> | $-7V_{dc}$        |

| 8     | S <sub>4</sub> , D <sub>1</sub> , D <sub>2</sub> , D <sub>3</sub> , T <sub>1</sub> , T <sub>2</sub> | $8V_{dc}$         | 8     | S <sub>4</sub> , D <sub>1</sub> , D <sub>2</sub> , D <sub>3</sub> , T <sub>3</sub> , T <sub>4</sub> | $-8V_{dc}$        |

| 9     | S <sub>1</sub> , S <sub>4</sub> , D <sub>2</sub> , D <sub>3</sub> , T <sub>1</sub> , T <sub>2</sub> | $9V_{dc}$         | 9     | S <sub>1</sub> , S <sub>4</sub> , D <sub>2</sub> , D <sub>3</sub> , T <sub>3</sub> , T <sub>4</sub> | $-9V_{dc}$        |

| 10    | S <sub>2</sub> , S <sub>4</sub> , D <sub>1</sub> , D <sub>3</sub> , T <sub>1</sub> , T <sub>2</sub> | $10V_{dc}$        | 10    | S <sub>2</sub> , S <sub>4</sub> , D <sub>1</sub> , D <sub>3</sub> , T <sub>3</sub> , T <sub>4</sub> | $-10V_{dc}$       |

| 11    | S <sub>1</sub> , S <sub>2</sub> , S <sub>4</sub> , D <sub>3</sub> , T <sub>1</sub> , T <sub>2</sub> | $11V_{dc}$        | 11    | S <sub>1</sub> , S <sub>2</sub> , S <sub>4</sub> , D <sub>3</sub> , T <sub>3</sub> , T <sub>4</sub> | $-11V_{dc}$       |

| 12    | S <sub>3</sub> , S <sub>4</sub> , D <sub>1</sub> , D <sub>2</sub> , T <sub>1</sub> , T <sub>2</sub> | $12V_{dc}$        | 12    | S <sub>3</sub> , S <sub>4</sub> , D <sub>1</sub> , D <sub>2</sub> , T <sub>3</sub> , T <sub>4</sub> | $-12V_{dc}$       |

| 13    | S <sub>1</sub> , S <sub>3</sub> , S <sub>4</sub> , D <sub>2</sub> , T <sub>1</sub> , T <sub>2</sub> | $13V_{dc}$        | 13    | S <sub>1</sub> , S <sub>3</sub> , S <sub>4</sub> , D <sub>2</sub> , T <sub>3</sub> , T <sub>4</sub> | $-13V_{dc}$       |

| 14    | S <sub>2</sub> , S <sub>3</sub> , S <sub>4</sub> , D <sub>1</sub> , T <sub>1</sub> , T <sub>2</sub> | $14V_{dc}$        | 14    | S <sub>2</sub> , S <sub>3</sub> , S <sub>4</sub> , D <sub>1</sub> , T <sub>3</sub> , T <sub>4</sub> | $-14V_{dc}$       |

| 15    | S <sub>1</sub> , S <sub>2</sub> , S <sub>3</sub> , S <sub>4</sub> , T <sub>1</sub> , T <sub>2</sub> | $15V_{dc}$        | 15    | S <sub>1</sub> , S <sub>2</sub> , S <sub>3</sub> , S <sub>4</sub> , T <sub>3</sub> , T <sub>4</sub> | $-15V_{dc}$       |

Table 2. Switching table for generating 31-level output voltage in proposed configuration.

# 3. Switching techniques

The pulse width modulation is the most important and effective switching technique for controlling the multilevel inverter output voltage. Based on PWM technique, the output voltage can be easily converted to sinusoidal waveform by utilizing the less size of passive filters. Generally, sinusoidal pulse width modulation technique (SPWM) is utilized for generating the switching pulses to achieve the desired output voltage waveform [26–29]. In this chapter, the proposed configuration switches are triggered by using the trapezoidal reference with triangular carriers. Trapezoidal pulse width modulation technique is one of the types of advanced pulse width modulation technique. This technique provides better performance output voltage when compared with sinusoidal pulse width modulation technique which is the main advantage [28]. The combination of two slopes and one horizontal line makes the trapezoidal reference waveform. Generally, the waveform can be attained by the triangular reference waveform by limiting the magnitude or peak value of the waveform.

The angle of horizontal line of the waveform is as follows:

$$2\emptyset = (1 - \sigma)\pi\tag{1}$$

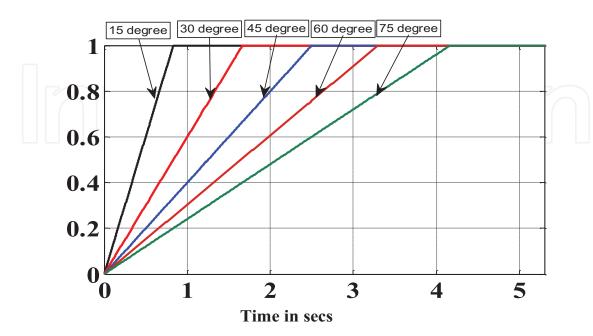

where  $\sigma$  is called the triangular factor. If the triangular factor is  $\sigma$  = 1, the waveform shape will become triangular waveform. The shape of trapezoidal waveform is purely depending on the location of slope angle ( $\alpha$ ). **Figure 2** shows the different angle of slope for the trapezoidal waveform. The harmonic content and waveform quality will differ based on the different locations of the slope angle ( $\alpha$ ). The mathematical formula for calculating the harmonic amplitude for different slope of different order is given by

$$A_n = \frac{4}{\pi} \int_{0}^{\pi/2} F(\theta) \sin n\theta \, d\theta \tag{2}$$

where

$$F(\theta) = \begin{cases} 1/\alpha \ 0^{\circ} < \theta < \alpha \\ 1 \ \alpha < \theta < 90^{\circ} \end{cases}$$

(3)

So, the Eq. (8) can be written as follows

$$A_{n} = \frac{4}{2\pi} \left[ \left[ \frac{-\theta k \cos(n\theta)}{n} \right] \right]_{0}^{\alpha} + \frac{1}{n} \int_{0}^{\alpha} k \cos(n\theta) d\theta + \frac{4}{\pi} \int_{0}^{\pi/2} \sin(n\theta) d\theta$$

(4)

Figure 2. Different angle of slope in trapezoidal reference.

The above equation can be simplified and rewritten as follows

$$A_n = \frac{4}{n^2 \pi} \times \frac{\sin(n\alpha)}{\alpha} \tag{5}$$

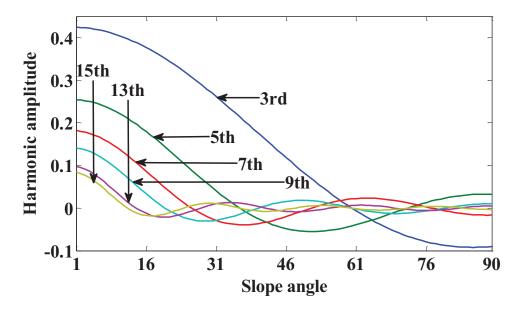

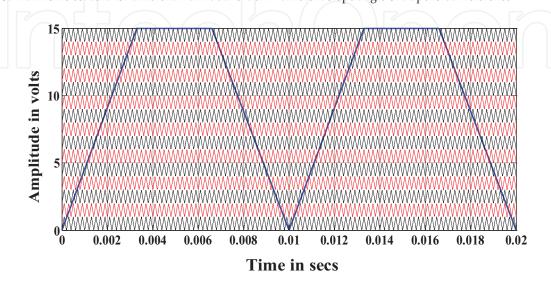

**Figure 3** shows the harmonic content of different harmonic order for different slope angle. From that **Figure 3**, it is evident that the harmonic order value increases when the slope angle near to zero degree. If the slope angle moves towards to 90 degree, the harmonic order value decreases. In this paper, the slope of the trapezoidal reference waveform is considered as 60°. Also, in this paper, unipolar reference is considered for generating the switching pulses. In unipolar, the carriers count is reduced half of the value when compared to bipolar PWM technique, which is the main advantage of unipolar PWM method [26]. The proposed topology is tested with phase disposition (PD) carrier arrangement. Phase disposition defines that the utilization of 15 carriers is each in phase with same amplitude and frequency. The representation of unipolar trapezoidal reference with phase disposition carriers is shown in **Figure 4**.

Figure 3. Harmonic content for different individual order in different slope angle of trapezoidal reference.

Figure 4. Unipolar trapezoidal reference with PD carrier arrangement.

# 4. Proposed MLI integrated with photovoltaic system

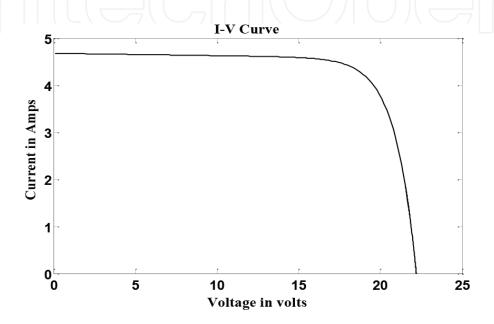

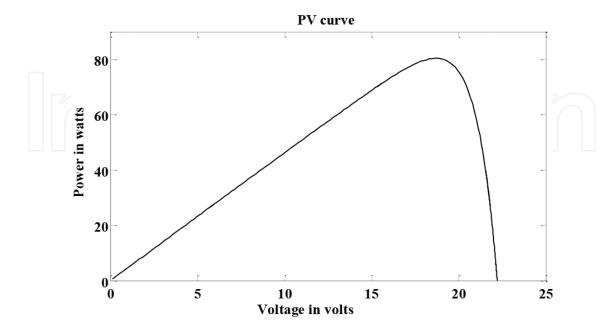

The proposed multilevel inverter requires four separate DC sources for generating the 31-level output voltage. So, the separate DC sources are replaced by the photovoltaic panel or array of photovoltaic panel depends on the input value of proposed multilevel inverter configuration. In this work, 80 W photovoltaic panel is considered. **Figure 5** shows that the proposed multilevel

Figure 5. Proposed configuration integrated with photovoltaic system.

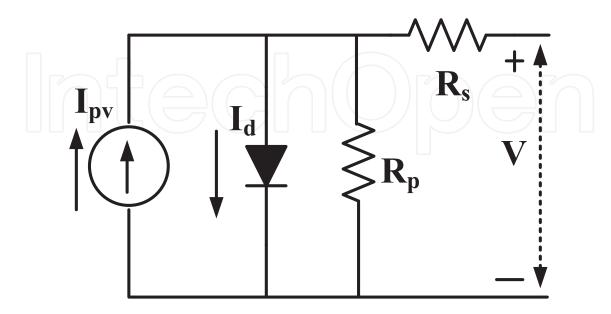

inverter is integrated with the photovoltaic system. For a conventional type, the integration of MLI with photovoltaic system requires separate solar panel with separate boost converter with MPPT technique for achieving the required output voltage level. Therefore, the system becomes complexity, and an initial cost of the system is too high. To overcome this drawback, this chapter proposed that the array of PV panels is connected in the series manner to achieve the required output voltage. The array of PV panels is directly connected to the proposed MLI for replacing the each DC source of it. In future, the same study is further extended with the high gain multi-output converters with appropriate MPPT techniques for reducing the count of PV array panels. The first DC source of proposed MLI is replaced by a single photovoltaic panel. The second DC source of proposed MLI is replaced by the series connection of two 80 W photovoltaic panel. The third and fourth DC sources are placed by the series connection of four panels and eight panels, respectively. Figure 6 shows the single diode model equivalent circuit for the photovoltaic cell. Figures 7 and 8 show the I-V and P-V characteristics of the PV model. The generalized formula for photovoltaic panel is modeled as follows [30, 31]

$$I = I_{PV} - I_o \left[ exp\left(\frac{V + R_s I}{aV_t}\right) - 1 \right] - \frac{V + R_s I}{R_p} ; V_t = \frac{V_s kT}{q}$$

$$\tag{6}$$

$$I_{PV} = (I_{PV,n} + K_I \Delta_t) \frac{G}{G_n} \tag{7}$$

$$I_{o} = \frac{I_{sc,n} + K_{I}\Delta_{t}}{exp[(V_{oc,n} + K_{V}\Delta_{t})/aV_{t}] - 1}$$

(8)

where k, a, T and q denote Boltzmann constant (1.3806503  $\times$  10<sup>-23</sup> J/K), diode ideality constant, absolute temperature (K), and electron charge (1.60217646  $\times$  10<sup>-19</sup> C), respectively.  $I_{PV}$  and  $I_o$  denote photovoltaic current and saturation current of array, respectively.  $I_{PV,n}$  represents

Figure 6. Single diode model equivalent circuit.

nominal PV current, and  $R_s$  and  $R_p$  denote equivalent series and parallel resistance of solar cell respectively.  $V_t$  denotes thermal voltage.  $N_s$  and  $N_p$  denote solar cells connected in series and solar cells connected in parallel, respectively.  $V_{oc,n}$  and  $I_{sc,n}$  indicate open circuit voltage and nominal short circuit current, respectively;  $K_V$  and  $K_I$  represent the short circuit voltage/temperature co-efficient and short circuit current/temperature co-efficient, respectively;  $T_n$  indicates nominal temperature (K); G and  $G_n$  represent irradiation (W/m²) on the device surface and nominal irradiation and  $\Delta_t$  indicates  $T - T_n$ , difference between actual and normal temperature. **Table 3** shows the parameters value for the 80 W photovoltaic panel.

Figure 7. I-V characteristics of photovoltaic panel.

Figure 8. P-V characteristics of photovoltaic panel.

| Parameters                               | Values  |

|------------------------------------------|---------|

| Short circuit current ( $I_{sc}$ )       | 4.71 A  |

| Open circuit voltage ( $V_{oc}$ )        | 22.24 V |

| Maximum power point voltage $(V_{mp})$   | 18.33 V |

| Maximum power point current ( $I_{mp}$ ) | 4.37 A  |

| Maximum power $(P_{mp})$                 | 80 W    |

| Capacitors ( $C_1$ – $C_4$ )             | 1500 μF |

Table 3. Different parameters value for photovoltaic panel.

#### 5. Result and discussion

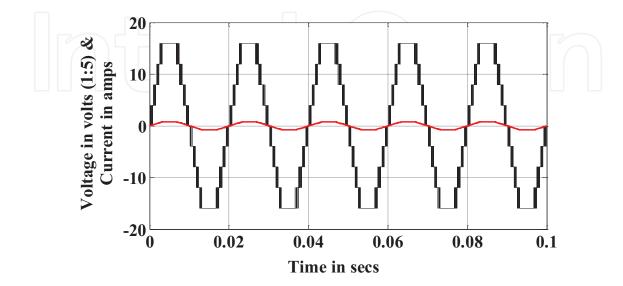

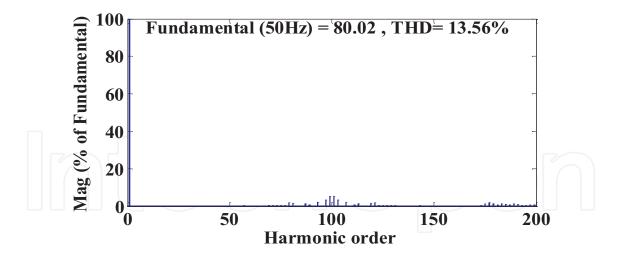

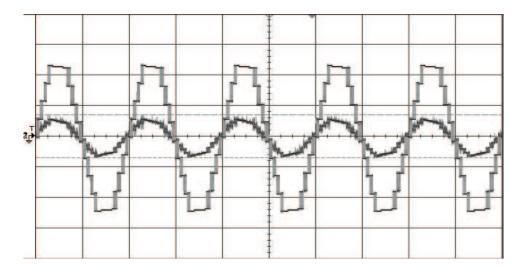

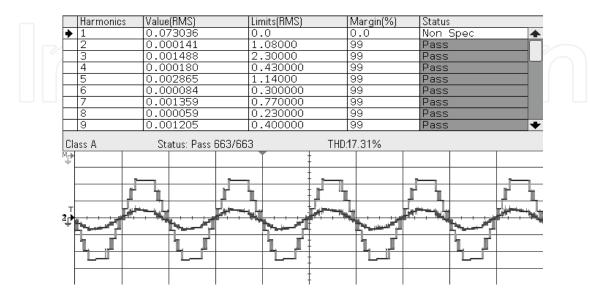

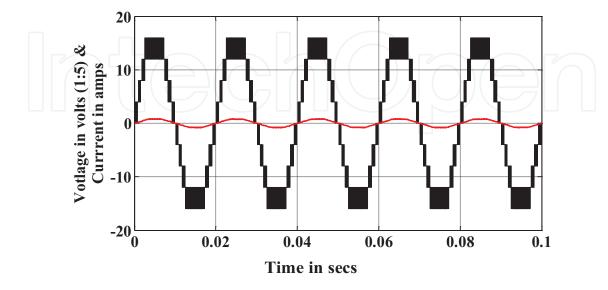

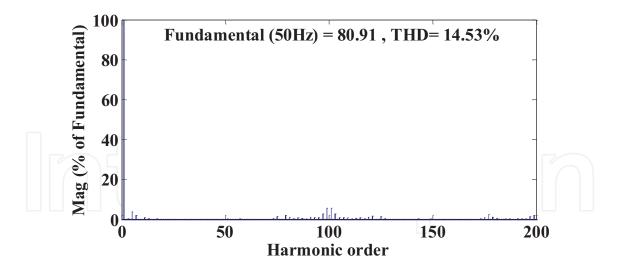

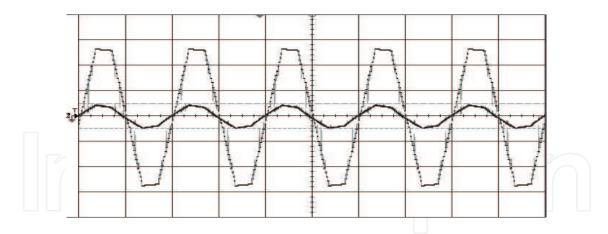

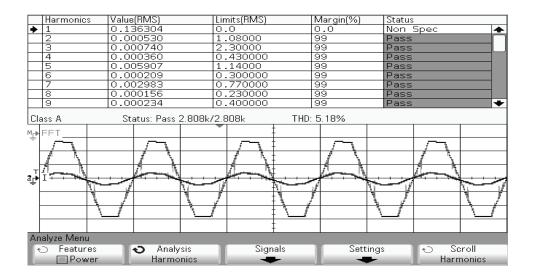

The conventional CHBMLI and proposed MLI configuration are tested with MATLAB/ SIMULINK for generating the 9-level and 31-level output voltage with trapezoidal pulse width modulation technique for the same number of DC source. Here, the conventional CHBMLI consists of four single H-bridge multilevel inverters which are connected in series. The conventional CHBMLI and proposed MLI configuration are tested with laboratory-based experimental set up for generating the desired output voltage using dSpace 1104 real-time controller. The unipolar PWM trapezoidal reference with triangular carriers is utilized for generating the switching pulses of the proposed multilevel inverter configuration switches in simulation and experimental step-up. Insulated Gate Bipolar Transistor (IGBT-FGA25N120) is utilized as switching devices and TLP250 as the IGBT driver for proposed topology. The main reason for selecting this PWM strategy is to produce better harmonic profile as well as to radically reduce the utilization of carrier count. Figures 9 and 10 show the simulation 9-level output voltage, output current and their harmonics plot for output voltage, respectively, for conventional CHBMLI. Figures 11 and 12 show the experimental result of 9-level output voltage and output current and their harmonics plot for the conventional CHBMLI. The conventional CHBMLI is

Figure 9. Simulation results for output voltage and current in conventional CHBMLI.

Figure 10. Harmonics plot for output voltage in conventional CHBMLI.

Figure 11. Experimental results for output voltage and current in conventional CHBMLI (CH1: 30 V/div, CH2: 5 A/div).

Figure 12. Experimental Harmonics plot for output voltage in conventional CHBMLI.

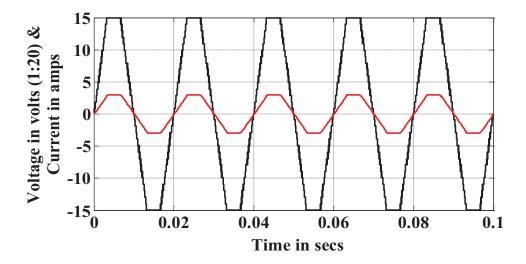

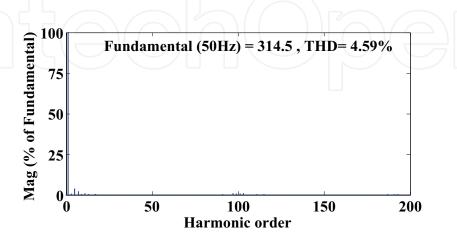

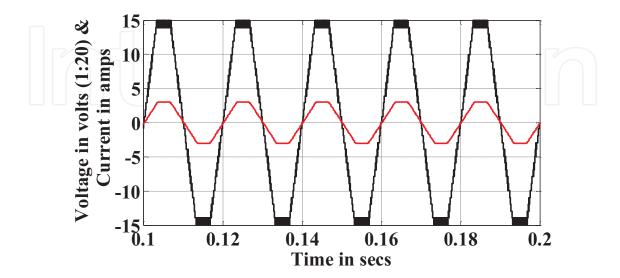

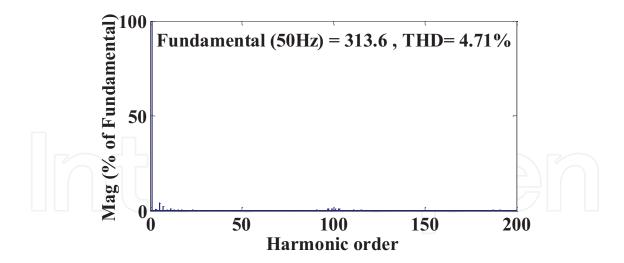

tested with the photovoltaic panels by replacing the separate DC sources. **Figures 13** and **14** show the output voltage and output current and their harmonics plot for the CHBMLI with photovoltaic systems. **Figures 15** and **16** show the simulation output voltage, output current and their harmonics plot for trapezoidal reference with PD carriers. **Figures 17** and **18** show the experimental result of output voltage and output current and their harmonics plot for the proposed topology. Also, this configuration is tested with the photovoltaic panels by replacing the separate DC sources. **Figures 19** and **20** show the output voltage and output current and their harmonics plot for the proposed configuration with photovoltaic systems. The power loss is the addition of switching losses and conduction losses. The switching losses and conduction losses can be calculated using the following formulas [18–19]

$$L_{sw} = \sum_{k=1}^{N_{sw}} \left( \sum_{i=1}^{N_{on,k}} E_{on,k,i} + \sum_{i=1}^{N_{off,k}} E_{off,k,i} \right)$$

(9)

$$L_c(t) = \sum_{k=1}^{N_{sw}} (L_{c,sw,k}(t) + L_{c,d,k}(t))$$

(10)

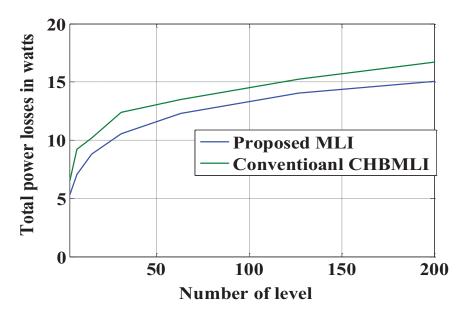

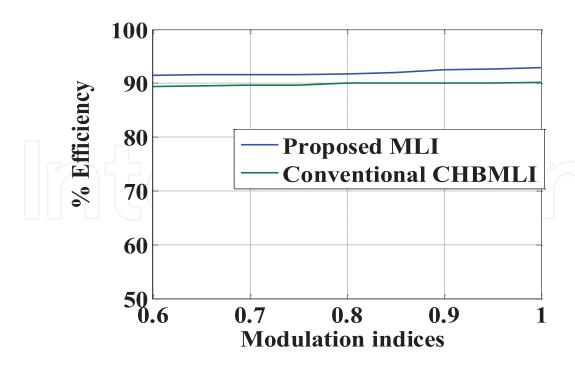

**Figure 21** shows that the total power loss versus a different number of levels for the proposed configuration. Also, the proposed configuration is tested with different modulation indices. **Table 4** shows the comparison table for proposed configuration with conventional MLIs in terms of many factors. From that **Table 4**, it is clearly understood that the proposed configuration requires lesser component count for generating the desired output voltage level. Also, the minimum count of conducting switches is required for generating each voltage level when compared to conventional MLIs. **Figure 22** shows the efficiency graph for the proposed configuration for different modulation indices. Therefore, the proposed configuration provides better results in terms of number of levels, efficiency and switching

Figure 13. Output voltage and current for conventional CHBMLI integrated with PV.

Figure 14. Harmonics plot for output voltage in conventional CHBMLI integrated with PV.

Figure 15. Simulation results for output voltage and current in proposed MLI.

Figure 16. Harmonics plot for output voltage in proposed MLI.

Figure 17. Experimental results for output voltage and current in proposed MLI (CH1: 100 V/div, CH2: 5 A/div).

Figure 18. Experimental harmonics plot for output voltage in proposed MLI.

Figure 19. Output voltage and current for proposed MLI integrated with PV.

Figure 20. Harmonics plot for output voltage in proposed MLI integrated with PV.

Figure 21. Power loss comparisons for proposed MLI with CHBMLI.

|                                              | DCMLI | FCMLI | CHBMLI | Proposed MLI |

|----------------------------------------------|-------|-------|--------|--------------|

| Number of switches                           | 60    | 60    | 60     | 8            |

| Number of DC sources                         | 1     | 1     | 15     | 4            |

| Total number of output voltage levels        | 31    | 31    | 31     | 31           |

| Number of drive circuit                      | 60    | 60    | 60     | 8            |

| Clamping diodes                              | 56    | _     | _      | _            |

| Clamping capacitors                          | _     | 28    | -      | -            |

| DC bus capacitors                            | 30    | 30    | -      | -            |

| Conducting switches/diodes per voltage level | 30    | 30    | 30     | 6            |

Table 4. Comparison table of proposed configuration with conventional MLIs for 31-level output voltage.

Figure 22. Efficiency comparisons for proposed MLI with CHBMLI.

| Parameters          | %THD without solar |              | %THD with solar |

|---------------------|--------------------|--------------|-----------------|

|                     | Simulation         | Experimental | Simulation      |

| Conventional CHBMLI | 13.56              | 17.31        | 14.53           |

| Proposed MLI        | 4.59               | 5.18         | 4.71            |

Table 5. Comparison table of %THD for proposed MLI with conventional MLI.

losses. **Table 5** shows the %THD value for conventional CHBMLI and proposed MLI without integrated solar and with an integrated solar system. From **Table 5**, it is clearly understood that the proposed MLI with integrated solar system provides <5% THD value which satisfies IEEE519 harmonic standard.

# 6. Conclusion

Multilevel inverter topologies have been more popular in renewable energy application. The proposed reduced switch multilevel inverter configuration has many advantages such as reduction of switches, driver circuits and the DC source count. Also, it is operated at asymmetric condition so that it requires the minimum count of conducting switches per voltage level generation when compared with conventional MLI topologies. Therefore, the switching losses and conducting losses of this configuration are considerably low. The proposed configuration utilizes unipolar PWM strategies for improving the quality of output voltage. The operation of proposed configuration is tested with MATLAB/SIMULINK simulation, and it is verified in hardware set up using dSpace 1104 real-time

controller. The proposed configuration is tested with photovoltaic panels for proving the ability of it. As a result, the proposed configuration requires lesser component count for generating higher output voltage level with lower %THD, and it is well suitable for the photovoltaic system.

#### Nomenclature

$E_{on}$  and  $E_{off}$

$N_{sw}$

MLI Multilevel inverter ΡV Photovoltaic THD Total harmonic distortion **CHBMLI** Cascaded H-bridge multilevel inverter PD Phase disposition **SPWM** Sinusoidal pulse width modulation **PWM** Pulse width modulation Photovoltaic current  $I_{PV}$ Saturation current  $I_o$ Series resistance of solar cell  $R_s$ Parallel resistance of solar cell  $R_v$ Solar cells connected in series  $N_s$  $N_n$ Solar cells connected in parallel G Irradiation on the device surface Conducting losses  $L_c$ Conducting losses of switch and conduction losses of diode  $L_{c,sw}$  and  $L_{c,d}$ DC Direct current **DCMLI** Diode clamped multilevel inverter **FCMLI** Flying capacitor multilevel inverter I-V Current-voltage P-V Power-voltage FFT Fast Fourier transform PV current  $I_{pv,n}$  $V_t$ Thermal voltage Open circuit voltage  $V_{oc,n}$  $I_{sc,n}$ Short circuit current  $K_V$ Short circuit voltage or temperature co-efficient  $K_I$ Short circuit current or temperature co-efficient  $G_n$ Nominal irradiation Switching losses

Turn on energy loss and turn off energy loss

Number of switch

# **Author details**

Natarajan Prabaharan\*, Subramani Saravanan, Amalorpavaraj Rini Ann Jerin and Kaliannan Palanisamy

\*Address all correspondence to: prabaharan.nataraj@gmail.com

School of Electrical Engineering, VIT University, Vellore, Tamil Nadu, India

### References

- [1] Rodríguez J, Leon JI, Kouro S, Portillo R, Prats MAM. The age of multilevel converters arrives. IEEE Industrial Electronics Magazine. 2008;2(2):28–39

- [2] Rodriguez J, Lai JS, Peng FZ. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Transactions on Industrial Electronics. 2002;49(4):724–738

- [3] Kouro S, Malinowski M, Gopakumar K, Pou J, Franquelo LG, Bin Wu BW, Rodriguez J, Pérez MA, Leon JI. Recent advances and industrial applications of multilevel converters. IEEE Transactions on Industrial Electronics. 2010;57(8):2553–2580

- [4] Rodriguez J, Bernet S, Steimer PK, Lizama IE. A survey on neutral-point-clamped inverters. IEEE Transactions on Industrial Electronics. 2010;57(7):2219–2230

- [5] Samadaei E, Gholamian SA, Sheikholeslami A, Adabi J. An envelope type (E-Type) module: Asymmetric multilevel inverters with reduced components. IEEE Transactions on Industrial Electronics. 2016;63(11):7148–7156

- [6] Hsieh C, Liang T, Chen SM, Tsai S. Design and implementation of a novel multilevel DC-AC inverter. IEEE Transactions on Industry Applications. 2016;**52**(3):2436–2443

- [7] Babaei E, Hosseini SH, Gharehpetian GB, Haque MT, Sabahi M. Reduction of DC voltage sources and switches in asymmetrical multilevel converters using a novel topology. Electric Power Systems Research. 2007;77(8):1073–1085

- [8] Islam M, Mekhilef S, Hasan M. Single phase transformer-less inverter topologies for gridtied photovoltaic system: A review. Renewable & Sustainable Energy Reviews. 2015;45:69–86

- [9] Babaei E. Optimal topologies for cascaded sub-multilevel converters. Journal of Power Electronics. 2010;**10**(3):251–261

- [10] Babaei E, FarhadiKangarlu M. Cross-switched multilevel inverter: An innovative topology. IET Power Electronics. 2013;6(4):642–651

- [11] Babaei E, Kangarlu MF, Sabahi M, Pahlavani MRA. Cascaded multilevel inverter using sub-multilevel cells. Electric Power Systems Research. 2013;96:101–110

- [12] Babaei E. A cascade multilevel converter topology with reduced number of switches. IEEE Transactions on Power Electronics. 2008;23(6):2657–2664

- [13] ShalchiAlishah R, Nazarpour D, Hosseini SH, Sabahi M. Novel multilevel inverter topologies for medium and high-voltage applications with lower values of blocked voltage by switches. IET Power Electronics. 2014;7(12):3062–3071

- [14] Banaei MR, Salary E. New multilevel inverter with reduction of switches and gate driver. Energy Conversion and Management. 2011;**52**:1129–1136

- [15] Trabelsi M, Bayhan S, Ghazi KA, Abu-Rub H, Ben-Brahim L. Finite-control-set model predictive control for grid connected packed-U-cells multilevel inverter. IEEE Transactions on Industrial Electronics. 2016;63(11):7286–7295

- [16] Fuentes CD, Rojas CA, Renaudineau H, Kouro S, Perez MA, Thierry M. Experimental validation of a single DC bus cascaded H-bridge multilevel inverter for multistring photovoltaic systems. IEEE Transactions on Industrial Electronics. 2017; 64(2):930–934

- [17] Karasani RR, Borghate VB, Meshram PM, Suryawanshi HM. Sabyasachi S. A three-phase hybrid cascaded modular multilevel inverter for renewable energy environment. IEEE Transactions on Power Electronics. 2017;32(2):1070–1087

- [18] Sonti V, Jain S, Bhattacharya S. Analysis of the modulation strategy for the minimization of the leakage current in the PV grid-connected cascaded multilevel inverter. IEEE Transactions on Power Electronics. 2017;32(2):1156–1169

- [19] Lee SS, Chu B, Idris NRN, Goh HH, Heng YE. Switched-battery boost-multilevel inverter with GA optimized SHEPWM for standalone application. IEEE Transactions on Industrial Electronics. 2016;63(4):2133–2142

- [20] Nademi H, Das A, Burgos R, Norum LE. A new circuit performance of modular multilevel inverter suitable for photovoltaic conversion plants. IEEE Journal of Emerging and Selected Topics in Power Electron. 2016;4(2):393–404

- [21] Gandomi AA, Saeidabadi S, Hosseini SH, Babaei E, Sabahi M. Transformer-based inverter with reduced number of switches for renewable energy applications. IET Power Electronics. 2015;8(10):1875–1884

- [22] Wang L, Zhang D, Wang Y, Wu B, Athab HS. Power and voltage balance control of a novel three-phase solid state transformer using multilevel cascaded H-bridge inverters for microgrid applications. IEEE Transactions on Power Electronics. 2016;**31**(4):3289–3301

- [23] Panda AK, Suresh Y. Research on cascade multilevel inverter with single DC source by using three-phase transformers. Electric Power Systems Research. 2012;**40**:9–20

- [24] Suresh Y, Panda AK. Investigation on hybrid cascaded multilevel inverter with reduced DC sources. Renewable & Sustainable Energy Reviews. 2013;**26**:49–59

- [25] Veenstra M, Rufer A. Control of a hybrid asymmetric multilevel inverter for competitive medium-voltage industrial drives. IEEE Transactions on Industrial Applications. 2005;41 (2):655–664

- [26] Prabaharan N, Palanisamy K. Analysis and integration of multilevel inverter configuration with boost converters in a photovoltaic system. Energy Conversion and Management. 2016;28(C):327–342

- [27] Prabaharan N, Palanisamy K. Comparative analysis of symmetric and asymmetric reduced switch MLI topologies using unipolar pulse width modulation strategies. IET Power Electronics. 2016;9(15):2808–2823

- [28] Prabaharan N, Palanisamy K. Investigation of single phase reduced switch count asymmetric multilevel inverter using advanced pulse width modulation technique. International Journal of Renewable Energy Research. 2015;5(3):879–890

- [29] Nami A, Zare F, Ghosh A, Blaabjerg F. A hybrid cascade converter topology with series-connected symmetrical and asymmetrical diode-clamped h-bridge cells. IEEE Transactions on Power Electronics. 2011;26(1):51–65

- [30] Prabaharan N, Palanisamy K. A single phase grid connected hybrid multilevel inverter for interfacing photo-voltaic system. Energy Procedia 2016;103:250–255

- [31] Prabaharan N, Palanisamy K. Modeling and analysis of a quasi-linear multilevel inverter for photovoltaic application. Energy Procedia. 2016;**103**:256–261