We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

185,000

200M

Our authors are among the

TOP 1% most cited scientists

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

# Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

# Heteroepitaxy of III–V Zinc Blende Semiconductors on Nanopatterned Substrates

Thomas Riedl and Jörg K.N. Lindner

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/67572

#### Abstract

In the last decade, zinc blende structure III–V semiconductors have been increasingly utilized for the realization of high-performance optoelectronic applications because of their tunable bandgaps, high carrier mobility and the absence of piezoelectric fields. However, the integration of III–V devices on the Si platform commonly used for CMOS electronic circuits still poses a challenge, due to the large densities of mismatch-related defects in heteroepitaxial III–V layers grown on planar Si substrates. A promising method to obtain thin III–V layers of high crystalline quality is the growth on nanopatterned substrates. In this approach, defects can be effectively eliminated by elastic lattice relaxation in three dimensions or confined close to the substrate interface by using aspect-ratio trapping masks. As a result, an etch pit density as low as  $3.3 \times 10^5$  cm<sup>-2</sup> and a flat surface of submicron GaAs layers have been accomplished by growth onto a SiO<sub>2</sub> nanohole film patterned Si(001) substrate, where the threading defects are trapped at the SiO<sub>2</sub> mask sidewalls. An open issue that remains to be resolved is to gain a better understanding of the interplay between mask shape, growth conditions and formation of coalescence defects during mask overgrowth in order to achieve thin device quality III–V layers.

**Keywords:** heteroepitaxy, nanopatterning, crystal defects, defect trapping, compound semiconductors, strain relaxation

# 1. Introduction

III–V compound semiconductors are the materials of choice for making state-of-the-art power electronic and optoelectronic devices, which is due to the outstanding properties of this class of semiconductors. First, they have mostly direct bandgaps covering a broad range between 0.2 eV for InSb [1] and 5.3 eV for zinc blende AlN [2] (at room temperature, respectively).

© 2017 The Author(s). Licensee InTech. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited. Also, bandgaps and lattice parameters can be continuously tailored by forming ternary and quaternary alloys. This allows for continuous tuning of the wavelength of light-emitting or absorbing devices and of the lattice parameter in order to reduce lattice misfit to the substrate or between different layers in the device. By decreasing the size of the semiconductor close to the size of the electron wavelength quantum confinement effects come into play, providing an additional degree of freedom for tailoring the emission or absorption wavelength. Another benefit of the carrier confinement arises from the change in the density of states distribution leading to sub-band formation and increased exciton-binding energies in quantum wells, which enables the realization of high-performance LEDs, laser devices and solar cells. Moreover, GaAs, InAs and InSb have very high electron mobilities in the range between 9400 cm<sup>2</sup>/Vs for GaAs [3] and 78,000 cm<sup>2</sup>/Vs for InSb [4], which make them ideal for applications in high-speed power electronics. A particular advantage of zinc blende semiconductors as opposed to their wurtzite-structure counterparts is that piezoelectric fields occur to a much lesser extent in the former because of their high symmetry. In zinc blende layers grown along the [001] direction piezoelectric effects are completely absent [5].

In view of the compelling properties and the great potential for applications but also the high production cost of III–V semiconductor wafers there is a rising demand for integrating III–V structures into the less expensive and well established Si technology [6]. This is important e.g. for developing high-performance light sources on the Si platform. However, growth of high-quality III–V layers on planar Si substrates is hampered by the considerable mismatch of lattice parameters and thermal expansion coefficients as well as by the polar/non-polar surface incompatibility leading to the formation of defects, i.e. threading dislocations (TDs), stacking faults (SFs), twins and anti-phase boundaries (APBs). Threading defects, which cross the active layers of devices, are known to degrade their performance and lifetime by formation of electronic levels in the bandgap inducing non-radiative carrier recombination [7]. In addition, charge carriers are scattered at the defects, the diffusion of impurities is intensified, and defects reaching the layer surface increase its roughness.

In order to reduce the defect density in heteroepitaxial-mismatched layers on planar substrates different strategies have been pursued, like utilization of graded buffer layers [8], thermal cycle annealing and strained layer superlattices [9, 10]. Unfortunately, these approaches are time-consuming, yield limited defect density reductions or require thick buffer layers to be grown. For example, by application of complex thermal cycle annealing and strained layer superlattice processes in the case of GaAs growth on Si(001) an etch pit density lower than ~1.2 × 10<sup>6</sup> cm<sup>-2</sup> could not be achieved [9–11]. An alternative route of eliminating defects consists of using *nanopatterned* instead of planar substrates for the heteroepitaxial growth. In this way, III–V layers of remarkably high structural and morphological quality with respect to their low thickness have been achieved in the last ten years. Heteroepitaxial growth of c-GaN on nanopatterned 3C-SiC/Si(001) has also extensively been studied [12, 13] but in the following emphasis will be placed on arsenides, phosphides and anti-monides.

The book chapter is organized as follows. Section 2 reviews the different heteroepitaxial approaches for growing zinc blende structure III–V layers on nanopatterned mismatched

substrates. Focus is put on approaches that aim at a reduction of defect densities by applying different defect elimination mechanisms. Also, the resulting structural, morphological and optical quality of the layers is assessed. After that, Section 3 highlights the relevance of such high-quality III–V layers for advanced applications.

## 2. Heteroepitaxial layer growth and quality on nanopatterned surfaces

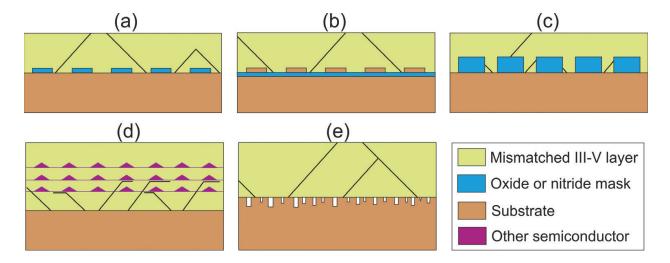

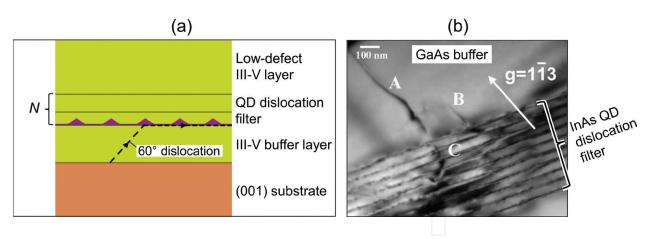

In the following semiconductor, heteroepitaxy strategies are reviewed, which use nanopatterned substrates in order to minimize the density of misfit-related defects in III–V layers. **Figure 1** provides an overview. Most of these heteroepitaxy approaches rely on nanoscale selective growth (Section 2.1.1) on a mask-patterned surface, i.e. selective growth on nanoscale crystalline areas, which are laterally surrounded by an oxide or nitride mask layer (**Figure 1(a–c**)). This growth mode, which also enables selective area growth of nanowires and quantum dots (QDs), can be exploited for the epitaxial lateral overgrowth (Section 2.1.2) and aspect ratio trapping (ART) techniques (Section 2.1.3). Moreover, multiple QD layers on planar, buffer layer coated substrates can be exploited as dislocation filters (**Figure 1(d)**, Section 2.2). Yet another approach uses nanoporous substrate surfaces without any mask, where the local three-dimensional elastic lattice relaxation enhances the layer quality (**Figure 1(e)**, Section 2.3).

#### 2.1. Growth on mask-patterned surfaces

The use of nanopatterned oxide or nitride masks offers a great potential for the heteroepitaxial growth of mismatched semiconductor layers. Low-defect III–V layers have been dem-

**Figure 1.** Overview of heteroepitaxial growth methods on nanopatterned substrates. The graphs show schematic crosssections of the layer systems, respectively. (a–c) Three variants of mask-controlled growth with nucleation on nanoscale substrate areas: (a) thin mask film with nanoopenings, (b) continuous mask film with substrate nanoislands on top, (c) mask nanoopenings with aspect ratio >1 (aspect ratio trapping technique), (d) growth using multiple QD layers as dislocation filters and (e) growth on a mask-free nanoporous substrate. In (a–e) the inclined black lines indicate the propagation of threading crystal defects.

onstrated on substrates covered with (i) a mask layer having nanoscale line or round shaped openings, or with (ii) semiconductor islands or mesas on top of a continuous mask layer. In both variants the nanoscale semiconductor areas on the surface serve as nucleation sites for the III–V growth. Due to lateral growth the overgrown islands eventually coalesce to form continuous III–V layers, bridging the mask areas in between them.

#### 2.1.1. Nanoscale selective growth

Nanoscale selective growth (NSG) describes selective homoepitaxial or heteroepitaxial growth on the unmasked areas of a partially masked substrate surface. It represents a key mechanism in the growth of mismatched layers on mask patterned substrates, first proposed by Luryi and Suhir [14]. In the following two subsections, the conditions required for NSG are analysed theoretically and corresponding experimental observations are described [15].

#### 2.1.1.1. Theoretical description

On an ideal surface, i.e. in absence of nucleation centres such as impurities, defects or surface steps, selective growth can be achieved (i) by surface out-diffusion of the adatoms from the masked to the unmasked areas and/or (ii) by adatom desorption before the cluster formation starts. The surface out-diffusion mechanism works if the lateral dimensions of the masked areas are chosen smaller than the surface migration length of the adatoms, i.e. the average diffusion length before desorption or agglomeration with other atoms. This allows the adatoms to diffuse to the unmasked areas and to suppress crystal nucleation on the masked areas resulting in selective growth in the mask openings [15]. In the case (ii) the surface diffusion length of the adatoms without coming across other adatoms has to be less than a characteristic length describing the average distance between adjacent adatoms [16]. NSG can be described by an equation analogous to that for step-flow growth with a critical cluster size of 1, where arriving atoms diffuse to a step edge:

$$\frac{\partial n}{\partial t} = F - \frac{n}{\tau_{\rm des}} + D \,\nabla^2 \,n \tag{1}$$

Here, *n* denotes the areal density of adatoms on the mask at time *t*, *F* is the flux of atoms arriving on a unit mask area per unit time *t*.  $\tau_{des}$  designates the desorption-limited adatom residence time on the surface, and *D* the surface diffusion constant.

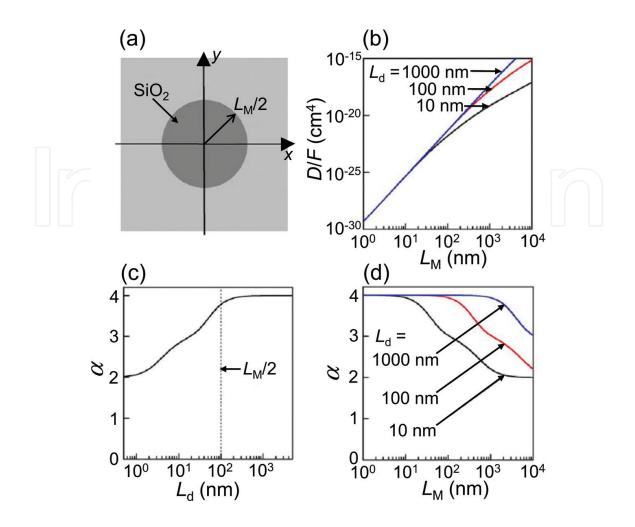

In the vicinity of the substrate-mask boundary a gradient of the surface potential occurs, which provides the driving force for diffusion of adatoms from the mask to the substrate [16, 17]. The potential gradient also prevents the adatoms to diffuse in reverse direction, i.e. from the GaAs surface onto the mask. For a circular SiO<sub>2</sub> mask with diameter  $L_M$  as displayed in **Figure 2** and the boundary condition  $n(L_M/2, t) = 0$ , the steady state is given for [15]:

$$\frac{D}{F} = \frac{\pi L_M^4}{4N} \sum_{m=1}^{\infty} \left[ z_m^2 + \left( \frac{L_M}{2L_d} \right)^2 \right]^{-1} \sim L_M^{\alpha}$$

(2)

For selective growth the total number of Ga adatoms on the SiO<sub>2</sub> mask *N* is small and can be set to 1 without affecting the results for  $\alpha$ .  $z_m$  is the *m*th zero of the zero-order Bessel function,  $L_d$  is the diffusion length of a Ga atom on a planar SiO<sub>2</sub> surface and  $\alpha$  is a

Heteroepitaxy of III–V Zinc Blende Semiconductors on Nanopatterned Substrates 87 http://dx.doi.org/10.5772/67572

**Figure 2.** (a) Schematic of a SiO<sub>2</sub> disc of diameter  $L_M$  deposited on a GaAs surface, (b) calculated ratio D/F versus  $L_M$  for different  $L_d$  according to Eq. (2). (c, d) Diagrams showing the exponent  $\alpha$  as a function of (c)  $L_d$  and (d)  $L_{M'}$  obtained from (b), respectively. In (c)  $L_M$  = 200 nm ( $\alpha$  = 3.8), where the dashed line marks  $L_d = L_M/2$ . (Reproduced from [15], with the permission of AIP Publishing.)

dimensionless exponent [15]. **Figure 2(b)** plots *D/F* as a function of  $L_{\rm M}$  for different  $L_{\rm d}$ , and **Figure 2(c)** and **(d)** display the resulting exponent  $\alpha$  versus  $L_{\rm d}$  and  $L_{\rm M'}$  respectively. With increasing  $L_{\rm M}$  and decreasing  $L_{\rm d} \alpha$  decreases from 4 to 2, owing to desorption. In the limit  $\alpha = 4$  ( $L_{\rm M} \ll L_{\rm d}$ ) suppression of growth on the mask is achieved only by surface out-diffusion, whereas for  $\alpha = 2$  ( $L_{\rm M} \gg L_{\rm d}$ ) selective growth is accomplished solely by desorption. In the latter case the critical flux below which selective growth occurs obeys an exponential scaling law:

$$F_{\rm c} \sim \frac{\nu_0^2}{C} \exp\left[-\frac{2E_{\rm des} - E_{\rm diff}}{kT}\right],\tag{3}$$

where  $E_{des}$  denotes the activation energy for adatom desorption,  $E_{diff}$  is the activation energy for adatom surface diffusion, *T* is the absolute temperature, *k* is the Boltzmann constant and  $v_0$  is a desorption rate constant. Commonly,  $2E_{des} > E_{diff}$ , meaning that the critical flux below which nucleation on the SiO<sub>2</sub> mask can be suppressed increases with rising temperature.

#### 2.1.1.2. Experimental observations

Experimentally, two main types of nanopatterned substrates have been utilized for oxide mask-based NSG/nanoheteroepitaxial growth: (i) substrates covered with a mask film having round or line shaped openings and (ii) substrates capped with a continuous mask layer with nanoscale semiconductor islands or horizontal wires on top. On the one hand, the fabrication of type (i) substrates is more facile. On the other hand, type (ii) offers the advantage of compliant nanoscale substrate islands, which can accommodate a portion of the misfit strain.

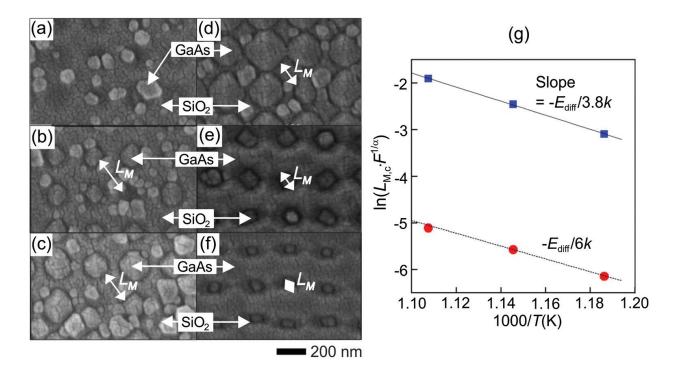

Approach (i) has been extensively studied by Lee et al. [16, 17] and Lee and Brueck [15]. They used SiO, films deposited on GaAs(001) substrate by electron beam evaporation. For the patterning of the SiO<sub>2</sub> films interference lithography followed by dry etching [15] was deployed, resulting in arrays of approximately circular mask openings with pattern periods between 260 and 350 nm. By varying the dry etching time different opening sizes were realized. For the longer etching times the openings coalesced leaving isolated SiO<sub>2</sub> islands on the GaAs substrate. Scanning electron microscopy (SEM) images of the surface after molecular beam epitaxy (MBE) growth at 570°C using a Ga flux of  $F = 0.33 \times 10^{14}$  atoms/(cm<sup>2</sup>s) show that the growth becomes increasingly selective [15], when reducing the mask dimension  $L_{\rm M}$  from infinity to 70 nm (Figure 3(a–f)). For these conditions the critical mask dimension  $L_{M_c}$  below which growth on the mask is completely inhibited amounts to ~120 nm. The experimental  $L_{Mc}$  results for different growth temperatures and Ga fluxes confirm that the temperature has the strongest influence on  $L_{\rm Mc}$ . Figure 3(g) depicts a plot of  $\ln(L_{\rm Mc} \cdot F^{1/\alpha})$  over 1/*T* for  $\alpha$  = 3.8 and  $\alpha$  = 6, where  $\alpha$  = 3.8 is the exponent, which the calculations (Eq. (2), **Figure 2**) predict for the experimental mask dimensions, and  $\alpha \approx 6$  has been found by means of growth kinetic MBE simulations [18] for a critical cluster size of 1 by using different boundary conditions than in the study of Lee et al. [15]. From the slope the activation energy  $E_{\text{diff}}$  for surface diffusion of a Ga adatom on a SiO<sub>2</sub> surface was determined in the range between ~4.9 eV for  $\alpha$  = 3.8 and ~6.8 eV for  $\alpha$  = 6, which significantly exceeds the activation energy for surface diffusion of a Ga adatom on a GaAs surface of ~1 eV [19]. The short diffusion lengths of Ga adatoms on  $SiO_2$  related to the large  $E_{diff}$  comply with the small critical mask dimensions observed in the experiments.

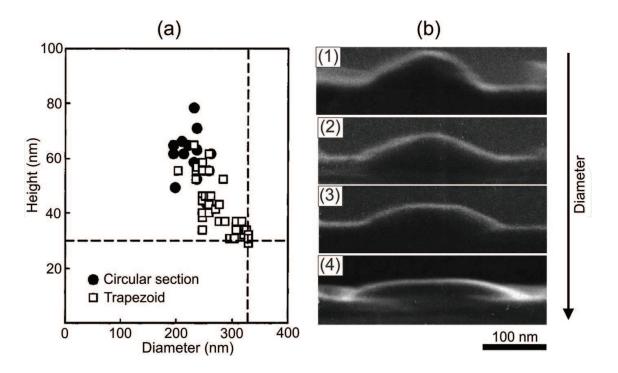

Regarding the morphology of the GaAs islands selectively grown in circular mask openings it has been found that the height as well as the shape of the islands varies with the diameter of the openings [17]. With decreasing opening diameter the island height increases, because of the larger mask area and related increased number of Ga atoms diffusing from the mask to the GaAs surface (**Figure 4(a)**). Side-view SEM images show that the crosssections of the GaAs islands change from a round profile for small opening diameters to trapezoidal shapes for larger diameters (**Figure 4(b)**). In all cases, the total GaAs volume deposited in the mask openings is considerably smaller than the estimated volume of a continuous GaAs layer on a mask-free GaAs surface using the same deposition time, indicating that not all Ga adatoms impinging on the SiO<sub>2</sub> areas migrate to the mask openings. According to the estimated volume of GaAs islands deposited at 630°C on a continuous SiO<sub>2</sub> film a sticking coefficient of Ga atoms on SiO<sub>2</sub> of ~0.13 was estimated [17]. A more recent study found a value of ~0.007 at 632°C and confirmed the expected exponential dependence on the inverse absolute temperature [20].

**Figure 3.** Top-view SEM images showing GaAs grown by MBE at 570°C on GaAs(001) covered with SiO<sub>2</sub> masks having different lateral dimensions  $L_{M^*}$  (a) Continuous SiO<sub>2</sub> film, i.e. infinite  $L_{M'}$  (b)  $L_M \approx 270$  nm, (c)  $L_M \approx 220$  nm, (d)  $L_M \approx 180$  nm, (e)  $L_M \approx 120$  nm, and (f)  $L_M \approx 70$  nm. The periodic features in (b) through (d) are SiO<sub>2</sub> mask openings, while those in (e) and (f) are SiO<sub>2</sub> islands. (g) A plot of  $\ln(L_{M,c} \cdot F^{1/\alpha})$  over 1/*T* for NSG of GaAs on SiO<sub>2</sub>-nanopatterned GaAs(001) and two different exponent values  $\alpha = 3.8$  and  $\alpha = 6$ . The values of the critical mask dimension  $L_{M,c}$ , the flux *F* and the growth temperature *T* are deduced from MBE growth experiments conducted at three different temperatures. Straight lines are Arrhenius fits. (Reproduced from [15], with the permission of AIP Publishing.)

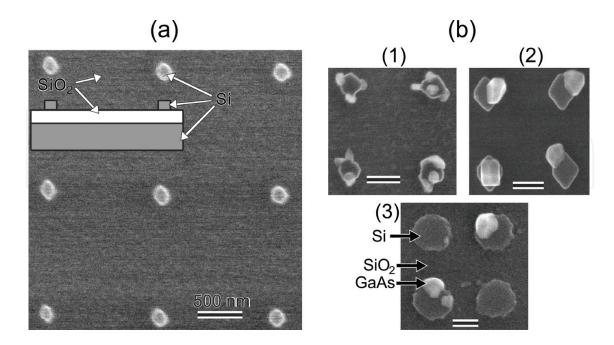

In the second approach, nanoscale Si islands on a continuous  $SiO_2$  film mask serve as nucleation sites for the heteroepitaxial growth. Such patterned surfaces can be obtained by patterning of silicon-on-insulator (SOI) wafers, i.e. by removing parts of the Si top layer. Zubia et al. studied the metalorganic vapour phase epitaxy (MOVPE) growth of GaAs on square arrays of SOI islands with diameters between 100 and 280 nm, and a pitch of 500 nm (**Figure 5(a)**) [21, 22].

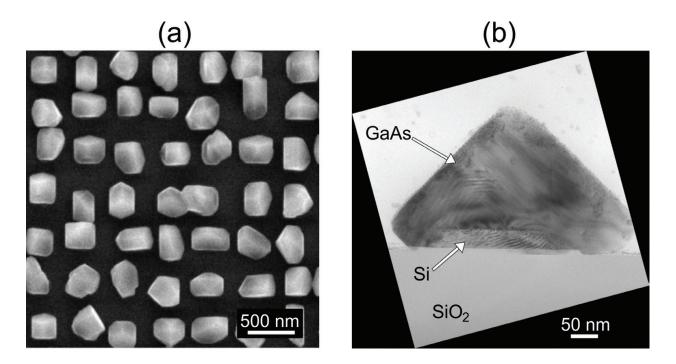

During the initial growth stage crystalline GaAs nuclei form on the Si islands, where the number and size of the nuclei strongly depend on the temperature-controlled surface diffusion (**Figure 5(b**)) [21]. For low temperatures multiple GaAs crystals were observed on each Si island, while only a fraction of the Si islands was covered with GaAs for high temperatures. At an optimum temperature of 605°C each Si island has one GaAs crystal on top. The size, shape and structural quality of these GaAs nuclei play an important role for the subsequent lateral growth (performed at optimum temperature). For an initial growth temperature below 605°C various types of defects such as twins appear in the overgrown GaAs, while for 605°C (**Figure 6**) only stacking faults on the {111} planes have been found by transmission electron microscopy (TEM) diffraction [21]. In contrast, threading dislocations represent the dominant defect in GaAs growth on planar Si. The spacings of the Moirée fringes visible in TEM images as well as the diffraction spot spacings consistently indicate a residual lattice strain of 0.4–0.7% in the GaAs [21], i.e. given the GaAs-Si lattice misfit of ~4% the nanoheteroepitaxial GaAs is predominantly relaxed. However, it has not been clarified whether the relaxation originates from misfit dislocations (MDs) at the Si/GaAs heterointerface, from elastic relaxation or from both.

**Figure 4.** (a) Diagram plotting the height of GaAs islands grown by MBE selectively in  $SiO_2$  mask openings as a function of opening diameter. The vertical and horizontal dotted lines represent the pattern period and the thickness of a GaAs layer on a mask-free GaAs substrate using the same growth parameters, respectively. (b) Side-view SEM images showing the diameter-dependent transition from round to trapezoidal cross-section profiles of the GaAs islands selectively grown in the mask openings. (Reproduced from [17], with the permission of AIP Publishing.)

**Figure 5.** (a) Plan view SEM image of the patterned silicon-on-insulator (001) substrate with Si nanoislands on top. The inset shows a schematic cross-section of the structure. (b) Plan view SEM images of GaAs crystallites on silicon islands for different growth temperatures: (1) 519°C, (2) 605°C and (3) 734°C. The scale bars in (b) are 200 nm [22].)

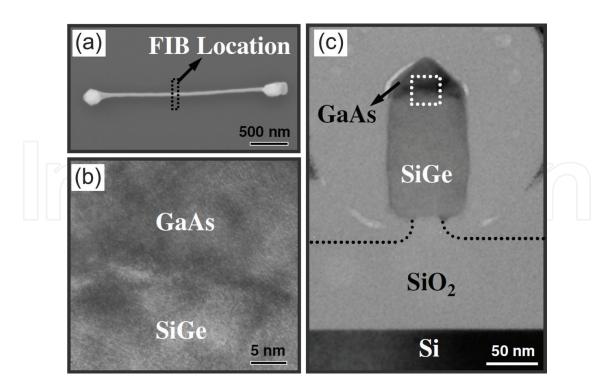

Apart from nanoscale semiconductor islands also lateral nanowires on a continuous mask film can be used for selective three-dimensional growth of III–V semiconductors. On Si(001) substrate Chin et al. fabricated Si<sub>0.35</sub>Ge<sub>0.65</sub>-on-SiO<sub>2</sub> structures by deposition of a Si<sub>0.85</sub>Ge<sub>0.15</sub> layer onto a SOI substrate and subsequent two-step Ge condensation process [23]. After photoli-thography and dry etching lateral Si<sub>0.35</sub>Ge<sub>0.65</sub> nanowires on SiO<sub>2</sub> were obtained, which served for the study of selective migration enhanced epitaxy (MEE) growth of GaAs onto the nanowires (**Figure 7**). Owing to the pulsed Ga and As fluxes and intermittent annealing phases in MEE, selective growth is achieved even in the case of masks patterned on the micrometre scale. Cross-sectional TEM images reveal that GaAs grows pseudomorphically and defect-free in the form of facetted planar nanowires on top of ~75 nm wide Si<sub>0.35</sub>Ge<sub>0.65</sub> nanowires (**Figure 7(c)**). Defects that relieve the strains due to the ~1.5% lattice misfit are absent because both Si<sub>0.35</sub>Ge<sub>0.65</sub> and GaAs lattice regions relax elastically in the lateral and vertical directions.

#### 2.1.2. Lateral overgrowth of oxide mask and layer coalescence

By means of continued deposition on a mask nanopatterned substrate the selectively formed heteroepitaxial crystals grow and finally coalesce to form a continuous layer. In 1991 Ismail et al. were probably the first who—unintentionally—performed heteroepitaxial overgrowth of a nanometre thin holey SiO<sub>x</sub> film [24]. GaAs was deposited by two-step MOVPE growth onto a sawtooth-patterned vicinal Si(001) substrate defined by {111} surface facets. The two-step growth was followed by either an ex situ rapid thermal annealing at 900°C or a thermal cycle growth. In TEM analyses, it was found that a ~1 nm thin SiO<sub>x</sub> film covered the Si/GaAs interface. The GaAs layer exhibited an exceptionally low etch pit density of <10<sup>4</sup> cm<sup>-2</sup> at 0.8 µm distance from the heterointerface, and a dislocation density evaluated from plan-view TEM of

**Figure 6.** Plan view SEM (a) and cross-sectional TEM image (b) of 100 nm GaAs MOVPE growth on nanopatterned silicon-on-insulator (001) substrate. The GaAs nucleation was performed at 605°C [22].)

**Figure 7.** (a) Top-view SEM image depicting a  $Si_{0.33}Ge_{0.65}$  nanowire with a GaAs layer grown on top, (b, c) cross-sectional TEM images confirming pseudomorphic, defect-free GaAs on the  $Si_{0.35}Ge_{0.65}$ . Image (b) covers the region defined by the white dotted rectangle in (c). The TEM specimen was prepared by focussed ion beam at the position marked by an arrow in (a). (Reproduced from [23], with the permission of AIP Publishing.)

$<10^{5}$  cm<sup>-2</sup> for 1 µm layer thickness. Based on the limited TEM data, two different mechanisms were considered to account for the occurrence of such a low-defect density: firstly, the orientation of the Si substrate could be transferred to the GaAs layer via Si-GaAs contacts in small pinholes in the interfacial oxide, where MDs formed. Because of the small area fraction of the pinholes, the overall MD density was strongly reduced. The also observed twins and SFs are likely to originate from the roughness of the oxide layer [25]. Secondly, the obtained GaAs layer could have resulted from a type of graphoepitaxy, where the GaAs 'perceives' only the symmetry and the inclination of the {111} facets and not the exact positions of the Si atoms. As the SiO<sub>x</sub> film separated the GaAs and Si crystals, relaxed dislocation-free GaAs formed directly above the SiO<sub>x</sub> during the final annealing step.

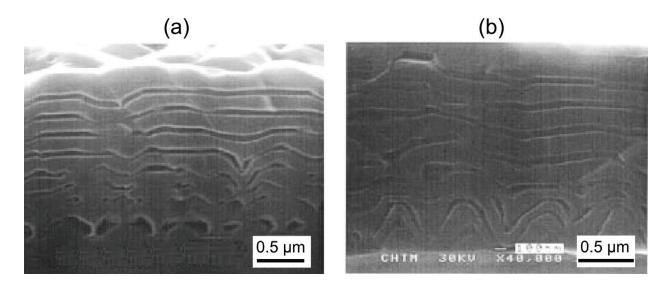

Following a theoretical study on the concept of nanoheteroepitaxy by Zubia and Hersee [26], Hersee et al. reported that the faceting of the forming heteroepitaxial NSG crystals plays a decisive role for the island coalescence and thus for the surface morphology of the coalesced layer [27]. Like in the earlier work of Zubia et al. [21] heterogeneous faceting was observed, which leads to locally different growth rates. To analyse explicitly the layer coalescence behaviour, GaAs and  $Al_{0.4}Ga_{0.6}As$  marker layers were grown by MOVPE onto a GaAs(001) substrate nanopatterned with a holey SiO<sub>2</sub> film [27]. After coalescence different growth habits of the layer surface were observed along two orthogonal cleaving directions by using cross-section SEM [27] (**Figure 8**): in one direction a rapid surface planarization occurred, while the growth remained conformal to the substrate geometry in the orthogonal

direction. This can provoke again surface roughening in the former direction, which slowly decays with increasing layer thickness. However, still significant large-scale variations of the layer thickness in the order of 100 nm were present even for layer thicknesses in excess of 1  $\mu$ m.

More recently, the growth of coalesced heteroepitaxial III–V layers on highly mismatched substrates patterned with nanoporous or nanohole oxide masks was investigated in the cases of GaSb on GaAs(001) (misfit ~7.8%) and GaSb on Si(001) (misfit ~12%).

Jha et al. deployed a SiO<sub>2</sub> nanohole mask (hole diameter ~20 nm) fabricated by blockcopolymer lithography and reactive ion etching for MOVPE heteroepitaxy of GaSb on GaAs(001) and reported an improved quality of the GaSb layers [28]. For a layer thickness of 200 nm the width of the (004) X-ray rocking curve decreased to ~40% of that of GaSb grown on non-patterned GaAs. Moreover, the GaSb layer on the nanopatterned GaAs exhibited a strongly reduced surface roughness as measured by atomic force microscopy (AFM), and the absence of threading dislocations as indicated by cross-sectional TEM. However, twins on the {111} planes were observed, which seem to nucleate on the SiO<sub>2</sub> mask.

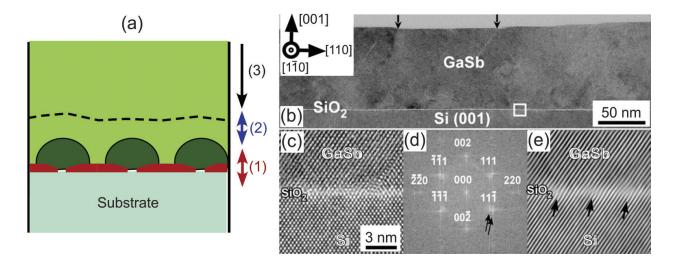

Nanoheteroepitaxial growth with reduced surface roughness and defect density was demonstrated by Nakamura et al. for even larger misfits, i.e. for the GaSb/Si system [29]. They used ultrathin SiO<sub>2</sub> films (thickness ~0.3 nm) with openings of a high areal density of 10<sup>9</sup> to 10<sup>12</sup> cm<sup>-2</sup> as masks on the Si(001) substrate. The growth was performed in three stages by means of MBE (**Figure 9(a)**): In the first stage elastically strain-relaxed GaSb nanodots formed in the SiO<sub>2</sub> openings, followed by nanodot coalescence in the second stage. During the third stage, which was conducted at a higher temperature than stages 1 and 2, the final layer with a flattened surface was obtained. For optimum growth temperatures a root mean square surface roughness of ~7 nm was achieved for a total layer thickness of ~90 nm. Crosssectional HRTEM images indicated a reduced threading dislocation density of ~10<sup>8</sup>–10<sup>9</sup> cm<sup>-2</sup>

**Figure 8.** Cross-section SEM images of a coalesced GaAs layer grown on oxide nanopatterned GaAs(001) substrate along two orthogonal cleaving directions (a, b). The darker layers are intentionally grown Al<sub>0.4</sub>Ga<sub>0.6</sub> As layers serving as thickness markers. (Copyright 2002 IEEE. Reprinted, with permission, from [27].)

as compared to  $10^9$  cm<sup>-2</sup> for a ~1 µm thick GaSb layer grown by using an AlSb initiation layer (**Figure 9(b)**). According to Fourier transformation analysis of HRTEM images the GaSb lattice was almost completely relaxed (**Figure 9(c)** and **(d)**). As, except for the openings, GaSb and Si were separated by the ultrathin SiO<sub>2</sub> layer, the misfit was not accommodated by MDs. Rather, the GaSb lattice planes above the SiO<sub>2</sub> exhibited close-to-equilibrium spacings, i.e. ~12% wider spacings than the corresponding Si planes beneath the oxide (**Figure 9(e)**), which can be attributed to the elastic relaxation in the nanodots during the growth. The direct Si/GaSb contacts in the openings, but also the very thin oxide layer enable a transfer of the epitaxial relationship.

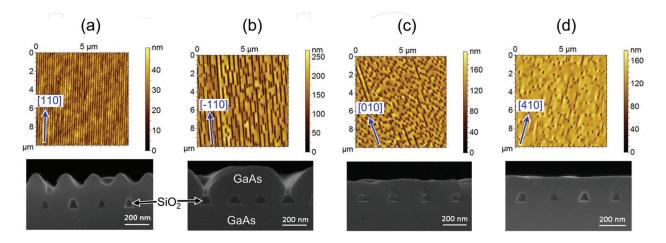

Heteroepitaxial growth and continuous layer formation has also been studied by using gratingshape nanopatterned oxide masks. He et al. [30] applied a three-stage MOVPE growth scheme to obtain a smooth GaAs layer surface on a Si(001) substrate: the first stage served for selective deposition of GaAs in the trenches, while in the second and third stages coalescence and planarization of the GaAs layer were achieved. Repetition of the experiment for different trench orientations showed that this has a strong impact on the coalescence and consequently on the surface roughness of the layer. Minimum surface roughness was observed for a trench orientation parallel to [410], i.e. ~31° inclined to the [110] direction, due to maximum and uniform lateral growth rate. **Figure 10** compares the GaAs layer morphology for different trench orientations on the basis of AFM and cross-sectional SEM images.

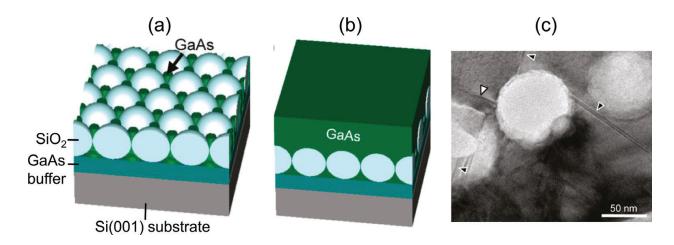

Another approach compassing nanoscale selective growth and filtering of defects relies on MBE growth through the openings of a silica colloidal monolayer [31]. First, a GaAs buffer layer is grown on a planar Si(001) substrate, partially relieving the misfit by formation of extended defects. The subsequently deposited silica sphere monolayer enables selective growth of GaAs in the monolayer openings on the GaAs buffer surface (**Figure 11**). Due to the conical shape of the openings, propagating defects are largely stopped at the silica surfaces.

**Figure 9.** (a) Schematic of the three-step MBE growth procedure, (b) cross-sectional HRTEM image of a GaSb layer on Si(001) substrate obtained by the procedure of (a), (c) Detail of (b) showing the marked square area in (b), (d) Fourier transform of (c), (e) inverse Fourier transform using the  $(11 \overline{1})$  and  $(\overline{1} \overline{1} 1)$  lattice planes. (Copyright IOP Publishing. Reproduced with permission from [29]. All rights reserved.)

When the growing GaAs surface has passed half the height of the spheres elastic relaxation in the lateral directions contributes to reduce the misfit strains.

#### 2.1.3. Aspect ratio-trapping techniques

Although three-dimensional elastic relaxation of the lattice relieves the misfit strains during lateral overgrowth of thin masks, defects at the heterointerface may still form threading segments, which extend far into the layer. In order to stop the propagation of such defects ART techniques have been developed, where the growth areas are situated at the bottom of cylindrical or trench shaped mask openings whose height exceeds their lateral width. Therefore, defects that propagate in the layer on planes inclined to the substrate surface, such as {111} slip planes in the case of a {001} substrate, get trapped at the intersections of the slip planes with the mask walls and are hence hindered to further spread into the layer. Essentially, the lattice undergoes a plastic relaxation where the defects are confined to a region close to the heterointerface and mask sidewall regions. Owing to the efficient plastic relaxation and considerable mask height the layer is nearly completely relaxed when reaching the mask top so that elastic relaxation during mask overgrowth can be neglected.

#### 2.1.3.1. Growth on surfaces patterned with a trench mask

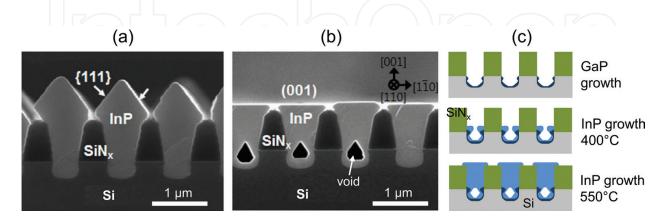

Among the ART techniques those deploying  $SiO_2$  or  $SiN_x$  masks with trench shaped openings along [110] or [110] have been most extensively studied. The trench masks can be fabricated (i) by oxidation of the Si substrate surface, lithography and reactive ion etching, or alternatively (ii) by using processes based on the established shallow trench isolation technology [32]. In particular, selective-area MOVPE growth of InP and GaAs on trench mask patterned Si(001) substrate has attracted great interest [25, 33–43]. Although the detailed defect reduction mechanism depends on the trench dimensions, on the shape of the trench bottom as well as on the heteroepitaxial growth sequence and conditions, the common characteristic

**Figure 10.** AFM images (top row) and cross-sectional SEM images (bottom row) of GaAs layers after the second MOVPE growth stage on SiO<sub>2</sub> stripe patterned Si(001), with stripe orientations: (a) [110], (b) [ $\overline{1}$ 10], (c) [010] and (d) [410]. (Reproduced from [30], with the permission of AIP Publishing.)

**Figure 11.** (a, b) Schematics illustrating the growth of a GaAs layer onto a SiO<sub>2</sub> nanosphere layer covered Si(001)/GaAs buffer template, (c) cross-section TEM image corresponding to (b). The black arrowheads and the white arrowhead point to {111} stacking faults and to a defect off from {111}, respectively. (Reprinted (adapted) with permission from [31]. Copyright 2011 American Chemical Society.)

of trench-based ART techniques consists in the stopping of propagating misfit defects, i.e. dislocations, stacking faults and twins, at the trench sidewalls. This applies to defects on {111} planes parallel to the trench direction. However, threading defects running on {111} planes inclined to the trenches are not trapped and can cross the layer (**Figure 12**). XRD  $\omega$ -2 $\theta$  scans of the (004) reflection demonstrated that the selectively grown InP and GaAs regions are almost fully relaxed [36, 40]. Obviously, the aspect ratio of the trenches (height divided by the width) determines the fraction of threading defects that are trapped by the sidewalls. For aspect ratios larger than 2 misfit defects are confined to the lower part of the trenches, whereas the upper part has a high crystal quality with an etch pit density close to zero [43].

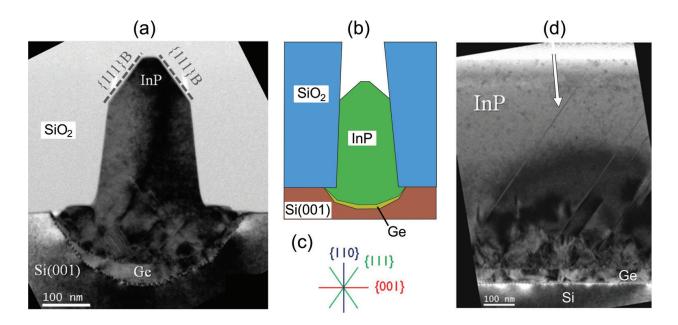

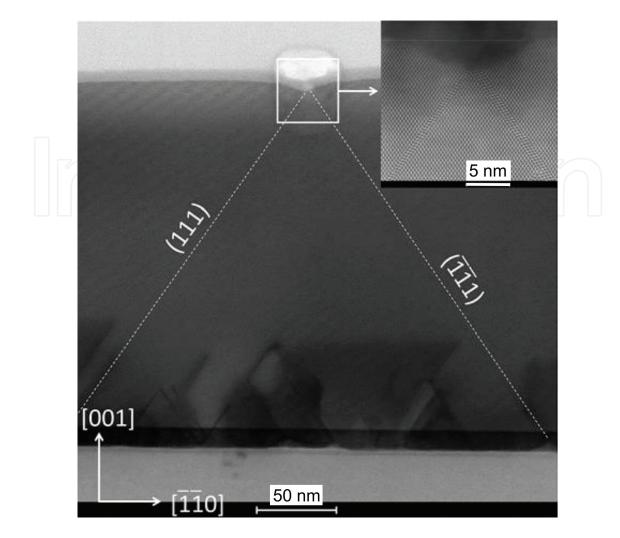

One of the key factors for the formation and trapping efficiency of defects is the shape of the trench bottom. Orzali et al. found that in the case of a recess in the Si substrate defined by a Si(001) bottom surface and Si{111} facets in the vicinity of the sidewalls MOVPE GaAs nucleated preferentially on the {111} facets, thus forming a central void after growth front coalescence [25]. SFs and TDs originating from the trench bottom annihilated at the oxide sidewalls, while only few twin lamellae crossed the layer and reached the surface. Merckling et al., who used a Ge buffer layer in a 'round' Si recess defined by {111}, {112} and (001) facets, evidenced a MD network at the Si/Ge interface (Figure 12(a)). Threading defects on the trench parallel {111} planes are stopped by the SiO<sub>2</sub> sidewalls (Figure 12(a)), whereas some defects on the inclined {111} planes reach the layer surface (Figure 12(d)). A {111} V grooved trench bottom, which can be conveniently fabricated by anisotropic wet etching of the Si substrate, permits a further reduction of the defect density in the III-V layer, for several reasons: firstly, the {111} surface, especially when covered with an As monolayer, energetically facilitates the nucleation of III-V layers [25]. Secondly, single steps on Si{111} surfaces do not induce APB formation [44]. Thirdly, the incorporation and arrangement of MDs in the {111} heterointerface is alleviated, because dislocations can glide on the {111} planes. In the case of MOVPE GaAs deposited in such trenches propagating SFs and TDs are confined to the lower part of the trench, leaving the upper part defect-free with very few twins [25].

Heteroepitaxy of III–V Zinc Blende Semiconductors on Nanopatterned Substrates 97 http://dx.doi.org/10.5772/67572

**Figure 12.** (a, d) Cross-section TEM images of InP/Ge/Si(001) heterostructures (Ge: buffer layer) in 150 nm wide in SiO<sub>2</sub> trenches with viewing direction (a) parallel and (d) perpendicular to the trenches, (b) schematic of the structure, dashed lines indicate threading defects, (c) orientation of lattice planes in (a–c). In (a) the vertical surfaces of the SiO<sub>2</sub> mask are invisible. In (d) the white arrow marks a twin lamella crossing the entire layer. (Reproduced from [36], with the permission of AIP Publishing.)

As shown by XRD pole figure analysis for the InP/Si(001) system the defects are distributed anisotropically on the {111} planes, i.e. more defects populate the ( $\bar{1}11$ ) and ( $1\bar{1}1$ ) planes parallel to the trench bottom faces (for trenches along [110]) than the inclined ( $11\bar{1}$ ) and (111) planes [37]. This finding agrees with TEM analyses, which prove the presence of a dense nanotwin network within 10 nm distance from the trench-parallel Si/InP{111} interfaces, effecting the lattice relaxation. On the other inclined {111} planes stacking faults and twins propagate, which extend from the Si/InP interface towards the layer top surface, where they could limit the performance of devices. Regarding the determination of defect densities of heteroepitaxial nanostructures the width of XRD rocking curves provides qualitative data useful for the comparison of samples having the same layer thickness, as the X-ray penetration depth is in the  $\mu$ m range. For the quantification of defect densities plan-view TEM of larger areas represents the most reliable technique, which yields a density of layer-crossing twin lamellae in the 10<sup>8</sup>–10<sup>9</sup> cm<sup>-2</sup> range for GaAs fins grown in {111} V grooved trenches on Si(001) [25].

Furthermore, it has been found that the surface morphology of InP layers deposited selectively in trenches critically depends on the MOVPE growth conditions, especially on temperature and pressure [36, 38]. These parameters determine the precursor/adatom diffusivity and the heat transfer from the substrate to its surroundings, thus the growth rates of different facets. Before starting layer growth, a high temperature annealing step in the H<sub>2</sub> carrier gas is helpful to remove surface oxide layers and to promote the formation of double steps in the case of a Si(001) surface, which prevents the development of APBs [45]. Concerning the main growth step similar, but slightly different layer morphologies have been reported by different groups, depending on the structure of the patterned samples and the growth setup. By using phosphine as group-V precursor, a SiN<sub>x</sub> trench mask with rounded rectangular recess in the Si(001) substrate and GaP and InP low-temperature buffer layers Lee et al. obtained wedge-shaped InP ridges bounded by {111} facets for a high growth temperature of 650°C (**Figure 13(a**)), whereas an atomically smooth InP(001) top surface resulted for 550°C (**Figure 13(b**)) [38]. In the latter case, GaP islands appeared on the Si sidewalls and in the course of continued InP deposition the lateral growth led to coalescence of opposing sidewall deposits before the recess was fully filled (**Figure 13(c**)). Consequently, a void together with a (001) growth surface was formed. Merckling et al. in contrast deployed a SiO<sub>2</sub> trench mask with shallow curved recess in the Si(001) substrate, a Ge buffer layer with As termination for improved InP wetting, and used a two-stage InP deposition and tert-butylarsine and tertbutylphosphine as group-V precursors [36]. These authors reported highest uniformity of the ridge-shaped crystals bounded by {111} planes for a growth temperature of 550°C. At higher temperatures large three-dimensional islands protruding from the trenches were observed while at lower temperatures non-uniform faceting occurred due to a large density of defects.

Clear evidence for the correlation between crystal defects and surface morphology has been established Orzali et al. for GaAs grown by MOVPE on SiO<sub>2</sub> trench-patterned Si(001) [25]. Analysis of high-resolution STEM images reveals that single twins intersecting the surface give rise to steps, whereas twins that intersect beneath the surface produce surface pits (**Figure 14**).

In order to keep the defect density low, two distinct types of buffer layers are frequently used in combination with the trenches. On the one hand, buffer layers of a different material with a lattice parameter between those of the substrate and of the layer deposited on the trench bottom reduce the effective misfit. For the InP/Si system (i) Ge with a Ge/InP misfit of ~4% [33, 36] (**Figure 12**) and (ii) GaP avoiding the polarity mismatch at the InP/GaP interface [38] (**Figure 13**) have been used as buffer materials. On the other hand, buffer layers of the layer material grown at low temperature help to achieve a relatively smooth layer surface, since at low temperature the reduced Ga adatom diffusivity promotes the formation of a large density of small nucleation islands, which rapidly coalesce. Low temperature buffer layers contain a lot of defects leading to a relief of misfit strains and to an improved crystal quality in the following homoepitaxial layer grown at higher temperatures.

**Figure 13.** Cross-sectional SEM images of InP layer on  $SiN_x$  trench patterned Si(001) for a growth temperature of (a) 650°C and (b) 550°C. (c) Schematic growth evolution for (b). (Reprinted from [38], Copyright 2015, with permission from Elsevier.)

**Figure 14.** Bright-field STEM image of a GaAs layer in a  $SiO_2$  trench on Si(001) depicting a shallow surface pit with twin lamellae intersecting underneath. The viewing direction is perpendicular to the trench direction. Inset: High magnification high-angle annular dark field STEM image of the pit. (Reproduced from [25], with the permission of AIP Publishing.)

After prolonged growth on trench mask patterned substrates the III–V layer grows above the mask and coalesces to form a continuous layer, where the coalescence often induces the development of further defects. In the case of GaAs MOVPE growth over a SiO<sub>2</sub> trench mask Li et al. observed {111} twins and stacking faults initiating at the SiO<sub>2</sub> top surface [46]. By using optimized MOVPE growth parameters for the coalescence stage, i.e. a slightly lower temperature and a higher V/III ratio as compared to the growth in the trenches the density of these defects was reduced. In this way, Li et al. obtained a high-quality GaAs layer on patterned Si(001), however with considerable large-scale thickness variations.

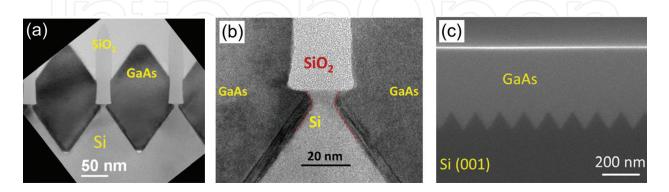

Very recently, it has been demonstrated that GaAs nanoridge arrays grown by the ART technique on exactly oriented Si(001) substrate can be used after removal of the SiO<sub>2</sub> mask as a GaAs-on-Si compliant substrate for a coalescence growth step in order to obtain APB-free, low-defect GaAs layers with flat (001) surfaces [47]. In the SiO<sub>2</sub> mask trenches V-grooved {111}

bottom faces were generated by KOH etching (**Figure 15**). The SiO<sub>2</sub> walls were underetched, and beneath the SiO<sub>2</sub> walls a curved Si surface formed, which undertakes the task of defect trapping instead of the SiO<sub>2</sub> walls. Remarkably, during the coalescence growth step no defects originated from the top of the Si ridges in between neighbouring V grooves, as seen in TEM images (**Figure 15**). Furthermore, the TEM analysis shows that the misfit was accommodated by a large density of SFs within the first few nanometres from the Si/GaAs interface. This method has the advantages that no new defects appear in the coalesced layer in the course of oxide overgrowth and that the resulting layer surface has a low root-mean-square roughness of 1.9 nm measured in a  $5 \times 5 \ \mu\text{m}^2$  scan area for a layer thickness of only ~300 nm.

#### 2.1.3.2. *Growth on surfaces patterned with a cylinder hole mask*

In contrast to trench masks cylindrical mask openings allow to trap misfit defects running on all lattice planes that are inclined against the substrate normal. Despite this benefit, ART with cylinder hole masks has been investigated only by few research groups [48–50]. Hsu et al. [48] reported the MOVPE growth of smooth continuous 900 nm thick GaAs layers of low defect density on Si(001) substrate patterned with a round nanohole SiO<sub>2</sub> mask having a hole diameter of 55 nm and aspect ratio of 4.7. Like in the case of ART trenches, threading misfit defects were confined to the lower part of the holes, giving monocrystalline, relaxed GaAs in the upper part and a very low etch pit density of  $3.3 \times 10^5$  cm<sup>-2</sup> of the coalesced continuous GaAs layer. Application of a two-stage growth scheme (nucleation layer at low temperature, main growth at higher temperature) allowed to avoid thermal tensile strains in GaAs arising from the thermal expansion mismatch between Si and GaAs, as observed in GaAs layers on planar Si substrates by a redshift of the photoluminescence bandgap emission energy. However, the surface morphology of the coalesced GaAs layer and its defect structure above the SiO<sub>2</sub> holes has not been addressed in the work of Hsu et al. [48].

Chang et al., who studied the selective MBE growth of GaAs on  $SiO_2$  nanohole patterned Si(001) found that the top surface of the GaAs nanostubs was not planar but bounded by inclined facets [50]. These authors stated that SFs starting near the Si/GaAs interface originated from disorders in the stacking sequence during merging of GaAs nuclei, owing to

**Figure 15.** (a, b) Cross-section TEM images of GaAs nanoridges grown by the ART technique on Si(001). The zoomed-in TEM image (b) reveals SF trapping by the curved Si undercuts. (c) Cross-section SEM image of a coalesced GaAs layer obtained from the nanoridges shown in (a, b) by overgrowth after  $SiO_2$  mask removal. (Reproduced from [47], with the permission of AIP Publishing.)

different Si surface planes generated by the reactive ion etching of the holes. In contrast, SFs originating at the  $SiO_2$  sidewalls formed due to local stresses in the GaAs induced by  $SiO_2$  surface roughness.

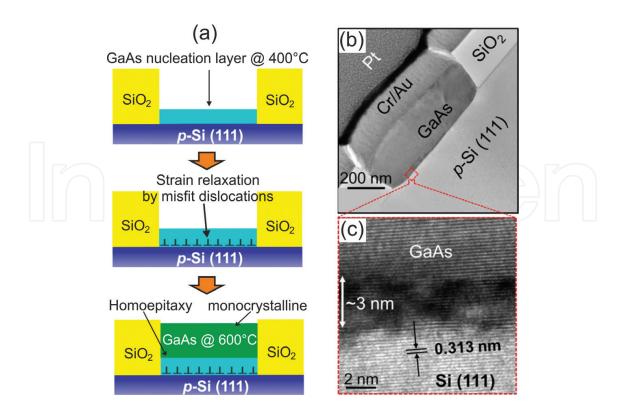

Although Si(111) does not constitute the main substrate in complementary metal oxide semiconductor technology, a method for the growth of small GaAs layer volumes on Si(111) having structural and morphological characteristics highly attractive for applications has been developed: Chu et al. [49] deployed a two-stage MBE growth to obtain monocrystalline GaAs with atomically smooth surface and low defect density in the openings of a SiO<sub>2</sub> hole mask on Si(111). The growth mechanism and thus the properties of the resulting layer can be understood as follows (**Figure 16(a)**): During the first low-temperature growth stage numerous small GaAs islands form by homogeneous nucleation, which then coalesce. During the temperature ramping from the lower to the higher temperature used in the second growth stage the nucleation layer regrows epitaxially and, as a consequence of the thermal expansion coefficient mismatch between Si and GaAs, MDs are introduced at the GaAs/Si interface. As revealed by cross-section TEM analyses, these dislocations are confined to within ~3 nm from the GaAs/Si interface (**Figure 16(c**)). In the second stage growth proceeded in a layerby-layer fashion, which yielded monocrystalline GaAs of high quality and low roughness (**Figure 16(b**)).

#### 2.2. Defect filtering by multiple quantum dot layers

Another approach to enhance the quality of III–V semiconductor layers grown on mismatched substrates, exploits multiple layers of QDs, which act as a filter for threading defects [51]. QDs form by self-organized Stranski-Krastanov growth of a semiconductor material which shows (i) good wettability and (ii) considerable lattice misfit to the host crystal on which it is deposited. Typically, the QD layers are not grown directly on the substrate, but on a low-temperature buffer of the III–V layer material to be deposited (Figure 17(a)). In this way, the QD layers hinder the threading defects coming from the plastically relaxed buffer in extending to the subsequently grown III-V layer. Moreover, misfit strain in the vicinity of the QD layer originates only from the misfit between the QD and the III-V layer material, and not additionally from misfit between different lower and upper layer materials. The defect blocking effect has been explained by a deflection of the defect propagation induced by the strain fields of the QDs [52, 53]. In these strain fields dislocations experience shear Peach-Koehler forces, which lead to a sideward deflection so that the dislocation is redirected towards the material edges or subjected to annihilation before reaching the surface (Figure 17(a)). Calculations based on continuum elasticity predict increasing effectiveness of a single QD layer to bend TDs with increasing QD base area, but only a weak increase with QD height [52]. Besides the QD base area, the dislocation bending effectiveness is enhanced by using a larger number of QD layers. However, in the case of too large QDs or too large number of QD layers strain accumulates and gives rise to MD formation. Therefore, an optimum layer quality is expected for a QD size and number of QD layers just below the critical values for dislocation formation. For the Si/ GaAs system, Yang et al. reported that a defect filter layer consisting of ten InAs QD layers with a QD width of 20–30 nm separated by 50 nm spacer layers on 2 µm GaAs buffer layer

**Figure 16.** (a) Schematic of the two-stage MBE growth on  $SiO_2$  hole mask patterned Si(111), (b) cross-section TEM image of the Si/GaAs heterostructure fabricated by the procedure of (a), (c) HRTEM image from the marked area in (b). (Reprinted (adapted) with permission from [49]. Copyright 2014 American Chemical Society.)

was most effective [52]. Their TEM analysis demonstrated that 60° dislocations were bent to the side (i.e. the dislocation labelled 'B' in **Figure 17(b)**), and moreover, that pure edge dislocations were stopped at the interface between the GaAs spacer layer and the QD (the dislocation labelled 'C' in **Figure 17(b)**). The detailed mechanism of this blocking of edge dislocations is not well understood. Apart from dislocation filtering, QD layers also contribute to reduce the density of point defects in the layer, because the QD strain field imposes a driving force for point defects with compressive (dilatative) strain to migrate to elastically dilated (compressed) lattice regions. Further reduction of the defect density, measured as the etch pit density on the GaAs layer surface, was enabled by a combined application of QD dislocation filter layers and a buffer layer grown in three stages, starting with low temperature, followed by intermediate and eventually high-temperature growth [54]. However, the etch pit density of 9×10<sup>5</sup> cm<sup>-2</sup> resulting for a GaAs top layer thickness of 1 µm [54] still exceeds the value achieved with ART growth of GaAs using a SiO<sub>2</sub> cylinder hole mask [48] (Section 2.1.3.2).

#### 2.3. Growth on mask-free nanopatterned surfaces

Although the growth on mask-free nanopatterned surfaces has been frequently used for site controlled fabrication of semiconductor QDs or nanoislands [55], it is also beneficial for improving the quality of continuous III–V layers [56–59]. Here, 'nanopatterned' means that the substrate surface exhibits ordered or random topographical features with

**Figure 17.** (a) Schematic cross-section of a heterostructure, in which multiple QD layers are deployed as dislocation filter, (b) cross-section TEM image using (113) diffracting planes, showing the bending or blocking effect of a ten-fold InAs QD layer stack on threading dislocations (A, B, C) in GaAs grown on Si(001) substrate. ((b) (Copyright 2007 IEEE. Reprinted, with permission, from [52].)

dimensions well below 1  $\mu$ m. In general, the insufficient blocking of threading defect propagation in the growth on mask-free nanopatterned surfaces leads to a lower increase of the layer quality as compared to the heteroepitaxy approaches based on: (i) selective growth on mask-patterned substrates (Section 2.1) and (ii) on growth using QD dislocation filter layers (Section 2.2). Nevertheless, growth on mask-free nanopatterned surfaces is interesting for reducing defect densities in III–V layers because of the simplicity and low cost of the processes needed for the substrate nanopatterning. Essentially, the active defect elimination mechanisms originating from the reduced growth area size and the geometry of the substrate surface rely on three-dimensional elastic lattice relaxation of the substrate and/or the layer as well as on defect trapping at steep or concave topographic features.

So far, morphologically different surfaces fabricated by different methods have been deployed in studies of the quality of III–V layers grown on mask-free nanopatterned surfaces. One possibility to create nanoroughened surfaces is *in-situ* annealing of Si(001) in  $H_2/O_2$  ambient in the MOVPE reactor, which effects the formation of volatile Si compounds such as SiO and thus a nanoscale roughening (pitting) of the Si surface. By using spectroscopic polarimetry Liu et al. [56] showed that polar GaP deposited by MOVPE on non-polar nanoroughened vicinal Si(001) (misfit ~0.4%) formed continuous layers, and attributed the continuous layer growth to a large number of nucleation sites owing to the higher reactivity between nanoroughened Si and the TMGa precursor, whose mobility was seen to decrease.

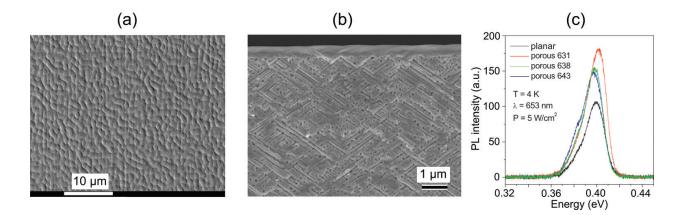

Nohavica et al. [57] performed liquid phase epitaxy growth of InAs on electrochemically etched micro- to nanoporous InP substrates (misfit ~3.2%). Due to the enhanced elastic relaxation of misfit strains an improved InAs layer morphology and a 20–35% reduction of the dislocation density of etched surfaces were obtained as compared to an InAs layer grown on a planar InP substrate. Similarly, the same group reported MOVPE growth and characterization of In<sub>x</sub>Ga<sub>1-x</sub>As layers ( $0.2 \le x \le 1$ ) on electrochemically etched nanoporous GaAs(001) substrates [58]. Such nanoporous GaAs surfaces showed low roughness areas

between the pore openings and are therefore suitable for nucleation of a layer on these small smooth areas. SEM images revealed a relatively smooth surface of a deposited 0.4  $\mu$ m thick In<sub>0.2</sub>Ga<sub>0.8</sub>As layer (**Figure 18(b**)). However, the mosaic-shaped pattern visible in top-view SEM images indicated the presence of grains (**Figure 18(a**)). InAs layers grown on nanoporous GaAs exhibited enhanced low-temperature photoluminescence emission as compared to an InAs layer of same thickness grown on planar substrate (**Figure 18(c**)). As crystal defects boost non-radiative electronic transitions, the photoluminescence intensity represents an indicator of the crystal quality. The observed improved crystal quality can be assigned to elastic relaxation of misfit strains both in the layer and in the substrate during lateral pore overgrowth leading to a reduction of the defect density. Due to the high porosity of the GaAs substrate of ~50% compliancy of the substrate lattice is expected.

**Figure 18.** Plan view (a) and cross-section (b) SEM images of a 0.4  $\mu$ m thick In<sub>0.2</sub>Ga<sub>0.8</sub>As layer on nanoporous GaAs(001) substrate (misfit ~1.4%), (c) photoluminescence spectra of 1.2  $\mu$ m thick InAs layers grown on planar and on porous GaAs(001) substrates with different pore layer thicknesses (610–631, 635–638, 641–643  $\mu$ m). (Reprinted from [58], Copyright 2013, with permission from Elsevier.)

# 3. Relevance of nanoheteroepitaxial layers for advanced optoelectronic applications

It has been recognized long ago that excellent crystalline quality is essential for a high performance of semiconductor power and optoelectronic devices. In particular, minority carrier devices such as insulated-gate bipolar transistors, as well as light-emitting and absorbing devices require dislocation densities below 10<sup>5</sup> cm<sup>-2</sup> [24, 60], which has not been achieved by traditional methods of defect reduction in planar III–V heteroepitaxy on the common Si platform. However, in the last 10 years, substantial progress has been made in the heteroepitaxial growth of low-defect, mismatched semiconductors by using nanopatterned substrates, which allowed to accomplish a good crystalline quality of III–V layers close to that needed for long-lifetime devices. Recently, these nanoheteroepitaxy methods have been exploited for the realization of several III–V devices integrated on a Si platform. Examples include laser diodes [59, 61], GaAs solar cells [49], and GaAs/In<sub>x</sub>Ga<sub>1-x</sub>As tunnel diodes for digital circuits applied e.g. in inverters or random-access memory cells [62, 63]. Further applications have been proposed such as In-rich In<sub>x</sub>Ga<sub>1-x</sub>As channels for n-type metal oxide semiconductor field effect transistors with enhanced electrical characteristics [64] or GaAs waveguides for lasers [42]. Exemplarily, we will briefly describe the fabrication and performance of two such unique devices, one using oxide-separated, disc-shaped III–V volumes as the active region of a solar cell, and one exploiting the V-groove defect reduction technique as the basis for a QD microdisc laser structure.

#### 3.1. GaAs nanodisc *p-i-n* solar cell on Si(111) nanopatterned with a SiO, hole mask

A prototype GaAs nanodisc *p-i-n* solar cell was fabricated on p-doped Si(111) substrate by using two-stage MBE growth for selective deposition of an intrinsic GaAs buffer layer (nucleation layer: 25 nm, main layer: 150 nm) in the circular openings of a SiO<sub>2</sub> hole mask, as described in Section 2.1.3.2 [50]. On the (111) surface of the buffer layer 50 nm of strongly n-doped (n+) GaAs was grown. To complete the device, indium tin oxide (ITO) and indium contacts were deposited on the top GaAs and bottom Si, respectively (**Figure 19(a)**). In the dark, the current density-voltage characteristic of the solar cell showed a good rectification behaviour with a current ratio > 10<sup>2</sup> for ±1 V bias (**Figure 19(b**)). Under illumination of one sun AM 1.5G a short circuit current of 18.4 mA/cm<sup>2</sup>, an open circuit voltage of 0.18 V, an ideality factor *n* = 1.6 and a fill factor of 28% were obtained. The resulting energy conversion efficiency of 0.9% is similar to the values reported for nanostructured solar cells, but much lower than those for conventional Si solar cells. The poor conversion efficiency and fill factor can be explained by surface states at the GaAs/SiO<sub>2</sub> interface and carrier-trapping dislocations at the Si/GaAs interface. It is expected that these characteristic values can be enhanced by suitable SiO<sub>2</sub> surface passivation and improved contacts.

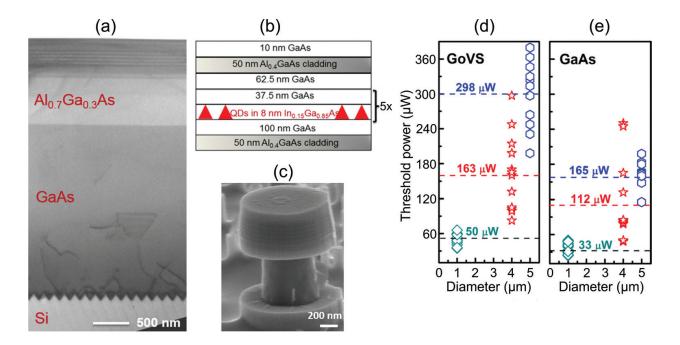

#### 3.2. QD microdisc laser using nanoheteroepitaxial buffer on Si(001)

GaAs buffer layers on V-grooved exact-oriented Si(001) templates have been used to fabricate InAs/In<sub>x</sub>Ga<sub>1-x</sub>As dot-in-a-well microdisc laser structures emitting at ~1.2 µm wavelength with almost similar characteristics as devices fabricated on native GaAs substrate [59]. For the growth of the low-defect GaAs buffer layer a two-step deposition was used starting with selective growth in SiO<sub>2</sub> trenches followed by SiO<sub>2</sub> removal and the mask-free GaAs coalescence growth step by MOVPE, as described in Section 2.1.3.1. The active region comprised five InAs QD layers embedded in In<sub>x</sub>Ga<sub>1-x</sub>As quantum wells separated by GaAs spacer layers, respectively, grown by MBE (**Figure 20(b**)). **Figure 20(a**) depicts a cross-section TEM image of the as-deposited layer structure. In order to obtain the micro-discs (**Figure 20(c**)) colloidal lithography and reactive ion etching were deployed.

Optical emission spectra were measured with a micro-photoluminescence setup in surfacenormal pump/collection configuration under continuous wave excitation at 10 K. A low average threshold power of 50  $\mu$ W has been achieved for 1  $\mu$ m disc diameter, as compared to 33  $\mu$ W for

**Figure 19.** (a) Schematic cross-section of the p-i-n solar cell grown on Si(111), (b) current density-voltage characteristics of the device in the dark and under illumination of one sun AM 1.5G. The inset shows a semilogarithmic current density-voltage curve for the non-illuminated state. (Reprinted (adapted) with permission from [49]. Copyright 2014 American Chemical Society.)

lasers on GaAs substrate (**Figure 20(d, e**)). With increasing disc diameter the threshold power rose due to smaller mode separation, occurrence of multimode lasing and absorption in the microdisc centre. The larger lasing thresholds on the Si substrate can be explained by the presence of crystal defects (i) inside the active region, reducing the modal gain and (ii) outside the active region promoting carrier recombination, thus lowering the injection efficiency of the carriers.

**Figure 20.** (a) Cross-section TEM image of the as deposited laser structure on V-grooved Si(001), (b) Schematic crosssection of layers in the disc region, (c) oblique-view SEM image of the microdisc, (d, e) threshold power for different disc diameters on GaAs-on-V-groove-Si (GoVS) template (d) and on GaAs substrate (e). The dashed lines denote the average thresholds. (Reproduced from [59], with the permission of AIP Publishing.)

### 4. Summary

In summary, heteroepitaxial approaches deploying nanopatterned substrates for the growth of mismatched III–V zinc blende semiconductor layers of low defect density are reviewed. As an important growth mode occurring in some of these approaches, nanoscale selective growth is explained with focus on its scaling with adatom surface migration and desorption. Efficient trapping and elimination of misfit-related defects has been demonstrated by ART techniques using nanopatterned oxide or nitride masks as well as by utilization of multiple QD defect filter layers. The active mechanisms of defect elimination in these growth methods are described. Besides, heteroepitaxial growth on mask-free nanoporous substrates also reduces the defect density, albeit in a less pronounced fashion. Finally, selected applications of low-defect III–V layers integrated on the common Si platform are presented. Remarkably, laser structures on the Si substrate have been realized exhibiting characteristics not far from those of structures grown on native GaAs substrates.

# Acknowledgements

The authors acknowledge financial support of the German Science Foundation (DFG) under project numbers Ri2655/1-1 and Li449/16-1.

# Author details

Thomas Riedl\* and Jörg K.N. Lindner

\*Address all correspondence to: thomas.riedl@uni-paderborn.de

Department of Physics, University of Paderborn, Paderborn, Germany

# References

- [1] Vurgaftman I, Meyer JR, Ram-Mohan LR. Band parameters for III–V compound semiconductors and their alloys. Journal of Applied Physics. 2001;89:5815–5875. DOI: 10.1063/1.1368156

- [2] Adachi S. Properties of Group-IV, III-V and II-VI Semiconductors. Chichester: J. Wiley & Sons; 2005. 387 p. DOI: 10.1002/0470090340

- [3] Stillman GE, Wolfe CM, Dimmock JO. Hall coefficient factor for polar mode scattering in n-type GaAs. Journal of Physics and Chemistry of Solids. 1970;31:1199–1204. DOI: 10.1016/0022-3697(70)90122-8

- [4] Rode DL. Electron transport in InSb, InAs and InP. Physical Review B. 1971;3:3287–3299. DOI: 10.1103/PhysRevB.3.3287

- [5] Duggen L, Willatzen M, Lassen B. Crystal orientation effects on the piezoelectric field of strained zinc-blende quantum-well structures. Physical Review B. 2008;78:205323. DOI: 10.1103/PhysRevB.78.205323

- [6] Lourdudoss S. Heteroepitaxy and selective area heteroepitaxy for silicon photonics. Current Opinion in Solid State and Materials Science. 2012;16:91–99. DOI: 10.1016/j. cossms.2012.01.003

- [7] Mahajan S. Defects in semiconductors and their effects on devices. Acta Materialia. 2000;48:137–149. DOI: 10.1016/S1359-6454(99)00292-X

- [8] Groenert ME, Leitz CW, Pitera AJ, Yang V, Lee H, Ram RJ, Fitzgerald EA. Monolithic integration of room-temperature cw GaAs/AlGaAs lasers on Si substrates via relaxed graded GeSi buffer layers. Journal of Applied Physics. 2003;93:362–367. DOI: 10.1063/1.1525865

- [9] Hayafuji N, Miyashita M, Nishimura T, Kadoiwa K, Kumabe H, Murotani T. Effect of employing positions of thermal cyclic annealing and strained-layer superlattice on defect reduction in GaAs-on-Si. Japanese Journal of Applied Physics. 1990;29:2371–2375. DOI: 10.1143/JJAP.29.2371

- [10] Yamaguchi M. Dislocation density reduction in heteroepitaxial III-V compound films on Si substrates for optical devices. Journal of Materials Research. 1991;6:376–384. DOI: 10.1557/JMR.1991.0376

- [11] Takano Y, Hisaka M, Fujii N, Suzuki K, Kuwahara K, Fuke S. Reduction of threading dislocations by InGaAs interlayer in GaAs layers grown on Si substrates. Applied Physics Letters. 1998;73:2917–2919. DOI: 10.1063/1.122629

- [12] Kemper RM, Hiller L, Stauden T, Pezoldt J, Duschik K, Niendorf T, Maier HJ, Meertens D, Tillmann K, As DJ, Lindner JKN. Growth of cubic GaN on 3C–SiC/Si (001) nanostructures. Journal of CrystalGrowth. 2013;378:291–294. DOI: 10.1016/j.jcrysgro.2012.10.011

- [13] Kemper RM, As DJ, Lindner JKN. Cubic GaN on nanopatterned 3C-SiC/Si (001) substrates. In: Li H, Wu J, Wang ZM, editors. Silicon-based Nanomaterials. Springer Series in Materials Science 187; 2013. Chapter 15, pp. 381–405. DOI: 10.1007/978-1-4614-8169-0\_15

- [14] Luryi S, Suhir E. New approach to the high quality epitaxial growth of lattice mismatched materials. Applied Physics Letters. 1986;49:140–142. DOI: 10.1063/1.97204

- [15] Lee SC, Brueck SRJ. Scaling of the surface migration length in nanoscale patterned growth. Applied Physics Letters. 2009;94:153110. DOI: 10.1063/1.3117366

- [16] Lee SC, Dawson LR, Brueck SRJ, Stintz A. Heteroepitaxial selective growth of In<sub>x</sub>Ga<sub>1-x</sub>As on SiO<sub>2</sub>-patterned GaAs(001) by molecular beam epitaxy. Journal of Applied Physics. 2004;96:4856–4865. DOI: 10.1063/1.1786677

- [17] Lee SC, Malloy KJ, Brueck SRJ. Nanoscale selective growth of GaAs by molecular beam epitaxy. Journal of Applied Physics. 2001;90:4163–4168. DOI: 10.1063/1.1401805

- [18] Schroeder M, Wolf DE. Magic islands and submonolayer scaling in molecular beam epitaxy. Physical Review Letters. 1995;74:2062–2065. DOI: 10.1103/PhysRevLett.74.2062

- [19] Neave JH, Dobson PJ, Joyce BA, Zhang J. Reflection high-energy electron diffraction oscillations from vicinal surfaces—A new approach to surface diffusion measurements. Applied Physics Letters. 1985;47:100–102. DOI: 10.1063/1.96281

- [20] Spirkoska D, Colombo C, Heiss M, Abstreiter G, Fontcuberta i Morral A. The use of molecular beam epitaxy for the synthesis of high purity III-V nanowires. Journal of Physics: Condensed Matter. 2008;20:454225. DOI: 10.1088/0953-8984/20/45/454225

- [21] Zubia D, Zhang S, Bommena R, Sun X, Brueck SRJ, Hersee SD. Initial nanoheteroepitaxial growth of GaAs on Si(100) by OMVPE. Journal of Electronic Materials. 2001;30:812– 816. DOI: 10.1007/s11664-001-0062-7

- [22] Zubia D. Personal communication; 2017

- [23] Chin HC, Gong X, Ng TK, Loke WK, Wong CP, Shen Z, Wicaksono S, Yoon SF, Yeo YC. Nanoheteroepitaxy of gallium arsenide on strain-compliant silicon-germanium nanowires. Journal of Applied Physics. 2010;108:024312. DOI: 10.1063/1.3465327

- [24] Ismail K, Legoues F, Karam NH, Carter J, Smith HI. High-quality GaAs on sawtooth-patterned Si substrates. Applied Physics Letters. 1991;**59**:2418–2420. DOI: 10.1063/1.106034

- [25] Orzali T, Vert A, O'Brien B, Herman JL, Vivekanand S, Hill RJW, Karim Z, Rao SSP. GaAs on Si epitaxy by aspect ratio trapping: analysis and reduction of defects propagating along the trench direction. Journal of Applied Physics. 2015;118:105307. DOI: 10.1063/1.4930594

- [26] Zubia D, Hersee SD. Nanoheteroepitaxy: The application of nanostructuring and substrate compliance to the heteroepitaxy of mismatched semiconductor materials. Journal of Applied Physics. 1999;85:6492–6496. DOI: 10.1063/1.370153

- [27] Hersee SD, Zubia D, Sun X, Bommena R, Fairchild M, Zhang S, Burckel D, Frauenglass A, Brueck SRJ. Nanoheteroepitaxy for the integration of highly mismatched semiconductor materials. IEEE Journal of Quantum Electronics. 2002;38:1017–1028. DOI: 10.1109/ JQE.2002.800987

- [28] Jha S, Liu CC, Kuan TS, Babcock TS, Nealey PF, Park JH, Mawst LJ, Kuech TF. Defect reduction in epitaxial GaSb grown on nanopatterned GaAs substrates using full wafer block copolymer lithography. Applied Physics Letters. 2009;95:062104. DOI: 10.1063/1.3204013

- [29] Nakamura Y, Miwa T, Ichikawa M. Nanocontact heteroepitaxy of thin GaSb and AlGaSb films on Si substrates using ultrahigh-density nanodot seeds. Nanotechnology. 2011;22:265301. DOI: 10.1088/0957-4484/22/26/265301

- [30] He Y, Wang J, Hu H, Wang Q, Huang Y, Ren X. Coalescence of GaAs on (001) Si nanotrenches based on three-stage epitaxial lateral overgrowth. Applied Physics Letters. 2015;106:202105. DOI: 10.1063/1.4921621

- [31] Lee SC, Dawson LR, Huang SH, Brueck SRJ. Lithography-free nanoscale patterned growth of GaAs on Si(001) with sub-100-nm silica nanoparticles by molecular beam epitaxy. Crystal Growth and Design. 2011;**11**:3673–3676. DOI: 10.1021/cg101363q

- [32] May GS, Sze SM. Fundamentals of Semiconductor Fabrication. New York: J. Wiley & Sons; 2007. 320 p. ISBN: 978-0-471-23279-7

- [33] Wang G, Leys MR, Loo R, Richard O, Bender H, Waldron N, Brammertz G, Dekoster J, Wang W, Seefeldt M, Caymax M, Heyns MM. Selective area growth of high quality InP on Si (001) substrates. Applied Physics Letters. 2010;97:121913. DOI: 10.1063/1.3491554

- [34] Wang G, Leys MR, Nguyen ND, Loo R, Brammertz G, Richard O, Bender H, Dekoster J, Meuris M, Heyns MM, Caymax M. Growth of high quality InP layers in STI trenches on miscut Si (0 0 1) substrates. Journal of Crystal Growth. 2011;315:32–36. DOI: 10.1016/j. jcrysgro.2010.07.039

- [35] Wang G, Leys M, Loo R, Richard O, Bender H, Brammertz G, Waldron N, Wang WE, Dekoster J, Caymax M, Seefeldt M, Heyns M. Selective area growth of InP and defect elimination on Si (001) substrates. Journal of the Electrochemical Society. 2011;158:H645– H650. DOI: 10.1149/1.3571248

- [36] Merckling C, Waldron N, Jiang S, Guo W, Richard O, Douhard B, Moussa A, Vanhaeren D, Bender H, Collaert N, Heyns M, Thean A, Caymax M, Vanderhorst W. Selective area growth of InP in shallow trench isolation on large scale Si(001) wafer using defect confinement technique. Journal of Applied Physics. 2013;114:033708. DOI: 10.1063/1.4815959

- [37] Merckling C, Waldron N, Jiang S, Guo W, Barla K, Heyns M, Collaert N, Thean A, Vandervorst W. Selective-area metal organic vapour-phase epitaxy of III-V on Si: What about defect density? In: Harame D, Caymax M, Heyns M, Masini G, Miyazaki S, Niu G, Reznicek A, Saraswat K, Tillack B, Vincent B, Yeo YC, Ogura A, Murota J, editors. SiGe, Ge, and Related Compounds 6: Materials, Processing, and Devices. Book Series: ECS Transactions Vol. 64, pp. 513–521. Pennington: The Electrochemical Society; 2014. DOI: 10.1149/06406.0513ecst

- [38] Lee SM, Cho YJ, Park JB, Shin KW, Hwang E, Lee S, Lee MJ, Cho SH, Shin DS, Park J, Yoon E. Effects of growth temperature on surface morphology of InP grown on patterned Si(001) substrates. Journal of Crystal Growth. 2015;416:113–117. DOI: 10.1016/j. jcrysgro.2015.01.027

- [39] Li JZ, Bai J, Park JS, Adekore B, Fox K, Carroll M, Lochtefeld A, Shellenbarger Z. Defect reduction of GaAs epitaxy on Si (001) using selective aspect ratio trapping. Applied Physics Letters. 2007;91:021114. DOI: 10.1063/1.2756165

- [40] Guo W, Date L, Pena V, Bao X, Merckling C, Waldron N, Collaert N, Caymax M, Sanchez E, Vancoille E, Barla K, Thean A, Eyben P, Vandervorst W. Selective metal-organic chemical vapour deposition growth of high quality GaAs on Si(001). Applied Physics Letters. 2014;105:062101. DOI: 10.1063/1.4892468

- [41] David S, Roque J, Rochat N, Bernier N, Piot L, Alcotte R, Cerba T, Martin M, Moeyaert J, Bogumilowizc Y, Arnaud S, Bertin F, Bassani F, Baron T. Spatially correlated structural and optical characterization of a single InGaAs quantum well fin selectively grown on Si by microscopy and cathodoluminescence techniques. APL Materials. 2016;4:056102. DOI: 10.1063/1.4949761

- [42] Kunert B, Guo W, Mols Y, Tian B, Wang Z, Shi Y, Van Thourhout D, Pantouvaki M, Van Campenhout J, Langer R, Barla K. III/V nano ridge structures for optical applications on patterned 300 mm silicon substrate. Applied Physics Letters. 2016;109:091101. DOI: 10.1063/1.4961936

- [43] Hsu CW, Chen YF, Su YK. Heteroepitaxy for GaAs on nanopatterned Si (001). IEEE Photonics Technology Letters. 2012;24:1009–1011. DOI: 10.1109/LPT.2012.2192726

- [44] Paladugu M, Merckling C, Loo R, Richard O, Bender H, Dekoster J, Vandervorst W, Caymax M, Heyns M. Site selective integration of III-V materials on Si for nanoscale logic and photonic devices. Crystal Growth and Design. 2012;12:4696–4702. DOI:10.1021/ cg300779v

- [45] Ting SM, Fitzgerald EA. Metal-organic chemical vapour deposition of single domain GaAs on Ge/Ge<sub>x</sub>Si<sub>1-x</sub>/Si and Ge substrates. Journal of Applied Physics. 2000;87:2618– 2628. DOI: 10.1063/1.372227

- [46] Li JZ, Bai J, Major C, Carroll M, Lochtefeld A, Shellenbarger Z. Defect reduction of GaAs/ Si epitaxy by aspect ratio trapping. Journal of Applied Physics. 2008;103:106102. DOI: 10.1063/1.2924410

- [47] Li Q, Ng KW, Lau KM. Growing antiphase-domain-free GaAs thin films out of highly ordered planar nanowire arrays on exact (001) silicon. Applied Physics Letters. 2015;106:072105. DOI: 10.1063/1.4913432

- [48] Hsu CW, Chen YF, Su YK. Nanoepitaxy of GaAs on a Si(001) substrate using a roundhole nanopatterned SiO<sub>2</sub> mask. Nanotechnology. 2012;23:495306. DOI: 10.1088/0957-4484/23/49/495306

- [49] Chu CP, Arafin S, Nie T, Yao K, Kou X, He L, Wang CY, Chen SY, Chen LJ, Qasim SM, BenSaleh MS, Wang KL. Nanoscale growth of GaAs on patterned Si(111) substrates by molecular beam epitaxy. Crystal Growth and Design. 2014;14:593–598. DOI: 10.1021/ cg401423d

- [50] Chang YJ, Simmonds PJ, Beekley B, Goorsky MS, Woo JCS. Selective-area growth of heavily n-doped GaAs nanostubs on Si(001) by molecular beam epitaxy. Applied Physics Letters. 2016;108:163106. DOI: 10.1063/1.4947436

- [51] Huang D, Reshchikov MA, Yun F, King T, Baski AA, Morkoc H. Defect reduction with quantum dots in GaN grown on sapphire substrates by molecular beam epitaxy. Applied Physics Letters. 2002;80:216–218. DOI: 10.1063/1.1432445

- [52] Yang J, Bhattacharya P, Mi Z. High-performance In<sub>0.5</sub>Ga<sub>0.5</sub>As/GaAs quantum-dot lasers on silicon with multiple-layer quantum-dot dislocation filters. Transactions on Electron Devices. 2007;54:2849–2855. DOI: 10.1109/TED.2007.906928

- [53] Bhattacharya P, Mi Z, Yang J, Basu D, Saha D. Quantum dot lasers: from promise to highperformance devices. Journal of Crystal Growth. 2009;311:1625–1631. DOI: 10.1016/j. jcrysgro.2008.09.035

- [54] Hu H, Wang J, He Y, Liu K, Liu Y, Wang Q, Duan X, Huang Y, Ren X. Modified dislocation filter method: toward growth of GaAs on Si by metal organic chemical vapor deposition. Applied Physics A. 2016;122:588. DOI: 10.1007/s00339-016-0116-6

- [55] Usman M, Reithmaier JP, Benyoucef M. Site-controlled growth of GaAs nanoislands on pre-patterned silicon substrates. Physica Status Solidi A. 2015;212:443–448. DOI: 10.1002/ pssa.201431459

- [56] Liu X, Kim IK, Aspnes DE. Investigation of heteroepitaxy on nanoscopically roughened (001)Si by real-time spectroscopic polarimetry. Physica Status Solidi C. 2008;5:1312–1315. DOI: 10.1002/pssc.200777896

- [57] Nohavica D, Grym J, Hulicius E, Pangrac J, Gladkov P, Jarchovsky Z. Epitaxial overgrowth of InP and GaAs micropores, microcavities and microlamellas by InAs and InGaAs. In: Proceedings of the 2nd NANOCON International Conference; 12–14 October 2010; Olomouc/Czech Republic. pp. 28–33. ISBN: 978-80-87294-19-2

- [58] Grym J, Nohavica D, Gladkov P, Hulicius E, Pangrac J, Piksova K. Epitaxial growth on porous GaAs substrates. Comptes Rendus Chimie. 2013;**16**:59–64. DOI: 10.1016/j. crci.2012.06.012

- [59] Wan Y, Li Q, Liu AY, Chow WW, Gossard AC, Bowers JE, Hu EL, Lau KM. Subwavelength InAs quantum dot micro-disk lasers epitaxially grown on exact Si (001) substrates. Applied Physics Letters. 2016;108:221101. DOI: 10.1063/1.4952600

- [60] Kroemer H. MBE growth of GaAs on Si: Problems and progress. MRS Symposium Proceedings. 1986;67:3–14. DOI: 10.1557/PROC-67-3

- [61] Wang Z, Tian B, Pantouvaki M, Guo W, Absil P, Campenhout JV, Merckling C, Van Thourhout D. Room-temperature InP distributed feedback laser array directly grown on silicon. Nature Photonics. 2015;9:837–843. DOI: 10.1038/NPHOTON.2015.199

- [62] Li Q, Han Y, Lu X, Lau KM. GaAs-InGaAs-GaAs fin-array tunnel diodes on (001) Si substrates with room-temperature peak-to-valley current ratio of 5.4. IEEE Electron Device Letters. 2016;37:24–27. DOI: 10.1109/LED.2015.2499603