# We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

6,900

186,000

200M

Download

154

Countries delivered to

Our authors are among the

**TOP 1%**

most cited scientists

12.2%

Contributors from top 500 universities

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected.

For more information visit www.intechopen.com

# **Tailoring Oxide/Silicon Carbide Interfaces:**

**NO Annealing and Beyond**

John Rozen

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/54396

#### 1. Introduction

We live in an energy-hungry world in which industrialization and globalization have accelerated the demand for resources that now doubles approximately every 40 years. Today, we consume about 18 TW ( $18 \times 10^{12}$  Watts) which is equivalent to 97 billion barrels of crude oil yearly. While renewable energy sources offer an environmentally conscious alternative to fossil fuels, they account for only about 10% of this total [64]. In parallel to the advent of clean energy, an effort has to be made to curb consumption, which can in part be achieved by improving system efficiency. In this Section, we will discuss in such terms why high-volume sectors such as transportation, electricity generation, and distribution, can benefit from SiC-based electronics.

First, it should be recognized that the adoption of a new technology will be driven mainly by component cost and end-user benefits. Silicon carbide electronics is no exception and only makes sense if it can deliver on these fronts. A good example is the recent introduction of the pricier fluorescent light sources which make financial sense in the long term since they consume a fraction of the energy of incandescent bulbs and last some 20 times longer, proving that efficiency and reliability can justify the investment. So what are the key parameters that influence SiC device cost and efficiency?

Cost - Substrate size and availability have benefited from the boom in LED demand as III-nitride blue diodes can be fabricated on SiC. Indeed, the diameter of commercially available substrates has steadily increased from the release of two inch (50 mm) wafers in September 1997 to the recent unveiling of six inch (150 mm) wafers in August 2012 by Cree, inc., a very fast pace compared to Si evolution [100]. Also, tremendous quality improvements have been achieved together with increased process rate and uniformity. One of the many challenges facing SiC production has been the reduction of extended defects such as micropipes [29, 49]. Today, substrates are virtually free of such defects, optimizing device

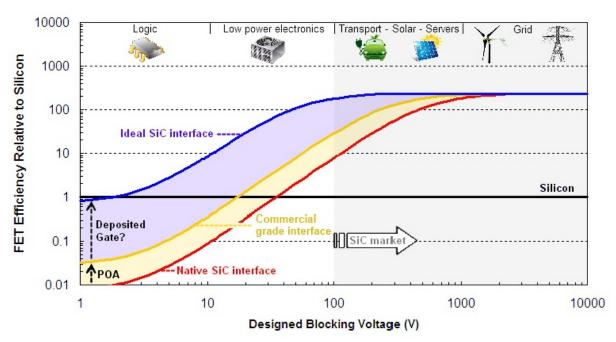

**Figure 1.** DC efficiency of SiC-based FETs relative to Si devices at given designed blocking voltages. While commercially available switches using NO-annealed thermal gate oxides have improved efficiency, one suggested route is the use of deposited oxides to achieve optimum properties [109].

yield. Demand and production costs have thus progressively driven down the price of the material, which has translated into cheaper and higher quality components for optoelectronic and high power applications.

Efficiency - While investment costs have diminished, SiC-based devices are still more expensive than their Si counterparts. Their efficiency is what can make them attractive As illustrated in Fig. in the long run. 1, the energy consumption of metal-oxide field-effect transistors (MOSFETs) can be orders of magnitude lower when using silicon carbide as a substrate to control high blocking voltages. Industries that would benefit from the widespread of such components include transportation, electricity distribution, grid coupling, high-performance computing, etc. Indeed, automakers have invested heavily in SiC research, targeting the implementation of SiC-based inverters in hybrid vehicles. To get an idea of how single device consumption will translate into system efficiency, let's take the example of photovoltaic (PV) power converters. PV inverters are used to convert the DC current from solar sources to feed it to the AC grid. They are made of power diodes and switches. A typical residential system has a nominal power of 5 kW at 400 V AC. Such Si-based converters can operate at over 95% efficiency but replacing Si components by commercially available SiC Schottky diodes and power MOSFETs can cut the loss by about 50%, yielding a saving of the order of \$100 a year per household [22, 23]. Moreover, they can operate at higher temperature, so that limited cooling and volume requirements go in favor of system prices which can indeed prove beneficial over the years for the consumer choosing to adopt the new technology.

Further improvements in SiC device efficiency will make the case even stronger. Among the key building blocks at the device level is the oxide/semiconductor interface. Figure 1 highlights how it affects consumption, especially at low biases. In this Chapter, we will derive important parameters defining SiC devices from physical properties, and discuss the role and formation of the oxide/semiconductor interface, covering thermal oxides, post-oxidation annealing, and deposited dielectrics.

# 2. Breakdown field and device efficiency

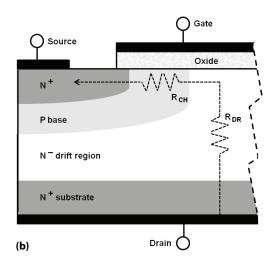

Let us compare vertical double-implanted MOSFETs (DMOSFETs) designed to control the same bias, one Si-based, the other SiC-based, as shown in Fig. 2(b), using the constants of Fig. 2(a). The key differences between the two materials can be traced back to the Si-Si bond and the Si-C bond, respectively. The stronger interaction between silicon and carbon atoms is evidenced by the shorter bond length of 1.89 Å when compared to 2.35 Å for Si-Si. The proximity of atoms in SiC yield a more pronounced splitting of bonding and antibonding levels, which translates into a wider band gap in the periodic crystalline structures. The diatomic base of silicon carbide also explains the better thermal conductivity of the material because its vibration modes, i.e. phonons, are more energetic on average, as reflected in the Debye temperature. Ultimately, it is the phonon distribution that explains the higher critical field of silicon carbide,  $\xi_c$ , that can be used to derive a key parameter impacting device efficiency in high power electronics, the drift component of the specific ON resistance.

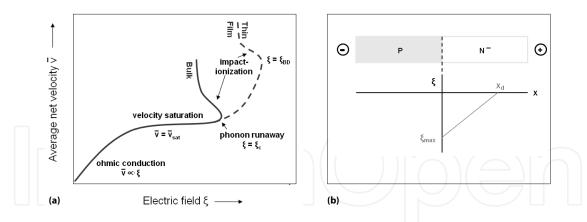

The breakdown field of a material is indeed not directly related to its band gap  $E_g$ . While, to first order, the free carriers need to reach a kinetic energy of at least 3/2  $E_g$  to induce the cascading impact ionization phenomenon, called avalanche, that multiplies the number of carriers and therefore the conductivity, the limiting factor in the bulk is phonon coupling [84, 86]. If the net velocity of carriers  $\bar{v}$ , proportional to the current, is smaller than or equal to the thermal velocity  $v_{th} = \sqrt{3k_bT/m^*}$ , the electron-phonon system is in equilibrium because of the ability of phonons to thermalize the carriers. In that regime, phonon scattering damps the energy gain of free carriers whose distribution in the bands can be visualized as a Fermi sphere slightly shifted in the direction of the electric field. However, if the field increases and reaches  $\xi_c$ , the rate at which carriers gain energy becomes too high to allow equilibrium with the lattice vibrations. Hot carriers then achieve phonon runaway. Their motion is no longer damped and they can accelerate freely from  $v_{th}$  to the critical speed  $v_c \approx \sqrt{3E_g/m^*}$  allowing the avalanche process to start. It is worth noting here that in thin films, an additional constraint comes from the time the carriers take to accelerate to  $v_c$ , so that  $\xi_c$  can become larger than the bulk value, as illustrated in Fig. 3(a).

| <u> </u>                                      | 411.6:6 | C:1:    |

|-----------------------------------------------|---------|---------|

| Constant                                      | 4H-SiC  | Silicon |

| Bandgap $E_g(eV)$                             | 3.26    | 1.12    |

| $e^-$ mobility $\mu_e$ (cm <sup>2</sup> /V.s) | 1000    | 1400    |

| $e^-$ effective mass $(m^*/m_0)$              | 0.36    | 0.26    |

| Critical field $\xi_c(MV/cm)$                 | 2.2     | 0.3     |

| Dielectric constant $(\epsilon/\epsilon_0)$   | 9.7     | 11.7    |

| Debye temperature $T_d(K)$                    | 1300    | 640     |

| Th. conductivity $\theta$ (W/cm.K)            | 3.7     | 1.5     |

|                                               |         |         |

(a)

**Figure 2.** (a) Properties of 4H-SiC and Si with  $10^{15}$ - $10^{16}$  cm<sup>-2</sup> doping at 300 K [30, 65, 66, 84, 121]. (b) Vertical power DMOSFET.

**Figure 3.** (a) Hot carrier velocity saturation and dielectric breakdown [105]. (b) Field distribution in a one-sided reverse-biased PN junction.

The critical field  $\xi_c$  of a semiconductor, can be used to design the most efficient device for a given blocking voltage  $V_d$ . When a DMOSFET is in the OFF state, the positive bias applied to the drain is entirely dropped in the N<sup>-</sup> drift region [84, 124]. Indeed, together with the P base, it forms a reverse-biased one-sided PN junction, represented in Fig. 3(b). For a large blocking voltage,  $V_d \gg E_g/q$ , the extent of the depletion region on the lowly-doped side in the step-junction approximation is

$$x_d = \sqrt{\frac{2\epsilon_s V_d}{q N_d}} \tag{1}$$

where  $N_d$  is the density of donor atoms in the drift region,  $\epsilon_s$  is the permittivity of the semiconductor, and q is the elementary charge. The peak electric field, at the boundary, being

$$\xi_{max} = 2\frac{V_d}{x_d} = \sqrt{\frac{2qN_dV_d}{\epsilon_s}}$$

(2)

The highest doping concentration that can sustain  $V_d$  is therefore

$$N_d^* = \xi_c^2 \frac{\epsilon_s}{2qV_d} \tag{3}$$

obtained by substituting for the critical field in Eq. (2). Then, from Eqs. (1) & (3), the minimum thickness of the drift region is given by

$$x_d^* = 2\frac{V_d}{\xi_c} \tag{4}$$

Accordingly, the drift region of a 4H-SiC DMOSFET can be substantially thinner and more highly doped than a Si-based device designed to control the same bias. Neglecting the current spread [9], the ratio of the optimal ON resistance components from the drift region can thus be estimated by

$$\frac{R_{dr}^{*}}{R_{dr}^{*}}\Big|_{Si}^{SiC} = \frac{N_{d}^{*} \mu_{dr}}{x_{d}^{*}}\Big|_{Si} \frac{x_{d}^{*}}{N_{d}^{*} \mu_{dr}}\Big|_{SiC} = \frac{\mu_{dr} \epsilon_{s} \xi_{c}^{3}}{\mu_{dr} \epsilon_{s} \xi_{c}^{3}}\Big|_{SiC}$$

(5)

where  $\mu_{dr}$  is the drift mobility in the bulk of the semiconductor. Plugging the respective constants of the bulk semiconductors into Eq. (5) implies that in ideal devices the energy dissipated using 4H-SiC would be several hundred times lower compared to the Si equivalent for a given ON current [15].

In a real device, however, there are other components to the resistance such as the contact resistance and the channel resistance. Here we will discuss only the channel specific resistance which contains the contribution from the oxide/semiconductor interface of interest in this Chapter. It can be calculated using the long channel approximation as

$$R_{ch} = \frac{V_d}{I_{sat}} P^2 = \frac{LP}{nq\mu_{ch}} \tag{6}$$

where L is the channel length, P is the channel width, or the square cell pitch,  $\mu_{ch}$  is the inversion mobility, and n is the minority carrier density [9]. The total specific ON resistance is then

$$R_{tot} = R_{dr}^* + R_{ch} = \frac{x_d^*}{N_d^* q \mu_{dr}} + \frac{LP}{nq\mu_{ch}}$$

(7)

which has the following dependence on designed blocking voltage according to Eqs. (3) & (4)

$$R_{tot} = \frac{4V_d^2}{\mu_{dr}\epsilon_s \xi_c^3} + \frac{LP}{nq\mu_{ch}}$$

(8)

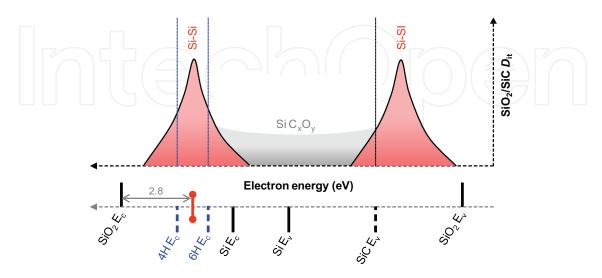

**Figure 4.** Schematic of the density of interface traps at the  $SiO_2/SiC$  interface.

From Eqs. (7) & (8), it can be seen that the smaller the designed blocking voltage, the smaller the width of the necessary drift region, and the larger the contribution from the channel resistance. In Si, that does not have a major impact in power devices because  $\mu_{ch}$  can be as high as 50% of the bulk value  $\mu_{dr}$ . However, SiC channels suffer from a mobility that can be less than 1% of  $\mu_{dr}$  at the native SiO<sub>2</sub>/4H-SiC interface. Therefore, interface quality can affect performance even in the kV range and the full potential of the SiC material cannot be reached. This is highlighted in Fig. 1, where the ratio of ON resistances was calculated using Fig. 2(a) constants,  $L=1\mu m$ ,  $P=10\mu m$ ,  $n=10^{15}$  cm<sup>-2</sup>, and the following SiC  $\mu_{ch}$ : 5, 50, and 500 cm<sup>2</sup>/V.s. The significance of those mobility values are discussed in the next Sections.

# 3. Channel mobility and interface state density

Mobility is a measure of the ease a carrier can be moved in a solid under the application of an electric field  $\xi$ . It can be related to the speed of the carrier which is limited by scattering events occurring at average time intervals  $\tau$ . Several types of scattering processes affect transport but the ones yielding the most frequent disturbances define the mobility value which can be written explicitly as

$$\frac{1}{\mu} = \frac{\xi}{\bar{v}} = \frac{m^*}{q} \sum_{i} \frac{1}{\tau_i} \tag{9}$$

where  $m^*$  is the effective mass,  $\bar{v}$  is the net drift velocity, and  $\tau_i$  corresponds to mean scattering times associated with various processes.

Because of the sudden termination of the semiconductor periodic lattice at the oxide interface, the channel mobility,  $\mu_{ch}$ , is expected to be lower than the bulk mobility. Indeed, electrically active levels can appear in the band gap and act as recombination centers or Coulomb scattering centers. Moreover, the free carriers can interact remotely with charged border states in the oxide, further reducing  $\tau_{Cb}$ . Other major damping mechanisms include surface-phonon and surface-roughness scattering represented by  $\tau_{ph}$  and  $\tau_{sr}$ , respectively. We note that the coupling of carriers to scattering effects depends strongly on their velocity such that Coulomb scattering dominates at low fields, while surface roughness scattering becomes dominant at higher fields. Because of these interface phenomena, the best  $\mathrm{SiO}_2/\mathrm{Si}$  devices display a channel mobility of about  $700~\mathrm{cm}^2/\mathrm{V.s}$ , equivalent to 50% of the bulk mobility [78]. In the case of 4H-SiC however, the native oxide interface yields mobilities of about  $5~\mathrm{cm}^2/\mathrm{V.s}$ , or less than 1% of the bulk value. So why is  $\mathrm{SiC}$  so affected by the formation of a thermally grown interface? Let us discuss it from the point of view of Coulomb scattering, so that the question becomes: why is the density of interface traps ( $D_{it}$ ) so much more prominent in  $\mathrm{SiC}$ ?

First, a down side of having a wider band gap is that it is sensitive to a wider range of defects. To first order, only the corresponding levels falling inside the band gap can be charged and yield Coulomb scattering. Since there is no evidence that SiO<sub>2</sub> formed on SiC is any different from thermally oxidized silicon [99], it can contain the same type of defects, some having energy levels affecting only SiC carriers. Let's take the example of the oxygen vacancy, detected by electron spin resonance (ESR) in both systems, which yields Si-Si bonds [75, 106]. The energy split of that dimer is inversely proportional to the proximity between

atoms. Long Si-Si bonds, i.e. bigger than 2.35 Å, can have energy levels inside both the Si and SiC gaps. But the splitting between short Si-Si levels can be outside the silicon gap while being electrically active at a  $SiO_2/SiC$  interface [90, 130], as illustrated in Fig. 4. The same analysis is true when comparing defect levels in the 6H- and 4H-SiC polytypes which have energy gaps of 3 and 3.3 eV, respectively. Because their valence bands are lined up, the conduction band of 4H-SiC is 0.3 eV higher. This is why the major defect affecting 4H-SiC, located 0.1 eV below its conduction band, has a limited impact on 6H-SiC devices [114]. It is interesting to note that this defect corresponds to an energy of 0.4 eV above the Si conduction band and that a similar trap level has been observed in  $SiO_2$  on Si even though it does not limit channel mobility [3, 4, 8].

The second reason explaining the large defect density at SiC interfaces is the oxidation process

$$2SiC + 3O_2 \rightarrow 2SiO_2 + 2CO \tag{10}$$

Like silicon oxidation, it follows the Deal-Grove reaction-diffusion model, so that the thermal oxide thickness as a function of time can be written as

$$x[t] = -\frac{1}{2} \frac{B}{B/A} + \frac{B}{2} \sqrt{\frac{1}{(B/A)^2} + \frac{4(t+t_0)}{B}}$$

(11)

where B/A is the linear rate constant, B is the parabolic rate constant, and  $t_0$  is an offset time constant [45]. For details on SiC oxidation kinetics and parameters corresponding to various orientations, pressures, and temperatures, see Refs. [43, 68, 98, 113, 122, 127, 135, 136]. But unlike Si oxidation, Eq. (10) implies the release of carbon. Because of this complex multi-step process, a variety of atomic defects involving C can result from oxide formation if CO molecules do not all find their way to the gas phase. [48, 71, 90]

Now that we have reviewed the impact and origin of defects at the SiO<sub>2</sub>/SiC interface, a comprehensive picture of associated trap levels limiting inversion mobility can be put forward, as shown in Fig. 4. Thermal oxidation of silicon carbide results in a  $SiC_xO_y$ inter-layer that includes threefold and fourfold coordinated Si and C atoms [8, 44, 90, 130]. Some generate dangling bonds whose energy spreads across the band gap because it is determined by the environment surrounding the defects. Another stable configuration yielding a trap level in the gap is a split C interstitial. When substituting for a Si site in the semiconductor, it can be viewed as a small C-aggregate or "C-cluster" comprising A carbon-rich interface has indeed been observed by techniques such as Rutherford backscattering (RBS) [46, 57, 89, 97], x-ray photoelectron spectroscopy (XPS) [54, 62, 67, 77, 128], electron energy-loss spectroscopy (EELS) [33-35], Raman spectroscopy [80], and in-situ spectroscopic ellipsometry [63]. The dominant defects however, are likely oxide-related. Indeed, Si-Si bonds of various lengths can extend into SiO<sub>2</sub> yielding interface and border traps [6, 17, 50, 72, 92, 112]. As mentioned before, the majority of corresponding bonding and antibonding states are located outside of the silicon gap but the former induce a distribution centered between the 4H and 6H-SiC conduction bands. The slightly smaller density of levels at lower energies is probably due to the majority of antibonding levels residing within the valence band of SiC whose edge is common in different polytypes [1]. The combination of trap levels associated with the  $SiC_xO_y$  inter-layer and Si-Si bonds, yields the U-shaped  $D_{it}$  distribution. It rises sharply towards the SiC band edges because of the Si-related defects not dominant at silicon interfaces. Therefore, the efficiency of passivation techniques are expected to be very different at interfaces formed on the two semiconductors.

In the following Sections, we will discuss how to reduce  $D_{it}$  and its relationship with mobility. Although there is extensive literature dedicated to various orientations and polytypes, this overview is dedicated to devices fabricated on the (0001) Si-face of 4H-SiC.

#### 4. Argon anneal

Oxidation conditions and post-oxidation annealing (POA) can affect the trap density at the  $SiO_2/4H$ -SiC interface. Both Ar anneal performed at growth temperature and re-oxidation at lower temperatures (e.g. 900 °C) have indeed proven to slightly reduce the amount of deep states [40, 129]. This can be explained by the removal of excess carbon without additional oxide formation, as corresponding atomic configurations yield defects populating interface states toward the middle of the gap. Since it does not reduce the density of levels close to the conduction band edge of 4H-SiC, Ar POA alone is not sufficient to enable efficient SiC devices. Nevertheless, it is typically used after thermal oxidation and before other annealing schemes.

# 5. Hydrogen passivation

Wet oxidation of 4H-SiC also yields a small reduction of interface states with energies away from the semiconductor band edges when compared to  $SiO_2$  formation in dry oxygen [2, 26, 55, 90, 130]. It correlates well with the effects of  $H_2$  POA. While at silicon interfaces hydrogen annealing yields a  $D_{it}$  from about  $10^{11}$  to  $10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup> in the middle of the gap and a mobility close to half the one of the bulk [20, 21], its impact at SiC interfaces is much less efficient, highlighting the differences between the two semiconductors [27, 58, 96]. Molecular hydrogen can indeed passivate Si- or C- dangling bonds, and insert long Si-Si bonds [28]. But it does not significantly affect split carbon interstitials and slow near interface states which populate the majority of the  $D_{it}$  at the 4H-SiC band edges. Like Ar annealing, wet oxidation and/or  $H_2$  POA can be used together with other annealing techniques to optimize the trap density throughout the semiconductor band gap.

#### 6. Nitridation

#### 6.1. NO annealing

In 1997, the group of Prof. Dimitrijev, at Griffitth University in Australia, demonstrated that high temperature (1100 °C) nitric oxide (NO) annealing reduces the  $D_{it}$  at SiO<sub>2</sub>/6H-SiC interfaces [76]. In 2000, Chung *et al.* published results on the effects of NO at the SiO<sub>2</sub>/4H-SiC interface revealing that, in addition to removing deep states, it is also very efficient at reducing the density of slow states (by a factor of  $\approx 10$ ), and yields an order of magnitude increase in the channel mobility from about 5 to 50 cm<sup>2</sup>/V.s along the Si-face [40, 41]. This breakthrough discovery, which originated from the joint effort between Auburn University and Vanderbilt University, led to the adoption of the NO process by the scientific and industrial communities as it enables the fabrication of high-quality oxide-based SiC power devices, facilitating their commercial release (Fig. 1).

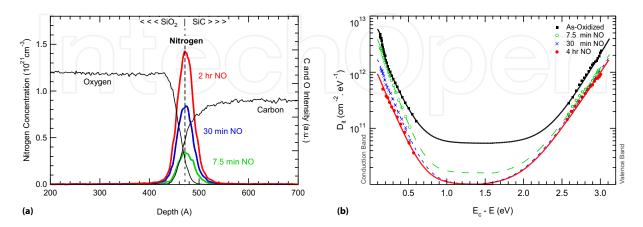

The benefits of NO annealing have been directly correlated with the incorporation of nitrogen, which is confined to the SiO<sub>2</sub>/SiC interface, as detected by various techniques such as secondary ion mass spectroscopy (SIMS) [82, 106], nuclear reaction analysis (NRA) [81], electron energy loss spectroscopy (EELS) [33], and medium energy ion scattering (MEIS) [47, 137]. To study the impact of nitrogen, the amount incorporated can be tailored by the NO annealing time as illustrated in Fig. 5(a). The N density is then extracted by integrating SIMS interface peaks resulting from 1175 °C NO exposure of a dry thermal oxide for up to 2 hours. The nitrogen content is found to saturate around  $6 \times 10^{14}$  cm<sup>-2</sup> or about a half monolayer coverage of the SiC surface. The nitridation kinetics result from a balance between N incorporation and removal. Indeed, at this temperature, NO decomposes partially into N<sub>2</sub> and O<sub>2</sub>. While 1175 °C is required to enable NO diffusion to the interface and subsequent nitridation, the presence of oxygen limits its effect as interfacial nitrogen is unstable against the slow re-oxidation occurring in parallel [37]. Moreover, additional defect formation can also result from the presence of the excess oxygen.

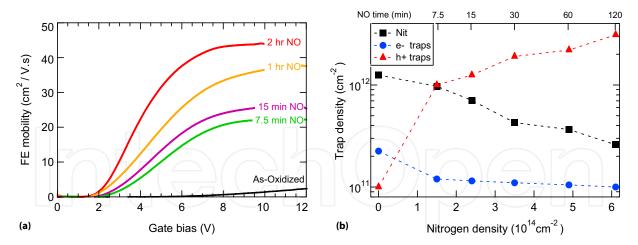

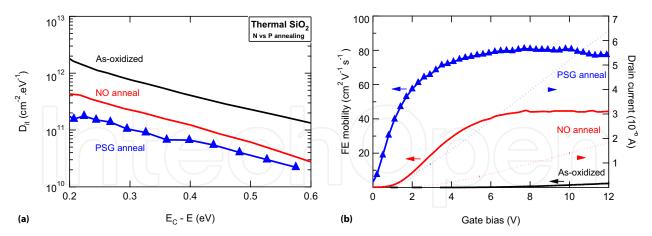

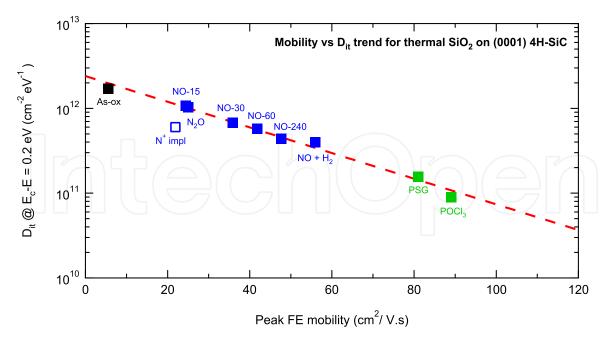

Progressive reduction of the  $D_{it}$  across the 4H-SiC band gap corresponding to the tailored introduction of nitrogen has been measured in metal-oxide-semiconductor capacitors (MOSCAPs), as shown in Fig. 5(b). The density of states shows a strong correlation to the nitrogen content and is reduced by up to an order of magnitude close to the conduction band edge [82, 106, 108]. The sensitivity of the inversion mobility of electrons to the  $D_{it}$  reduction was studied in lateral field-effect transistors containing different amounts of nitrogen at the SiO<sub>2</sub>/4H-SiC interface. From the results depicted in Figs. 6(a) & 10, the peak field-effect mobility is found to be inversely proportional to the density of charged states, which reveals a Coulomb-scattering-limited transport. It is important to note that this is true even in devices with the lowest  $D_{it}$  so that further defect passivation is projected to increase the mobility from 50 to more than 100 cm<sup>2</sup>/V.s, which cannot be achieved by NO POA alone as nitrogen density becomes saturated. These conclusions are in agreement with separate mobility studies using Hall effect measurements on nitrided samples [13, 114, 125]. Such experiments also reveal that at higher fields, mobility becomes limited by surface-roughness scattering. Although NO POA has been shown to yield smoother interfaces [51], it is not clear what else can be done to further reduce that particular component.

**Figure 5.** (a) SIMS Nitrogen profiles showing progressive accumulation at the  $SiO_2/SiC$  interface with increasing NO annealing time. Adapted from Ref. [106]. (b) Density of interface traps across the 4H-SiC band gap. Longer NO anneals yield lower  $D_{it}$ . Reproduced with permission from Ref. [108]. ©2011 IEEE

**Figure 6.** (a) Field-effect mobility extracted from lateral n-channel MOSFETs on 4H-SiC fabricated using different N doses. Reproduced with permission from Ref. [107]. ©2010 TTP (b) Dependence of integrated interface trap density ( $N_{it}$ ), electron-generated levels, and positive oxide traps, on N content. Reproduced with permission from Ref. [107]. ©2010 TTP

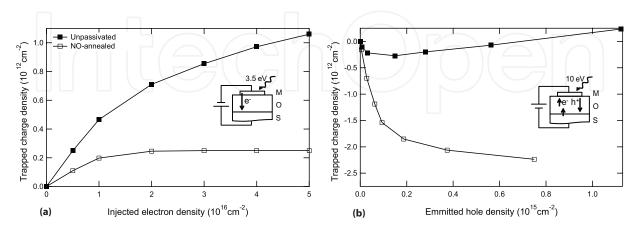

The benefits of nitrogen incorporation also extend to the reliability of SiC devices when it comes to electron injection in the gate oxide, which is inherent to n-channel transistor operation, as the dielectric is exposed to leakage currents and charge tunneling from the inversion layer towards the biased gate contact [31, 32, 52, 73, 132]. While the resulting degradation can take a long time to develop under normal operation, accelerated techniques can be used to study device response to excess carriers penetrating the gate structure. To best simulate actual bias conditions, electrons were injected at low oxide fields (< 2 MV/cm) using a mercury lamp promoting carriers from the negatively-biased gate metal to the conduction band of 4H-SiC in MOSCAPs fabricated using dry oxidation followed by various NO annealing times [103, 106]. As shown in Fig. 7(a), the density of trapped negative charge, extracted from the flatband voltage shift of capacitance-voltage (CV) curves, can be plotted as a function of the integrated gate current, i.e. the injected electron density. If no nitrogen is present at the oxide/semiconductor interface, device characteristics continuously drift towards positive voltages. From the observation of hysteresis behavior of CV curves, this has been correlated to electron-induced acceptor state generation at the interface [5]. However, the presence of even the smallest amount of nitrogen can suppress the degradation, exposing the secondary component of the negative charge, the bulk electron traps in SiO2 [103], Fig. 6(b).

When it comes to positive charge trapping however, the presence of nitrogen proves to be detrimental to device stability [73, 74]. This can be of concern even for n-channel transistors to which a negative gate bias can be applied to ensure that it is OFF in its idle state. Several methods have been used to accelerate hole exposure of the gate oxide such as x-ray irradiation [52], Fowler-Nordheim tunneling, and internal photoemission [104]. Figs. 6(b) & 7(b) show the positive trapped charge as a function of the injected hole carrier density using such a technique with samples containing different amount of nitrogen. There is a clear correlation between nitrogen content and oxide trap density. Because the nitrogen is contained at the interface and the charge is stable against bias reversal, it is attributed to near-interface traps in the SiON layer. ESR experiments have ruled out oxygen vacancies as the main positive trap in the oxide, another indication that atomic configurations involving

nitrogen must be at play [106]. In fact, similar conclusions have been drawn from N-induced negative bias temperature instability (NBTI) on silicon which has been attributed to Si-N bonds [24, 25], which also suggests that the defects must originate from the SiO<sub>2</sub> conversion into a nitride.

From the impact of nitrogen incorporation on  $D_{it}$ , electron traps, and hole traps, summarized in Fig. 6(b), it is possible to paint a picture of what happens at the atomic level. First, it is important to note that although the term "passivation" is often used to describe the effects of nitrogen, the large density introduced by the NO process more likely yields a complete reconfiguration of the interface from SiO/SiC to SiON/SiC. But for simplicity, let us look at the effect of nitrogen on single defects. As mentioned previously, the majority of traps at the thermally grown interface are considered to be single and split carbon interstitials, as well as Si-Si bonds. Unlike hydrogen, nitrogen can reduce the energy of most of these atomic configurations by substituting for threefold-coordinated carbons or by inserting short suboxide bonds [90, 130]. While it can suppress acceptor levels close to the 4H-SiC conduction band edge, the donor nature of nitrogen and its 5 valence electrons can then yield states close to, or even within, the semiconductor valence band [104]. If the resulting atomic configurations are located on the oxide side of the interface, they can therefore act as stable hole traps. Let us take the example of a short Si-Si suboxide bond expected to have an unoccupied state close to the 4H-SiC conduction band. When inserted by NO, it yields a Si-NO-Si bridge and moves the trap level close the valence band. Theory suggests that the nitrogen lone electron pair leads to a partially occupied state that is a favorable hole trap, since giving away an electron makes the atomic configuration reduce its energy by a few eV. As mentioned earlier, nitrogen might not discriminate between defects and stoichiometric oxide sites as it indeed converts SiO to SiON. Therefore, the same configuration could result from N insertion in bridging Si-O-Si, which can create trap levels where there was none before.

In summary, the presence of nitrogen at the oxide/semiconductor interface is beneficial as it reduces  $D_{it}$ , increases mobility, and suppresses electron-induced interface state generation. But on the other hand, re-oxidation during NO POA limits the amount of N that can be inserted, and nitrogen generates a quantity of new traps by bonding in the near-interface

**Figure 7.** Effective trapped charge as a function of (a) injected electron density and (b) emitted hole density by internal photoemission. NO POA suppresses electron-induced interface state generation but increases the amount of hole traps in the oxide. Adapted from Refs. [103, 104]

region of the oxide. Since we have shown that more nitrogen would increase the mobility even further, other nitridation methods could maximize its density while confining it to the interface boundary.

#### 6.2. N<sub>2</sub>O and NH<sub>3</sub>

Ammonia (NH<sub>3</sub>) POA shows benefits as well in terms of  $D_{it}$  reduction close to the conduction band edge of 4H-SiC [39, 53, 133]. However, it yields unnecessary incorporation of nitrogen throughout the oxide, totalling a density  $\sim 100$  times larger than NO POA. This compromises the integrity and reliability of the gate dielectric, as evidenced by the lowering of the breakdown voltage.

Nitrous oxide (N<sub>2</sub>O) oxidation or POA also improves the properties of the oxide/semiconductor interface, but to a lesser extent than NO [12, 37, 70, 76, 81]. This is because it decomposes at high temperature into NO, O<sub>2</sub>, and N<sub>2</sub>. While the resulting NO incorporates nitrogen at the 4H-SiC/SiO<sub>2</sub> interface, the larger fraction of background oxygen mitigates this greatly. Indeed, since incorporated N is unstable against the slow re-oxidation occurring in parallel, N<sub>2</sub>O POA yields about an order of magnitude less nitrogen than pure NO POA at similar process temperature. It reduces D<sub>it</sub> by about a factor of 2 close to E<sub>c</sub> and leads to a peak field-effect mobility of up to  $\approx 25 \text{ cm}^2/\text{V.s}$  in 4H-SiC transistors, as indicated in Fig. 10. However, nitrous oxide is sometimes preferred over NO for safety reasons as it comes with less demanding handling requirements.

#### 6.3. N implants and radicals

Following the improvements induced by NO POA, other methods were developed to introduce N at the SiO<sub>2</sub>/SiC interface. Although they may be more involved, they can yield NO-like properties for oxide-based devices formed on 4H-SiC and bring their own contribution to understanding the role of nitrogen.

One such nitridation technique is implantation. N<sup>+</sup> ions can be inserted in the top semiconductor layer that will subsequently be consumed by thermal oxidation, yielding the presence of nitrogen at the interface. The amount of N atoms can be tuned by implantation dose and energy. Studies have revealed that similarly to NO POA, the higher the nitrogen density at the thermally-formed interface, the lower the  $D_{it}$ , and the higher the field-effect mobility [42, 91, 93]. In fact, Poggi et al. have reported about an order of magnitude reduction of electrically active defects close to the conduction band edge of 4H-SiC and a room temperature field-effect mobility of up to 42 cm<sup>2</sup>/V.s in lateral nFETs fabricated on the (0001) surface [94, 95], Fig. 10. While the progressive increase of  $\mu_{FE}$  with N dose is consistent with the reduction of Coulomb scattering, Hall mobility measurements reveal that in devices with the higher nitrogen content,  $\mu_{Hall}$  decreases with temperature. This implies that, unlike for the NO process, another dominant scattering mechanism appears following high implant doses. This has been attributed to induced damages in SiC and residual N interstitials left within the semiconductor [16]. Also, note that the process temperature can be kept at or below 1100 °C following implantation, to avoid activation that would convert N atoms into donors in SiC. But activation of a minority of dopants in the tail end of the implant can never be ruled out.

Another elegant way to introduce nitrogen is the exposure of thermal oxides to nitrogen radicals [116, 134, 137]. It can be achieved using a remote plasma generating highly reactive  $N^+$  ions. SIMS measurements have shown that, like NO-POA, this results in nitrogen accumulation strictly at the interface between the oxide and the semiconductor. One advantage being that it can potentially occur without re-oxidation, allowing for N maximization. Studies on devices fabricated on the Si-face of 4H-SiC again show that the  $D_{it}$  is reduced proportionally to the amount of incorporated nitrogen, in line with results from NO POA. In fact, similar and even better performance in terms of peak field-effect mobility has been demonstrated using that technique. However, prolonged plasma exposure can also reduce the integrity of the gate oxide, implying that this promising nitridation method still requires optimization.

# 7. Phosphorus

In 2009, about a decade after the introduction of NO annealing, Okamoto  $et\,al.$ , from the Nara Institute of Science and Technology in Japan, proposed another post-oxidation annealing technique that significantly reduces  $D_{it}$  at  $SiO_2/4H$ -SiC interfaces. As mentioned in the previous section, implantation of nitrogen in SiC prior to oxidation has proved to be a beneficial nitridation technique. Hence, Prof. Yano and his group cleverly extended this logic to a screening method for various potential passivating species [87]. This is how phosphorus caught their attention as oxidation of P-implanted SiC also showed a lower density of electrically active defects than as-oxidized un-implanted interfaces. Following this discovery, they implemented a more gentle way to introduce P at the interface in order to avoid ion-induced damages and undesirable doping of the substrate, by flowing gas through a POCl<sub>3</sub> bubbler during a high temperature post-oxidation anneal.

When performed at 1000 °C on SiO<sub>2</sub>, grown on the Si-face of 4H-SiC, POCl<sub>3</sub> POA leads to a  $D_{it}$  below  $10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> close to E<sub>c</sub>, or several times lower than following NO POA [88]. This is reflected in the efficiency of lateral nFETs as the peak value of the field-effect mobility almost doubles compared to NO POA to about 90 cm<sup>2</sup>/V.s. This has been correlated with the presence of phosphorus at the interface. Another proposed method to reach similar mobility values is exposing a thermal oxide to  $P_2O_5$  extracted from a solid phosphosilicate glass (PSG) diffusion source [115]. Device properties following POCl<sub>3</sub> or PSG POA are reported in Figs. 8(a), 8(b) & 10.

Note that from SIMS analysis, it is found that both POCl<sub>3</sub> and PSG POA convert the dielectric into a phosphosilicate by yielding phosphorus throughout the gate. This compromises the reliability of the devices. Recently, forming a thin P-containing interfacial oxide, using POCl<sub>3</sub> and O<sub>2</sub>, followed by dielectric deposition, was shown to reduce trapping by narrowing the phosphorus profile [11].

The benefits of phosphorus at SiO<sub>2</sub>/SiC interfaces represent a milestone for silicon carbide research; not only because of mobility improvements, but also because it shines light on the nature of passivation at the atomic level. Indeed, both N and P are among the group V elements of the periodic table, possessing similar chemistry due to their 5 valence electrons. For example, it has fueled the discussion of the role of sub-surface SiC doping in improving device characteristics [36]. But while the physics of N and P binding at interfaces is still being debated, we are one step closer to a more comprehensive understanding of post-oxidation annealing mechanisms.

**Figure 8.** (a)  $D_{it}$  reduction compared to as-oxidized films using NO POA or a phosphorus source. Adapted from Ref.[115]. (b) Transfer characteristics and extracted field-effect mobilities showing the efficiency of P. Adapted from Ref.[115].

# 8. Deposited oxides

Considering all the efforts necessary to improve the interface, boasting that silicon carbide should be preferred over other wide band gap semiconductors because it can grow a stable thermal oxide may no longer be a valid argument. First, the dominating trap level close to the conduction band edge of 4H-SiC has been associated with slow near-interface defects most likely residing inside SiO<sub>2</sub>, possibly oxygen vacancies. Second, evidence is mounting that the oxidation process itself, which creates C-related defects at the oxide/semiconductor interface, also yields a transition region that extends within SiC, potentially affecting transport properties inside the inversion layer of transistors [10, 17, 19, 117].

In particular, it has been proposed by the group of Prof. Kimoto, from Kyoto University in Japan, that thermal oxidation results in the emission of C atoms from the interface towards the bulk of the semiconductor [61]. Indeed, deep level transient spectroscopy (DLTS) measurements reveal a strong similarity between the effects of thermal oxidation and the ones of C implantation in irradiated samples, as both processes yield the suppression of a level labeled  $Z_{1/2}$  thought to be associated with C vacancies in silicon carbide [69, 123]. A refined oxidation model including the kinetics of emitted atoms was then put forward by Prof. Hijikata's research group at Saitama University in Japan; it successfully models their in-situ ellipsometry observations of thermal oxide growth rate on silicon carbide in both the thin and thick film regimes [59].

Because of these drawbacks of thermal oxidation, it should not come as a surprise that using deposited oxides has yielded encouraging results. For example, chemical vapor deposition of a thin SiN buffer layer on the Si-face of 4H-SiC followed by SiO<sub>2</sub> deposition and N<sub>2</sub>O annealing, has been reported to lower the  $D_{it}$  and increase the field-effect mobility to above  $30~\rm cm^2/V.s$  in lateral n-channel devices [85]. This is an improvement in efficiency compared to gates formed thermally in N<sub>2</sub>O, highlighting the benefits of deposited dielectrics. In that particular case, thinning the SiN layer has also proven to be key as thick oxynitride films resulting from oxygen insertion can possess a high density of positive charges which lower mobility and move the threshold voltage to negative values.

#### 8.1. Alternate dielectrics

The versatility added in device fabrication from using deposited oxides allows to explore a variety of deposition techniques, temperatures, and most importantly the ability to use gate materials other than SiO<sub>2</sub>. It is interesting to note that the reason for considering alternate dielectrics is to move away from thick thermal oxides to reach higher mobility, which is fundamentally different from the evolution of gate fabrication in silicon technology where the motivation comes from scaling and the need for physically thicker oxides at a given capacitance to maintain gate control while minimizing leakage, often at the expense of mobility [56, 131]. This has led to the development and integration of materials which possess a higher dielectric constant, or higher k, that are used in the new generations of Si electronics. Regardless of the dichotomy, it comes at a very opportune time for SiC device research which looks to take advantage of the acquired expertise in deposited gate dielectrics.

Another factor to consider when using high-k oxides on a wide band gap material like SiC however, is the reduced band offsets between the semiconductor and the dielectric. The conduction band offset relative to 4H-SiC for example goes from  $\approx 3$  eV with a SiO<sub>2</sub> gate to  $\approx 1$  eV with a HfO<sub>2</sub> gate [1, 102]. This has implications in terms of leakage current and reliability as such small barriers promote tunneling of carriers into the insulator, even more so that SiC devices are expected to perform at high temperature, which exacerbates the issue [105]. So if HfO<sub>2</sub> is to be considered as a gate material, a thin SiO interlayer is necessary to achieve reasonable leakage. Indeed, Afanas'ev *et al.* have demonstrated that such structures have good interface properties, without the need for nitridation, but that it comes at the expense of a maximum surface field of about 3 MV/cm in the semiconductor to ensure gate integrity, dangerously close to transistor minimum requirements [7]. Ultimately, a balancing act between SiO and HfO<sub>2</sub> thicknesses yields a compromise between performance and reliability [38].

But unlike Si technology, we are not aiming for the highest possible dielectric constant, so we can somewhat move away from this compromise as long as a quality dielectric can be obtained on SiC. A promising candidate in this respect is Al<sub>2</sub>O<sub>3</sub>; it has a dielectric constant close to 9 and a band gap only a few tens of eV narrower than SiO2, yielding a conduction band offset relative to 4H-SiC that is still above 2 eV. Most importantly, it does not possess the same dominating trap level as SiO<sub>2</sub>, so that high electron mobility can be achieved in n-channel devices. Indeed, peak field-effect mobility values measured at room temperature on the Si-face can exceed 100 cm<sup>2</sup>/V.s [60, 79]. A key observation is again that a thin thermal SiO or SiON layer is still required, not so much to reduce gate leakage but to increase efficiency by providing a progressive transition between the semiconductor and the deposited oxide. Since it acts as a passivating layer, it is no surprise that while it is needed, the thinner it is, the better, so that a good interface can be formed while reducing the impact of remote thermal oxide traps on channel transport properties. In practice, the stability of a high-k material on SiO has to be considered carefully to avoid intermixing of the atomic species during subsequent device fabrication steps. To mitigate this, a SiN barrier layer can be used between the thermal oxide and Al<sub>2</sub>O<sub>3</sub>, blocking Al diffusion to the interface [83], or the learning from Si technology can be extended to the use of low-temperature gate-last processing schemes [14].

#### 8.2. Surface conditioning

In the previous Sections, we have shown that while moving away from a thermally-formed gate oxide improves transport properties in 4H-SiC devices, a thin SiO transition layer still brings a much-needed passivated interface. While this is also true for deposited dielectrics on Si, the remarkable difference is that the thinner the thermal oxide is, the better. The next logical step is therefore to avoid thermally-formed SiO entirely, circumventing the negative impact of oxidation-induced defects and near-interface traps. But how can this be done so that there is a clean transition between the SiC surface and the deposited oxide?

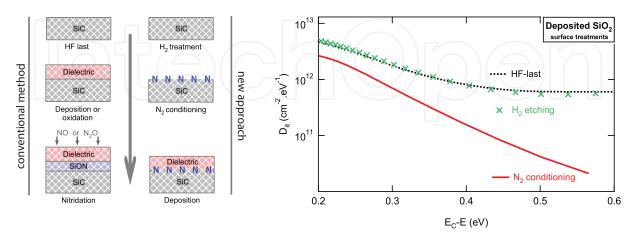

It all comes down to surface preparation of the semiconductor, which cannot simply end with a wet clean since atomic ordering and bonding are paramount. A common surface preparation technique that has been used prior to epitaxial deposition or graphene formation on SiC might provide part of the answer. Hydrogen exposure of the (0001) face of hexagonal SiC to high temperatures (e.g. 1350 °C) etches the surface, smoothing it and yielding atomic reconstruction [18, 101, 120, 126]. However, if a gate dielectric is deposited directly on it, there appears to be no reduction of the D<sub>it</sub> when compared to an HF-last surface, which, as expected, is even worse than a thermally formed interface, at least when looking at SiO<sub>2</sub> deposition on 4H-SiC. But Shirasawa *et al.* observed on 6H-SiC that when high temperature H<sub>2</sub> exposure is directly followed by N<sub>2</sub> exposure at the same temperature, it results in an ordered surface terminated by a monolayer of SiN topped by a monolayer of SiO [118, 119]. These thin films have well defined band gaps, a sign of their electrical integrity, and are estimated to be stable without the existence of dangling bonds at the SiC surface.

Our group at the Central Research Institute of Electronic Industry, located in Yokosuka, Japan, then speculated that such a technique could be applied to 4H-SiC in order to form an ideal seed layer for subsequent deposition [110, 111]. Indeed, this "nitrogen conditioning" process is expected to yield an interface saturated by N atoms which are highly localized within a monolayer, a very promising scenario since we know that maximizing nitrogen content at the interface while limiting its presence in the oxide is key. Moreover, the single oxide layer formed by Si-O-Si bridges bonded to the nitrogen provides the bare minimum silicon oxide, while still offering a clean transition to a deposited layer.

**Figure 9.** Schematic of the nitrogen conditioning technique for deposited oxides vs. conventional nitridation methods. On the right is the corresponding  $D_{it}$  from deposited SiO<sub>2</sub> on surfaces which were subjected to various treatments. Adapted from Refs. [110, 111].

XPS and SIMS measurements confirm that a SiON layer can be formed using nitrogen conditioning on the Si-face of 4H-SiC. More importantly, we find that the nitrogen remains localized at the interface following 900 °C SiO<sub>2</sub> deposition by CVD. N is exclusively bonded to silicon, and no C-O, C-N, or N-O bonds are detected, which is consistent with the structure mentioned above, and atomically cleaner than interfaces resulting from either thermal oxidation or NO POA [77]. Electrical characterization shows that the density of interface states of a deposited oxide is lower than the one of a thermal oxide only when nitrogen conditioning is used, Fig. 9. While this is a notable improvement over as-deposited oxides on a HF-last surface, even better results are expected with alternate dielectrics and low temperature deposition methods such as atomic layer deposition (ALD). Indeed, if the seed layer can be kept intact and a quality oxide can be deposited, this smooth and clean interface should translate into higher inversion mobility because of reduced Coulomb and surface-roughness scattering.

# 9. Summary and conclusions

In order to realize the full potential of SiC-based devices across the voltage range depicted in Fig. 1, the quality of the oxide/semiconductor interface must be improved. Figure 10 summarizes both mobility and  $D_{it}$  from thermal oxide gates following the various annealing processes described in this Chapter. Despite increasingly efficient POA processes from N<sub>2</sub>O, to NO, to phosphorus exposure, the wide band gap and complex oxidation process yield a large density of states that still limits the mobility in even the best oxide-based SiC transistors. While rigourous experiments have led to that conclusion, the trend depicted in Fig. 10 shows a clear dependence between carrier transport and interface states. It suggests that the significant increase in mobility compared to NO POA induced by PSG or POCl<sub>3</sub> annealing is

**Figure 10.** Peak field-effect mobilities extracted from lateral MOSFETs fabricated on (0001) 4H-SiC using thermal oxides with various POAs and the corresponding  $D_{it} @ 0.2$  eV from the conduction band. The plot suggests that Coulomb scattering is the dominant mechanism affecting carrier transport. Further reduction of the interface trap density will keep improving device efficiency. Data gathered from Refs. [12, 88, 94, 106, 108, 115, 130].

still hampered by trap-induced Coulomb scattering. Moreover, it is another indication that if  $D_{it}$  can be decreased further, the mobility could potentially reach values well above 100 cm<sup>2</sup>/V.s.

One can then speculate whether the best properties will be obtained from passivating a defective thermally-formed  $SiO_2/SiC$  interface or using alternate dielectrics like promising  $Al_2O_3$  gate stacks that have demonstrated such high mobilities. Both of these top-down and bottom-up approaches come with their respective challenges going from process integration to device stability and reliability. Thermal oxide POA must optimize the density of passivating species while limiting their presence inside the oxide, indeed  $D_{it}$  is inversely proportional to the amount of nitrogen but the quantity of hole traps increases with it. As for alternate dielectrics, benefits could arise by moving away from pre- or post-deposition oxidation, using instead efficient surface preparation techniques.

If the steady progress made during the past couple decades is any indication, silicon carbide research, development, and technology, have a bright future ahead.

# Acknowledgements

The author would like to thank his friends and colleagues at Vanderbilt University, Auburn University, the Central Research Institute of Electric Power Industry, and IBM, for discussions, challenges, and opportunities that have contributed to the work summarized here.

#### **Author details**

John Rozen\*

\* Address all correspondence to: jrozen@us.ibm.com

IBM T.J. Watson Research Center, Yorktown Heights, NY, USA

#### References

- [1] Afanas'ev, V. V., Bassler, M., Pensl, G., Schulz, M. J. & von Kamienski, E. S. [1996]. Band Offsets and Electronic Structure of SiC/SiO<sub>2</sub> Interfaces, *J. Appl. Phys.* 79: 3108–3114.

- [2] Afanas'ev, V. V., Bassler, M., Pensl, G. & Schulz, M. [1997]. Intrinsic SiC/SiO<sub>2</sub> Interface States, *Phys. Status Solidi A* 162(1): 321–337.

- [3] Afanas'ev, V. V. & Stesmans, A. [1997a]. Interfacial Defects in SiO<sub>2</sub> Revealed by Photon Stimulated Tunneling of Electrons, *Phys. Rev. Lett.* 78(12): 2437–2440.

- [4] Afanas'ev, V. V. & Stesmans, A. [1997b]. Photon-Stimulated Tunnelling of Electrons in SiO<sub>2</sub>: Evidence for a Defect-Assisted Process, *J. Phys.: Condens. Matter* 9(6): L55–L60.

- [5] Afanas'ev, V. V., Stesmans, A., Bassler, M., Pensl, G., Schulz, M. J. & Harris, C. I. [1999]. SiC/SiO<sub>2</sub> Interface-State Generation by Electron Injection, J. Appl. Phys. 85(12): 8292–8298.

- [6] Afanas'ev, V. V., Stesmans, A., Bassler, M., Pensl, G. & Schulz, M. J. [2000]. Shallow Electron Traps at the 4H-SiC/SiO<sub>2</sub> Interface, *Appl. Phys. Lett.* 76(3): 336–338.

- [7] Afanas'ev, V. V., Stesmans, A., Chen, F., Campbell, S. A. & Smith, R. [2003]. HfO<sub>2</sub>-Based Insulating Stacks on 4H-SiC (0001), *Appl. Phys. Lett.* 82(6): 922–924.

- [8] Afanas'ev, V. V., Ciobanu, F., Pensl, G. & Stesmans, A. [2004]. *Silicon Carbide: Recent Major Advances*, Springer, chapter Contributions to the Density of Interface States in SiC MOS Structures, pp. 343–372.

- [9] Agarwal, A., Ryu, S.-H. & Palmour, J. [2004]. Silicon Carbide: Recent Major Advances, Springer, chapter Power MOSFETs in 4H-SiC: Device Design and Technology, pp. 785–811.

- [10] Agarwal, A. & Haney, S. [2008]. Some Critical Materials and Processing Issues in SiC Power Devices, *J. Electron. Mater.* 37(5): 646–654.

- [11] Akagi, T., Yano, H., Hatayama, T. & Fuyuki, T. [2012]. Effect of Interfacial Localization of Phosphorus on Electrical Properties and Reliability of 4H-SiC MOS Devices, *Proceedings of the 9th European Conference on Silicon Carbide and Related Materials*, TuP–61.

- [12] Allerstam, F., Gudjónsson, G., Ólafsson, H. Ö., Sveinbjörnsson, E. Ö., Rödle, T. & Jos, R. [2007]. Comparison Between Oxidation Processes Used to Obtain the High Inversion Channel Mobility in 4H-SiC MOSFETs, *Semicond. Sci. Technol.* 22(4): 307–311.

- [13] Arnold, E. & Alok, D. [2001]. Effect of Interface States on Electron Transport in 4H-SiC Inversion Layers, *IEEE Trans. Electron Dev.* 48(9): 1870–1877.

- [14] Auth, C., Buehler, M., Cappellani, A., Choi, C., Ding, G., Han, W., Joshi, S., McIntyre, B., Prince, M., Ranade, P., Sandford, J. & Thomas, C. [2008]. 45nm High-k+Metal Gate Strain-Enhanced Transistors, *Intel Tech. J.* 12(2): 77–86.

- [15] Baliga, B. J. [2006]. Silicon Carbide Power Devices, World Scientific Publishing Co.

- [16] Basile, A. F., Dhar, S. & Mooney, P. M. [2011]. Electron Trapping in 4H-SiC MOS Capacitors Fabricated by Pre-Oxidation Nitrogen Implantation, *J. Appl. Phys.* 109: 114505.

- [17] Basile, A., Rozen, J., Williams, J. R., Feldman, L. C. & Mooney, P. M. [2011]. Capacitance-Voltage and Deep-Level-Transient Spectroscopy Characterization of Defects near SiO<sub>2</sub>/SiC Interfaces, *J. Appl. Phys.* 109(6): 064514–064514.

- [18] Bernhardt, J., Schardt, J., Starke, U. & Heinz, K. [1999]. Epitaxially Ideal Oxide-Semiconductor Interfaces: Silicate Adlayers on Hexagonal (0001) and (000-1) SiC surfaces, *Appl. Phys. Lett.* 74(8): 1084–1086.

- [19] Biggerstaff, T. L., Reynolds Jr, C. L., Zheleva, T., Lelis, A., Habersat, D., Haney, S., Ryu, S. H., Agarwal, A. & Duscher, G. [2009]. Relationship Between 4H-SiC/SiO<sub>2</sub> Transition Layer Thickness and Mobility, *Appl. Phys. Lett.* 95: 032108.

- [20] Brower, K. L. [1988]. Kinetics of H<sub>2</sub> Passivation of Pb Centers at the (111) Si/SiO<sub>2</sub> Interface, *Phys. Rev. B* 38(14): 9657–9666.

- [21] Brower, K. L. [1990]. Dissociation Kinetics of Hydrogen-Passivated (111) Si/SiO<sub>2</sub> Interface Defects, *Phys. Rev. B* 42(6): 3444–3453.

- [22] Burger, B., Kranzer, D. & Stalter, O. [2008]. Cost Reduction of PV-Inverters with SiC-DMOSFETs, 5th International Conference on Integrated Power Systems, VDE.

- [23] Burger, B. & Kranzer, D. [2009]. Extreme High Efficiency PV-Power Converters, 13th European Conference on Power Electronics and Applications, IEEE.

- [24] Campbell, J. P., Lenahan, P. M., Cochrane, C. J., Krishnan, A. T. & Krishnan, S. [2007]. Atomic-Scale Defects Involved in the Negative Bias Temperature Instability, *IEEE Trans. Dev. Mat. Rel.* 7(4): 540–557.

- [25] Campbell, J. P., Lenahan, P. M., Krishnan, A. T. & Krishnan, S. [2007]. Identification of Atomic-Scale Defect Structure Involved in the Negative Bias Temperature Instability in Plasma-Nitrided Devices, *Appl. Phys. Lett.* 91: 133507.

- [26] Campi, J., Shi, Y., Luo, Y., Yan, F. & Zhao, J. H. [1999]. Study of Interface State Density and Effective Oxide Charge in Post-Metallization Annealed SiO<sub>2</sub>/SiC Structures, *IEEE Trans. Electron Dev.* 46(3): 511–519.

- [27] Cantin, J. L., von Bardeleben, H. J., Shishkin, Y., Ke, Y., Devaty, R. P. & Choyke, W. J. [2004]. Identification of the Carbon Dangling Bond Center at the 4H-SiC/SiO<sub>2</sub> Interface by an EPR Study in Oxidized Porous SiC, *Phys. Rev. Lett.* 92(1): 15502.

- [28] Cantin, J. L. & von Bardeleben, H. J. [2006]. Forming Gas Annealing of the Carbon  $P_{bC}$  Center in Oxidized Porous 3C- and 4H-SiC: an EPR Study, *Mater. Sci. Forum* 527: 1015–1018.

- [29] Carter Jr, C. H., Tsvetkov, V. F., Glass, R. C., Henshall, D., Brady, M., Müller, S. G., Kordina, O., Irvine, K., Edmond, J. A., Kong, H. S., Singh, R., Allen, S. T. & Palmour, J. W. [1999]. Progress in SiC: from Material Growth to Commercial Device Development, Mat. Sci. Eng. B-Solid 61: 1–8.

- [30] Casady, J. B. & Johnson, R. W. [1996]. Status of Silicon Carbide (SiC) as a Wide-Bandgap Semiconductor for High-Temperature Applications: A Review, *Solid State Electron*. 39(10): 1409–1422.

- [31] Chakraborty, S., Lai, P. T. & Kwok, P. C. K. [2002]. MOS Characteristics of NO-grown Oxynitrides on n-type 6H-SiC, *Microelectron. Reliab.* 42: 455–458.

- [32] Chanana, R. K., McDonald, K., Di Ventra, M., Pantelides, S. T., Feldman, L. C., Chung, G. Y., Tin, C. C., Williams, J. R. & Weller, R. A. [2000]. Fowler-Nordheim Hole Tunneling in p-SiC/SiO<sub>2</sub> Structures, *Appl. Phys. Lett.* 77(16): 2560–2562.

- [33] Chang, K. C., Cao, Y., Porter, L. M., Bentley, J., Dhar, S., Feldman, L. C. & Williams, J. R. [2005]. High-Resolution Elemental Profiles of the Silicon Dioxide/4H-Silicon Carbide Interface, *J. Appl. Phys.* 97: 104920.

- [34] Chang, K. C., Nuhfer, N. T., Porter, L. M. & Wahab, Q. [2000]. High-Carbon Concentrations at the Silicon Dioxide-Silicon Carbide Interface Identified by Electron Energy Loss Spectroscopy, *Appl. Phys. Lett.* 77: 2186.

- [35] Chang, K. C., Porter, L. M., Bentley, J., Lu, C. Y. & Cooper, J., J. [2004]. Electrical, Structural, and Chemical Analysis of Silicon Carbide-Based Metal-Oxide-Semiconductor Field-Effect-Transistors, *J. Appl. Phys.* 95: 8252.

- [36] Chatterjee, A., Matocha, K., Tilak, V., Fronheiser, J. & Piao, H. [2010]. Multiscale Modeling and Analysis of the Nitridation Effect of SiC/SiO<sub>2</sub> Interface, *Mater. Sci. Forum* 645: 479–482.

- [37] Chatty, K., Khemka, V., Chow, T. P. & Gutmann, R. J. [1999]. Re-Oxidation Characteristics of Oxynitrides on 3C-and 4H-SiC, J. Electron. Mater. 28(3): 161–166.

- [38] Cheong, K. Y., Moon, J. H., Park, T. J., Kim, J. H., Hwang, C. S., Kim, H. J., Bahng, W. & Kim, N. K. [2007]. Improved Electronic Performance of HfO<sub>2</sub>/SiO<sub>2</sub> Stacking Gate Dielectric on 4H-SiC, *IEEE Trans. Electron Dev.* 54(12): 3409–3413.

- [39] Chung, G., Tin, C. C., Williams, J. R., McDonald, K., Di Ventra, M., Chanana, R. K., Pantelides, S. T., Feldman, L. C. & Weller, R. A. [2000]. Effects of Anneals in Ammonia on the Interface Trap Density near the Band Edges in 4H-Silicon Carbide Metal-Oxide-Semiconductor Capacitors, *Appl. Phys. Lett.* 77(22): 3601–3603.

- [40] Chung, G. Y., Tin, C. C., Williams, J. R., McDonald, K., Ventra, M. D., Pantelides, S. T., Feldman, L. C. & Weller, R. A. [2000]. Effect of Nitric Oxide Annealing on the Interface Trap Densities near the Band Edges in the 4H Polytype of Silicon Carbide, *Appl. Phys. Lett.* 76(13): 1713–1715.

- [41] Chung, G. Y., Tin, C. C., Williams, J. R., McDonald, K., Chanana, R. K., Weller, R. A., Pantelides, S. T. & Feldman, L. C. [2001]. Improved Inversion Channel Mobility for 4H-SiC MOSFETs Following High Temperature Anneals in Nitric Oxide, *IEEE Electron Dev. Lett.* 22(4): 176–178.

- [42] Ciobanu, F., Pensl, G., Afanas' ev, V. & Schöner, A. [2005]. Low Density of Interface States in n-type 4H-SiC MOS Capacitors Achieved by Nitrogen Implantation, *Mater. Sci. Forum* 483: 693–696.

- [43] Costello, J. A. & Tressler, R. E. [1986]. Oxidation Kinetics of Silicon Carbide Crystals and Ceramics: I, In Dry Oxygen, *J. Am. Ceram. Soc.* 69(9): 674–681.

- [44] Deak, P., Knaup, J. M., Hornos, T., Thill, C., Gali, A. & Frauenheim, T. [2007]. The Mechanism of Defect Creation and Passivation at the SiC/SiO<sub>2</sub> Interface, *J. Phys. D. Appl. Phys.* 40: 6242–6253.

- [45] Deal, B. E. & Grove, A. S. [1965]. General Relationship for the Thermal Oxidation of Silicon, J. Appl. Phys. 36: 3770.

- [46] Dhar, S., Song, Y. W., Feldman, L. C., Isaacs-Smith, T., Tin, C. C., Williams, J. R., Chung, G., Nishimura, T., Starodub, D., Gustafsson, T. & Garfunkel, E. [2004]. Effect of Nitric Oxide Annealing on the Interface Trap Density near the Conduction Band Edge of 4H-SiC at the Oxide/(11-20) 4H-SiC Interface, Appl. Phys. Lett. 84(9): 1498–1500.

- [47] Dhar, S. [2005]. Nitrogen and Hydrogen Trap Passivation at the SiO<sub>2</sub>/4H-SiC Interface, PhD thesis, Vanderbilt University, Nashville, TN.

- [48] Di Ventra, M. & Pantelides, S. T. [1999]. Atomic-Scale Mechanisms of Oxygen Precipitation and Thin-Film Oxidation of SiC, Phys. Rev. Lett. 83(8): 1624–1627.

- [49] Dimitriev, V. A. & Spencer, M. G. [1998]. SiC Materials and Devices, Academic Press, chapter SiC Fabrication Technology: Growth and Doping, pp. 21–76.

- [50] Dimitrijev, S., Tanner, P. & Harrison, H. B. [1999]. Slow-Trap Profiling of NO and N<sub>2</sub>O Nitrided Oxides Grown on Si and SiC Substrates, Microelectron. Reliab. 39: 441–449.

- [51] Dimitrijev, S., Harrison, H. B., Tanner, P., Cheong, K. Y. & Han, J. [2004]. Silicon Carbide: Recent Major Advances, Springer, chapter Properties of Nitrided Oxides on SiC, pp. 373–386.

- [52] Dixit, S. K., Dhar, S., Rozen, J., Wang, S., Schrimpf, R. D., Fleetwood, D. M., Pantelides, S. T., Williams, J. R. & Feldman, L. C. [2006]. Total Dose Radiation Response of Nitrided and Non-nitrided SiO<sub>2</sub>/4H-SiC MOS Capacitors, IEEE Trans. Nucl. Sci. 53(6): 3687–36892.

- [53] Dunn, G. J. & Wyatt, P. W. [1989]. Reoxidized Nitrided Oxide for Radiation-Hardened MOS devices, IEEE Trans. Nucl. Sci. 36(6): 2161–2168.

- [54] Ekoue, A., Renault, O., Billon, T., Di Cioccio, L. & Guillot, G. [2003]. Study of the Wet Re-Oxidation Annealing of SiO<sub>2</sub>/4H-SiC (0001) Interface Properties by AR-XPS Measurements, Materials Sci. Forum 433: 555-558.

- [55] Friedrichs, P., Burte, E. P. & Schörner, R. [1996]. Interface Properties of Metal-Oxide-Semiconductor Structures on n-type 6H and 4H-SiC, J. Appl. Phys. 79: 7814.

- [56] Gusev, E. P., Narayanan, V. & Frank, M. M. [2006]. Advanced High-κ Dielectric Stacks with poly-Si and Metal Gates: Recent Progress and Current Challenges, IBM J. Res. Dev. 50(4-5): 387-410.

- [57] Hayton, D. J., Jenkins, T. E., Bailey, P. & Noakes, T. C. Q. [2002]. Optical and Ion-Scattering Study of SiO<sub>2</sub> Layers Thermally Grown on 4H-SiC, Semicond. Sci. Technol. 17(7): L29-L32.

- [58] Helms, C. R. & Poindexter, E. H. [1994]. The Silicon-Silicon Dioxide System: Its Microstructure and Imperfections, Rep. Prog. Phys. 57(8): 791–852.

- [59] Hijikata, Y., Yaguchi, H. & Yoshida, S. [2010]. Model Calculations of SiC Oxide Growth Rate at Various Oxidation Temperatures Based on the Silicon and Carbon Emission Model, Mater. Sci. Forum 645: 809-812.

- [60] Hino, S., Hatayama, T., Kato, J., Tokumitsu, E., Miura, N. & Oomori, T. [2008]. High Channel Mobility 4H-SiC Metal-Oxide-Semiconductor Field-Effect Transistor with Low Temperature Metal-Organic Chemical-Vapor Deposition Grown Al<sub>2</sub>O<sub>3</sub> Gate Insulator, *Appl. Phys. Lett.* 92(18): 183503.

- [61] Hiyoshi, T. & Kimoto, T. [2009]. Elimination of the Major Deep Levels in n- and p-type 4H-SiC by Two-Step Thermal Treatment, *Appl. Phys. Express* 2: 091101.

- [62] Hornetz, B., Michel, H.-J. & Halbritter, J. [1994]. ARXPS Studies of SiO<sub>2</sub>-SiC Interfaces and Oxidation of 6H-SiC Single Crystal Si-(001) and C-(00-1) Surfaces, J. Mater. Res. 9(12): 3088-3094.

- [63] Iida, T., Tomioka, Y., Yoshimoto, K., Midorikawa, M., Tukada, H. & Orihara, M. [2002]. Measurements of the Depth Profile of the Refractive Indices in Oxide Films on SiC by Sprectroscopic Ellipsometry, Jpn. J. Appl. Phys. 41(2): 800–804.

- [64] International Energy Outlook [2011]. Technical report, Energy Information Administration.

- [65] Ioffe Physico-Technical Institute. Electronic Archive of New Semiconductor Materials; Characteristics and Properties. URL: http://www.ioffe.ru/SVA

- [66] Jarrendahl, K. & Davis, R. F. [1998]. SiC Materials and Devices, Academic Press, chapter Materials Properties and Characterization of SiC, pp. 1–20.

- [67] Jernigan, G. G., Stahlbush, R. E. & Saks, N. S. [2000]. Effect of Oxidation and Reoxidation on the Oxide-Substrate Interface of 4H-and 6H-SiC, Appl. Phys. Lett. 77: 1437.

- [68] Kakubari, K., Kuboki, R., Hijikita, Y., Yaguchi, H. & Yoshida, S. [2006]. Time Observation of SiC Oxidation Using an in-situ Ellipsometer, Mater. Sci. Forum 527: 1031-1034.

- [69] Kawahara, K., Suda, J. & Kimoto, T. [2012]. Analytical Model for Reduction of Deep Levels in SiC by Thermal Oxidation, J. Appl. Phys. 111: 053710.

- [70] Kimoto, T., Kanzaki, Y., Noborio, M., Kawano, H. & Matsunami, H. [2005]. Interface Properties of Metal-Oxide-Semiconductor Structures on 4H-SiC(0001) and (11-20) Formed by N<sub>2</sub>O Oxidation, Jpn. J. Appl. Phys. 44: 1213–1218.

- [71] Knaup, J. M., Deák, P., Frauenheim, T., Gali, A., Hajnal, Z. & Choyke, W. J. [2005a]. Theoretical Study of the Mechanism of Dry Oxidation of 4H-SiC, Phys. Rev. *B* 71(23): 235321.

- [72] Knaup, J. M., Deák, P., Frauenheim, T., Gali, A., Hajnal, Z. & Choyke, W. J. [2005b]. Defects in SiO<sub>2</sub> as the Possible Origin of Near Interface Traps in the SiC/SiO<sub>2</sub> System: A Systematic Theoretical Study, Phys. Rev. B 72(11): 115323.

- [73] Krishnaswami, S., Das, M. K., Agarwal, A. K. & Palmour, J. W. [2004]. Reliability of Nitrided Oxides in n-and p-type 4H-SiC MOS Structures, Spring Meeting Proceedings, Vol. 815, MRS, p. J8.4.

- [74] Krishnaswami, S., Ryu, S.-H., Heath, B., Agarwal, A., Palmour, J., Geil, B., Lelis, A. & Scozzie, C. [2006]. A Study on the Reliability and Stability of High Voltage 4H-SiC MOSFET Devices, *Mater. Sci. Forum* 527-529: 1313–1316.

- [75] Lenahan, P. M. & Dressendorfer, P. V. [1984]. Hole Traps and Trivalent Silicon Centers in Metal/Oxide/Silicon Devices, J. Appl. Phys. 55: 3495–3499.

- [76] Li, H., Dimitrijev, S., Harrison, H. B. & Sweatman, D. [1997]. Interfacial Characteristics of N<sub>2</sub>O and NO Nitrided SiO<sub>2</sub> Grown on SiC by Rapid Thermal Processing, Appl. Phys. *Lett.* 70(15): 2028–2030.

- [77] Li, H., Dimitrijev, S., Sweatman, D., Harrison, H. B., Tanner, P. & Feil, B. [1999]. Investigation of Nitric Oxide and Ar Annealed Interfaces by X-Ray Photoelectron Spectroscopy, J. Appl. Phys. 86(8): 4316–4321.

- [78] Liang, M., Choi, J., Ko, P. & Hu, C. [1986]. Inversion-Layer Capacitance and Mobility of Very Thin Gate-Oxide MOSFETs, IEEE Trans. Electron Dev. 33(3): 409–413.

- [79] Lichtenwalner, D., Misra, V., Dhar, S., Ryu, S. & Agarwal, A. [2009]. High-Mobility Enhancement-Mode 4H-SiC Lateral Field-Effect Transistors Utilizing Atomic Layer Deposited Al<sub>2</sub>O<sub>3</sub> Gate Dielectric, Appl. Phys. Lett. 95: 152113.

- [80] Lu, W., Feldman, L. C., Song, Y., Dhar, S., Collins, W. E., Mitchel, W. C. & Williams, J. R. [2004]. Graphitic Features on SiC Surface Following Oxidation and Etching Using Surface Enhanced Raman Spectroscopy, *Appl. Phys. Lett.* 85: 3495.

- [81] McDonald, K., Huang, M. B., Weller, R. A., Feldman, L. C., Williams, J. R., Stedile, F. C., Baumvol, I. J. R. & Radtke, C. [2000]. Comparison of Nitrogen Incorporation in SiO<sub>2</sub>/SiC and SiO<sub>2</sub>/Si Structures, Appl. Phys. Lett. 76(5): 568.

- [82] McDonald, K., Weller, R. A., Pantelides, S. T., Feldman, L. C., Chung, G. Y., Tin, C. C. & Williams, J. R. [2003]. Characterization and Modeling of the Nitrogen Passivation of Interface Traps in SiO<sub>2</sub>/4H-SiC, J. Appl. Phys. 93(5): 2719–2722.

- [83] Moon, J., Yim, J., Seo, H., Lee, D. H., Kim, C., Kim, H., Cheong, K., Bahng, W. & Kim, N. [2010]. Effects of Rapid Thermal Annealing on Al<sub>2</sub>O<sub>3</sub>/SiN Reaction Barrier Layer/Thermal-Nitrided SiO<sub>2</sub> Stacking Gate Dielectrics on n-type 4H-SiC, Appl. Phys. Lett. 96: 122108.

- [84] Muller, R. & Kamins, T. [2003]. Device Electronics for Integrated Circuits, Wiley, New York.

- [85] Noborio, M., Suda, J., Beljakowa, S., Krieger, M. & Kimoto, T. [2009]. 4H-SiC MISFETs with Nitrogen-Containing Insulators, Phys. Status Solidi (A) 206(10): 2374–2390.

- [86] O'Dwyer, J. J. [1973]. The Theory of Electrical Conduction and Breakdown in Solid Dielectrics, Oxford University Press.

- [87] Okamoto, D., Yano, H., Hatayama, T. & Fuyuki, T. [2010]. Systematic Investigation of Interface Properties in 4H-SiC MOS Structures Prepared by over-Oxidation of Ion-Implanted Substrates, Mater. Sci. Forum 645: 495-498.

- [88] Okamoto, D., Yano, H., Hirata, K., Hatayama, T. & Fuyuki, T. [2010]. Improved Inversion Channel Mobility in 4H-SiC MOSFETs on Si Face Utilizing Phosphorus-Doped Gate Oxide, IEEE Electron Dev. Lett. 31(7): 710–712.

- [89] Okawa, T., Fukuyama, R., Hoshino, Y., Nishimura, T. & Kido, Y. [2007]. Kinetics of Oxynitridation of 6H-SiC (11-20) and the Interface Structure Analyzed by Ion Scattering and Photoelectron Spectroscopy, Surf. Sci. 601(3): 706–713.

- [90] Pantelides, S. T., Wang, S., Franceschetti, A., Buczko, R., Di Ventra, M., Raashkeev, S. N., Tsetseris, L., Evans, M. H., Batyrev, I. G., Feldman, L. C., Dhar, S., McDonald, K., Weller, R. A., Schrimpf, R. D., Fleetwood, D. M., Zhou, X. J., Williams, J. R., Tin, C. C., Chung, G. Y., Isaacs-Smith, T., Wang, S. R., Pennycook, S. J., Duscher, G., Van Benthem, K. & Porter, L. M. [2006]. Si/SiO<sub>2</sub> and SiC/SiO<sub>2</sub> Interfaces for MOSFETs: Challenges and Advances, Mater. Sci. Forum 527: 935-948.

- [91] Pensl, G., Beljakowa, S., Frank, T., Gao, K., Speck, F., Seyller, T., Ley, L., Ciobanu, F., Afanas' ev, V., Stesmans, A., Kimoto, T. & Schoner, A. [2008]. Alternative Techniques to Reduce Interface Traps in n-type 4H-SiC MOS Capacitors, Phys. Status Solidi (b) 245(7): 1378-1389.

- [92] Pippel, E., Woltersdorf, J., Ólafsson, H. Ö. & Sveinbjörnsson, E. Ö. [2005]. Interfaces Between 4H-SiC and SiO<sub>2</sub>: Microstructure, Nanochemistry, and Near-Interface Traps, *J. Appl. Phys.* 97(3): 034302.

- [93] Poggi, A., Moscatelli, F., Hijikata, Y., Solmi, S. & Nipoti, R. [2007]. MOS Capacitors Obtained by Wet Oxidation of n-type 4H-SiC pre-Implanted with Nitrogen, Microelectron. Eng. 84(12): 2804-2809.

- [94] Poggi, A., Moscatelli, F., Solmi, S. & Nipoti, R. [2008]. Investigation on the Use of Nitrogen Implantation to Improve the Performance of n-Channel Enhancement 4H-SiC MOSFETs, IEEE Trans. Electron Dev. 55(8): 2021–2028.

- [95] Poggi, A., Moscatelli, F., Solmi, S., Armigliato, A., Belsito, L. & Nipoti, R. [2010]. Effect of Nitrogen Implantation at the SiO<sub>2</sub>/SiC Interface on the Electron Mobility and Free Carrier Density in 4H-SiC Metal-Oxide-Semiconductor Field-Effect-Transistor Channel, J. Appl. Phys. 107: 044506.

- [96] Poindexter, E. H. [1989]. MOS Interface States: Overview and Physicochemical Perspective, Semicond. Sci. Technol. 4(12): 961–969.

- [97] Radtke, C., Baumvol, I. J. R. & Stedile, F. C. [2002]. Effects of Ion Irradiation in the Thermal Oxidation of SiC, Phys. Rev. B 66(15): 155437.

- [98] Ray, E. A., Rozen, J., Dhar, S., Williams, J. R. & Feldman, L. C. [2008]. Pressure Dependence of SiO<sub>2</sub> Growth Kinetics and Electrical Properties on SiC, J. Appl. Phys. 103: 023522.

- [99] Raynaud, C. [2001]. Silica Films on Silicon Carbide: a Review of Electrical Properties and Device Applications, J. Non-Cryst. Solids 280(1-3): 1–31.

- [100] Richmond, J., Hodge, S. & Palmour, J. [2004]. Silicon Carbide Power Applications and Device Roadmap, Power Electronics Europe 7: 17.

- [101] Riedl, C., Coletti, C., Iwasaki, T., Zakharov, A. A. & Starke, U. [2009]. Quasi-Free-Standing Epitaxial Graphene on SiC Obtained by Hydrogen Intercalation, Phys. Rev. Lett. 103(24): 246804.

- [102] Robertson, J. [2000]. Band Offsets of Wide-Band-Gap Oxides and Implications for Future Electronic Devices, J. Vac. Sci. Technol. B 18(3): 1785–1791.

- [103] Rozen, J., Dhar, S., Wang, S., Pantelides, S. T., Afanas'ev, V. V., Williams, J. R. & Feldman, L. C. [2007]. Suppression of Interface State Generation upon Electron Injection in Nitrided Oxides Grown on 4H-SiC, Appl. Phys. Lett. 91: 153503.

- [104] Rozen, J., Dhar, S., Dixit, S. K., Roberts, F. O., Dang, H. L., Wang, S., Pantelides, S. T., Afanas'ev, V. V., Williams, J. R. & Feldman, L. C. [2008]. Increase in Oxide Hole Trap Density Associated with Nitrogen Incorporation at the SiO<sub>2</sub>/SiC Interface, J. Appl. Phys. 103: 124513.

- [105] Rozen, J. [2008]. Electronic Properties and Reliability of the SiO<sub>2</sub>/SiC Interface, PhD thesis, Vanderbilt University, Nashville, TN.

- [106] Rozen, J., Dhar, S., Zvanut, M. E., Williams, J. R. & Feldman, L. C. [2009]. Density of Interface States, Electron Traps, and Hole Traps as a Function of the Nitrogen Density is SiO<sub>2</sub> on SiC, *J. Appl. Phys.* 105(12): 124506.

- [107] Rozen, J., Zhu, X., Ahyi, A. C., Williams, J. R. & Feldman, L. C. [2010]. The Limits of Post Oxidation Annealing in NO, Mater. Sci. Forum 645-648: 693-696.

- [108] Rozen, J., Ayayi, A. C., Zhu, X., Williams, J. R. & Feldman, L. C. [2011]. Scaling Between Channel Mobility and Interface State Density in SiC MOSFETs, IEEE Trans. Electron Dev. 58(11): 3808–3811.

- [109] Rozen, J. [2012]. Energy Efficiency in High Power Electronics: Role and Challenges of Silicon Carbide Interfaces, Human Photonics International Forum, Saitama University.

- [110] Rozen, J., Nagano, M. & Tsuchida, H. [2012a]. Enhancing Interface Quality by Gate Dielectric Deposition on a Nitrogen-Conditioned 4H-SiC Surface, J. Mater. Res. [Online early access]: DOI: 10.1557/jmr.2012.269.

- [111] Rozen, J., Nagano, M. & Tsuchida, H. [2012b]. Improved Deposited Oxide Interfaces from N<sub>2</sub> Conditioning of Bare SiC Surfaces, Mater. Sci. Forum 717: 729–732.

- [112] Rudenko, T. E., Osiyuk, I. N., Tyagulski, I. P., Ólafsson, H. Ö. & Sveinbjörnsson, E. Ö. [2005]. Interface Trap Properties of Thermally Oxidized n-type 4H-SiC and 6H-SiC, *Solid-State Electron.* 49(4): 545–553.

- [113] Rys, A., Singh, N. & Cameron, M. [1995]. Modeling and Characterization of Thermally Oxidized 6H Silicon Carbide, J. Electrochem. Soc. 142: 1318.

- [114] Saks, N. S. [2004]. Silicon Carbide: Recent Major Advances, Springer, chapter Hall Effect Studies of Electron Mobility and Trapping at the SiC/SiO<sub>2</sub> Interface, pp. 387–410.

- [115] Sharma, Y. K., Ahyi, A. C., Issacs-Smith, T., Shen, X., Pantelides, S. T., Zhu, X., Feldman, L. C., Rozen, J. & Williams, J. R. [2012]. Phosphorous Passivation of the SiO<sub>2</sub>/4H-SiC Interface, Solid-State Electron. 68: 103-107.

- [116] Sharma, Y. K. [2012]. Advanced SiO<sub>2</sub>/SiC Interface Passivation, PhD thesis, Auburn University, Auburn, AL.

- [117] Shen, X. & Pantelides, S. T. [2011]. Identification of a Major Cause of Endemically Poor Mobilities in SiC/SiO<sub>2</sub> Structures, Appl. Phys. Lett. 98(5): 053507.

- [118] Shirasawa, T., Hayashi, K., Mizuno, S., Tanaka, S., Nakatsuji, K., Komori, F. & Tochihara, H. [2007]. Epitaxial Silicon Oxynitride Layer on a 6H-SiC (0001) Surface, Phys. Rev. Lett. 98(13): 136105.

- [119] Shirasawa, T., Hayashi, K., Yoshida, H., Mizuno, S., Tanaka, S., Muro, T., Tamenori, Y., Harada, Y., Tokushima, T., Horikawa, Y., Kobatashi, E., Kinoshita, T., Shin, S., Takahashi, T., Ando, Y., Akagi, K., Tsuneyuki, S. & Tochihara, H. [2009]. Atomic-Layer-Resolved Bandgap Structure of an Ultrathin Oxynitride-Silicon Film Epitaxially Grown on 6H-SiC (0001), Phys. Rev. B 79(24): 241301.

- [120] Sieber, N., Seyller, T., Ley, L., James, D., Riley, J., Leckey, R. & Polcik, M. [2003]. Synchrotron X-Ray Photoelectron Spectroscopy Study of Hydrogen-Terminated 6H-SiC (0001) Surfaces, Phys. Rev. B 67(20): 205304.

- [121] Son, N. T., Chen, W. M., Kordina, O., Konstantinov, A. O., Monemar, B., Janzen, E., Hofman, D. M., Volm, D., Drechsler, M. & Meyer, B. K. [1995]. Electron Effective Masses in 4H-SiC, Appl. Phys. Lett. 66(9): 1074–1076.

- [122] Song, Y., Dhar, S., Feldman, L. C., Chung, G. & Williams, J. R. [2004]. Modified Deal Grove Model for the Thermal Oxidation of Silicon Carbide, J. Appl. Phys. 95: 4953.

- [123] Storasta, L., Tsuchida, H., Miyazawa, T. & Ohshima, T. [2008]. Enhanced Annealing of the  $Z_{1/2}$  Defect in 4H-SiC Epilayers, J. Appl. Phys. 103(1): 013705.

- [124] Sze, S. M. [1981]. Semiconductor Devices, Physics and Technology, Wiley, New York.

- [125] Tilak, V., Matocha, K. & Dunne, G. [2007]. Electron-Scattering Mechanisms in Heavily Doped Silicon Carbide MOSFET Inversion Layers, IEEE Trans. Electron Dev. 54(11): 2823-2829.

- [126] Tsuchida, H., Kamata, I. & Izumi, K. [1997]. Infrared Spectroscopy of Hydrides on the 6H-SiC Surface, Appl. Phys. Lett. 70(23): 3072-3074.