## We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

6,900

185,000

200M

Our authors are among the

154

Countries delivered to

**TOP 1%**

12.2%

most cited scientists

Contributors from top 500 universities

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected.

For more information visit www.intechopen.com

# Influence of Ionizing Radiation and Hot Carrier Injection on Metal-Oxide-Semiconductor Transistors

Momčilo Pejović<sup>1</sup>, Predrag Osmokrović<sup>2</sup>, Milica Pejović<sup>1</sup> and Koviljka Stanković<sup>2</sup> <sup>1</sup>University of Niš, Faculty of Electronic Engineering, Niš, <sup>2</sup>University of Belgrade, Faculty of Electrical Engineering, Belgrade, Serbia

#### 1. Introduction

#### General characteristics of MOS components

Favourable characteristics of silicon dioxide (further referred to as oxide or SiO<sub>2</sub>) as an almost irreplaceable dielectric in MOS (Metal-Oxide-Semiconductor) components have contributed to a considerable extent to the great success of the technology of manufacturing integrated circuits during the last decades. However, it has been proved that instabilities of electric charge in the gate oxide and at  $Si-SiO_2$  interface, which inevitably occur due to the influence of ionizing radiation (y and X-radiation, electrons, ions) (IR) and hot carrier injection (which includes Fowler-Nordheim high electric field Stress, avalanche hole injection, avalanche electron injection, and so on (HCI) during the operation of MOS transistors, lead to instabilities of their electric parameters and characteristics and present a serious problem to the reliability of MOS integrated circuits [1-4]. Studying these instabilities, particularly causes and mechanisms responsible for their occurrence, is very significant as it may help the manufacturer define appropriate technological parameters with the aim of increasing their reliability. Considering the rate of development and requirement that the components should be highly reliable, the investigation of their instabilities in normal working conditions is practically impossible. In order to determine, as quickly as possible, mechanisms that cause instabilities, accelerated reliability tests are used and they comprise of the application of strong electric fields (so-called electric stress) in static and impulse modes at room temperature and/or at elevated temperatures. In this context, reliability comprises probability that the component may fulfil its target function during a certain period and under certain conditions, i.e. that it may preserve the electric characteristics and the value of electric parameters under certain exploitation conditions during a certain period. Reliability is defined as a probabilistic category as no failure of the component can be predicted with certainty. Namely, if a group of components manufactured in almost the same conditions is subjected to stress, a smaller number of them will fail earlier (early failure), while a larger number of them will fail later. In order to remove from such a group of components those with the possibility of early failure, a selection procedure is applied to all the components. This procedure consists of a series of

tests the most significant of which is the burn-in test. This test is carried out in two steps: short-term burning (10 – 30 hours) in normal and somewhat intense working conditions, in order to remove components liable to failure due to their manufacturing defects, and sufficiently long burning in tough working conditions in order to remove components with manifested functional failures. A significant fact that should be emphasized in relation to MOS components is that, although the high quality of components guarantees a certain level of their reliability, many defects may remain hidden and manifest during the application thus leading to the degradation of the components and their failure.

In recent times, the development of MOS integrated circuits shows a tendency of increasing the complexity and constantly decreasing dimensions, which comprises a need for increasingly thin gate oxides. In addition, discrete power MOS components have been also developed. At the beginning of their development, it was deemed that they would very soon replace bipolar transistors in power electronics. However, technological processes used in the manufacture of these transistors were more complex in relation to bipolar transistors so that a real progress in power electronics was made when VDMOS (Vertical-Double-Diffused MOS) transistors were developed because the manufacture of them was much simpler. Due to their favourable electric characteristics (great operative speed, low switch-on resistance, high switching voltage, etc.), the VDMOS transistors have found their application in the fields such as automotive industry [5]. Switching characteristics of VDMOS transistors at high frequencies (higher than 100 kHz [6]) have also proved very good owing to which these transistors are applied as switching components for high-frequency sources of supply used in medical electronics, engine control systems, switching sources of supply in telecommunication researches, etc.

In addition to its favourable properties, SiO<sub>2</sub> used in the manufacture of MOS components and integrated circuits has some shortcomings as well. Namely, instabilities of electric charge in the gate oxide and in interface traps, which are inevitable due to the presence of the IR or HCI processes, during the operation of MOS components and MOS integrated circuits, also lead to instabilities of their electric parameters and characteristics. Due to this, instabilities represent one of the most serious problems in relation to a reliable operation of MOS integrated circuits [2, 3] particularly when these components are used in radiation surroundings.

Researches have shown [3] that MOS components are very sensitive to different types of ionizing radiation and that their sensitivity significantly depends on the manufacturing technology. Additionally, some technological processes such as lithography with the use of a ray of electrons, X-rays, and processes in plasma, etc. included in the technological sequence for the production of integrated circuits with the aim of decreasing the dimensions of their components, may be significant sources of defects in the oxide [3].

The attention of today's researches on the impact of the IR and HCI processes on MOS components is directed in two ways. One way comprises the production of components with the highest possible resistance to these types of processes, while the other way leads towards the production of MOS transistors sensitive to IR in order to produce sensors and dosimeters of ionizing radiation [3]. It should be emphasized that the first operating principles of PMOS sensors and dosimeters of ionizing radiation were published as early as 1974 [7]. Unlike the influence of IR and HCI on the reliability of commercial MOS transistors which is the subject of many researches worldwide, PMOS transistors as IR dosimeters are investigated to a much lesser extent.

### 2. Origin and characteristics of defects and electrical charges in oxide and at Si-SiO<sub>2</sub> interface

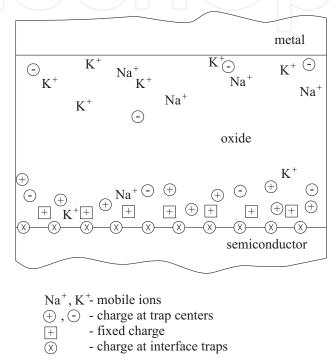

Electrical charges in the gate oxide and at the Si-SiO<sub>2</sub> interface may be divided into four groups as follows [2, 8, 9]: *mobile ions, charges at the traps, fixed centres charges and charges at interface traps*. However, if a division of charges based on their influence on the current-voltage characteristics of MOS transistors is made, only charges in the gate oxide (including mobile ions, charges at the trap centres, and fixed charges) and charges at interface traps may be distinguished. The main classification of charges in the gate oxide and at interface traps of MOS transistors is shown schematically in Figure 1.

Fig. 1. Classification of charge at  $Si - SiO_2$  interface and in the gate oxide of MOS transistor.

Mobile ions in the gate oxide are mainly positive ions of alkali metals such as Na<sup>+</sup> and K<sup>+</sup>, as well as hydrogen ions. They may be incorporated into the oxide during the mere processing of the wafer, or they may reach the oxide, coming from the surrounding surfaces, during the processes of passivation and packing [9, 10]. The existence of these ions in the gate oxide is associated with the fact that during high temperature processes, they easily diffuse into the oxide, from contaminated surfaces. Mobile ions are not distributed uniformly in the oxide, but most of them are located in the semiconductor or metal whereby many more ions are located in the metal as the attractive force towards the metal is much higher than the attractive force towards the semiconductor.

The most important instability mechanism related to electric charges in the gate oxide is the migration of positive ions to the oxide-metal interface and oxide-semiconductor interface under the influence of the positive polarization of the gate and elevated temperature. A series of treatments are taken with the MOS technology in order to minimize these instabilities. Besides the compulsory annealing at high temperature and high level of cleanliness of the technological space and materials used, some modifications in the oxide manufacturing technology have been made in order to minimize instability effects.

Furthermore, a generally accepted procedure for minimizing mobile ions is the introduction of chlorine into the oxide, which is achieved by introducing a certain quantity of HCl or  $\text{Cl}_2$  into the oxidation atmosphere or by passing oxygen through trichloroethylene.

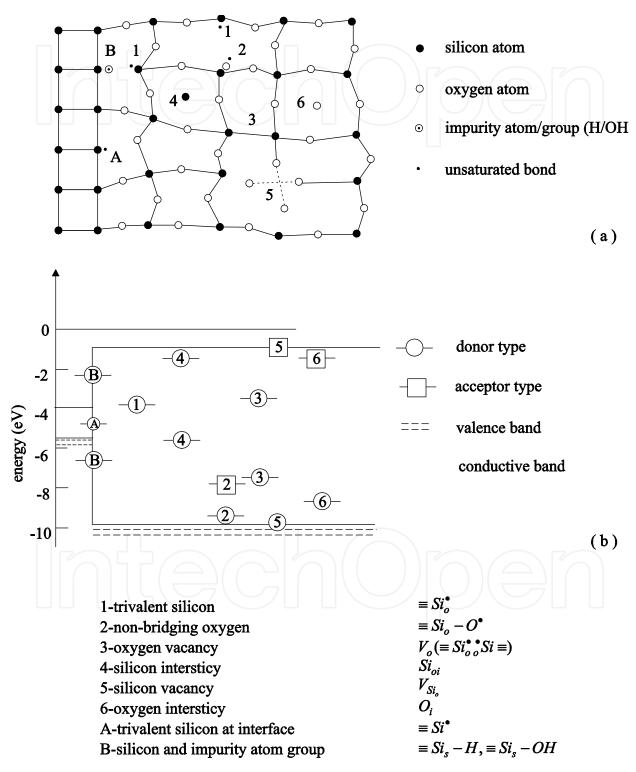

Fig. 2. Most common defects in oxide and at  $Si - SiO_2$  interface: (a) two dimensional model of chemical bonds; (b) energy band model.

Charges at the trap centres are defects and admixed atoms in the oxide which have permissible energy levels in the forbidden zone of the oxide. They are mainly located near the  $Si - SiO_2$  interface, while their number inside the oxide is negligible. Figure 2 shows the model of chemical bonding and diagram of energy zones that illustrate the most significant defects in the oxide and at the  $Si - SiO_2$  interface [4, 11]. Although this is not adequately shown in Figure 2a, it should be taken into account that the  $Si - SiO_2$  interface does not spread through only one atom layer, but rather through several of them. As Figure 2b shows, due to a great difference in the widths of the forbidden zones of silicon (1.12 eV) and oxide (9 eV), discontinuity of energy zones occurs at the interface, and charge carriers encounter a high energy barrier (around 3.2 eV for electrons and 4.7 eV for holes) which in normal conditions prevents any movement of electrons and holes from the semiconductor into the oxide.

The origin of the traps varies. They may be formed both on ≡Si-O- bonds and on defects in the oxide (oxygen vacancies, ≡Si-H and ≡Si-OH bonds, other admixed atoms, etc.). This means that there are different energy levels of the traps depending on the type and quality of the oxide. The traps may be neutral or charged either positively or negatively. During exploitation in certain conditions, they may become electrically charged by capturing electrons or holes, and neutralized by releasing the same, a consequence of which is the instability of the density of effective electric charge captured on them. Therefore, the defects are mainly donor-type defects meaning that they may be positively charged or neutral, so that total electric charge in the oxide is positive. It is important to note that holes may be captured more easily than electrons. Thus the ratio between the number of captured holes and the total number of holes injected into the oxide is approximately one, while, on the average, out of 105 injected electrons only less than one is captured. Nevertheless, instabilities of charges at the traps caused by the electron capture may be equal to instabilities caused by the capture of holes or even more pronounced. The reason for this lies in the fact that electrons may be more easily injected into the oxide, which increases the possibility of their capture.

The most significant mechanisms that lead to the occurrence of free carriers in the oxide may be classified into three groups: a) tunnelling of electrons and holes from the semiconductor or metal into the oxide, 2) injection of hot electrons and holes from the semiconductor into the oxide, and 3) generation of electron-hole pairs in the mere gate oxide which may be a consequence of various factors such as ionizing radiation effects, photo-generation or application of a strong electric field. To the traps in the oxide or to the valence or conductive zone of the oxide, holes from the valence zone of the semiconductor or electrons from the conductive zone of the semiconductor or metal may be tunnelled. The processes of tunnelling electrons or holes from the traps into the conductive or valence zone of the oxide, or directly into the semiconductor are possible, which by analogy leads to instability of the charge density at the traps.

There are four mechanisms related to the injection of hot carriers from the semiconductor into the gate oxide. These are: 1) substrate hot electron injection, 2) channel hot electron injection, 3) drain avalanche hot carrier injection (whereby the injection of holes is preferred when the normal component of the field is directed towards the oxide, while the injection of electrons is preferred when the field is directed towards the semiconductor), and 4) hot electron injection caused by secondary ionization by holes in the substrate. It should be noted that such changes in the density of charges at the traps are not the only form of instability that occur during the exploitation of MOS transistors. Namely, new traps may be

formed which are neutral at the beginning, but which may become charged by capturing electrons and holes.

Fixed charge is located near the  $Si-SiO_2$  interface at distances smaller than 8 nm and its density is constant regardless of changes in the threshold voltage of MOS components. This charge is always positive as it mainly consists of unsaturated bonds of silicon near the Si - SiO<sub>2</sub> interface. Fixed charge depends on the orientation of crystals and it is considerably higher with crystal orientation (111) than with crystal orientation (100). The quantity of fixed charge depends on the Technological conditions of oxidation (atmosphere and temperature). The oxide burn-in in nitrogen or argon at temperatures higher than 600°C decreases the density of fixed charge. This is one of the reasons for which the oxide burn-in has been introduced as a standard procedure in the manufacture of CMOS integrated circuits. It should be emphasized that instability of fixed charges is rarely manifested separately from changes in other charges in the oxide. Instabilities of this type are commonly followed by simultaneous changes in charges at interface traps and oxide traps. This is why in literature fixed charge is mentioned in a much broader sense, although this term also refers to charge in the traps particularly considering the instability of charge in them. Since the origin of fixed charge and traps is frequently the same, it may be assumed that they differ in instability mechanisms. Namely, instability of charge in the traps is a consequence of capturing and releasing free electrons and holes in the oxide, while the instability of fixed charge reflects in its increase as a result of appropriate chemical reactions. One of such reactions is the dissociation of the Si - H bond near the  $Si - SiO_2$  interface. Under the influence of modest negative polarization of the gate and increased temperature, the Si - H group reacts with the Si - O group, whereby a interface trap is formed on the Si atom from the semiconductor, while released hydrogen and oxygen form an OH group which diffuses towards the interface. After the transfer of one electron into the semiconductor, the Si atom in the oxide remains positively charged and this represents the fixed charge. However, it is often impossible to determine a strict boundary between fixed charge and charge at the traps.

Charges at interface traps represent a significant group of electric charges in the oxide. Interface traps are located at the Si - SiO<sub>2</sub> interface the energy levels of which are in the forbidden zone of the semiconductor. These traps develop as a consequence of the semiconductor structure breaking because surface atoms remain with one unsaturated bond. This means that on clean areas of the semiconductor the number of interface traps is approximately equal to the number of surface atoms. However, thermal oxidation reduces the number of interface traps by several orders of magnitude as a great number of silicon atom bonds become saturated by bonding to oxygen atoms. From the aspect of the origin of interface traps, there is a complete analogy between them and fixed charge and thus with the trap centres. The difference is that fixed charge and the trap centres are in the oxide, while interface traps are at the Si - SiO<sub>2</sub> interface and they are easily accessible to free carriers from the semiconductor. The exchange of charge between interface traps and the semiconductor is relatively fast, so that the density of charge in interface traps at a given moment depends on the distribution of the interface traps energy levels and the position of the Fermi level in the semiconductor forbidden zone. Although the process of thermal oxidation considerably decreases the density of interface traps, an additional decrease is needed for a proper operation of MOS components. Today, a procedure commonly used is the oxide burn-in after metallization performed in nitrogen or in a mixture of nitrogen and hydrogen. In this manner, hydrogen is directly introduced in the oxide, or it is formed after the reaction of water and aluminium. This procedure decreases both the density of interface

traps and density of fixed charge and therefore it is applied in almost all standard technologies. Another favourable circumstance is that oxides that increase in the presence of hydrogen chloride also contain, in addition to chlorine that neutralizes mobile ions, hydrogen that decreases the density of interface traps.

The mechanisms of instability of charges in interface traps are a consequence of the formation of new interface traps. Almost all of the described mechanisms may be monitored through the increase in the density of interface traps. The mechanism of fixed charge formation has already been described, whereby interface traps are formed simultaneously. The ion drift towards the Si – SiO<sub>2</sub> interface may lead to an increase in the density of interface traps. It has been proved that the processes of electric charge injection in the oxide most easily form new interface traps that may be achieved by the IR and HCI processes. It is important to point out that owing to the passage of electrons through the Si – SiO<sub>2</sub> interface new interface traps may be formed whereby electrons will not be captured by the traps, which means that the density of charge in them will not change.

As it has already been mentioned, interface traps exchange charge with the semiconductor very rapidly, while this is not the case with the trap centres. On the other hand, a considerable number of defects in the oxide are located in the close vicinity of the interface and they may, like interface traps and regardless of the fact that their microstructure is the same as that of defects deeper in the oxide, exchange charge with silicon. However, unlike real interface traps, these defects are separated from charges in silicon by an energy barrier so that the exchange of charge between them and silicon is carried out through carrier tunnelling whereby the duration of such a process depends to a great extent on the interface distance and the barrier height, and it may range from 1 µs to several years. The long period over which these defects exchange charge with silicon indicates that there is no strict boundary between the effects of charge in the oxide and the effects of interface traps on the electric parameters of MOS transistors. This is why in literature these defects are called boundary traps [12-15]. They may act both as the traps in the oxide and as interface traps. Such nature of the boundary traps may lead to problems in the interpretation of electric measuring results and to difficulties in separating the effects of interface traps and electric charge in the oxide since, depending on measuring conditions (values of the polarization voltage, signal frequency), the boundary traps may behave as interface traps or/and traps in the oxide. By combining appropriate measuring techniques and analysis it is possible to separate the effects of electric charge in the boundary traps [16, 17], which is particularly significant for the characterization of MOS components with a thin gate oxide, where all defects in the oxide are located near the interface and where these defects with their density values are comparable to or even exceed interface traps [14]. In case of thick oxides, as with power MOS transistors, the standard division into the traps in the oxide and interface traps is generally acceptable. In this case, the participation of boundary centres is that at the electric characterization of components will be registered as interface traps or the traps in the oxide, to a great extent depends on the measuring speed and the frequency of the signal that is used during the measurement.

### 3. Classification of the traps according to their effects on electric characteristics

According to the above, it may be concluded that all charges may be divided into two groups: charges in the oxide and charges at interface traps. Changes of charge densities in

the oxide  $\Delta N_{ot}$  and interface traps  $\Delta N_{it}$  are directly responsible for changes of sub-threshold characteristics of MOS transistors during the IR and HCI processes. The participation of a certain type of defects in the values of  $\Delta N_{ot}$  and  $\Delta N_{it}$  primarily depends on their electric effects on the charge carriers in the channel of MOS transistors, as well as on their location in space. If the defects may capture carriers from the channel, due to which the sub-threshold characteristic slope decreases, it is deemed that they behave as interface traps and that value  $\Delta N_{it}$  depends on them. If the defects act on carriers in the channel by attracting or rejecting them with Coulomb forces (depending on the mark of their electric charge), sub-threshold characteristics will be changed due to the change of  $\Delta N_{ot}$ . It should be emphasized that the influence of defects developed in the IR and HCI processes on  $\Delta N_{ot}$  and  $\Delta N_{it}$  is determined primarily by their electric effects and after by their location. This indicates that some defects located at the  $Si - SiO_2$  interface may behave as defects in the oxide (influence  $\Delta N_{ot}$ ), while some defects located in the oxide may behave as interface traps (influence  $\Delta N_{it}$ ) [3, 4, 18]. Although the influence of the location of defects on sub-threshold characteristics is smaller than their electric impact, it should not be neglected. For example, during recording subthreshold characteristics (which is a fast process), only part of these defects may capture carriers from the channel.

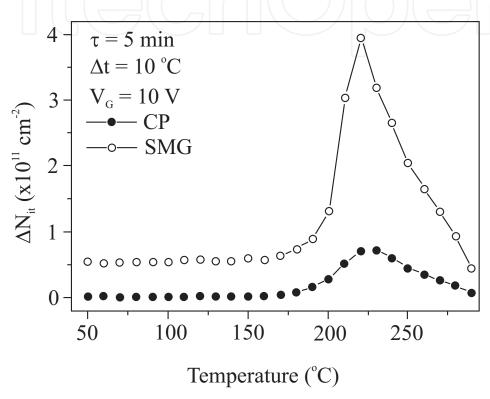

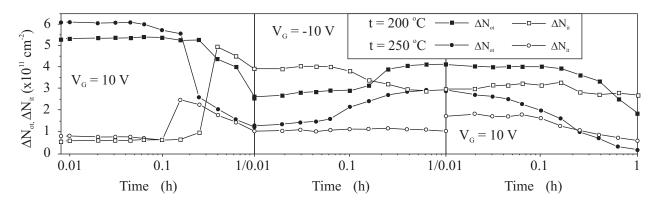

The most common techniques for determining densities of the traps in the oxide and at the Si – SiO<sub>2</sub> interface are subthreshold-midgap (SMG) [19] and charge pumping (CP) techniques [20, 21] (a detailed description of these techniques is given in Section 6). Based on the position of the traps detected by these techniques, a new classification of the centres became necessary as with the use of the SMG technique both  $\Delta N_{ot}$  (SMG) and  $\Delta N_{it}$  (SMG) may be determined, while with the use of the CP technique only  $\Delta N_{it}$  (CP) may be determined. The use of these two techniques is suitable as there is a great difference in effective frequencies (from several Hz for the SMG technique to 1 MHz for the CP technique). As a slower technique, SMG is used for determining two types of centres: fixed traps (FT) with a density of  $\Delta N_{st} \equiv \Delta N_{ot}$  (SMG) and switching traps (ST) with a density of  $\Delta N_{st} \equiv \Delta N_{it}$  (SMG) [22, 23].

Fixed traps (FT) are traps in the oxide that do not exchange charges with Si substrate during recording sub-threshold characteristics by the SMG technique. They are commonly located deeper in the oxide, although they may also be near or at the Si – SiO<sub>2</sub> interface. A significant characteristic of FT is that they may be permanently annealed [22, 23].

Switching traps (ST) may be divided into faster switching traps (FST) and slower switching traps (SST). ST may exchange charges with Si substrate during the measurement. The speed of ST depends on their distance from the Si – SiO<sub>2</sub> interface [24]. This indicates that all defects developed in the IR or HCI processes, which are located near this interface and are capable of exchanging charges with the substrate, become part of ST. Furthermore, some ST may be located deeper in the oxide so that there is not sufficient time for them to exchange, during the measurement, electric charges with carriers in the channel, meaning that  $\Delta N_{ft}$  may contain a certain number of ST. FST which are located at the mere interface and which represent true interface traps (with density  $\Delta N_{it}$ , i.e. meaning that  $\Delta N_{it}$ (CP)  $\equiv \Delta N_{fst}$ ). SST (with density  $\Delta N_{sst}$ ) located in the oxide, near the  $Si - SiO_2$  interface are frequently called slow states (SS) [21], anomalous positive charge (APC) [25], switching oxide traps (SOT) [26] or border traps (BT) [24].

Finally, it should be pointed out that during the measurement by the SMG technique, ST exchange charges during the measurement meaning that in case of an n-channel MOS transistor (NMOS) these centres capture charges from the channel but releases them when

the measurement is finished. It has been shown that ST may be temporarily annealed (compensation process) or permanently annealed (neutralization process), however not during the measurement but by exposing components to elevated temperatures.

### 3.1 Defects in $SiO_2$ and $Si - SiO_2$ interface caused by IR and HCI processes 3.1.1 Formation of electron-hole pairs in $SiO_2$

IR and HCI processes lead to the formation of similar defects in SiO<sub>2</sub> since the electrons play a crucial role in the energy transfer to the oxide in both cases, and the difference is in the electron energy. Namely, the secondary electrons released in the oxide by the gamma photons (IR), and the hot electrons (HCI), and, eventually, the secondary electrons released by the hot electrons play a main role in defect creations. However, it has been shown [22, 27-31] that a difference in electron energy has a significant influence on the created defect types. For instance, the highly energetic secondary electrons (the IR case) produce significantly less negatively charged FT than the low-energy hot electrons (the HCI case).

In the case of IR, the gamma photons interact with the electrons in the  $SiO_2$  molecules mainly via Compton effect, releasing secondary electrons and holes, i.e. gamma photons break  $Si_0$  – O and  $Si_0$  –  $Si_0$  covalent bonds in the oxide [3] (the index  $_0$  is used to denote the oxide). The released electrons (so called "secondary electrons") which are highly energetic, may be recombined by holes at the place of production, or may escape recombination. The secondary electrons that escape recombination with holes travel some distance until they leave the oxide, losing their kinetic energy through the collisions with other secondary electrons or, what is more probable, with the bonded electrons in  $Si_0$  – O and  $Si_0$  –  $Si_0$  covalent bonds in the oxide, releasing more secondary electrons (the latter bond represents an oxygen vacancy).

Each secondary electron, before it has left the oxide or been recombined by the hole, can break a lot of covalent bonds in the oxide producing a lot of new secondary highly energetic electrons, since its energy is usually much higher than an impact ionizing process energy (energy of 18 eV is necessary for the creation of one electron-hole pair [3], i.e. for electron ionization).

In the case of IR processes, gamma radiation breaks both covalent bonds in  $SiO_2$  between oxygen atoms and weak  $\equiv Si_0$  – H and  $\equiv Si_0$  – OH bonds in the oxide. These processes develop in the following reactions [32, 33]

$$O_3 \equiv Si_o - O - Si_o \equiv \xrightarrow{h\nu} \equiv Si_o - O^{\bullet} + e^{-} + h^{+}, \tag{1}$$

$$\equiv \operatorname{Si}_{o} - \operatorname{H} \equiv \xrightarrow{h\nu} \operatorname{Si}_{o}^{\bullet} + \operatorname{H}^{\bullet} + e^{-} + h^{+}, \tag{2}$$

$$\equiv \operatorname{Si}_{o} - \operatorname{OH} \equiv \xrightarrow{h\nu} \operatorname{Si}_{o}^{\bullet} + \operatorname{OH}^{\bullet} + e^{-} + h^{+}. \tag{3}$$

As it can be noted, these reactions lead to the formation of electron-hole pairs (e- - h+). A part of the electrons formed by reactions (1)-(3) break covalent bonds in the oxide (reaction (1)). It is obvious that the secondary electrons play a more important role in bond breaking than highly energetic photons, as a consequence of the difference in their effective masses, i.e. in their effective cross section. The electrons leaving the place of production escape the oxide rapidly (for several picoseconds), but the holes remain in the oxide.

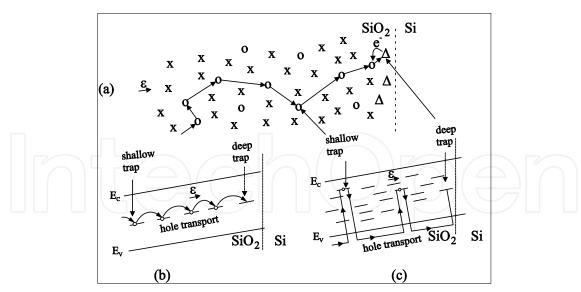

Fig. 3. Space diagram: (a) hole transport through the oxide bulk in the case of positive gate bias. "x" represents unbroken bonds and "o" represents broken bonds (trapped holes at shallow traps), respectively, and " $\Delta$ " represents the hole trap precursors near the interface (precursor of a deep trap). Energetic diagram: the hole transport (b) by tunneling between two localized traps and (c) by the oxide valence band.

Fig. 4. The electron tunneling between adjacent centers: (a) shallow centre and (b) deep centre.

The holes released in the oxide bulk are usually only temporary, but not permanently captured at the place of production, since there are no energetically deeper centres in the oxide bulk. The holes move towards one of the interfaces ( $SiO_2$  – Si or gate- $SiO_2$ ), depending on the oxide electric field direction, where they are trapped at energetically deeper trap hole centres (see Figures 3 and 4). Moreover, even in the zero gate voltage case, the electrical potential due to a work function difference between the gate and substrate is high enough for partial or complete holes moving towards the interface. In addition, some electrons could be trapped at the electron trapping centres of electron capture, but this is not very probable in the IR case [30].

In the case of HCI (e.g. Fowler-Nordheim tunnelling into the gate oxide), the hot electrons, having significantly lower energies than the secondary electrons created by IR, are injected either from the substrate or from the gate. Two cases should be considered: (1) thin oxide  $(d_{ox} \le 10 \text{ nm})$  and (2) thick oxide  $(d_{ox} > 10 \text{ nm})$ . In the former case, the hot electrons, tunnelling into the oxide conduction band, pass the oxide without collisions, since their travel distance is short and, consequently, the probability of the collision with the electrons in the covalent oxide bonds is low [34, 35]. The hot electrons reach the gate, if they are injected from the substrate, or reach the substrate, if they are injected from the gate, where they generate electron-hole pairs. The released (secondary) electrons are attracted by the gate or the substrate electrode, depending on the location of their release, while the generated holes are injected into the oxide.

In the case of thick oxide ( $d_{ox} > 10$  nm), a hot electron passing through the oxide has to collide with the electrons bonded in the oxide, giving a certain amount of energy to them and performing the impact ionization [34, 36, 37]. The hot electrons, whose energies are usually higher than 9 eV representing the SiO<sub>2</sub> band gap, can break the Si<sub>0</sub> – O and Si<sub>0</sub> – Si<sub>0</sub> covalent bonds in the oxide by impact ionization and create electron-hole pairs.

The hot and secondary electrons after certain collisions with each other, and what are more probable, with bonded electrons, escape the oxide rapidly, but the holes transport towards one of the interfaces. The high electric field forces the holes to leave their production places, since there is no significant concentration of energetically deep trapping hole created in the oxide bulk, but these centres exist near the interfaces (see Figure 3). Besides, the hot and secondary electrons can produce more electron-hole pairs before they leave the oxide. In addition, some hot/secondary electrons could be trapped at electron centres creating negative charge, which is a very probable mechanism [31].

#### 3.1.2 The defects created by electrons in the impact ionization process

The hot (HCI) and secondary electrons (IR and HCI) passing through the oxide bulk collide with bonded electrons in the most numerous bond: the non-strained silicon-oxygen bond,  $\equiv Si_0 - O - Si \equiv$  (it could be also represented as  $\equiv Si_0 \cdot O \cdot Si_0 \equiv$ , where  $\cdot \cdot$  represents two electrons making a covalent bond), by reaction [23]

$$\equiv \operatorname{Si}_{0} - \operatorname{O} - \operatorname{Si}_{0} \equiv \xrightarrow{e^{-}} \equiv \operatorname{Si}_{0} - \operatorname{O}^{\bullet} + {}^{+}\operatorname{Si}_{0} \equiv +2e^{-}, \tag{4}$$

$$Si_o - O - Si_o \equiv \xrightarrow{e^-} \equiv Si_o - O^+ + {}^{\bullet}Si_o \equiv +2e^-,$$

(5)

where  $\equiv$ , the indices  $_0$  and  $\cdot$  denote three  $Si_0$  – O bonds  $(O_3 \equiv Si_0$  – O), silicon atom in the oxide and an electron, respectively.

Reaction (4) represents the most probable reaction in the oxide bulk, since these are the most numerous centres. The formed  $\equiv Si_o - O^{+\bullet}Si_o \equiv$  complex is energetically very shallow, representing the temporary hole centre (the trapped holes can easily leave it [11]). The creation of  $\equiv Si_o - O^{+\bullet}Si_o \equiv$  complex, given in reaction (5) is less probable (the • denotes the unpaired electron, i.e. "uncoupled spin").

Nevertheless, the strained silicon-oxygen bond ( $\equiv Si_0 - O - Si_0 \equiv$ ), mainly distributed near the interfaces, can also be easily broken by the passing hot/secondary electrons, usually creating the amphoteric non-bridging-oxygen (NBO) centre  $\equiv Si_0 - O^{\bullet}$ , and positively charged E' centre,  $\equiv Si_0^+$  [38] known as an  $E'_s$  centre [39] (the same process as in reaction (4)). A NBO centre is an amphoteric defect that could be more easily negatively charged than positively by trapping an electron:

$$\equiv \operatorname{Si}_{0} - \operatorname{O}^{\bullet} + e^{-} \to \equiv \operatorname{Si}_{0} - \operatorname{O}^{-}. \tag{6}$$

Obviously, the NBO centre, as an energetically deeper centre, is the main precursor of the negatively charged traps (defect) in the oxide bulk and interface regions.

A hot/secondary electron passing through the oxide can also collide with an electron in the strained oxygen vacancy bond  $\equiv Si_o - Si_o \equiv$ , i.e.  $\equiv Si_o^{\bullet \bullet}Si_o \equiv$ , which is a precursor of an  $E_{\gamma}^{'}$  centre ( $\equiv Si_o^{\bullet \bullet}$ ) [40], breaking this bond and knocking out an electron:

$$\equiv \operatorname{Si}_{0}^{\bullet \bullet} \operatorname{Si}_{0} \equiv \rightarrow \equiv \operatorname{Si}_{0}^{+} + {}^{\bullet} \operatorname{Si}_{0} \equiv +2e^{-}$$

(7)

Moreover, this is a conventional structural model of the  $E_{\gamma}^{'}$  centre: a hole trapped at an oxygen monovacancy ( $\equiv Si_{o}^{+\bullet}Si_{o}\equiv$ ). The oxygen vacancy bonds are mainly distributed in the vicinity of interfaces.

The mentioned reactions could occur anywhere in the oxide: near the interfaces and in the oxide bulk. The trapped charge can be positive (oxide trapped holes) and negative (oxide trapped electrons) and the former is more important, since the holes trapping centres are numerous, including three types ( $E_s$ ,  $E_\gamma$  and NOB centres), compared with one electron capture (NBO). The holes and electrons captured near the Si – SiO<sub>2</sub> interface have the greatest effect on MOSFET characteristics, since they have the strongest influence on the channel carriers.

#### 3.1.3 Hole transport

The holes trapped at  $\equiv Si_0^+$  centres form oxygen vacancies, and strained silicon-oxygen bonds are energetically deep and steady, at which the holes can remain for a longer time period, i.e. their filling with electrons is more difficult in relation to some shallowly captured holes. These centres exist near both interfaces, especially near the Si – SiO<sub>2</sub> interface. The holes created and trapped at the bulk defects (reaction (4)), representing energetically shallow centres, are forced to move towards one of the interface under the electric field, where they are trapped at deeper traps, since there are a lot of oxygen vacancies, as well as a lot of strained silicon-oxygen bonds near the interfaces, grouping all trapped positive charge there. The holes leave the energetically shallow centres in the oxide spontaneously and they are transported to the interface by a hopping process using either shallow centres in the oxide (Figure 3(b); the holes "hop" from one to another centre) or

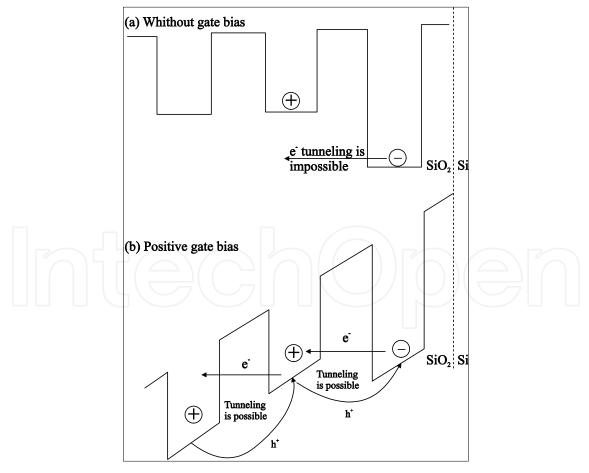

centres in the oxide valence band (Figure 3(c)) [41]. Figure 3 displays the holes transport in the space for the positive gate bias (a) and the energetic diagram for the possible mechanisms of this space process ((b) and (c)).

Figure 4 shows a possible hole (electron) tunnelling mechanism between adjacent centres: a shallow centre and deep centre. Figure 4(a) shows the case without gate bias, for the Si – SiO<sub>2</sub> interface. In this case, the holes, i.e. electrons tunnelling between these centres, are not possible. The holes are factious species representing the electron unoccupied places, and the hole movement is in fact the movement of bonded electrons, however the electron movement is the movement of free electrons.

When the MOS transistor is positively biased (Figure 4(b)), the bonded electron can tunnel from the deep centre to the shallow centre. It represents the hole tunnelling from shallow to deep centres, being permanently trapped at a deep centre. The electron, which is now in the shallow centre, can easily tunnel from this shallow centre to the next adjacent shallow centre, enabling the holes transport towards the interface. The pictures are similar for the negative gate bias [31].

#### 3.1.4 The defects created by the holes

The holes can be created either in the oxide bulk (thick oxide) or in the gate/substrate and injected into the oxide bulk (thin oxide). Moving throughout the oxide, the holes can react with the hydrogen defect precursors ( $\equiv Si_0 - H$  and  $\equiv Si_0 - OH$ ) and create the following defects [42].

$$\equiv \operatorname{Si}_{o} - H + h^{+} \rightarrow \equiv \operatorname{Si}_{o}^{\bullet} + H^{+}, \tag{8}$$

$$\equiv \operatorname{Si}_{o} - \operatorname{H} + \operatorname{h}^{+} \rightarrow \equiv \operatorname{Si}_{o}^{+} + \operatorname{H}^{o}, \tag{9}$$

$$\equiv \operatorname{Si}_{o} - \operatorname{OH} + \operatorname{h}^{+} \rightarrow \equiv \operatorname{Si}_{o} - \operatorname{O}^{\bullet} + \operatorname{H}^{+}, \tag{10}$$

$$\equiv Si_{o} - OH + h^{+} \rightarrow \equiv Si_{o} - O^{+} + H^{o},$$

(11)

The hot and secondary electrons may also interact, in a similar way, with these defect precursors. However, these precursors are not so important for the hot and secondary electrons, since their concentration is significantly lower than the concentration of the precursors representing the non-strained silicon-oxygen bonds. Moreover, it could not be expected that the holes break bonds in the non-strained silicon-oxygen bonds. Because of that, the precursors described in reactions (8-11) are only important for the holes that are transported through the oxide since the hydrogen is relatively weakly bounded and the holes can easily break these bonds. Reactions (8-11) are particularly important for the creation of the interface trap since they produce the hydrogen ion H<sup>+</sup> and hydrogen atom H°, which take part in defect creation at the Si – SiO<sub>2</sub> interface. The existence of these precursors in the oxide and, particularly, at the Si – SO<sub>2</sub> interface is very reasonable, since annealing in the hydrogen ambient is a standard step during the manufacture of numerous MOS devices.

When the holes reach the interface, they can break both the strained oxygen vacancy bonds  $\equiv \text{Si}_0 - \text{Si}_0 \equiv$ , forming  $E_{\nu}$  centres [38]

$$\equiv \operatorname{Si}_{0} - \operatorname{Si}_{0} \equiv +h^{+} \rightarrow \equiv \operatorname{Si}_{0}^{\bullet} + \equiv \operatorname{Si}_{0}^{+} \tag{12}$$

and the strained silicon-oxygen bonds  $\equiv Si_0 - O - Si_0 \equiv$ , creating the amphoteric NBO centres  $\equiv Si_0 - O^{\bullet}$  and  $E_s^{'}$  ( $\equiv Si_0^{+}$ ) centres:

$$\equiv Si_{o} - O - Si_{o} \equiv +h^{+} \rightarrow Si_{o} - O^{\bullet} \equiv Si_{o}^{+}$$

(13)

It could be assumed that the strained Si – O bonds,  $\equiv$  Si<sub>0</sub> – O – Si<sub>0</sub>  $\equiv$  and oxygen vacancy,  $\equiv$  Si<sub>0</sub> – Si<sub>0</sub>  $\equiv$ , represent the main defect precursors in the oxide bulk and at the interfaces. However, these precursors exist mainly near the interface. It should be noted that  $E_{\gamma}^{'}$ ,  $E_{s}^{'}$  (reactions (12) and (13)) and NBO centre (reaction (13)) represent energetically deeper hole and electron trapping centres, respectively. The energetic levels of the defects created after the holes at  $E_{\gamma}^{'}$  and  $E_{s}^{'}$  centres and electrons at NBO centre, respectively, have been trapped, can be various. In the chemical sense same defects show different behaviours depending on the whole bond structure: the angles and distances between the surrounding atoms. It could be assumed that these defects represent fixed traps (FT) and slow switching traps (SST) [29, 30]. They can be positively and negatively charged, as well as neutral. In the literature, there are many controversies about the oxide defects types induced by the IR and HCI processes and there are different names for the same or similar defects (see [23] for more details).

#### 3.1.5 Gate oxide/substrate (SiO<sub>2</sub> – Si) interface

The defects at the Si - SiO<sub>2</sub> interface, known as the fast switching traps (FST), or true interface traps, represent an amphoteric defect Si<sub>3</sub> = Si<sub>s</sub> a silicon atom = Si<sub>s</sub> at the Si - SiO<sub>2</sub> interface back bonded to three silicon atoms from the substrate = Si<sub>3</sub> and the FST are usually denoted as = Si<sub>s</sub> or Si . They can be directly created by incident photons/hot electrons tunnelling from the substrate or the gate [43, 44], however this amount can be neglected. The direct creation of FST is only emphasized in the case of hot electrons for the positive gate bias applied to thin oxides ( $d_{ox} < 10$  nm), where the electrons, tunnelling in the conduction band of oxide, pass the oxide without any collisions (the probability for collision process is small), accelerating themselves and reaching the interface with energy enough for an interface defect creation. Besides direct creation, the FST are mainly created by trapped holes (h<sup>+</sup> model) [45-48] and by hydrogen released in the oxide (hydrogen-released species model - H-model) [49-51].

The  $h^+$  model proposes that a hole trapped near the interface create FST, suggesting that an electron-hole recombination mechanism is responsible [46]. Namely, when holes are trapped near the interface and electrons are subsequently injected from the substrate, recombination occurs. The interface trap may be formed from the energy released by this electron-hole recombination. It was supposed [23] that FST can be created by the reaction:

$$\equiv Si_o^+ + e^+ + \equiv Si_s - Si_o^- + \equiv Si_o^- + \equiv Si_o^- + \equiv Si_o^-. \tag{14}$$

The main shortcoming of the h<sup>+</sup> model is its impossibility in explaining the delayed creation of FST [51]. However, this fact cannot completely disqualify this model, and we can suppose that part of interface traps are created by it.

The H model proposes that H<sup>+</sup> ions, released in the oxide by trapped holes (reactions (8) and (10)), drift towards the Si - SiO<sub>2</sub> interface under the positive electric field. When an H<sup>+</sup> ion arrives at the interface, it picks up an electron from the substrate, becoming a highly reactive hydrogen atom H° [52]:

$$H^+ + e^- \rightarrow H^\circ$$

. (15)

Also, according to the H model, the hydrogen atoms  $H^{\circ}$  released in reactions (9) and (11) diffuse towards the  $Si - SiO_2$  interface under the existing concentration gradient. Highly reactive  $H^{\circ}$  atoms react without an energy barrier at the interface producing FST

throughout the following reactions [53-55]: (i) The creation of interface trap  $\operatorname{Si}_{s}^{\bullet}$ , when  $\operatorname{H}^{\circ}$  reacts with an interface trap precursor  $\operatorname{Si}_{s}$  – H [52]

$$\operatorname{Si}_{s} - \operatorname{H} + \operatorname{H}^{o} \to \operatorname{Si}_{o}^{\bullet} + \operatorname{H}_{2}.$$

(16)

or an interface trap precursor Si<sub>s</sub> - OH:

$$Si_s - OH + H^o \rightarrow Si_o^{\bullet} + H_2O$$

. (17)

Many investigations have shown that the  $P_{b_0}$  and  $P_{b_1}$  centres which exist at the (100) interface represent interface traps [56-58]. The  $P_{b_0}$  defect has the following structure:  $Si_s \equiv Si_{s_0}^{\bullet}$ , but the structure of  $P_{b_1}$  defect, here denoted as  $\equiv Si_{s_1}^{\bullet}$ , is not known (the remaining three bonds of the  $\equiv Si_{s_1}^{\bullet}$  defect can be bonded to various species [59]).

(ii) The passivation of the interface traps, when H° reacts with previously formed (fabrication process or IR and HCI processes induced) interface trap [53, 60]

$$\operatorname{Si}_{s}^{\bullet} + \operatorname{H}^{o} \to \operatorname{Si}_{s} - \operatorname{H}.$$

(18)

(iii) Dimerization of hydrogen, when  $H^\circ$  reacts with another  $H^\circ$  also existing near the interface [61, 62]

$$H^{\circ} + H^{\circ} \rightarrow H_2 \tag{19}$$

Reactions (16) and (17) are most probable at the start of the interface trap creation, since both have a large number of  $Si_s$  – H(OH) precursors, and the effective cross sections for reactions (16) and (17) are higher than for reactions (18) and (19) [52].

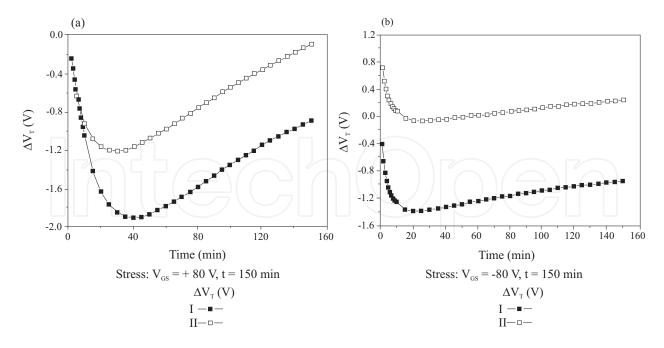

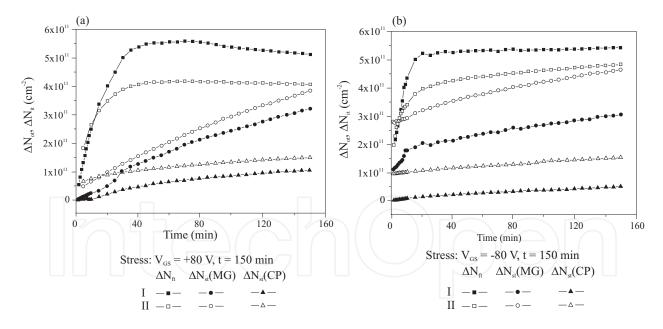

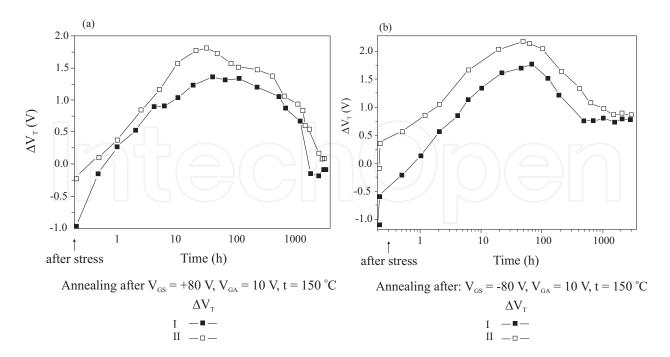

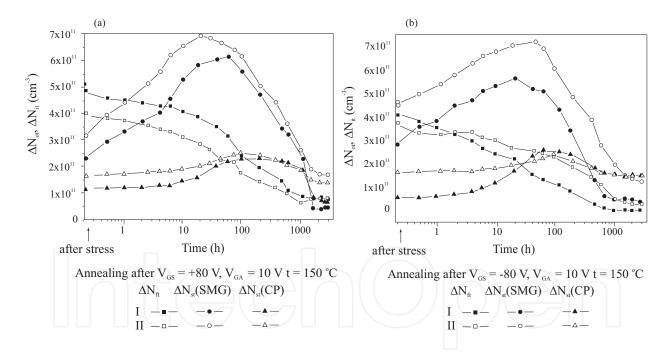

#### 4. Annealing of MOS components after IR and HCI processes

For the electric characteristics of MOS components, changes of charge in the oxide and changes in interface traps are significant both during the IR and HCI processes and after the end of these processes. Some of the mechanisms occurring after the end of the IR and HCI processes remain active, and new mechanisms also develop and last for a longer period of time. The generation of charge in the oxide takes place as long as an IR or HCI process goes on. When these processes end, the density of charge in the oxide starts to decrease, while the generation of interface traps continues and this process may occur for a longer period of

time [61, 63-73]. A process during which positive charge density in the oxide decreases with a simultaneous increase in interface traps density after an IR or HCI process, in which a large quantity of positive charge was incorporated in the oxide, is called annealing. This term is not fully adequate although it is frequently used, as only charge in the oxide is commonly "annealed" while the density of interface traps may increase. MOS components annealing may be performed spontaneously (in air atmosphere, at room temperature, without polarization), or at lowered or elevated temperatures, or in the presence of various intensity and direction electric field.

A number of experimental results [24, 74-80] have shown that the density of interface traps during annealing mainly does not change, while the density of trapped charge in the oxide decreases. Several models are proposed for the trapped charge annealing [75, 77]. It has been observed that during annealing part of trapped charge is permanently burnt-in (neutralized), while the other part may only be compensated, which leads to the effect of "inverse burn-in" (apparent increase in the density of trapped charge during annealing at gate negative polarization), which is attributed, by a group of authors, to the existence of the so-called Switching Oxide Trap (SOT) centres [77, 78]. Another group of authors attribute it to the existence of the so-called Anomalous Positive Charge (APC) centres [24, 79, 80]. Both groups explain inverse burn-in by the exchange of charge with substrate whereby such exchange, in case of SOT, is performed by electron tunnelling as the appropriate levels of these centres lay at the height of the substrate conductive zone [78], while APC are, similarly to interface traps, capable of performing direct exchange with the substrate as their energy levels are at the level of the forbidden zone [24, 79, 80]. Regardless of their different approaches, both groups have practically contributed to establishing the fact that SOT and APC are most probably the same centre, i.e. E' centre that, depending on the conditions of the experiment and measurement may exhibit various properties (burn-in, inverse burn-in or exchange of charges) and may be registered as a interface trap or the so-called boundary centre of capture.

A characteristic of these models of charge burn-in is that they are related to captured charge in the oxide and that they mainly do not exchange charge at interface traps, i.e. that they consider changes in the density of captured charge during annealing separately and independently of changes in the density of interface traps. This may be deemed the main disadvantage of this group of models, particularly because there are numerous experimental results that may be very accurately described by the above-described h+ and H models. It is important to point out that according to h+ and H models, the mechanisms of the formation of defects in the oxide and at the Si - SiO<sub>2</sub> interface take place not only during the IR or HCI processes, but after their cessation as well. This practically means that these two models are more comprehensive and more acceptable for explaining the annealing process than the charge burn-in model. It is important to emphasize here that most experimental results indicate the dominant role of hydrogen and that the H model in many cases gives a real picture of the processes in the oxide and at the Si – SiO<sub>2</sub> interface. Therefore, the processes of the captured charge density decrease and simultaneous increase in the density of interface traps, which take place within a shorter or longer time after the cessation of the IR or HCI processes, may be best described by the H model. However, this model may not describe the annealing processes in case in which the generation of interface traps begins and ends during mere tension so that their density do not increase during the annealing. In addition, none of the models mentioned so far may explain the phenomenon of a decrease in the density of interface traps during the annealing for a long period [81-83] and a latent increase in the density of interface traps [28,84]. Furthermore, none of the mentioned models may explain the phenomenon of an increase and then decrease in the density of interface traps during annealing for a longer period of time [85-88]. On the other hand, the latent generation of interface traps that occurs during annealing is manifested through rapid increase in their density after reaching apparent saturation, and simultaneous rapid decrease in the density of trapped charge, which is characteristic of MOS transistors the oxide of which contains a high concentration of oxygen and bounded hydrogen [87]. It is deemed that it is not the hydrogen originating from the mere oxide that is responsible for the latent increase in the density of interface traps, but rather the hydrogen which is, during the IR or HCI processes, released in the form of molecules in the adjusted layers (polysilicon gate, protective oxide). The hydrogen molecule diffuses towards the gate oxide and through it further towards the oxide-semiconductor interface in the vicinity of which it reacts with a positively charged centre of capture, according to the following reaction:

$$\equiv Si_0^+ + H_2 \to \equiv Si_0 - H + H^+. \tag{20}$$

As it can be seen from the last reaction, the captured charge is neutralized and hydrogen ions are released which then diffuse towards the  $Si - SiO_2$  interface and participate in the formation of a interface trap (reactions (16) and (17) [89]). The late increase in the density of interface traps is attributed to the long-lasting diffusion of hydrogen molecules which is particularly difficult through the polysilicon gate, as well as to a possibility that oxygen vacancies slow down the movement of hydrogen in the oxide [67, 89].

This explains the latent increase in the density of interface traps but cannot explain their decrease that occurs after the latent increase. Owing to this, based on experimental results of the annealing of irradiated power VDMOS transistors, the so-called Hydrogen-Water (H – W) model has been proposed, which can explain the behaviour of the densities of interface traps and captured charge during annealing including both the latent increase and the decrease in the density of interface traps [28, 85, 86]. According to this model, all free hydrogen (present in the oxide before the IR or HCI processes or released during these processes) is utilized for the so-called conventional generation of interface traps that ends with the cessation of the IR or HCI processes and/or in the initial stage of annealing immediately after the cessation of these processes. In the further stage of annealing, for initiating the latent generation of interface traps it is necessary and sufficient that a certain quantity (even a small one) of hydrogen ions appears at the interface. The origin of these ions will be discussed later. When these late ions reach the Si – SiO<sub>2</sub> interface under the influence of the electric field, they takeover electrons from the substrate (reaction 15) and form neutral atoms of hydrogen that may participate in one of the following processes:

(i) formation (depassivation) of interface traps (reaction (16)); (ii) pasivation of interface traps (reaction (18)); and (iii) dimerization (reaction (19)). Reaction (18) is more probable than the other two reactions because the concentration of  $\equiv \mathrm{Si}_s$  – H precursor is higher than the concentration of interface traps ( $\equiv \mathrm{Si}_s^{\bullet}$ ), as well as because the cross section of reactants is larger in this reaction in comparison to the other two, so that the density of interface traps begins to increase. In reactions (16) and (19), hydrogen molecules are released and therefore their concentration at the interface increases (concentration gradient occurs) due to which these molecules diffuse towards the inside of the oxide whereby on their way many of them react on with positively charged traps. The following reaction commonly occurs:

$$\equiv Si_0^+ + H_2 \rightarrow \equiv Si_0 - H + H^+.$$

(21)

Hydrogen ions formed in this reaction drift towards the interface, takeover electrons from the substrate and the processes (i) - (iii) are repeated. In this manner, for further formation of interface traps an additional source of H<sup>+</sup> ions is provided, and at the same time, burn-in of captured charge is performed, in compliance with results according to which the latent increase in the density of interface traps corresponds to the decrease in the density of captured charge.

Water molecules are deemed responsible for the decrease in the density of interface traps that occurs after the latent increase. Water molecules are mainly bounded (physically or chemically) in the thermal and/or protective CVD oxide. During annealing, they may be released (more expressed at higher temperatures) and after that they slowly diffuse towards the  $Si-SiO_2$  interface where they finally react with interface traps according to the following reaction:

$$\equiv \operatorname{Si}_{s}^{\bullet} + \operatorname{H}_{2} O \rightarrow \equiv \operatorname{Si}_{s} - OH + \operatorname{H}^{o}. \tag{22}$$

As it can be seen from the last reaction, the final contribution of water molecules after long annealing is the passivation of interface traps. Namely, in reaction (22) one interface trap is passivated and a neutral hydrogen atom formed in the same reaction may react with (i) another neutral hydrogen atom (reaction (19)) which will not change the result of reaction (22), meaning that one interface trap remains passivated, (ii) with the  $\equiv Si_s^{\bullet}$  defect (reaction (18)) with which one more interface trap is passivated, or (iii) with the  $\equiv$  Si $_{\rm s}$  - H precursor (reaction (16), the only one with which the effect of reaction (22) is annulled). In this manner, the H - W model covers the latent increase and, afterwards, the decrease in the density of interface traps. Based on this model, it may be concluded that a small quantity of any type of hydrogen particles (ions, neutral atoms or molecules) may trigger the latent generation of interface traps. Although the authors of this model [28] mention a possibility that this generation is triggered by hydrogen ions captured in the traps in the oxide, or by hydrogen molecules formed in reaction (22) from the water molecule after its slow diffusion through the oxide, they still believe that for triggering the latent increase in the density of interface traps, hydrogen molecules originating from the protective CVD oxide and/or polysilicon gate are most probably responsible. The cause of their late arrival to the oxide-semiconductor interface may be the reduced speed of diffusion through polysilicon, even through the gate oxide (as a consequence of a decrease in the diffusion constant in the oxide owing to the IR processes), as well as a possibility that hydrogen molecules may have reduced speed by being captured at oxygen vacancies from which they are subsequently released.

### 5. Influence of charges in the oxide and interface traps on MOS transistors parameters

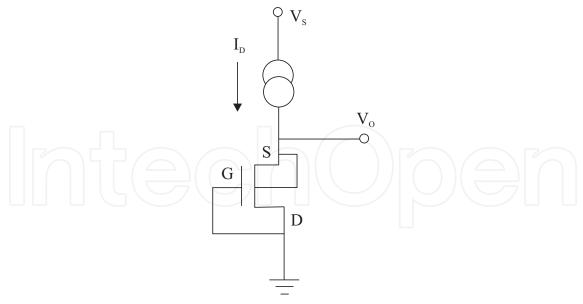

Charges in the oxide, as well as interface traps have a significant influence on the characteristics of MOS transistors. The transfer characteristic of MOS transistors in the saturation region may be described by the following expression [2, 4]:

$$I_D = \beta (V_G - V_T)^2 / 2$$

, (23)

where  $\beta$  is an amplifying factor and may be expressed as

$$\beta = \frac{\mu W C_{ox}}{L} \quad . \tag{24}$$

In expressions (23) and (24),  $I_D$  is drain current,  $V_G$  is voltage at the gate,  $V_T$  is threshold voltage,  $\mu$  is electric mobility in the channel,  $C_{ox} = \varepsilon_{ox}/d_{ox}$  is the capacitance of the gate oxide per area unit ( $\varepsilon_{ox}$  and  $d_{ox}$  represent dielectric constant and oxide thickness, respectively), while W and L are the width and effective length of the channel, respectively. Based on these expressions it may be noticed that charges in the oxide and in interface traps may influence the electric characteristics of MOS transistors only through the influence on threshold voltage and mobility of carriers in the channel. Positive charge in the oxide influences carriers in silicon by its electric field, attracting electrons towards the interface and rejecting holes from it. This leads to a change in threshold voltage which is decreased with NMOS, and increased (by absolute value) with PMOS transistors. At the same time, electrons approaching the interface with NMOS transistors should increase, while holes moving away with PMOS transistors should decrease the dispersal of carriers on the uneven areas of the interface, by which the mobility of carriers would be decreased with NMOS, and increased with PMOS transistors. However, it is deemed that charges in the oxide have a low influence on the carrier mobility and that their impact is not electrostatic but it is rather a consequence of the carrier capturing process [4, 90]. Namely, carrier capture in interface traps will not change the total amount of charge in the channel region, which means that no electric effect is produced. The influence of interface traps may be explained in the following way: interface traps capture a certain number of electrons or holes induced by a change in the surface potential caused by the gate voltage, due to which the formation of a channel requires higher gate voltage comprising an increase in the threshold voltage both with NMOS and PMOS transistors. At the same time, capturing carriers at the interface traps with both types of MOS transistors leads to a decrease in the number of conductive carriers in the channel (to a decrease in current) which is manifested in a decrease in the slope of transfer characteristics, a decrease in the amplifying factor and thus a decrease in the mobility of carriers  $\mu$ . Namely, the greater the density of interface traps, the greater the number of captured carriers in relation to a total number of induced carriers, which is manifested in an apparently greater mobility degradation. Through such a conclusion, the real situation (decreased number of mobile carriers in the channel) is replaced with an apparent one (unchanged number of mobile carriers with reduced mobility), but the effect on the conductivity in the channel (i.e. on the transistor current) remains absolutely the same. Due to this, the use of a simpler model given in expressions (23) and (24), whereby the so-called effective (or apparent) mobility is used instead of the real one, is much more purposeful than complicated consideration of the real situation which would require the knowledge about the accurate function of the interface trap energy levels distribution in the forbidden zone of silicon. This claim is supported by the definition of the mobility of carriers according to which this mobility is not a physical value but only the coefficient of proportionality in the expression for the dependence of drift rate on electric field. Therefore, the value of mobility is not constant but it is rather necessary to adjust it in order to maintain the applicability of Ohm's law to the transport of current in the semiconductor [4]. Owing to this, the concept of effective mobility is common in modelling the effects of various factors on transport processes in the semiconductor, such as doping effects, effects of electric field,

high levels of injection, surface dispersal, crystal orientation, as well as effects of charge in the oxide and effects of interface traps [4, 91-93]. Further in this text, the term mobility will be used, but it will comprise the effective value.

The considerations given so far suggest that with NMOS transistors a decrease in mobility should be expected with an increase in the density of either interface traps or charge in the oxide. Considering the dominant influence of interface traps, a decrease in mobility in general should be also expected for PMOS transistors, even in the case in which the density of charge in the oxide increases somewhat more rapidly than the density of interface traps. In literature, however, there are examples of an increase in mobility, one of which was recorded in a study of PMOS transistors with a polysilicon gate [94]. In the same experiment, PMOS transistors with an aluminium gate were irradiated and an expected decrease in mobility was recorded, while an expected increase in threshold voltage was almost the same with both types of transistors. By additional analysis, a great increase in the density of charge in the oxide was determined, approximately equal with both types of samples while at the same time an increase in the density of interface traps was much greater with the samples with aluminium gates in relation to the samples with polysilicon gates. An increase in mobility with PMOS transistors with polysilicon gates was explained by their high resistance to the formation of interface traps, i.e. by a disproportionately great increase in the density of charge in the oxide in relation to the increase in the density of interface traps during the IR processes. This result is not in accordance with the conclusion that charge in the oxide has low influence on mobility. It may be deemed even controversial as similar results with PMOS transistors with polysilicon gates [95, 96] showed the opposite result, i.e. reduced mobility. However, regardless of the contradiction of these results, it may be concluded that charge in the oxide has significant influence on the mobility of carriers in the channel, although such influence is lower than the influence of interface traps. This is indicated by the results of researches with PMOS dosimetric transistors which show that a considerable increase in the density of charge in the oxide leads to an increase in mobility

Many experimental results have shown that the influence of charge in the oxide and the influence of interface traps on the threshold voltage of MOS transistors may be modelled by the following expression [98]:

$$V_T = V_{T0} \mp \frac{qN_{ot}}{C_{ox}} + \frac{qN_{it}}{C_{ox}}$$

(25)

where  $V_{T0}$  is the threshold voltage of an ideal MOS transistor without any charge in the oxide and without interface traps, while the second and third terms include their influence, whereby the sigh "-" in front of the second term refers to an NMOS transistor, while the sign "+" refers to a PMOS transistor. Therefore, the influence of charge in the oxide  $(qN_{ot})$  is included as voltage drop that creates an electric field on the oxide, i.e.  $qN_{ot}/C_{ox}$ . On the other hand, it is claimed that the influence of interface traps on carriers in the channel reflects in their capture, so a that part of carriers induced in the channel by the gate voltage remain immobile. If, for given gate voltage, the number of captured carriers from the channel per area unit is  $qN_{it}$ , then part of the gate voltage amounting to  $qNit/C_{0X}$  is spent not on the formation of mobile carriers but rather on the formation of captured ones. By this amount the gate voltage required for the formation of a channel is increased (according to

absolute value), which means that the influence of interface traps on threshold voltage is  $qN_{it}/C_{ox}$ .

In order to give consideration to the influence of charge in the oxide and of interface traps on mobility, several models may be used [99-101] which are based on the empirical expression for the dependence of effective mobility on charge in the oxide and the concentration of admixtures in the channel of NMOS transistors given in the paper [102]

$$\mu = \frac{\mu_0}{1 + \alpha N_{ot}},\tag{26}$$

where  $\mu_0$  = 3440 – 164 log  $N_A$  [cm²/(Vs)] is mobility without charge in the oxide ( $N_A$  is the concentration of acceptor impurities expressed in cm³) and  $\alpha_{\rm ot}$  = -1.04 · 10-12 + 1.93 log  $N_A$  [cm²]. Based on later researches [98] it has been shown that the above expression should be modified taking into account the contribution of interface traps as well. Therefore, mobility may be expressed in the following way:

$$\mu = \frac{\mu_0}{1 + \alpha_{it} N_{it} \pm \alpha_{ot} N_{ot}},\tag{27}$$

where coefficients  $\alpha_{it}$  and  $\alpha_{ot}$  depend on technology, and due to greater influence of charge on interface traps  $\alpha_{it} > \alpha_{ot}$ . The sign "+" in front of the third term in the denominator refers to NMOS transistors, while the sign "-" refers to PMOS transistors. This is in accordance with the observation above that charge in the oxide, being almost always positive, may lead to an increase in mobility with PMOS transistors (although this happens rarely owing to the dominant influence of charge on interface traps).

Due to the increase in interface traps, the leakage current of the inversely polarized connection increases as well. Leakage current consists of free electrons and holes generated in the depletion region of the inversely polarized junction, which are transferred through the field into the n-type or p-type semiconductor. The generation of free holes in the presence of interface traps takes place through the transfer of electrons from the valence band to the energy level of interface traps near the Fermi level, while the generation of free electrons takes place through the transfer of electrons from the energy level of interface traps near the Fermi level to the conductive band of the semiconductor. Therefore, electrons pass from the valence band into the conductive band through interface traps. This process leads to the occurrence of leakage current of the inversely polarized junction. The leakage current directly depends on the density of interface traps.

The low-frequency noise of MOS transistors also increases with the increase in the density of interface traps. This noise appears because interface traps capture carriers that move through the channel retaining them for a certain period of time and then emitting them back into the channel. This is a process of accidental nature and it modulates the channel current which may be particularly observed at low frequencies and high densities of interface traps. The avalanche breakdown of the inversely polarized drain-substrate junction is a consequence of the presence of charge in the gate oxide originating from mobile ions, fixed charge, and charge in the traps. The sum of all these charges gives effective charge per area unit which is almost always positive. This charge transforms the drain-substrate p+-n junction in PMOS transistors into the p+-n+ junction meaning that breakdown voltage is reduced. In NMOS transistors, the substrate is of p-type, and charge in the oxide depletes it

leading to a reduction of the field at the drain-substrate n<sup>+</sup>-p junction and thus to an increase in avalanche breakdown voltage.

It is important to emphasize that it is impossible to give an appropriate typical quantitative picture of the described instabilities. There are differences not only in the values of changes in corresponding parameters, but also in the occurring instability mechanisms, and as it has been already mentioned these differences may lead to changes in an observed parameter even in opposite directions. The next important difference is in time dependencies of respective instabilities meaning that even if the same initial instability is manifested with this group of MOS transistors, the instabilities may significantly differ after some time. In addition, time dependences of respective parameters instabilities may have very complex forms as they are frequently defined by simultaneous activities of several mechanisms. Such differences in the behaviour of MOS transistor parameters are conditioned by differences in the manner of the gate oxide formation and by conditions of the component exploitation, and they may lead to qualitatively different forms of instabilities of the MOS transistor parameters.

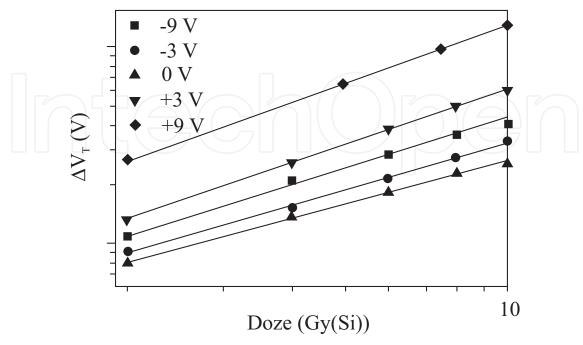

### 6. Techniques of determining electric charge density in oxide and interface traps

Change of electric charge density in gate oxide and interface traps, which occur during IR and HCI processes, are studied through the application of certain techniques. An important role in that procedure is played by changes in electric parameters, primarily threshold voltage and amplification factor (considering that the influence of electric charge in oxide and interface traps on electric characteristics are transferred through them), which are determined on the basis of recorded I-V characteristics.

It is already known that a change in threshold voltage of MOS transistors due to IR and HCI processes can be expressed in the following way:

$$\Delta V_T = \Delta V_{ot} + \Delta V_{it} \,, \tag{28}$$

where  $\Delta V_{ot}$  and  $\Delta V_{it}$  are contributions to the change in threshold voltage due to the electric charge in oxide and in interface traps, respectively. By using the expression (25), the change in surface electric charge density in oxide  $\Delta N_{ot}$  and the change in interface traps density  $\Delta N_{it}$  can be determined as

$$\Delta N_{ot} = \pm \frac{C_{ox}}{q} \Delta V_{ot}, \ \Delta N_{it} = \frac{C_{ox}}{q} \Delta V_{it}, \tag{29}$$

where the signs "+" and "-" refer to p-channel and n-channel MOS transistors, respectively.  $\Delta V_T$  (expression (28)) represents an experimentally determined value of threshold voltage  $\Delta V_T = V_T - V_T(0)$  and the corresponding change in the electric charge densities in oxide  $\Delta N_{ot} = N_{ot} - N_{ot}(0)$  and the interface traps  $\Delta N_{it} = N_{it} - N_{it}(0)$  (expression (29)), where  $V_T(0)$ ,  $N_{ot}(0)$  and  $N_{it}(0)$  are values of corresponding values prior to, and  $V_T$ ,  $N_{ot}$  and  $N_{it}$  after IR or HCI processes.

There are several techniques used to determine electric charge density, and/or to separate the influence of electric charge density in gate oxide and interface traps, and each of these techniques has its own advantages and deficiencies [3,103]. Here we will describe the two

techniques most commonly used today. These are subthreshold midgap (SMG) technique which is used to determine electric charge density in gate oxide and interface traps, and charge pumping (CP) technique which is used only to determine change in interface traps density.

#### 6.1 Subthreshold midgap technique

The subthreshold midgap (SMG) technique is based on the analysis of change in the subthreshold transfer characteristics of MOS transistors [19]. Theoretically, the subthreshold characteristic (dependence of drain current on the gate voltage for the given voltage on drain  $V_{DS}$ ) can be described by the expression [2]:

$$I_{D} = \mu \frac{W}{L} \cdot \frac{N_{A} L_{D} kT}{\sqrt{2}} \left(\frac{n_{i}}{N_{A}}\right)^{2} \exp\left(\frac{q \varphi_{s}}{kT}\right) \cdot \left[1 - \exp\left(-\frac{q V_{DS}}{kT}\right)\right] \cdot \sqrt{\frac{kT}{q \varphi_{s}}}, \tag{30}$$

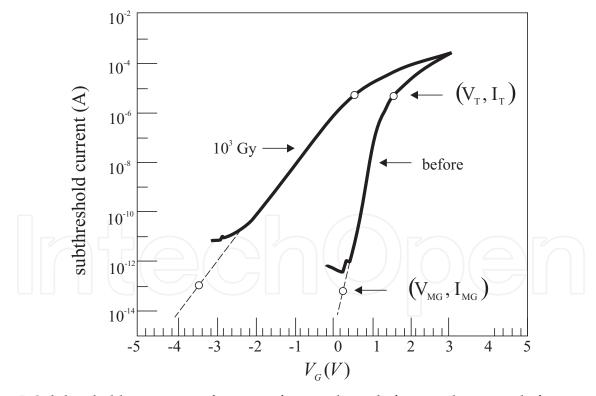

where  $N_A$  is the concentration of impurities in the p-channel area,  $L_D$  is Debye length,  $\varphi_s$  is surface potential which represents the voltage function at the gate [2]. The last expression clearly expresses exponential dependence of drain current on the surface potential, and thereby on the gate voltage as well. The subthreshold characteristics of n-channel MOS transistor prior to and after being subjected to the IR process, as well as the necessary elements to explain the technique are given on the Figure 5 [19].

Fig. 5. Subthreshold current as a function of gate voltage, before irradiation and after gamma radiation dose of 10<sup>3</sup> Gy.

From the viewpoint of subthreshold characteristic, an increase in interface traps density, as already mentioned before, under the influence of IR or HCI processes, is manifested through the change in its slope. Namely, as an increase in gate voltage is followed by capture of

carriers in interface traps, the "response" of surface potential will be decreased, and along with it, the drain current as well, to the changes in gate voltage, and therefore the voltage of subthreshold characteristic will be milder.

In case when Fermi level of semiconductors on the Si - SiO2 interface is located in the middle of the forbidden zone, the total electric charge on interface traps, regardless of the disposition within the forbidden zone of the substrate, is equal to zero. This means that the shift on the voltage axis between two subthreshold characteristics in that case is solely the consequence of change in electric charge density in oxide. The gate voltage in which Fermi level on the  $Si - SiO_2$  interface is located in the middle of the forbidden zone is marked with V<sub>MG</sub> (midgap voltage), and is calculated as abscissa of the point (V<sub>MG</sub>, I<sub>MG</sub>) on the subthreshold characteristics. The above-mentioned point is determined on the basis of its ordinate, i.e. I<sub>MG</sub> current (midgap current) which is calculated on the basis of the expression (30) by replacing appropriate values of surface potential  $\varphi_s = \varphi_F$  and experimentally determined mobility  $\mu$ . As the mobility of carriers depends on several parameters such as temperature, admixture concentrations, degree of component degradation (and thereby also the electric charge density in the oxide and interface traps), it must be determined experimentally for each component and for each radiation dose or duration of HCI process. It is determined from the slope of the curve  $\sqrt{I_D} = f(V_G)$  [19], as the drain current of MOS transistors in saturation is given through the following expression:

$$I_D = \mu \frac{W}{2L} C_{ox} (V_{GS} - V_T)^2 . {31}$$

The  $I_{MG}$  current in  $V_{MG}$  voltage is very small (order of magnitude of picoampere or smaller, depending on the size of transistor), i.e. it is often significantly smaller than the lowest measured level of subthreshold current, determined by the leakage current. For this reason, the point ( $V_{MG}$ ,  $I_{MG}$ ) is located on the extension of the most linear part of subthreshold characteristics marked by the dashed line on Figure 5. Therefore, change in electric charge density in oxide, formed under the influence of IR or HCI process is generated as [19]

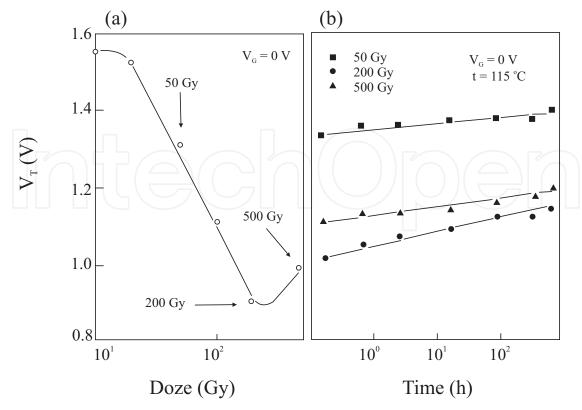

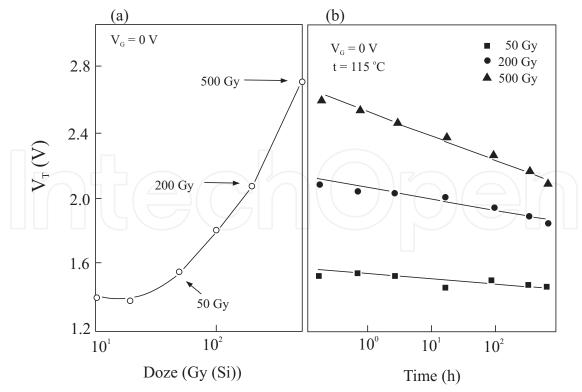

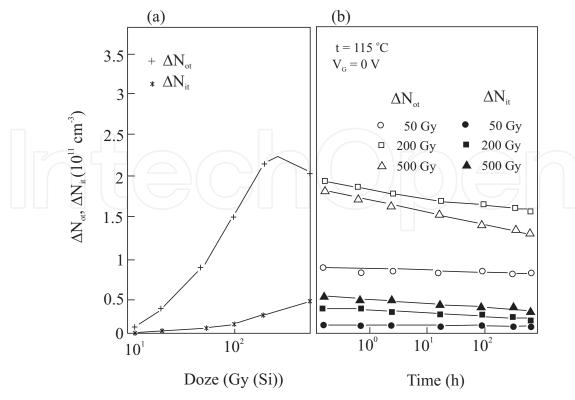

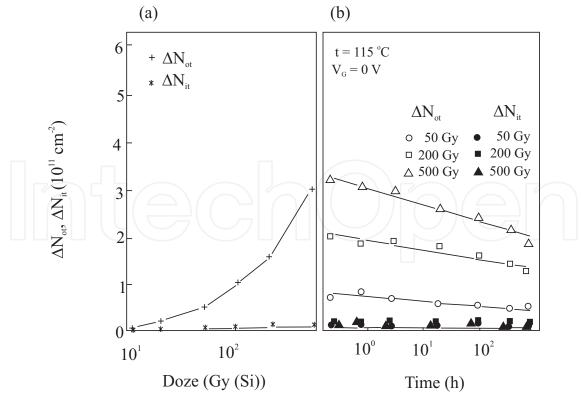

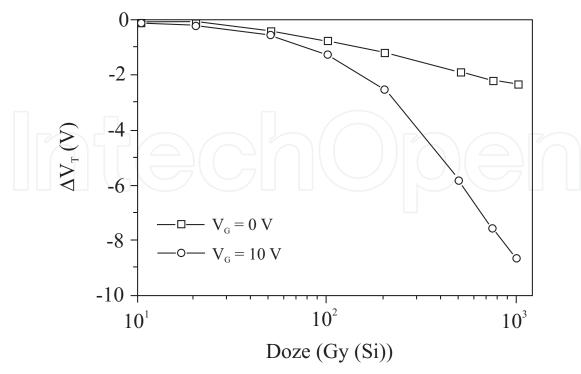

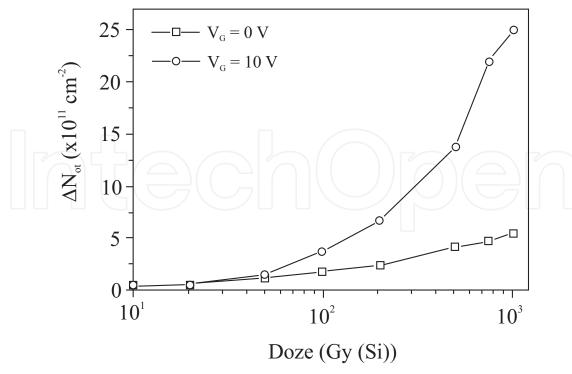

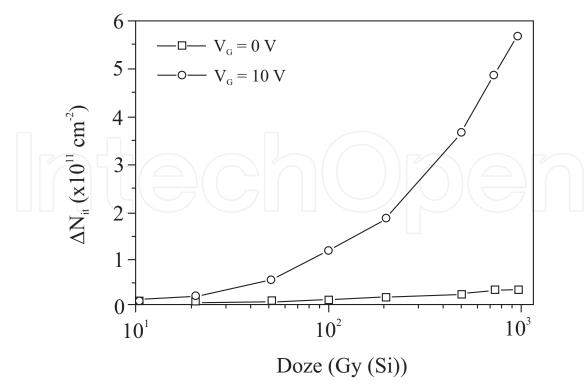

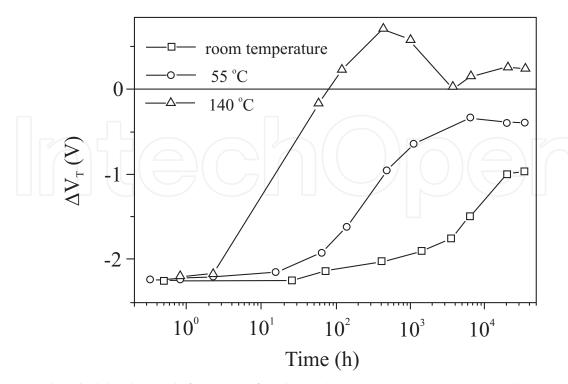

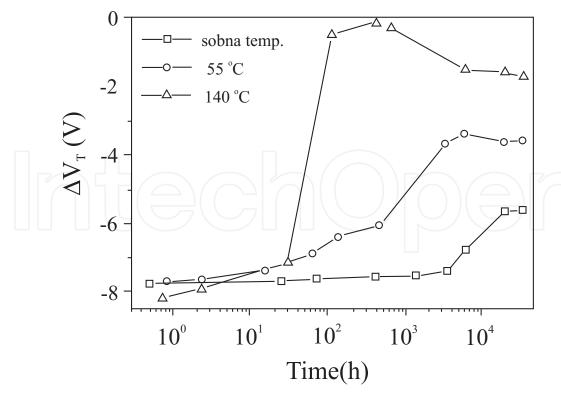

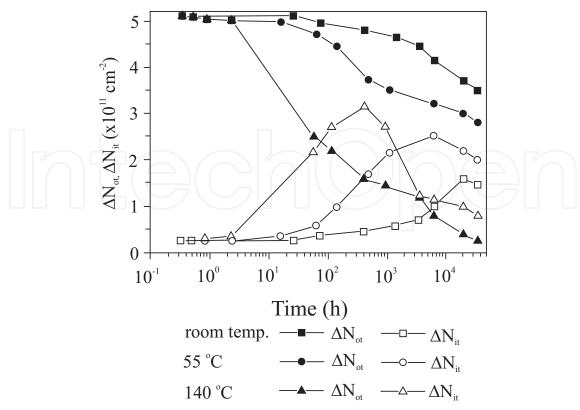

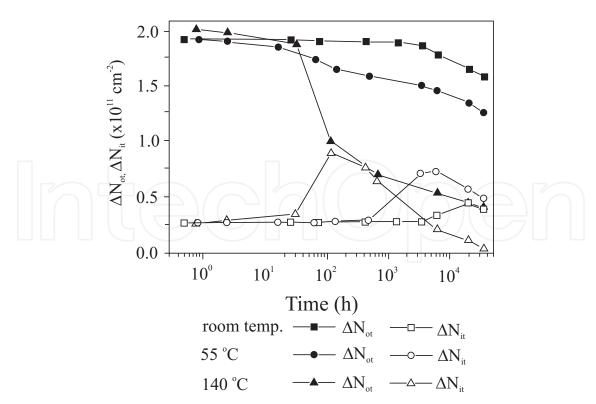

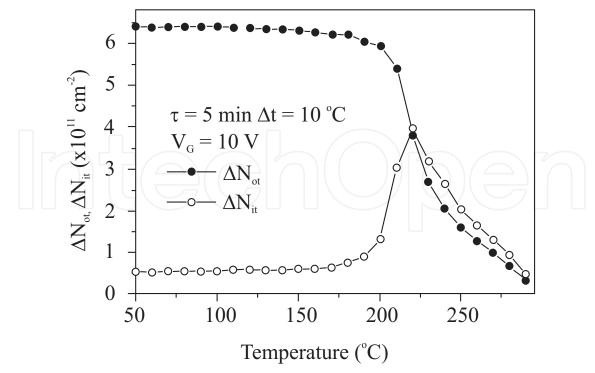

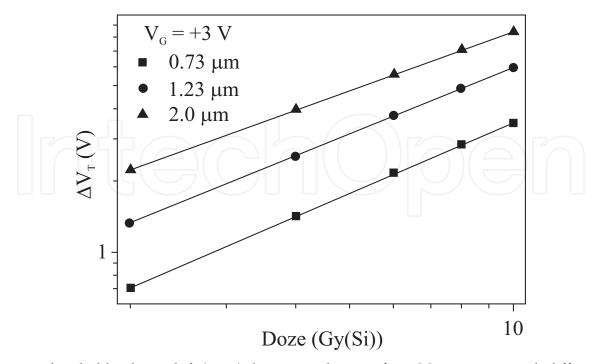

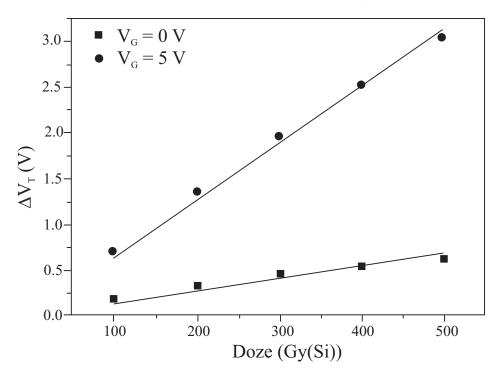

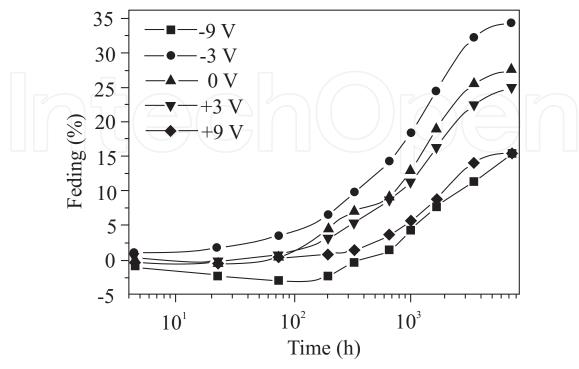

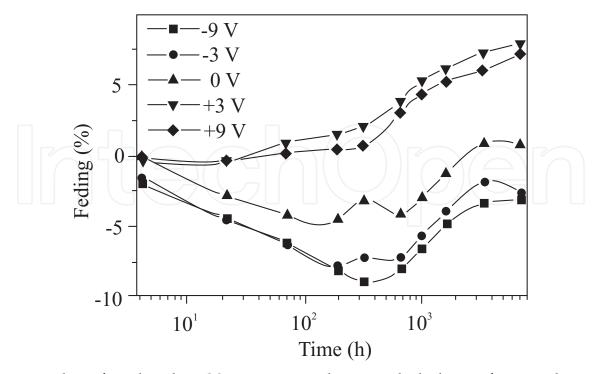

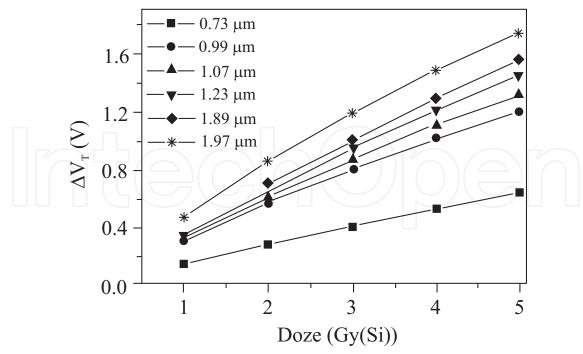

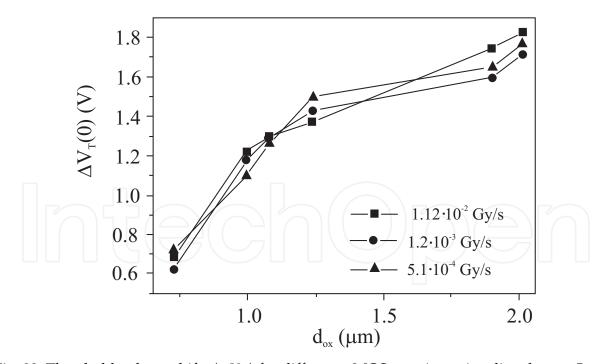

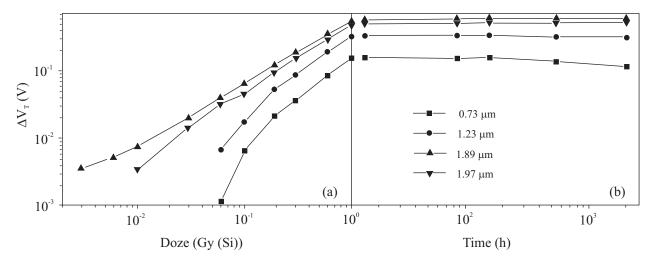

$$\Delta N_{ot} = \frac{C_{ox}}{q} \left( V_{MG}(0) - V_{MG} \right) \tag{32}$$