## We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

6,900

185,000

200M

Our authors are among the

154

Countries delivered to

**TOP 1%**

12.2%

most cited scientists

Contributors from top 500 universities

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected.

For more information visit www.intechopen.com

# Cascaded NPC/H-Bridge Inverter with Simplified Control Strategy and Superior Harmonic Suppression

Tom Wanjekeche, Dan V. Nicolae and Adisa A. Jimoh Tshwane University of Technology South Africa

#### 1. Introduction

In recent decades the electric power systems has suffered significant power quality problems caused by the proliferation of non linear loads, such as arc furnace lighting loads adjustable ac drives etc., which causes a large amount of characteristic harmonics, low power factor and significantly deteriorates the power quality of the distribution system (Benslimane, 2007; Franquelo et. al., 2008; Gupta et al., 2008). The increasing restrictive regulations on power quality have significantly stimulated the development of power quality mitigation equipments. For high power grid connected systems, the classical two level or three level converters topology are insufficient due to the rating limitations imposed by the power semiconductors (Holmes & McGrath, 2001; Koura et al., 2007). Hence considerable attention has been focused on multilevel inverter topologies. This important multilevel technology has found widespread application in medium and high voltage electric drives, renewable energy – grid interface, power conditioning, and power quality application (Lai & Peng, 1996; Peng et al., 1996; Rodriguez et al., 2002; Sinha & Lipo, 1996; Tolbert et al., 1999).

Multilevel converters offer several advantages compared to their conventional counterparts (Manjrekar & Lipo, 1988, 1998, 200; Corzine & Familiant, 2002; Lund et. al., 1999; Sneineh et. al., 2006; Park et. al., 2003; Zhang et al., 2002; Ding et. al., 2004; Duarte et al., 1997; Rojas & Ohnishi, 1997). By synthesizing the AC output terminal voltage from several voltage levels, staircase waveforms can be produced, which in their turn approach the sinusoidal waveform with low harmonic distortion, thus reducing filters requirements. However the several sources on the DC side of the converter make multilevel technology difficult to control by the need to balance the several DC voltages. For the class of multilevel inverter called diode clamped, if a higher output voltage is required one of the viable methods is to increase the number of inverter voltage levels. For Neutral Point Clamped (NPC) inverter voltage can only be increased up to five level beyond which DC voltage balancing becomes impossible. For single Phase H Bridge inverter, an increase in the number levels leads to increase in the number of separate DC sources, thus the proposed hybrid model is developed by combining the NPC and H- bridge topologies (Wu et al., 1999).

A lot of research has been done on single phase H- Bridge inverter where each inverter level generate three different voltage outputs,  $+V_{dc}$ , 0, and  $-V_{dc}$  by connecting the dc source to the ac output using different combinations of the four switches of the Bridge (Peng et al., 1996). There has also been more emphasis on modeling and control of a five level NPC/H-bridge inverter without cascading the bridge (Cheng & Wu, 2007). This fails to address the principle of realizing a general cascaded n- level NPC/H-Bridge. It is on this need of realizing a higher voltage output with simplified control algorithm that this book chapter proposes a simplified control strategy for a cascaded NPC/H-bridge inverter with reduced harmonic content. Because of the modularity of the model only two cascaded cells which gives a 9 level cascaded NPC/H-bridge inverter is considered. The new control strategy is achieved by decomposing the nine level output into four separate and independent threelevel NPC PWM output. By combining the three-level NPC PWM back to back using DC sources and properly phase shifting the modulating wave and carrier a simplified control strategy is achieved with reduced number of components. The control strategy is applied on cascaded NPC/H-bridge inverter that combines features from NPC inverter and cascaded H-Bridge inverter. For higher voltage applications, this structure can be easily extended to an n-level by cascaded NPC/H-Bridge PWM inverters.

The article starts by developing a control algorithm based on novel phase shifted PWM technique on the proposed inverter model. This is done on a two cell of the cascaded model to realize nine level voltage output. A theoretical harmonic analysis of the model with the proposed control algorithm is carried out based on double Fourier principle. Spectral characteristics of the output waveforms for all operating conditions are studied for a five-level and nine-level voltage output. Theoretical results are verified using MATLAB simulation. The results shows that the spectrum can be made to only consist of the multiples of fourth order for a five level and with proper phase shift combination, a multiple of eighth order is achieved for nine level voltage output. The results are compared with those of a conventional multicarrier PWM approach; it is shown that with the proposed phase shifted PWM approach, the inverter exhibits reduced harmonic content are present. Finally the article compares the components count of the the model with the convetional cascaded H-bridge inverter, it is clealry shown that the proposed model requires a lesser number of separate dc sources as compared to conventional cascaded H-bridge inverter.

#### 2. System topology and switching technique

#### 2.1 Main system configuration

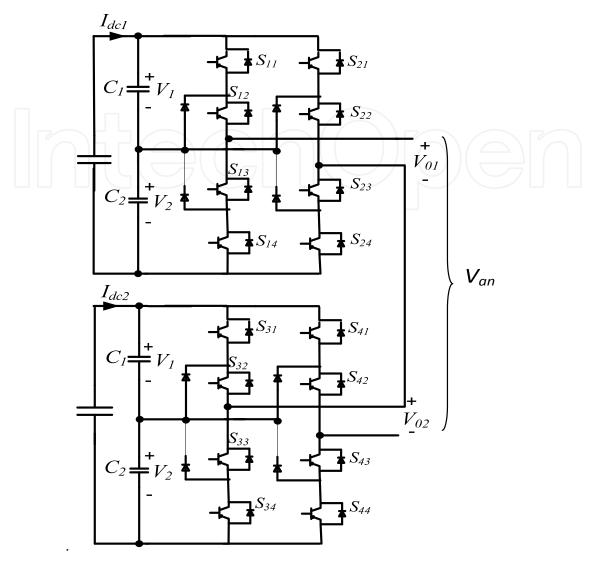

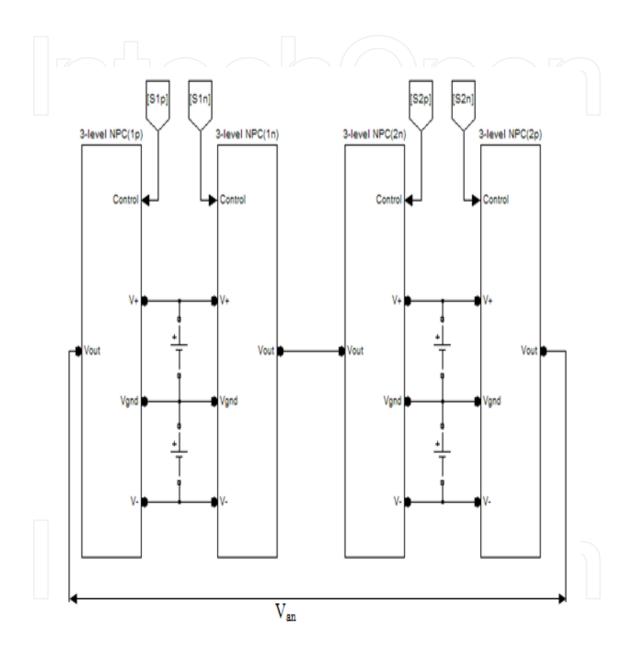

Fig 1 shows the circuit configuration of the proposed nine- level cascaded NPC/H-Bridge PWM inverter which consists of two legs for each cell connected to a common bus. Four active switches, four freewheeling diodes and two diodes clamped to neutral are adopted in each leg. The voltage stress of all the eight power switches is equal to half of DC bus voltage. The power switches in each leg are operated in high frequency using phase shifted PWM control technique to generate the three voltage levels on the ac terminal to neutral voltage point

The building block of the whole topology consists of two identical NPC cascaded cells. The inverter phase voltage  $V_{an}$  is the sum of the two cascaded cells, i.e.,

$$V_{an} = V_{01} + V_{02} \tag{1}$$

Fig. 1. Schematic diagram of the proposed cascaded NPC/H-bridge inverter model

Assuming that the two capacitor voltages on the DC bus voltage are equal, five different voltage levels +2Vdc,  $+V_{dc}$ , 0,  $-V_{dc}$  and  $-2V_{dc}$ , are generated on the ac terminal  $V_{01}$  which consist of two legs. Same applies to  $V_{02}$  fig. 2 shows the switching model for a nine-level output [6]. This implies that by cascading two NPC/H-Bridge inverters ( $V_{01}$  and  $V_{02}$ ) and properly phase shifting the modulating wave and carriers, a nine-level PWM output is achieved. The number of output voltage levels is given by

$$m = 4N + 1 \tag{2}$$

Where N is the number of series connected NPC/H-Bridges. The topology is made up of four three level legs and each leg has four active switches and four freewheeling diodes.

#### 2.2 System operation

Most of the past research on modeling of cascaded multilevel inverter has concentrated on realizing a switching model of conventional H- bridge inverter without giving a guideline

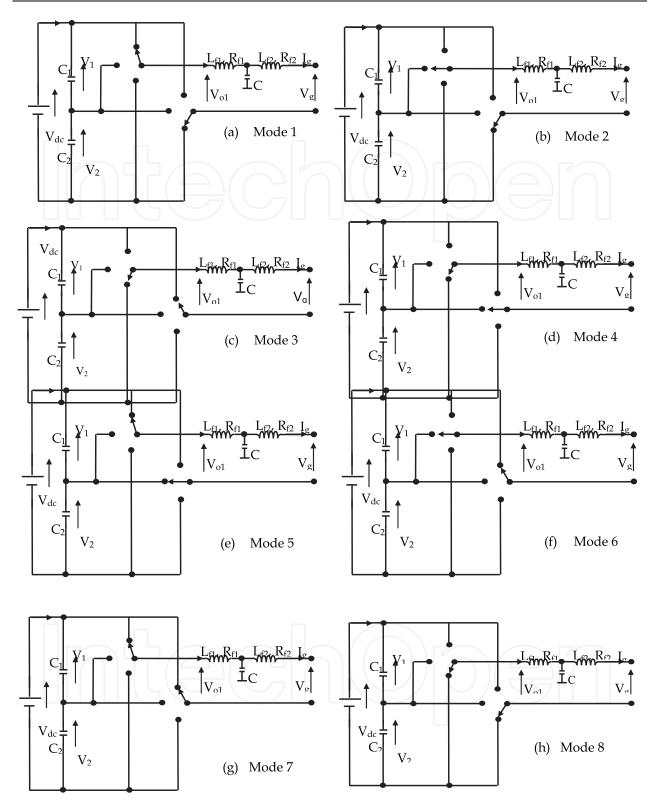

Fig. 2. Operating modes of one cell of NPC/H-Bridge inverter

on how one can get operating modes of cascaded NPC/H-bridge inverter and hence obtain a valid model for the topology. This section analyses eight valid operating modes of one cell of the proposed topology. The following assumptions are made in the modeling and analysis process:

- All components (power switches and capacitors) are ideal.

- The DC- link capacitors  $V_1$ ,  $V_2$ ,  $V_3$  and  $V_4$  have the same capacitance.

- PV cells supplies constant and equal voltages to the four DC link capacitors.

- The reference phase voltage is assumed to be a constant value during one switching period.

Figure 3 shows the operation modes for one NPC/H-bridge cell from the 9-level inverter. In mode 1 the power switches  $S_{11}$  &  $S_{12}$  and  $S_{23}$  &  $S_{24}$  are turned on to supply voltage at the output of first NPC/H-bridge cell that is equal to  $V_{01}$ =  $V_1$ +  $V_2$ . The capacitors  $C_1$  and  $C_2$  are discharged as they supply power to the utility as shown in figure 2 (a). The modes 2 to 8 are as shown in figures 2 (b) to 2 (h) respectively. In mode 2 the output voltage is  $V_{01}$ =  $V_2$ , in mode 3:  $V_{01}$ = - ( $V_1$ +  $V_2$ ), in mode 4:  $V_{01}$ = - $V_2$ , in mode 5:  $V_{01}$ =  $V_1$ , in mode 6:  $V_{01}$ = - $V_1$ : in mode 7:  $V_{01}$ = 0 and in mode 8:  $V_{01}$ = 0.

Based on the analysis of the operation model, the state variable equation for the proposed inverter can be estimated. To prevent the top and bottom power switched in each inverter leg from conducting at the same time, the constraints of power switches can be expressed as:

$$S_{i1} + S_{i3} = 1; S_{i2} + S_{i4} = 1$$

(3)

Where i = 1, 2. Let's define the switch operator as:  $T_1 = S_{11} \& S_{12}$ ;  $T_2 = S_{13} \& S_{13}$ ;  $T_3 = S_{21} \& S_{22}$   $T_4 = S_{23} \& S_{24}$ . The four valid expressions are given by:

$$T_1 = \begin{cases} 1 \text{ if both } S_{11} \& S_{12} \text{ are ON} \\ 0 \text{ Otherwise} \end{cases}$$

(4)

$$T_2 = \begin{cases} 1 & \text{if both } S_{13} \& S_{14} & \text{are ON} \\ 0 & \text{Otherwise} \end{cases}$$

(5)

$$T_3 = \begin{cases} 1 \text{ if both } S_{21} \& S_{22} \text{ are } ON \\ 0 \text{ Otherwise} \end{cases}$$

(6)

$$T_4 = \begin{cases} 1 \text{ if both } S_{23} \& S_{24} \text{ are ON} \\ 0 \text{ Otherwise} \end{cases}$$

(7)

From fig. 4 taking two legs for each cell to be *a* and *b*, the equivalent switching function are:

$$K_{a} = \begin{cases} 1 & \text{if } T_{1} = 1 \\ 0 & \text{if } S_{12} & 1 & \& K_{b} = \begin{cases} 1 & \text{if } T_{3} = 1 \\ 0 & \text{if } S_{22} & 1 \\ -1 & \text{if } T_{2} = 1 \end{cases}$$

$$(8)$$

Using equation (3 – 7), a switching state and corresponding voltage output  $V_{o1}$  can be generated as shown in table 1 which clearly indicates that there are 8 valid switching states; From table 1, the voltage  $V_{01}$  generate by the inverter can be expressed as:

$$V_{01} = V_a + V_b \tag{9}$$

For the control technique stated above; the voltage level for one leg of the cell is given as:

| Ka | K <sub>b</sub> | $T_1$ | T <sub>2</sub> | S <sub>12</sub> | T <sub>3</sub> | $T_4$ | S <sub>21</sub> | $V_a$  | $V_b$  | $V_{01}$       | Mode |

|----|----------------|-------|----------------|-----------------|----------------|-------|-----------------|--------|--------|----------------|------|

| 1  | -1             | 1     | 0              | 1               | 0              | 1     | 0               | $V_1$  | $-V_2$ | $V_1$ + $V_2$  | 1    |

| 0  | -1             | 0     | 0              | 1               | 0              | 1     | 0               | 0      | $-V_2$ | $V_2$          | 2    |

| -1 | 0              | 0     | 1              | 0               | 0              | 0     | 1               | 0      | $V_2$  | $-V_2$         | 3    |

| 1  | 0              | 1     | 0              | 1               | 0              | 0     | 1               | $V_1$  | 0      | $V_1$          | 4    |

| 0  | 1              | 0     | 0              | 1               | 1              | 0     | 1               | $-V_1$ | 0      | $-V_1$         | 5    |

| 1  | 1              | 1     | 0              | 1               | 1              | 0     | 1_              | $V_1$  | $V_1$  | 0              | 6    |

| -1 | [-1]           | 0     | 1              | 1               | 0              | 1     | / /1            | $V_2$  | $V_2$  | 0              | 7    |

| -1 | -1             | 0     | 1              | 0               | 1              | 0     | \ 1             | $V_2$  | $V_1$  | $-V_{1}-V_{2}$ | 8    |

Table 1. Switching States and Corresponding Voltage(s) for One Cell of NPC/H-bridge Inverter

$$V_{a} = K_{a} \left( \frac{K_{a} + 1}{2} \right) V_{1} - K_{a} \left( \frac{K_{a} - 1}{2} \right) V_{2}$$

(10)

Similarly for the second leg the expression is given by (11)

$$V_{b} = K_{b} \left( \frac{K_{b} + 1}{2} \right) V_{1} - K_{b} \left( \frac{K_{b} - 1}{2} \right) V_{2}$$

(11)

| S <sub>11</sub> | S <sub>12</sub> | S <sub>21</sub> | S <sub>22</sub> | S <sub>31</sub> | S <sub>32</sub> | S <sub>41</sub> | S <sub>42</sub> | $V_{01}$          | $V_{02}$          | V <sub>an</sub>   |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------------------|-------------------|-------------------|

| 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0                 | 0                 | 0                 |

| 0               | 0               | 0               | 1               | 0               | 0               | 0               | 0               | -V <sub>dc</sub>  | 0                 | -V <sub>dc</sub>  |

| 0               | 0               | 0               | 1               | 0               | 0               | 0               | 1               | -V <sub>dc</sub>  | -V <sub>dc</sub>  | -2V <sub>dc</sub> |

| 0               | 0               | 0               | 1               | 0               | 0               | 1               | 1               | -V <sub>dc</sub>  | -2V <sub>dc</sub> | -3V <sub>dc</sub> |

| 0               | 0               | 0               | 1               | 0               | 1               | 0               | 0               | -V <sub>dc</sub>  | $V_{dc}$          | 0                 |

| 0               | 0               | 0               | 1               | 1               | 1               | 0               | 0               | -V <sub>dc</sub>  | $2V_{dc}$         | $V_{dc}$          |

| 0               | 0               | 1               | 1               | 0               | 0               | 0               | 0               | -2V <sub>dc</sub> | 0                 | -2V <sub>dc</sub> |

| 0               | 0               | 1               | 1               | 0               | 0               | 0               | 0               | -2V <sub>dc</sub> | -V <sub>dc</sub>  | $-3V_{dc}$        |

| 0               | 0               | 1               | 1               | 0               | 0               | 1               | 0               | -2V <sub>dc</sub> | -2V <sub>dc</sub> | -4V <sub>dc</sub> |

| 0               | 0               | 1               | 1               | 0               | 1               | 0               | 0               | -2V <sub>dc</sub> | $V_{dc}$          | -V <sub>dc</sub>  |

| 0               | 0               | $\prod 1$       | 1               | 1               | 1               | 0               | 0               | -2V <sub>dc</sub> | $2V_{dc}$         | 0                 |

| 0               | 1               | 0               | 0               | 0               | 0               | 0               | 0               | $V_{dc}$          | 0                 | $V_{dc}$          |

| 0               | 1               | 0               | 0               | 0               | 0               | 0               | / 1(            | $V_{dc}$          | -V <sub>dc</sub>  | 0                 |

| 0               | 1               | 0               | 0               | 0               | 0               | 1               | 1               | $V_{dc}$          | -2V <sub>dc</sub> | -V <sub>dc</sub>  |

| 0               | 1               | 0               | 0               | 0               | 1               | 0               | 0               | $V_{dc}$          | V <sub>dc</sub>   | $2V_{dc}$         |

| 0               | 1               | 0               | 0               | 1               | 1               | 0               | 0               | $V_{dc}$          | $2V_{dc}$         | $3V_{dc}$         |

| 1               | 1               | 0               | 0               | 0               | 0               | 0               | 0               | $2V_{dc}$         | 0                 | $2V_{dc}$         |

| 1               | 1               | 0               | 0               | 0               | 0               | 0               | 1               | $2V_{dc}$         | -V <sub>dc</sub>  | $V_{dc}$          |

| 1               | 1               | 0               | 0               | 0               | 0               | 1               | 1               | $2V_{dc}$         | -2V <sub>dc</sub> | 0                 |

| 1               | 1               | 0               | 0               | 0               | 1               | 0               | 0               | $2V_{dc}$         | $V_{dc}$          | $3V_{dc}$         |

| 1               | 1               | 0               | 0               | 1               | 1               | 0               | 0               | $2V_{dc}$         | $2V_{dc}$         | $4V_{dc}$         |

| 1               | 1               | 1               | 1               | 1               | 1               | 1               | 1               | 0                 | 0                 | 0                 |

Table 2. Switching scheme for one phase leg of a nine level cascaded NPC/H- bridge inverter

From equation (9), the voltage output for one cell of the model can be deduced as;

$$V_{01} = \frac{K_a - K_b}{2} (V_1 + V_2) + \frac{K_a^2 - K_b^2}{2} (V_1 - V_2)$$

(12)

For the compound nine level inverter let's assume that  $V_1 = V_2 = V_3 = V_4 = V$ , the switching states are as shown in Table 2.

For a nine level cascaded NPC/H-bridge inverter, there are 22 valid switching states though two of the switching states are short circuits and thus cannot compensate the DC capacitor as current do not pass through either of the four DC- link capacitors.

#### 3. Mathematical analysis

Most of the past research on modeling of cascaded multilevel inverter has concentrated on realizing a switching model of conventional H- bridge inverter without giving a guideline on how one can get operating modes of cascaded NPC/H-bridge inverter and hence obtain a valid model for the topology. This section analyses eight valid operating modes of one cell of the proposed topology and proposes an equivalent circuit for the topology.

The following assumptions are made for deriving the mathematical model of the cascaded H-bridge inverters.

- The grid is assumed to be AC current source,

- The power losses of the whole system are categorized as series loss and parallel loss. The series loss and interfacing inductor loss are represented as equivalent series resistance (ESR). Parallel losses are represented as shunt connected resistances across the dc-link capacitors.

The differential equations describing the dynamics of the coupling inductor between the NPC/H-bridge inverter and the grid of the model shown in fig. 1 can be derived as:

$$\begin{cases}

L_{f1} \frac{di_{fx}}{dt} = -V_{cx} - i_{fx} R_{f1x} + \delta_{1x} V_1 + \delta_{2x} V_2 \\

L_{f2} \frac{di_{sx}}{dt} = -V_{cx} - i_{sx} R_{f2x} - V_{sx}

\end{cases}$$

(13)

According to Kirchhoff's law, the currents flowing into the dc link capacitors  $C_1$  and  $C_2$  can be expressed as:

$$\begin{cases} i_{C1} = C_1 \frac{dV_1}{dt} = \delta_{1x} i_{fx} \frac{V_1}{R} + \frac{V_2}{R} \\ i_{C2} = C_2 \frac{dV_2}{dt} = -\delta_{2x} i_{fx} \frac{V_1}{R} + \frac{V_2}{R} \\ i_{CX} = C_f \frac{dV_{fx}}{dt} = i_{fx} - i_{sx} \\ C_1 \frac{dV_1}{dt} - C_2 \frac{dV_2}{dt} = \delta_3 i_{fx} \end{cases}$$

$$(14)$$

The equations (13) and (14) can be rearranged as:

$$\begin{cases}

\frac{di_{fx}}{dt} = \frac{R_{f1x}}{L_{f1}} - \frac{V_{cx}}{L_{f1}} + \frac{\delta_{1x}V_{1}}{L_{f1}} + \frac{\delta_{2x}V_{2}}{L_{f1}} \\

\frac{di_{sx}}{dt} = \frac{V_{cx}}{L_{f2}} - \frac{R_{f1}}{L_{f2}} - \frac{V_{sx}}{L_{f2}} \\

\frac{dV_{1}}{dt} = \frac{\delta_{1x}i_{fx}}{C_{1}} - \left(\frac{V_{1}}{RC_{1}} + \frac{V_{2}}{RC_{1}}\right) \\

\frac{dV_{2}}{dt} = \frac{\delta_{2x}i_{fx}}{C_{2}} - \left(\frac{V_{1}}{RC_{2}} + \frac{V_{2}}{RC_{2}}\right) \\

\frac{dV_{f}}{dt} = \frac{i_{fx}}{C_{f}} - \frac{i_{sx}}{C_{f}} \\

\delta_{3}i_{fx} = C_{1}\frac{dV_{1}}{dt} - C_{2}\frac{dV_{2}}{dt}

\end{cases} \tag{15}$$

Equation (16) can be written in the format of:

$$Z\dot{x} = Ax + B \tag{16}$$

Capacitor current, inverter current and utility line current and DC- Link capacitors are taken as state variables:

$$x = [i_{fx} \ i_{sx} \ V_c \ V_1 \ V_2]^T \tag{17}$$

$$Z = \begin{bmatrix} L_{f1} & 0 & 0 & 0 & 0 \\ 0 & L_{f2} & 1 & 0 & 0 \\ 0 & 0 & C & 0 & 0 \\ 0 & 0 & 0 & C_1 & 0 \\ 0 & 0 & 0 & 0 & C_2 \end{bmatrix}$$

$$(18)$$

$$B = [0 - V_{s} \ 0 \ 0 \ 0]^{T} \tag{19}$$

Matrix A depends on each operating mode as such

• For  $V_{01} = +V_2$

$$A_{1} = \begin{bmatrix} -R_{f1} & 0 & -1 & 0 & 1\\ 0 & -R_{f2} & 1 & 0 & 0\\ 1 & -1 & 0 & 0 & 0\\ 0 & 0 & 0 & R^{-1}R^{-1}\\ -1 & 0 & 0 & R^{-1}R^{-1} \end{bmatrix}$$

(20)

• For  $V_{01} = -V_2$

$$A_5 = A_1^T \tag{21}$$

• For  $V_{01} = +V_1$

$$A_{2} = \begin{bmatrix} -R_{f1} & 0 & -1 & 1 & 0 \\ 0 & -R_{f2} & 1 & 0 & 0 \\ 1 & -1 & 0 & 0 & 0 \\ -1 & 0 & 0 & R^{-1}R^{-1} \\ 0 & 0 & 0 & R^{-1}R^{-1} \end{bmatrix}$$

(22)

• For  $V_{01} = -V_1$

$$A_6 = A_2^T \tag{23}$$

• For  $V_{01} = 0$

$$A_{4} = \begin{bmatrix} -R_{f1} & 0 & -1 & -1 & -1 \\ 0 & -R_{f2} & 1 & 0 & 0 \\ 1 & -1 & 0 & 0 & 0 \\ -1 & 0 & 0 & 0 & 0 \\ -1 & 0 & 0 & 0 & 0 \end{bmatrix}$$

(24)

Considering the same assumption made earlier that the dc link capacitors have the same capacitance  $C_1 = C_2 = C$  which implies  $V_1 = V_2 = V_{dc}/2$ , the state space equation (17) can be simplified to:

$$Z'\dot{x} = A'x + B' \tag{25}$$

With

$$x = [i_{fx} i_{sx} V_c V_{dc} / 2]^T$$

(26)

$$Z' = \begin{bmatrix} L_{f1} & 0 & 0 & 0 \\ 0 & L_{f2} & 1 & 0 \\ 0 & 0 & C & 0 \\ 0 & 0 & 0 & C_T \end{bmatrix}$$

(27)

$$B = [0 \ V_s \ 0 \ 0 \ 0]^T \tag{28}$$

$$A' = \begin{bmatrix} -R_{f1} & 0 & -k & k \\ 0 & -R_{f2} & k & 0 \\ k & -1 & 0 & 0 \\ -k & 0 & 0 & 0 \end{bmatrix}$$

(29)

Where *k* depends on the operating mode and can take five different values: 1. 0.5 0, -05, -1.

For a three phase system,  $V_s$  is replaced  $V_s(\cos\omega_0 t)$ ,  $V_s(\cos\omega_0 - 2\pi/3)$  and  $V_s(\cos\omega_0 + 2\pi/3)$ . similarly the Z, A and B matrices are expanded accordingly to three phase. Where  $V_s$  is the grid voltage.

#### 3.1 Harmonic analysis of a nine level cascaded NPC/H-bridge inverter

Having realized a nine- level output from the a cascaded 9- level model, it is important to theoretically investigate its harmonic structure and show how harmonic suppression is achieved. Based on the principle of double Fourier integral (Holmes & Thomas, 2003). the first modulation between triangular carrier  $v_{cr1}$ , and the positive sinusoidal waveform a naturally sampled PMW output  $V_p(t)$  of equation (30). Where M is the modulation index,  $V_{dc}$  is the DC link voltage of the PWM inverter and  $J_n$  is the nth order Bessel function of the first kind. Using  $v_{cr2}$  which is the same carrier but displaced by minus unity, the naturally sampled PWM output  $V_n$  is as given in equation (31)

$$V_{p}(t) = \begin{cases} \frac{V_{dc1}M}{2} + \frac{V_{dc1}M}{2}\cos\omega_{s}t + \frac{2V_{dc1}}{\pi}\sum_{m=1}^{\infty}\frac{1}{m}J_{0}(m\frac{\pi}{2}M) \\ \sin m\frac{\pi}{2}\cos\omega_{s}t + \frac{2V_{dc1}}{\pi}\sum_{m=1}^{\infty}\sum_{\substack{n=-\infty\\n\neq 0}}^{\infty}\frac{1}{m}J_{n} \\ (m\frac{\pi}{2}M)\sin(m+n)\frac{\pi}{2}\cos(n\omega_{c}t + n\omega_{s}t) \end{cases}$$

(30)

$$V_{n}(t) = \begin{cases} \frac{V_{dc1}}{2} - \frac{V_{dc1}M}{2} \cos \omega_{s} t - \frac{2V_{dc1}}{\pi} \sum_{m=1}^{\infty} \frac{1}{m} J_{0}(m\frac{\pi}{2}M) \\ \sin m\frac{\pi}{2} \cos \omega_{s} t + \frac{2V_{dc1}}{\pi} \sum_{m=1}^{\infty} \sum_{\substack{n=-\infty\\n \neq 0}}^{\infty} \frac{1}{m} J_{n} \\ (m\frac{\pi}{2}M) \sin(m+n)\frac{\pi}{2} \cos(n\omega_{c} t + n\omega_{s} t) \end{cases}$$

(31)

The output of leg 'a' is given by  $V_a(t) = V_p(t) - V_n(t)$  which is:

$$V_{a}(t) = \begin{cases} V_{dc1}\cos(\omega_{s}t) + \frac{4V_{dc1}}{\pi} \sum_{m=2,4,6}^{\infty} \sum_{n=\pm 1\pm 3\pm 5}^{\infty} \frac{1}{m} J_{n} \\ (m\frac{\pi}{2}M)\cos(m\omega_{c}t + n\omega_{s}t) \end{cases}$$

(32)

The output of leg 'b' is realized by replacing  $\omega_s$  with  $\omega_s$ +  $\pi$  and using  $v_{cr2}$  which is same as phase displacing  $v_{cr1}$  by minus unity which gives

$$V_{b}(t) = \begin{cases} -V_{dc1}\cos(\omega_{s}t) - \frac{4V_{dc1}}{\pi} \sum_{m=2,4,6}^{\infty} \sum_{n=\pm 1 \pm 3 \pm 5}^{\infty} \frac{(-1)^{m+n}}{m} J_{n} \\ (m\frac{\pi}{2}M)\cos(m\omega_{c}t + n\omega_{s}t) \end{cases}$$

(33)

From equations (32) and (33), it can be clearly deduced that that odd carrier harmonics and even sideband harmonics around even carrier harmonic orders are completely eliminated. Five- level obtained by taking the differential output between the two legs and is given by (35). Similarly the output between the other two legs of the second cell of the hybrid model is achieved by replacing  $\omega_s$  with  $\omega_s$ +  $\pi$  and  $\omega_c$  with  $\omega_c$  +  $\pi/4$  which gives another five level inverter for equation given by equation (34)

$$V_{01}(t) = \begin{cases} 2V_{dc1}\cos(\omega_{s}t) + \frac{8V_{dc1}}{\pi} \sum_{m=4,8,12}^{\infty} \sum_{n=\pm 1 \pm 3 \pm 5}^{\infty} \frac{1}{m}J_{n} \\ (m\frac{\pi}{2}M)\cos(m\omega_{c}t + n\omega_{s}t) \end{cases}$$

(34)

$$V_{02}(t) = \begin{cases} -2V_{dc1}\cos(\omega_{s}t) - \frac{8V_{dc1}}{\pi} \sum_{m=4,8,12}^{\infty} \sum_{n=\pm 1 \pm 3 \pm 5}^{\infty} \frac{(-1)^{\frac{m}{4} + n}}{m} J_{n} \\ (m\frac{\pi}{2}M)\cos(m\omega_{c}t + n\omega_{s}t) \end{cases}$$

(35)

Equations (34) and (35) clearly show that for five- level inverter, the proposed control strategy has achieved; Suppression of carrier harmonics to multiples of four; Elimination of even side harmonics around multiples of four carrier harmonics of Multiples of four carrier harmonics. Finally the output for a nine level is achieved differentiating the output voltage between the two cells of the five level cells and this is given by equation (36). It can be concluded that for a cascaded N-level inverter the carrier harmonic order is pushed up by factor of 4N where N is the number of cascaded hybrid inverters. The output voltages and spectral waveforms to confirm the validation of the control strategy using this approach of double Fourier transform will be discussed later.

$$V_{an}(t) = \begin{cases} 4V_{dc1}\cos(\omega_{s}t) + \frac{8V_{dc1}}{\pi} \sum_{m=8,16,24}^{\infty} \sum_{n=\pm 1 \pm 3 \pm 5}^{\infty} \frac{1}{m} J_{n} \\ (m\frac{\pi}{2}M)\cos(m\omega_{c}t + n\omega_{s}t) \end{cases}$$

(36)

#### 4. Proposed hybrid control method

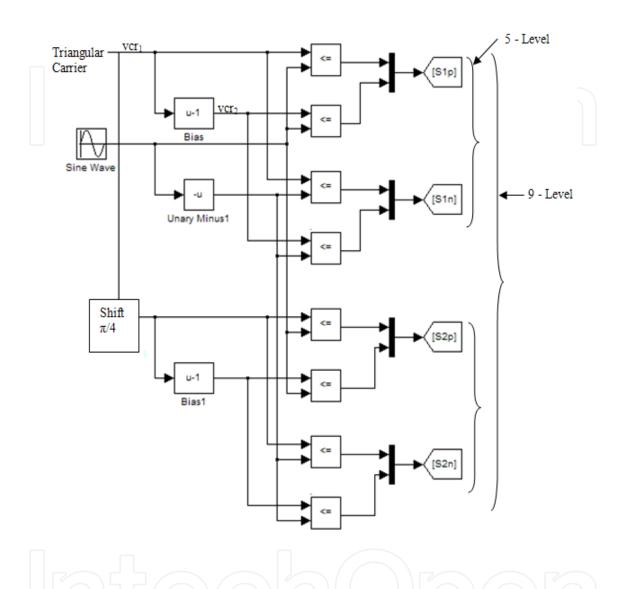

The above section has illustrated in general the switching technque for one cell of the cascaded NPC/H-bridge model, because of the modularity of the model, two cells will be considered for modulatin and analysis in this section. For the two cells an improved strategy for realizing nine level output is proposed in this book chapter. The article uses the principle of decomposition where each leg is treated independently and gives a three level output (Naderi & Rahmati, 2008).

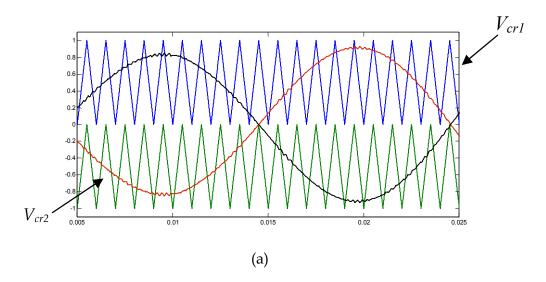

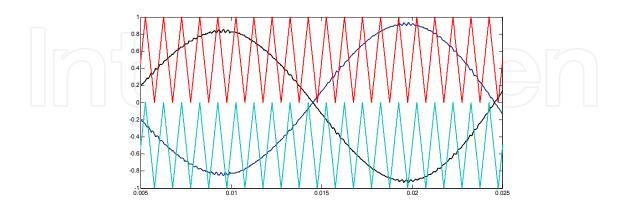

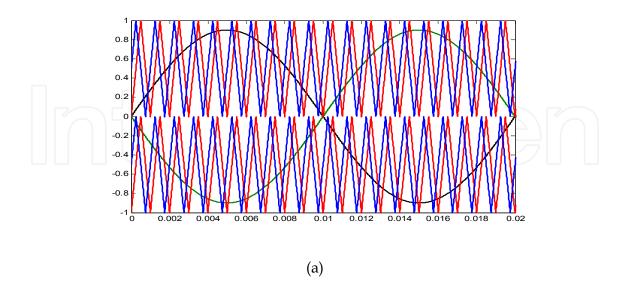

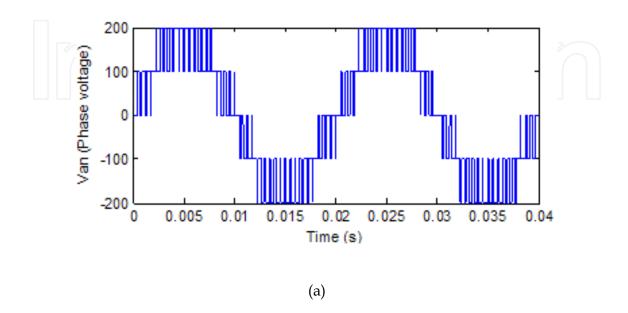

Positive and negative legs are connected together back to back and they share the same voltage source  $V_{dc}$ . PD modulation is used for achieving three level output (Rodriguez et al., 2002). To achieve a five level PWM output two triangular carriers  $V_{cr1}$  and  $V_{cr2}$  in phase but vertically disposed and modulating wave phase shifted by  $\pi$  are used. The multilevel converter model is modulated using phase shifted PWM technique as illustrated in fig. 3

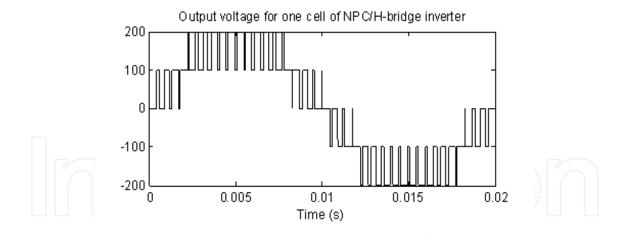

and 4 for the two NPC/H-Bridge cells. Finally a nine- level PWM output is achieved by using the same two carriers but phase shifted by  $\pi/4$  and modulating wave phase shifted by  $\pi$  as shown in fig. 5. This is a simple control strategy that can be easily implemented in a digital signal processor. The switching states for one phase leg of a nine- level NPC/H-bridge inverter is shown in table 2, as can be seen there several redundant states which can be utilized in DC voltage balance, this is not within the scope of this paper.

The control strategy has two advantages as compared to multicarrier PWM approach (Holmes & McGrath, 2001). First for an N-level cascaded NPC/H-bridge PWM inverter, we can use a switching frequency of 4N times less to achieve the same spectrum as multicarrier approach. This has an advantage of reducing the switching losses, which is an important feature in high power application. Secondly the multicarrier PWM approach requires 8 carriers to achieve nine level output, but the proposed control strategy requires only one carrier phase shifted by  $(N-1)\pi/4$  where N is the number of series connected NPC/H-Bridge inverter.

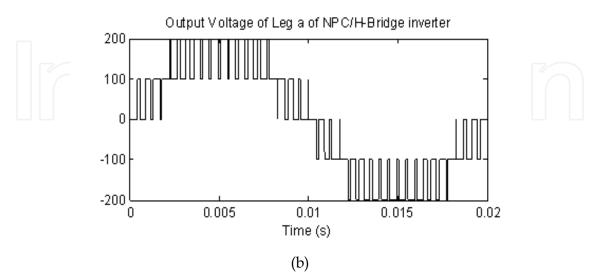

Fig. 3. (a) PWM scheme and (b) output voltage waveform for one cell of NPC/H-Bridge inverter

(a)

(b)

Fig. 4. (a) Phase shifted PWM scheme and (b) output voltage waveform for the second cell of cascaded NPC/H-Bridge inverter

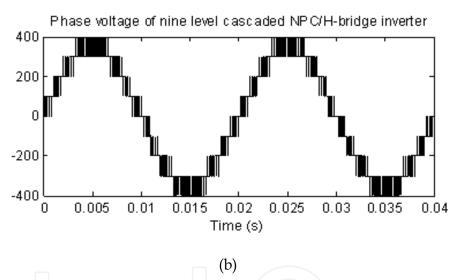

Fig. 5. (a) PWM scheme and (b) output voltage waveform for a nine level cascaded NPC/H-Bridge inverter

#### 5. MATLAB simulation

Part of the Matlab simulation has already been carried out in section 4 to investigate the proposed phase shifted PWM control technique. In order verify that a nine- level output is achieved by cascading two NPC/H-Bridge PWM inverter and properly phase shifting the carrier and the modulating wave, a model as shown in fig. 6 was developed and simulated in MATLAB. The control strategy to minimize harmonics was designed and developed in MATLAB as shown in fig. 7 (wanjekeche et.al., 2009). It is assumed that the dc voltage input for each module is E = 100V. The inverter operates under the condition of  $f_m = 50HZ$ ,  $m_f = 20$  for a five level output and  $m_a = 0.9$ . The device switching frequency is found from  $f_{sw,dev} = m_f/2$   $X f_m = 500HZ$

Fig. 6. Four legs of a nine-level cascaded NPC/H-bridge inverter

Fig. 7. Control strategy for a nine-level cascaded NPC/H-bridge inverter

#### 5.1 Simulation results and discussion

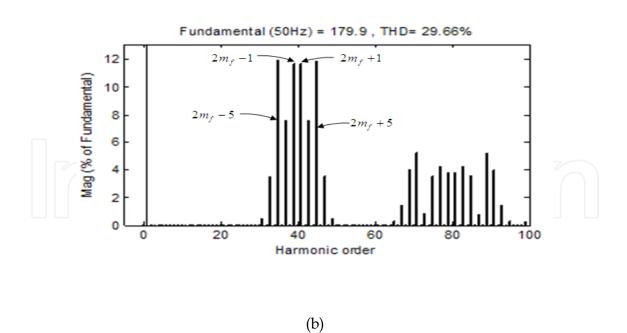

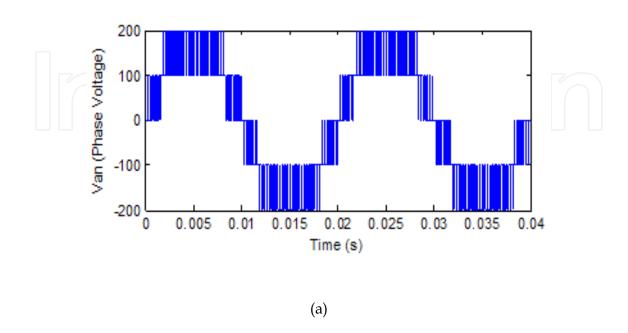

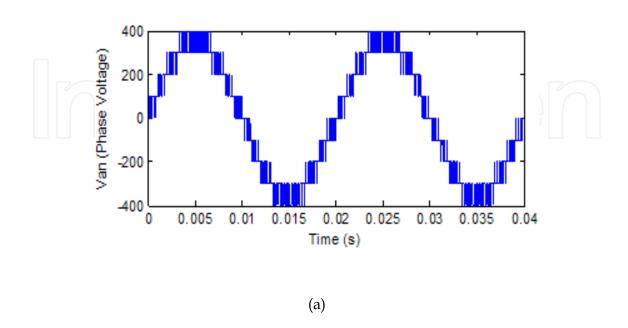

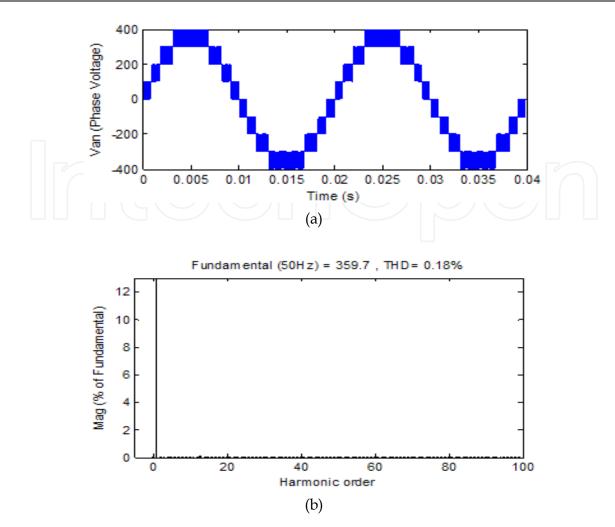

Five- level inverter output are shown in figs.8, 9 and 10 for various switching frequency. Fig.8 shows the simulated waveform for the phase voltage  $V_{01}$  of the NPC/H-Bridge PWM inverter and its harmonic content. The waveform  $V_{01}$  is a five voltage levels, whose harmonics appear as sidebands centered around  $2m_f$  and its multiples such as  $4m_f$ ,  $6m_f$ . This simulation verifies analytical equation (34) which shows that the phase voltage does not contain harmonics lower than the  $31^{st}$ , but has odd order harmonics (i.e.  $n=\pm 1\pm 3\pm 5$ ) centered around m=4, 8, 12. Figs. 9 & 10 shows five- level NPC/H-Bridge inverter output for device inverter switching frequency of 1000HZ and 200HZ respectively.

Fig. 8. (a) Waveform and (b) Spectrum for a five level NPC/H-Bridge inverter phase voltage ( $f_m$ =50HZ,  $f_{sw,dev}$ =500HZ,  $m_f$ =20,  $m_a$ =0.9)

Fig. 9. (a) Waveform and (b) Spectrum for a five level NPC/H-Bridge inverter phase voltage  $(f_m=50$ HZ,  $f_{sw,dev}=1000$ HZ,  $m_f=40$ ,  $m_a=0.9$ )

Fig. 10. (a) Waveform and (b) Spectrum for a five level NPC/H-Bridge inverter phase voltage ( $f_m$ =50HZ,  $f_{sw,dev}$ =2000HZ,  $m_f$ =80,  $m_a$ =0.9

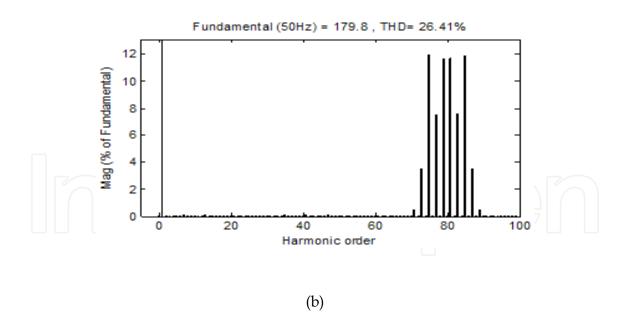

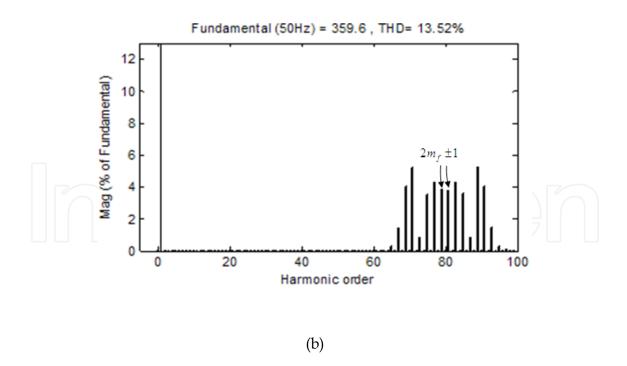

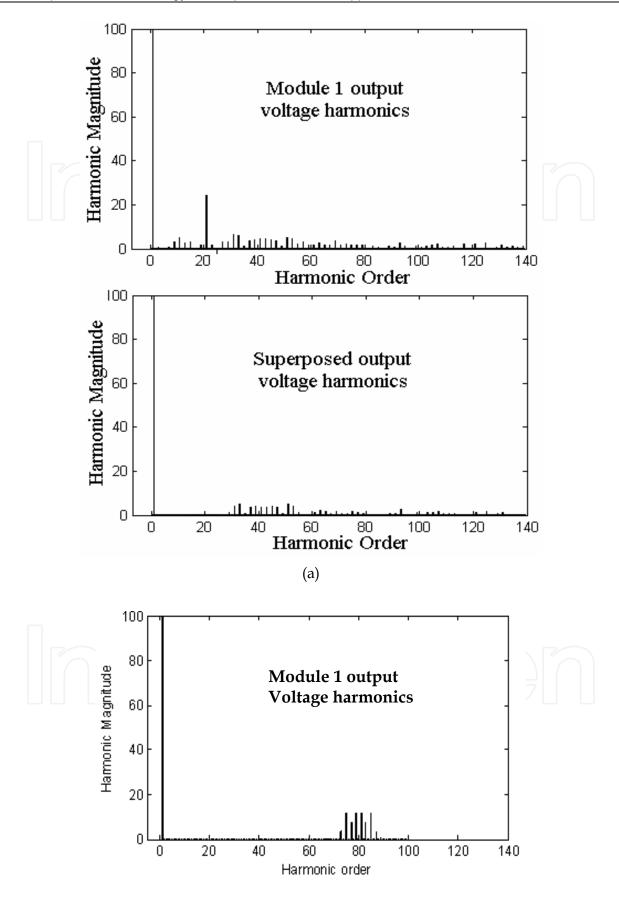

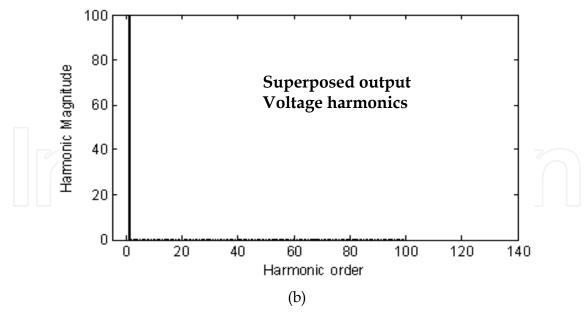

Fig. 11 shows the waveform of the phase voltage of a nine level NPC/H-Bridge PWM inverter. It has sidebands around  $4m_f$  and its multiples, this shows further suppression in harmonic content. This topology operates under the condition of  $f_m$ =50HZ,  $m_f$ =40 and  $m_a$ =0.9. The device switching frequency is found from  $f_{sw,dev}$ =  $m_f$ /4 X  $f_m$ =500HZ. This simulation verifies analytical equation (36) which shows that the phase voltage does not contain harmonics lower than the 67th, but has odd order harmonics (i.e. n=±1±3±5) centered around m=8, 16, 32. As can be seen from fig. 12, a switching frequency of 1KHZ which fits most of high power switching devices has a THD of 0.18% this makes the topology a perfect fit for most high power application such as utility interface power quality control and Medium Voltage drives.

Fig. 11. (a) Waveform and (b) Spectrum for a nine- level cascaded NPC/H-Bridge inverter phase voltage ( $f_m$ =50HZ,  $f_{sw,dev}$ =500HZ,  $m_f$ =40,  $m_a$ =0.9)

Fig. 12. (a) Waveform and (b) Spectrum for a nine-level cascaded NPC/H-Bridge inverter phase voltage ( $f_m$ =50HZ,  $f_{sw,dev}$ =1000HZ,  $m_f$ =80,  $m_a$ =0.9)

### 6. Comparison of the proposed control technique with conventional PWM multicarrier approach

As can be seen from fig. 1, to achieve the same voltage levels *N* for each phase, only (*N*-1)/4 separate dc sources are needed for one phase leg converter of the cascaded NPC/H-bridge model, whereas (*N*-1)/2 separate voltage voltages is need for cascaded H -bridge inverter. Thus for an n- cascaded NPC/H-bridge inverter, the number of separate DC sources S is given by:

$$S = \frac{N-1}{4} \tag{37}$$

Table 3 shows comparison on the number of components for various multilevel inverters, cascaded NPC/H-bridge inverter requires 16 switching devices just as the other topologies but used only two carriers for any level of voltage output. For comparison between the two cascaded inverters it is readily shown in table 4 that the NPC/H-bridge inverter has an advantage of realizing the same voltage level as cascaded H-bridge inverter with a half number of separate DC sources which is more expensive as compared to clamping diodes.

| Topology No. of Components | Diode<br>clamped | Flying<br>capacitor | Cascaded<br>H- bridge | Cascaded<br>NPC/H-<br>bridge |  |

|----------------------------|------------------|---------------------|-----------------------|------------------------------|--|

| Switching devices          | 16               | 16                  | 16                    | 16                           |  |

| Clamping diodes            | 56               | 0                   | 0                     | 8                            |  |

| Flying capacitors          | 0                | 56                  | 0                     | 0                            |  |

| Carriers                   | 8                | 8                   | 4)(4                  | 2                            |  |

| Separate cells             | 0                | 0                   | 4                     | 2                            |  |

| Separate dc sources        | 1                | 0                   | 4                     | 2                            |  |

Table 3. Component comaprison for different multilevel inverters for nine level voltage output

| Topology No. of Components | Cascaded<br>H- bridge | Cascaded<br>NPC/H-bridge |  |

|----------------------------|-----------------------|--------------------------|--|

| Switching devices          | 2N-1                  | 2N-1                     |  |

| Clamping diodes            | 0                     | N-1                      |  |

| Flying capacitors          | 0                     | 0                        |  |

| Carriers                   | (N-1)/2               | 2                        |  |

| Separate cells             | (N-1)/2               | (N-1)/4                  |  |

| Separate dc sources        | (N-1)/2               | (N-1)/4                  |  |

Table 4. Component comaprison for different multilevel inverters for nine level voltage output

#### 6.1 Comparison of the MATLAB simulation results of the two PWM control methods

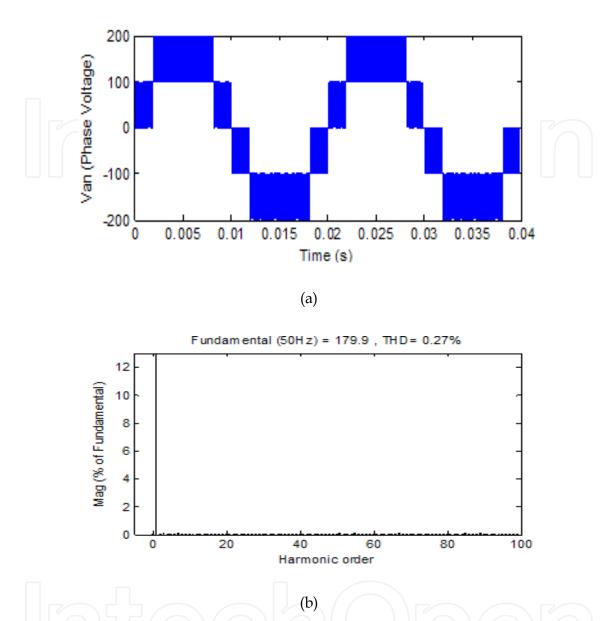

To clearly investigate the superiority of the model under the proposed PWM control technique, Matlab simulation results was carried out on a cascaded NPC/H-bridge nine level inverter model under the conditions of  $f_m$ =50HZ,  $f_c$  =1000Hz and  $m_a$ =0.9.

With the proposed Phase – shifted PWM technique, there is further harmonic suppression as shown in fig. 13 (b), as compared to conventional PWM Phase shifted approach. This is clearly illustrated in fig. 13 (a) where Phase Disposition and Phase shifted PWM modulation strategy is adopted (Jinghua & Zhengxi, 2008). This is beacuse with conventional PWM multicarrier approach, optimum harmonic cancellation is achieved by phase shifting each carrier by  $(i-1)\pi/N$  (Holmes & Thomas, 2003). where i is the  $i^{th}$  converter, N is the number of series – connected single the multicarrier PWM approach requires 8 carriers to achieve nine level output, but the proposed control strategy requires only one carrier phase shifted by  $(N-1)\pi/4$  as stated in section 4.1(Wanjekeche et al., 2009).

Fig. 13. Spectra voltage waveforms of NPC/H-bridge topology using (a) conventional multicarrier phase shifted PWM approach (b) proposed phase shifted PWM approach

#### 7. Conclusion

In this chapter it has been demonstrates with proper modeling of the converter, the operating characteristic and the control technique to be applied on the model can be easily found. This can be used to develop standard model for cascaded NPC/H-bridge inverter which is currently not available.

The article has developed an improved topology that can be used to achieve a nine-level NPC/H-Bridge PWM inverter. It has been clearly shown that five level NPC/H-Bridge inverter that has been proposed by many researchers gives a higher THD which is not acceptable in most high and medium power application unless a filter is used. And since there is limited research on cascaded this important hybrid model, the chapter has developed a novel phase shifted PWM control technique that was tested on a two cell cascaded NPC/H-bridge model. In the proposed control technique it has been shown that by properly phase shifting both the modulating wave and the carrier, a nine-level voltage output can be achieved with a reduced harmonic content. With a THD of 0.18% without a filter, this makes the control strategy for a cascaded nine level NPC/H-bridge inverter a good option for medium and high power application such as utility interface and medium drives.

The simulation results obtained clearly verifies the analytical equations from double Fourier transform, showing that a nine-level output has multiples of eighth- order cross modulated harmonics. From the mathematical analysis it has been shown that cross modulated harmonics for a generalized m- level cascaded NPC/H-Bridge inverter is a multiple of 4N where N is the number of series connected NPC/H-Bridge inverter

And finally the superiority of the proposed phase shifted PWM control technique is validated by comparing its waveform spectra with that of the conventional phase shifted PWM technique and it was shown the inverter exhibits reduced harmonic content

#### 8. References

- Benslimane, T. (2007). Open Switch Faults Detection and Localization Algorithm for Three Phase Shunt Active Power Filter based on Two Level Voltage Source Inverter," *Electronics and Electrical Engineering Conference* 2(74), pp. 21-24, ISSN 1392-1215

- Franquelo, L.G.; Rodriquez, J.; Leon, J.I.; Kouro, S.; Portillo, R. & Prats, M.A.M. (2008). The Age of Multilevel Converters Arrives, *IEEE Industrial Electronics Magazine*, pp. 28-39, ISSN 1932-4529

- Gupta, R.; Ghosh, A. & Joshi, A. (2008). Switching Characteristics of Cascaded Multilevel Inverter Controlled Systems, *IEEE Transactions on Industrial Electronics*, vol.55, no.3, pp. 1047-1058, ISSN: 0278-0046

- Holmes, D.G. & McGrath, B.P. (2001). Opportunities for harmonic cancellation with carrier-based PWM for two level and multilevel cascaded inverters, *IEEE Transaction on Industrial Applications*, vol. 37, no. 2, pp.547 582, ISSN 0093-9994, August 2002

- Kouro, S.; Rebolledo J. & Rodriquez J. (2005). Reduced switching frequency modulation algorithm for high power multilevel inverters, *IEEE Transaction on Industrial Electronics*, vol.54, no.5, pp. 2894- 2901, ISBN 0-7803-9033-4, January 2006

- Lai, J. S. & Peng, F. Z. (1995). Multilevel Converters A New Breed of Power Converters," *IEEE Transactions on Industry Applications*, vol. 32, no. 3, pp. 509-517, ISBN 0-7803-3008-0 August 2002

- Peng, F. Z.; Lai, J. S.; McKeever, J. W. & VanCoevering, J. (1996). A Multilevel Voltage-Source Inverter with Separate DC Sources for Static Var Generation, *IEEE Transactions on Industry Applications*, vol. 32, no. 5, pp. 1130-1138, Aug. 2002. ISBN: 0-7803-3008-0

- Rodriguez, J.; Lai, J. S. & Peng, F. Z. (1995). Multilevel Inverters: Survey of Topologies, Controls, and Applications, *IEEE Transactions on Industry Applications*, vol. 49, no. 4, pp. 724-738, ISSN 0278-0046

- Sinha, G. & Lipo, T. A. (1996). A Four Level Rectifier-Inverter System for Drive Applications, *IEEE-IAS Conference Record*, pp. 980-987, ISBN 0-7803-3544-9, August 2002

- Tolbert, L. M.; Peng, F. Z. & Habetler, T. (1999). Multilevel Converters for Large Electric drives, *IEEE Trans. Ind. Application*, vol.35, pp. 36-44, ISSN 0093-9994, August 2002

- Manjrekar, M.D. & Lipo, T.A. (1988). A hybrid multilevel inverter topology for drive applications, *IEEE APEC*, pp. 523-529, ISBN 0-7803-4340-9, August 2002

- Manjrekar, M.D. & Lipo, T.A. (1998). A generalized structure of multilevel power converter, *Proc. IEEE PEDS*, 62-67, ISBN 0-7803-4879-6

- Manjrekar, M.D. & Lipo, T.A. (2000). Hybrid multilevel power conversion system: A competitive solution for higher power application, IEEE *Transaction on Industry Application*, Vol. 36, no. 3, pp. 834-841, ISSN 0093-9994, August 2002

- Corzine, K. & Familiant, Y. (2002). A new cascaded multilevel H- bridge drive, *IEEE Trans on Power Electronics*, Vol. 17, no.1, pp. 125-131, ISSN 0885-8993

- Lund, R. et. al., (1999). Control strategies for hybrid seven level inverter, EPE Conference Proceedings

- Sneineh, A.A.; Wang, M. W. & Tian, K. (2006). A new topology for capacitor clamp cascaded multilevel converters, *IEEE -IPEMC*, pp. 1-5, ISSN 1-4244-0448-7, February 2009

- Park J. et. al., (2003). A new single phase 5 level PWM inverter employing a deadbeat control scheme, *IEEE Transaction on Power Electronics*, vol.18, no.3, pp. 831-843, ISSN 0885-8993

- Zhang, L.; Watkins, S.J. & Shepherd, W. (2002). Analysis and control of multilevel flying capacitor inverter, *IEEE CIEP*, pp. 66-71, ISBN 0-7803-7640-4, August 2003

- Ding, K. et. al., (2004). A novel hybrid diode clamp cascade multilevel converter for high power application, *IEEE Transaction on Industry Application*, 39<sup>th</sup> IAS Annual Meeting, 820-827, ISBN 0-7803-8486-5

- Duarte, J.L.; Jullicher, P.J.M.; Offringa L.J.J. & Groningen, W.D.H. (1997). Stability analysis of multilevel converters with imbricated cells, *EPE Conference Proceedings*, pp. 168-174.

- Rojas, R. & Ohnishi, T. (1997). PWM control method with reduced of total capacitance required in a three-level inverter, *COBEP Conference Proceedings*, pp. 103-108

- Wu, C.M.; Lau W.H. & Chung, H. (1999). A five-level neutral-point-clamped H-bridge PWM inverter with superior harmonics suppression: A theoretical analysis, *ISACS '99, proceedings of the 1999 IEEE international symposium*, vol. 5, pp.198-201

- Cheng, Z. & Wu, B. (2007). A novel switching sequence design for five-Level NPC/H-Bridge inverters with improved output voltage spectrum and minimized device switching frequency, *IEEE Transactions on Power Electronics*, vol. 22 no.6, 2138 2145, ISSN 0885-8993

- Naderi, R. & Rahmati, A. (2008). Phase shifted carrier PWM technique for general cascade inverters, *IEEE Transactions on power electronics*, vol. 23, no.3, pp.1256-1269, ISSN 0885-8993

- Jinghua, Z. & Zhengxi, L. (2008). Research on hybrid modulation strategies based on general hybrid topology of multilevel inverter, *International symposium on power electronics* and electric drives, automation and motion (SPEEDAM), pp. 784 788, ISBN 978-1-4244-1663-9

- Holmes, D.G. & Thomas, A.L. (2003). *Pulse Width Modulation for Power Converters –principles and practices*, IEEE press series, A John Wiley & Sons inc. publication, ISBN: 978-0-471-20814-3, 445 Hoes Lane, Piscataway NJ 0885

- Wanjekeche, T. Jimoh, A.A. & Nicolae, D.V. (2009). A Novel Multilevel 9- level inverter based on 3 level NPC/H-Bridge topology for Photovoltaic application" international review of electrical engineering, Vol. 4, No.5, ISSN 1827-6679

- Wanjekeche, T. Nicolae, D.V. & Jimoh, A.A. (2009). A Cascaded NPC/H-bridge inverter with simplified control strategy and minimum component count, *IEEE Africon*, pp. 1-6, ISBN 978-1-4244-3918-8

#### MATLAB - A Ubiquitous Tool for the Practical Engineer

Edited by Prof. Clara Ionescu

ISBN 978-953-307-907-3 Hard cover, 564 pages

Publisher InTech

Published online 13, October, 2011

Published in print edition October, 2011

A well-known statement says that the PID controller is the "bread and butter†of the control engineer. This is indeed true, from a scientific standpoint. However, nowadays, in the era of computer science, when the paper and pencil have been replaced by the keyboard and the display of computers, one may equally say that MATLAB is the "bread†in the above statement. MATLAB has became a de facto tool for the modern system engineer. This book is written for both engineering students, as well as for practicing engineers. The wide range of applications in which MATLAB is the working framework, shows that it is a powerful, comprehensive and easy-to-use environment for performing technical computations. The book includes various excellent applications in which MATLAB is employed: from pure algebraic computations to data acquisition in real-life experiments, from control strategies to image processing algorithms, from graphical user interface design for educational purposes to Simulink embedded systems.

#### How to reference

In order to correctly reference this scholarly work, feel free to copy and paste the following:

Tom Wanjekeche, Dan V. Nicolae and Adisa A. Jimoh (2011). Cascaded NPC/H-Bridge Inverter with Simplified Control Strategy and Superior Harmonic Suppression, MATLAB - A Ubiquitous Tool for the Practical Engineer, Prof. Clara Ionescu (Ed.), ISBN: 978-953-307-907-3, InTech, Available from:

http://www.intechopen.com/books/matlab-a-ubiquitous-tool-for-the-practical-engineer/cascaded-npc-h-bridge-inverter-with-simplified-control-strategy-and-superior-harmonic-suppression

#### InTech Europe

University Campus STeP Ri Slavka Krautzeka 83/A 51000 Rijeka, Croatia Phone: +385 (51) 770 447

Fax: +385 (51) 686 166 www.intechopen.com

#### InTech China

Unit 405, Office Block, Hotel Equatorial Shanghai No.65, Yan An Road (West), Shanghai, 200040, China 中国上海市延安西路65号上海国际贵都大饭店办公楼405单元

Phone: +86-21-62489820 Fax: +86-21-62489821 © 2011 The Author(s). Licensee IntechOpen. This is an open access article distributed under the terms of the <u>Creative Commons Attribution 3.0</u> <u>License</u>, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.