# We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

6,900

186,000

200M

Downloads

154

Countries delivered to

Our authors are among the

TOP 1%

most cited scientists

12.2%

Contributors from top 500 universities

#### WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected.

For more information visit www.intechopen.com

# Performance Improvement of CMOS APS Pixels using Photodiode Peripheral Utilization Method

Suat U. Ay University of Idaho USA

#### 1. Introduction

Charge-coupled device (CCD) technology had been leading the field of solid-state imaging for over two decades, in terms of production yield and performance until a relatively new image sensor technology called active pixel sensor (APS) (Fossum, 1993), using existing CMOS facilities and processes, emerged as a potential replacement in the early 1990s. While CMOS APS technology was originally considered inferior, continuous improvements in cost, power consumption (Cho et al., 2000), dynamic range (Gonzo et al., 2002), blooming threshold, readout scheme and speed (Krymsky et al.,1999), low supply voltage operation (Cho et al., 2000), large array size (Meynants, 2005), radiation hardness (Eid et al., 2001), and smartness have achieved performance equal to or better than CCD technology (Agranov et al., 2005; Krymsky et al., 2003).

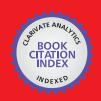

Electro-optical performance of a photodiode (PD) type APS pixel is directly related to physical properties of photodiode diffusion layer. Doping concentration, junction depth, junction grading, biasing conditions, and physical shape of the photodiode diffusion layer determine the pixel full-well capacity, which is one of the main performance benchmarks of the PD-APS pixel. Pixel full-well capacity is related to sensitivity, charge capacity, charge saturation, dynamic range, noise performance, and the spectral response of the pixel (Theuwissen, 1995). Pixel dynamic range versus full well capacity for different pixel noise levels could be plotted as shown on Fig. 1. Thus, increasing full well capacity is desirable. In this chapter, so called photodiode peripheral utilization method (PPUM) is introduced addressing performance improvement of photodiode type CMOS APS pixels, (Ay, 2008). PPUM addresses the improvement of the metrics full well capacity and spectral response especially in blue spectrum (short wavelength). First, identification of junction and circuit parasitics and their use in improving the full-well capacity of a three-transistor (3T) PD-APS pixel through photodiode peripheral capacitance utilization is discussed. Next, spectral response improvement of PD-APS pixels by utilizing the lateral collection efficiency of the photodiode junction through PPUM is discussed. The PPUM method and its proposed benefits were proven on silicon by designing a multiple-test-pixel imager in a 0.5µm, 5V, 2P3M CMOS process. Measurement results and discussions are presented at the end of the chapter.

Fig. 1. Pixel dynamic range versus full well capacity and noise floor.

# 2. Photodiode Peripheral Utilization Method (PPUM)

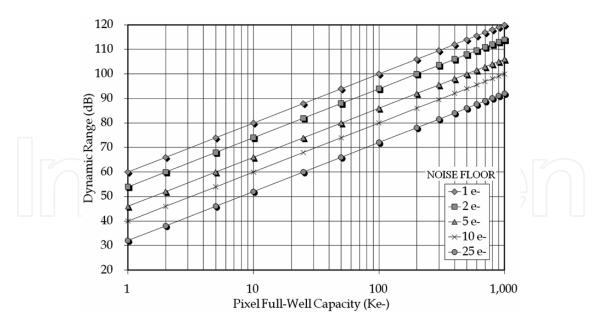

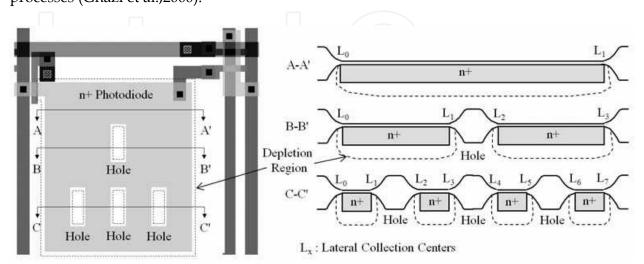

The theory behind the photodiode peripheral utilization method (PPUM) is that, if the pixel pitch is restricted to a certain size, then pixel full-well capacity could be increased by opening holes in the photodiode's diffusion. These diffusion holes could be used to increase photodiode parasitic capacitance, by increasing the perimeter capacitance of the photodiode for certain process technologies shown on Fig 2. Diffusion holes also can increase spectral response of a photodiode by utilizing lateral collection of charges converted close to the semiconductor surface at the edges of photodiode, (Fossum, 1999; Lee and Hornsey, 2001).

Fig. 2. Unit junction capacitance of CMOS processes, (Ay, 2004).

A reverse-biased PN-junction diode is used in photodiode (PD) type CMOS APS pixels as a photon conversion and charge (electron) storage element. The total capacitance of the photodiode diffusion layer determines key pixel performance parameters. For example, wide-dynamic-range pixels require large pixel full-well capacity and low readout noise. Photodiode full-well capacity is comprised of two components: bottom plate (area) and side wall (peripheral) junction parasitic capacitance. Designer controls the size of the photodiode diffusion bottom plate, while peripheral junction depth and doping concentration are process and technology dependent. The photodiode's unit area junction capacitance (C<sub>A</sub>) and unit peripheral junction capacitance (C<sub>P</sub>) are given in the following equations, (Theuwissen 1995), including technology and design parameters, for the first-order capacitance that contributes to total well capacity.

$$C_{PD} = C_A \cdot A + C_P \cdot P \tag{1}$$

$$C_{PD} = \frac{C_{J0A} \cdot A}{\left[1 - \frac{V_{PD}}{\Phi_B}\right]^{MJ}} + \frac{C_{J0SW} \cdot P}{\left[1 - \frac{V_{PD}}{\Phi_{BSW}}\right]^{MJSW}}$$

(2)

where

C<sub>A</sub>, C<sub>P</sub> unit area junction capacitance and unit peripheral junction capacitances,

respectively;

C<sub>J0A</sub>, C<sub>J0SW</sub> unit zero-bias area and peripheral junction capacitances, respectively;

A, P area and peripheral of the photodiode regions, respectively;  $\Phi_{B}$ ,  $\Phi_{BSW}$  built-in potential of area and side-wall junctions, respectively;

M<sub>J</sub>, M<sub>JSW</sub> junction grading coefficients of area and side-wall junctions, respectively;

V<sub>PD</sub> photodiode junction voltage.

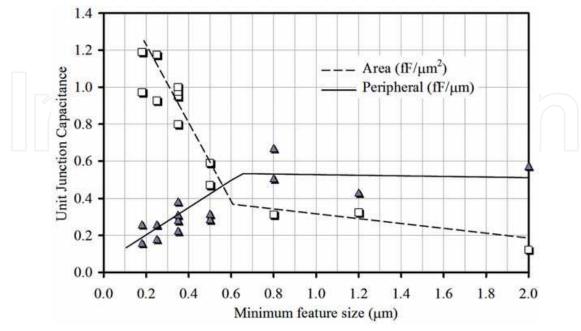

Other parasitic capacitances due to the reset and readout transistors in pixel contributing to total photodiode junction capacitance are shown in Fig. 3. for a three-transistor (3T) PD-APS pixel. These parasitic capacitances contribute to total pixel capacitance differently in different modes of pixel operation, (Ay, 2004). Right after photodiode reset and during scene integration periods, overlap capacitances  $C_{O1}$  and  $C_{O2}$  and gate-to-body capacitance of the

Fig. 3. Parasitic capacitances of photodiode type CMOS APS pixel.

readout transistor M2 ( $C_{B2}$ ) add to the total photodiode capacitance. During a readout period, miller capacitance  $C_{M2}$  and overlap capacitances  $C_{O1}$  and  $C_{O2}$  contribute to the total photodiode capacitance. Contribution of pixel circuit parasitic capacitances is described by the following equations during imaging (3) and readout (4):

$$C_{\text{par,imaging}} = \left[ W_{\text{M1}} \cdot L_{\text{OL,M1}} + W_{\text{M2}} \cdot \left[ L_{\text{M2}} - L_{\text{OL,M2}} \right] \right] \cdot C_{\text{OX}}$$

(3)

$$C_{\text{par,read}} = \left[\frac{2}{3} \cdot W_{\text{M2}} \cdot \left[L_{\text{M2}} - 2 \cdot L_{\text{OL,M2}}\right] \cdot \left[1 - G\right]\right] \cdot C_{\text{OX}}$$

(4)

$$+\left[W_{M1}\cdot L_{OL,M1}+W_{M2}\cdot L_{OL,M2}\cdot\left[2-G\right]\right]\cdot C_{OX}$$

where

$W_1, W_2$  channel width of the reset and source-follower transistors, respectively;  $L_{OL1}, L_{OL2}$  channel overlap length of the reset and source-follower transistors,

respectively;

C<sub>OX</sub> unit oxide capacitance,

G pixel source follower gain factor.

$C_A$  and  $C_P$  of a few CMOS process technologies, with minimum feature sizes 2.0µm–0.18µm, is shown in Fig. 2., (Ay, 2004). Unit-area capacitance is larger for deep sub-micron devices with a minimum feature size <0.5µm, due to the increased channel-stop doping-level (for better device isolation, higher diffusion doping concentrations, and shallower junction depths) (Packan, 2000). Thus, peripheral junction capacitance could be better utilized in processes that have equal or more unit peripheral junction capacitances than in processes with <0.5µm feature sizes, by opening holes in the photodiode region. As will be shown in the next sections, this will not only improves the total full-well capacity of the pixel, but also improves the spectral response for detecting short wavelength photons.

## 3. Photodiode lateral collection improvement

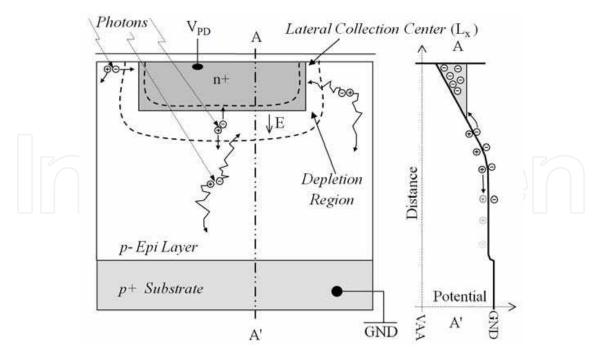

The photosensitive element in APS pixels, the photodiode (PD), works in charge integration-mode where pixels are accessed at the end of a time interval called the integration period. When it is accessed, photodiode is read and then cleared for next scene integration. Fig. 4. shows the cross-section of a PN-junction photodiode formed in a CMOS process; the photodiode is reverse-biased and formed by using the shallow N+ doped, drain-source diffusion of an NMOS device. A bias voltage applied to the N+ region forms a depletion region around the metallurgical PN-junction, which is free of any charge because of the electrical field. Any electron-hole pairs generated in this region see the electrical field as shown in the AA' cross-section view of the photodiode in Fig.4. Electrons move in the opposite direction of the electric field (toward the N+ region), while holes move toward the P-region. As a result, electrons are collected in a charge pocket in the N+ region, while holes are recombined in the substrate. This type of photodiodes has been widely used in CMOS and early CCD-type image sensors as a photo conversion and collection element.

There are two issues associated with using the N+ drain/source diffusion of an NMOS transistor as photosensitive element. First is the dark current induced by stress centres around the diffusion, (Theuwissen 1995). These stress centres are formed during the field

Fig. 4. a)Cross-section and b)potential-well diagram of a PN-photodiode.

oxide (FOX) formation in standard CMOS processes. The second issue is the surface-related dark current generated from the work function difference between the N+ diffusion surface and overlaying isolation oxide layer. This second one causes surface recombination centers and defects. Both of them absorb photo-generated electron-hole pairs close to the surface, resulting in quantum loss at shorter wavelengths. As a result, silicon photodiodes show less sensitivity in the blue spectrum (<400nm. Most blue photons are collected through lateral diffusion of the carriers generated on or in the vicinity of a photodiode peripheral—known as peripheral photoresponse or lateral photocurrent (Lee et al., 2003). Thus, increasing lateral collection centers or peripheral length of a photodiode potentially improves collection efficiency for short-wavelength photons (Fossum, 1999; Lee et al., 2001) as it is depicted in Fig. 5. This method was adopted for UV photodiode devices in P-well CMOS processes (Ghazi et al., 2000).

Fig. 5. Improving lateral collection by increasing photodiode peripheral for blue photons.

# 4. CMOS pixel design using PPUM

There are many ways to test CMOS imaging pixels using test vehicles. Some uses product grade imager platforms to test not only the performance of the imaging pixels, but also their performance in final product environment. Some uses very small array of dumb pixels to measure basic characteristics of the pixel under investigation. A commonly used architecture is called fully flexible open architecture (FFOA) that composes of sample and hold circuits, correlated double sampling (CDS) and differential delta sampling (DDS) circuits, and source follower amplifiers (Nixon et al, 1996; Mendis et al., 1997). Simple FFOA architecture gives very reliable and predictable signal path characteristics. It also allows multiple pixel types with different sizes to be integrated on the same chip.

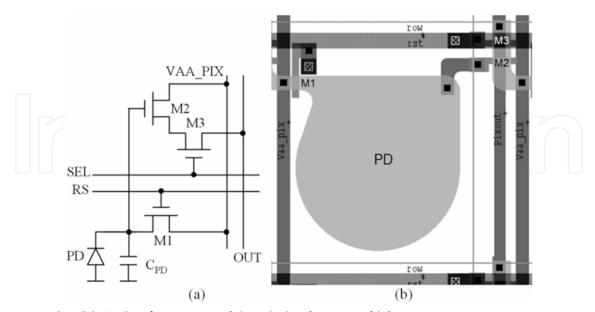

A test imager was designed containing reference and pixels utilizing PPUM as proof of concept. The reference or baseline three-transistor (3T) photodiode type (PD) APS reference pixel (REF) is shown in Fig. 6. It was designed to normalize measurement results of the test pixels with diffusion holes. A fairly large pixel size of  $18\mu m \times 18\mu m$  was chosen. It has circular-looking photodiode diffusion region for reducing overall dark current. Row select and reset signals were drawn on top of each other using horizontal metal-2 and metal-3 lines, and metal-1 was used on the vertical direction for routing pixel output and supply signals.

The reference photodiode diffusion area and peripheral were  $141.7\mu m2$  and  $44.6\mu m$ , respectively. Unit area and peripheral capacitance of the photodiode's N+ diffusion layer in used process were  $0.25fF/\mu m2$  and  $0.22fF/\mu m$ , respectively. Total pixel capacitance was calculated by including the Miller contribution of the source-follower transistor (M2) and other parasitic capacitances from equations (3) and (4). Miller contribution to the total photodiode capacitance at 0.75 source-follower gain was calculated to be 1.1fF; peripheral junction capacitance made up of 20 percent of the total photodiode capacitance, and the total calculated photodiode capacitance was about 47.5fF.

Fig. 6. 3T CMOS APS reference pixel (REF) a) schematic, b) layout.

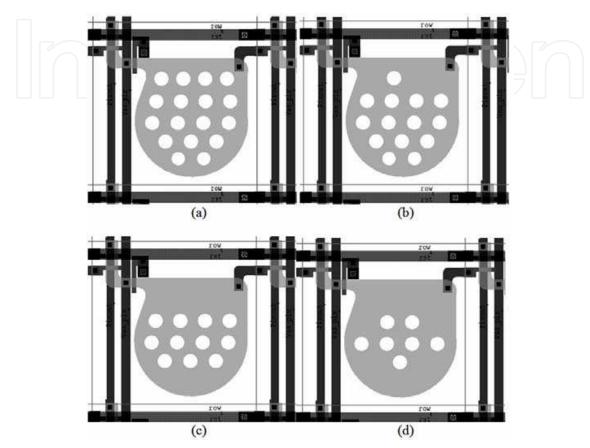

Four test pixels with a number of circular diffusion openings were designed to model the peripheral utilization effect on pixel performance, with layouts shown in Fig. 7. Pixels have

1.6µm-diameter circular holes on the photodiode diffusion with the same base as the reference pixel (REF). The total number of circular diffusion holes was 17, 14, 11, and 7 for pixel layouts called c17, c14, c11, and c7, respectively. Holes were randomly placed on the reference design. Again, the circular shape was chosen for holes to reduce stress-related dark current.

Fig. 7. Test pixels with circular openings; a) c17, b) c14, c) c11, d) c7

# 5. CMOS APS imager design

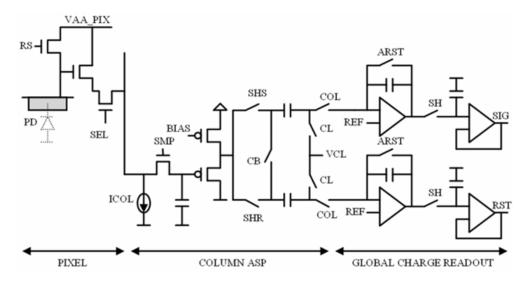

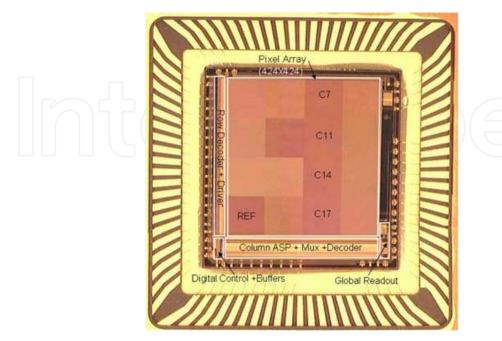

All test pixels were placed in the same imager to compare performance under common imaging and environmental conditions. Single-channel serial-readout architecture was adopted to pass all pixel signals through the same signal path for accurate comparison of the effects (Ay et al., 2002). Imagers were composed of a 424x424 pixel array, row decoder and drivers, timing generators, digital and analog buffers, a column analog signal processor (ASP), a column decoder and multiplexer, and a single, global readout channel. The pixel array was divided in to 16 different subsections with 106 x 106 pixel arrays, with different pixel designs in each subsection. A shift-register type decoder was used in the column, too. Decoder control signals were generated in the timing generator block separately for frame operation. A pseudo-differential charge amplifier and sample-and-hold circuits were used in the global readout block. Chip outputs were in differential analog signals (SIG) and reset (RST). Signal analog-to-digital conversion used an analog-frame-grabber card.

A detailed schematic of the prototype imager's analog signal chain is shown in Fig. 8. Each column contains a PMOS source follower, two sample-and-hold capacitors and a number of

switches. A PMOS source follower was used for level shifting and signal amplification. Column signals were read during column time through single channel, pseudo-differential charge amplifiers and buffered for off-chip analog-to-digital conversion.

Fig. 9. shows a microphotograph of the prototype imager. The prototype was designed in  $0.5\mu m$ , 5V, 2P3M CMOS process, and different test pixel quadrants could be recognized on the pixel array with the naked eye. Table 1 provides specifications for the prototype imager. Global charge amplifier gain was adjusted so that the gain-loss in pixel and column source followers balanced to achieve unity gain from pixel-to-chip output. Operating at 5 Mp/s readout speed, the prototype achieved a 30-frame per second (FPS) frame rate. A 5V supply was used and the total power consumption of the chip was <200mW. Noise floor of the readout channel was  $850\mu V$ .

Fig. 8. Analog signal chain from pixel to chip output.

Fig. 9. Micrograph of Prototype CMOS APS imager chip.

| Array Size                       | 424 x 424           |

|----------------------------------|---------------------|

| Pixel Size                       | 18 μm x 18 μm       |

| Pixel Type                       | 3T Photodiode APS   |

| Technology                       | 0.5 μm CMOS (2P3M)  |

| Output Format                    | Differential Analog |

| Frame Rate                       | 30 FPS              |

| Gain (photodiode to chip output) | 1.0 V/V             |

| Noise Floor                      | 850 μVolt           |

| Fixed Pattern Noise (FPN)        | < 0.25 (% Vsat)     |

| Power Supply (VAA,VAA PIX)       | 5 Volt              |

| Power Consumption                | < 200 mWatts        |

| Package                          | PGA 84L             |

| Chip Size                        | 9.75 mm x 9.75 mm   |

Table 1. Design specifications of the prototype CMOS imager

#### 6. Measurement results

Electrical and optical characteristics of reference and circular-opening test pixels measured under the same environmental and imaging conditions, (Ay, 2004). Having them integrated on same focal plane array make these measurements more manageable and easy.

#### 6.1 Reference pixel measurements

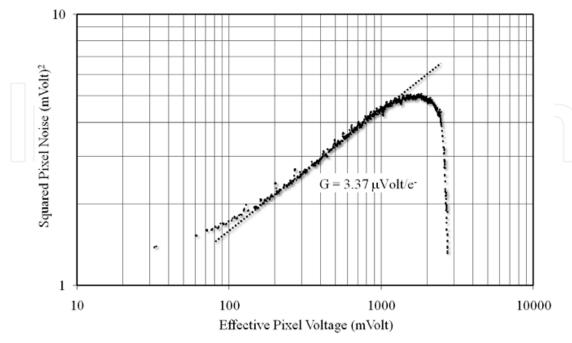

Dark current was measured at room temperature. It was 10.63 mVolt per second. This equals to 3155 e-/sec with the measured conversion gain of 3.37  $\mu$ Volt per electrons. Measured photon transfer curve of the reference pixel is shown in Fig. 10. Total measured pixel capacitance was 47.5 fF as oppose to the calculated value of 46.5fF. Measured pixel full-well capacity was 508Ke- with 1.714V effective photodiode voltage.

Fig. 10. Measured photon transfer curve of the reference pixel (REF1).

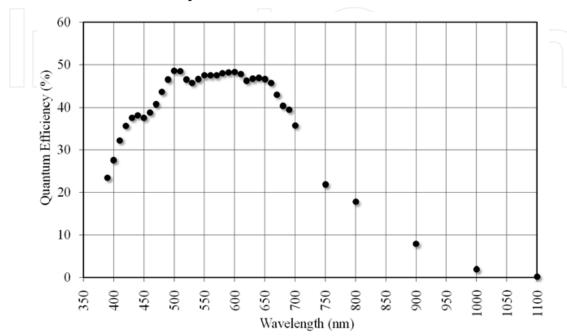

Measured light sensitivity was 2.44 Volt/Lux\*sec while peak quantum efficiency was 48.55 percent at 500nm as shown in Fig.11. At 400nm, quantum efficiency of the reference pixel was 23.4 percent. Dynamic range of the reference pixel was around 66.4 dB because of the higher noise floor measured. Rest of the measurement and calculations are listed in Table 2 for the reference pixel (REF1). All measurements of the test pixels with diffusion holes are normalized with the reference pixel characteristics.

Fig. 11. Measured quantum efficiency of the reference pixel (REF1).

| Parameter          | Measured | Calculated | Unit         |

|--------------------|----------|------------|--------------|

| Sensitivity        | 2.44     |            | Volt/lux.sec |

| Light Saturation   | 1.07     |            | lux.sec      |

| Saturation Voltage | 2.74     |            | Volt         |

| Quantum Efficieny  | 23.41    |            | at 390nm     |

|                    | 47.44    |            | at 550nm     |

|                    | 48.55    |            | peak         |

| Conversion Gain    | 3.370    | 3.446      | μV/e-        |

| Full Well          | 1.714    | 1.714      | Volt         |

|                    | 508,736  | 497,530    | e-           |

| Pixel Capacitance  | 47.54    | 46.49      | fF           |

| Dark Current       | 10.63    |            | mVolt/sec    |

|                    | 3155     |            | e-/sec       |

| Dynamic Range      | 66.39    | 79.67      | dB           |

Table 2. Calculated and measured parameters of the reference pixel (REF1).

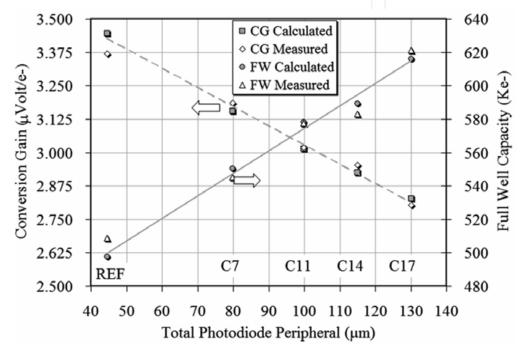

## 6.2 Conversion gain and pixel full-well capacity measurements

Conversion gain and the full-well saturation voltage of the reference and test pixels were measured to determine pixel well capacity. Measurement results are shown in Fig. 12. Pixel

well capacity increases with proper utilization of the photodiode peripheral junction, by using the holes on the photodiode diffusion region. Conversion gain of the pixel reduces with increased pixel capacitance, and the pixel full-well capacity increases.

It was observed that a linear correlation between total peripheral capacitance and pixel full-well capacity exist, because  $C_A$  is almost equal to  $C_P$  in the process used. The area loss was compensated for by the peripheral increase, by a factor of 2.5. Because the radius of the opening was set to  $0.8\mu m$ , and the opening peripheral was ( $p = 2\pi r$ )  $5.027\mu m$  while the area was ( $p = 2\pi r$ )  $p = 2\pi r$ 0. A factor of four could easily be achieved by choosing an opening radius of approximately  $p = 2\pi r$ 1. However, reducing diameter results in depletion region overlap, and lowers peripheral capacitance and utilization.

Fig. 12. Conversion gain and full-well capacity of the pixels.

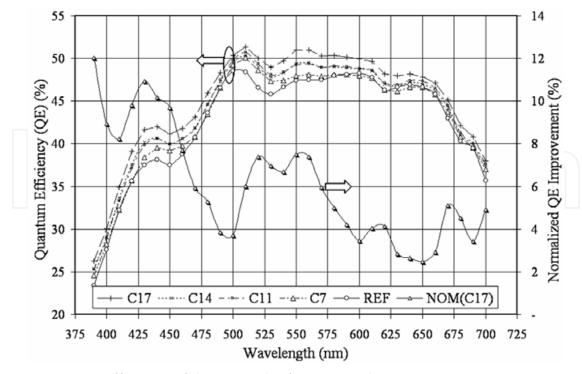

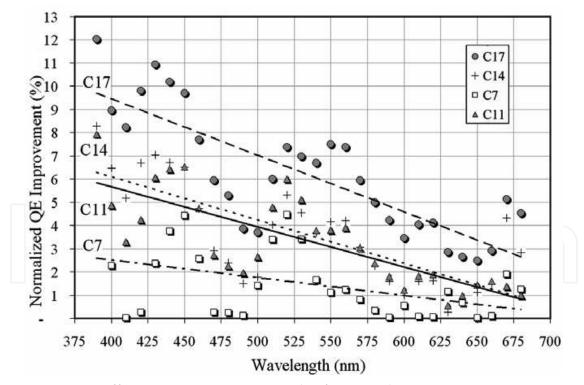

#### 6.3 Quantum Efficiencies (QE)

Quantum efficiencies (QE) of the reference (REF) and test pixels were measured by using a very stable light source, a monochromator, and a calibrated photodiode. Measurement was performed between 390nm and 700nm, with 10nm steps. QE measurement results for reference (REF) and test pixels (c17, c14, c11) are shown in Fig. 13. In the figure, QE difference between the reference pixel and a test pixel with 17 openings (c17), normalized by reference QE, was also plotted. Spectral response improvement was observed with an increased number of openings on the photodiode. The most improvement was achieved at the shorter wavelengths and large number of openings, which is more visible in Fig. 14. Blue photons generated as electron-hole pairs close to the surface of the silicon were collected better laterally at close surroundings of the photodiode area. By adding circular openings these lateral collection areas were increased, which leads to a better QE response at shorter wavelengths. However, deep-penetrating photon collection probability did not increase as much as that of surface photons, giving less improvement in longer wavelengths.

Fig. 13. Quantum efficiency of the test and reference pixels.

Fig. 14. Quantum efficiency improvement trends of test pixels.

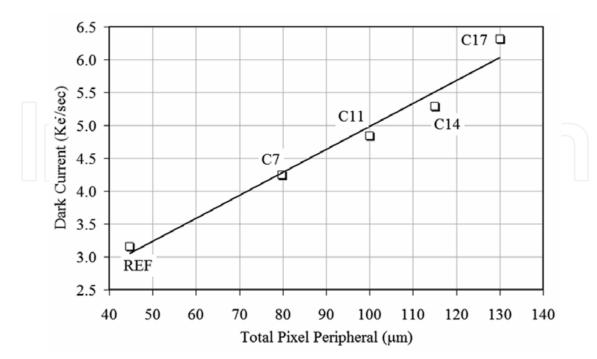

# 6.4. Dark current

Measured dark current for the reference pixel was 10.63 mV/s at room temperature, or 3155 e-/s with the measured conversion gain of  $3.37\mu\text{V}$  per electron. More dark current was

observed from the test pixels with longer peripherals than the reference pixel, as shown in Fig. 15. Dark current, in terms of electrons per second, increases by approximately one-third of the reference dark electrons when the photodiode peripheral doubles (assuming the surface dark current effect was neglected).

In reality, measured dark current has two components, surface dark current and stress-center- related dark current. Surface dark current is related to the area of the photodiode, while stress-center-based dark current is related to the peripheral region. Opening a hole on a photodiode region reduces the surface contribution and increases the peripheral contribution on the total dark current. It is possible to determine the contribution of these two components of the dark current by designing fixed-area and varying-peripheral test pixels.

Dark current also increases noise floor effectively working against the gain achieved by PPMU method. In current design this contribution was not observed because the readout noise was larger than the dark current shot noise in low light condition. Measured dynamic range was around 66dB due to the higher readout channel noise. Dark current electrons add up on pixel capacity, yet, their contribution is less that 0.5% of the full well in worst case.

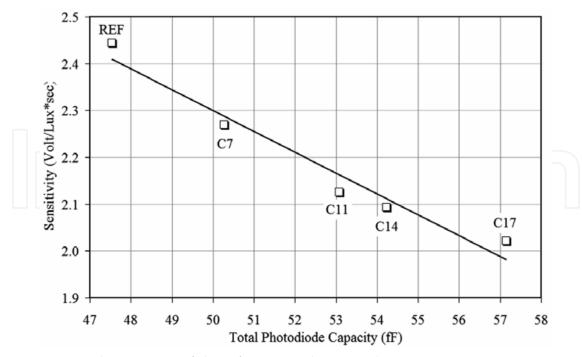

### 6.5 Sensitivity

Sensitivity of the test and reference pixels were measured with a very sharp green (550nm ±20nm) bandpass filter at 175ms integration time. Measurement results are shown in Figure 13. Sensitivity's correlation with pixel capacity was extracted by fixing the light wavelength, pixel fill factor, and integration time. It was observed that the higher the pixel capacity, the lower the sensitivity was, for an inverse correlation. A 20 percent increase in pixel capacity causes a 17 percent decrease in pixel sensitivity between reference and test pixels with 17 openings, as shown in Fig. 16.

Fig. 15. Measured dark current rates of reference and test pixels.

Fig. 16. Measured sensitivity of the reference and test pixels.

#### 7. Conclusion

Photodiode-type CMOS APS pixels' quantum efficiency was improved by opening number of circular holes on the photodiode diffusion area of a prototype imager. A method called photodiode peripheral utilization method (PPUM) was developed to accommodate pixel performance improvement in a fixed size pixel. Utilizing PPUM, four test pixels with 7, 11, 14, and 17 circular openings, and a reference pixel (REF), were designed, fabricated, and tested in a prototype APS imager made with a  $0.5\mu m$ , 5V, 2P3M CMOS process. Measured pixel characteristics are summarized in Table 3.

| Pixel Design                | C17   | C14   | C11   | C7    | REF   | Unit                      |

|-----------------------------|-------|-------|-------|-------|-------|---------------------------|

| PD Area                     | 107.5 | 113.5 | 119.6 | 127.6 | 141.7 | μm²                       |

| PD Peripheral               | 130.1 | 115.0 | 99.9  | 79.8  | 44.6  | μm                        |

| Dark Current                | 6.31  | 5.29  | 4.84  | 4.25  | 3.15  | Ke-/sec.                  |

| Conversion Gain             | 2.80  | 2.95  | 3.02  | 3.19  | 3.37  | μVolt/e-                  |

| Quantum Efficieny           | 26.22 | 25.34 | 25.26 | 24.58 | 23.41 | % @ 390nm                 |

|                             | 51.00 | 49.41 | 49.24 | 47.97 | 47.44 | % @ 550nm                 |

|                             | 51.31 | 50.35 | 50.72 | 50.05 | 48.55 | % @ peak                  |

| QE improvement              | 12.0  | 8.3   | 7.9   | 5.0   | 0.0   | %QE <sub>REF</sub> @390nm |

|                             | 7.5   | 4.2   | 3.8   | 1.1   | 0.0   | %QE <sub>REF</sub> @550nm |

| Sensitivity                 | 2.02  | 2.09  | 2.13  | 2.27  | 2.44  | Volt/Lux.sec              |

| Pixel Full-Well Depth       | 621.4 | 583.1 | 577.6 | 545.2 | 508.7 | Ke-                       |

| Pixel Full-Well Improvement | 22.1  | 14.6  | 13.5  | 7.2   | 0.0   | %FW <sub>REF</sub>        |

| Pixel Capacitance           | 57.1  | 54.2  | 53.1  | 50.3  | 47.5  | fF                        |

Table. 3. Key measured pixel parameters and improvements

#### 8. References

- Agranov, G., Gilton, T., Mauritzson, R., Boettiger, U., Altice, P., Shah, J., Ladd, J., Fan, X., Brady, F., McKee, J., Hong, C., Li, X., Patrick, I. (2005). Optical-electrical characteristics of small, sub-4µm and sub-3µm pixels for modern CMOS Image Sensors, *Proceedings of IEEE Workshop on CCDs and Advanced Image Sensors*, R-31, Tokyo, Japan, June 2005.

- Ay, S. U., Lesser, M., Fossum, E. R., (2002). CMOS Active Pixel Sensor (APS) Image sensor for Scientific Applications, in Survey and Other Telescope Technologies and Discoveries, *Proceedings of SPIE*, vol. 4836, pp. 271-278, 2002, ISBN: 9780819446152.

- Ay, S. U. (2004). *Design Issues and Performance of Large Format Scientific CMOS Image Sensors*, University of Southern california, Ph.D. Thesis, OCLC:65169363.

- Ay, S. U. (2008). Photodiode peripheral utilization effect on CMOS APS pixel performance, *IEEE Transactions on Circuit and Systems I*, vol.55, no.6, pp.1405-1411, ISSN 1549-8328.

- Cho, K.-B., Krymsky, A. I., Fossum, E. R. (2000). A 1.2 V Micropower CMOS Active Pixel Image Sensor for Portable Applications, *Digest of Technical Papers IEEE International Solid-State Circuits Conference (ISSCC)*, pp.114-115, ISSN 78035853-8, San Francisco, CA, 7-9 February 2000.

- Eid, E.-S., Spagnuolo, R., Chan, T. Y., Fossum, E. R., Tsai, R. H., Deily, J., Byers Jr., W. B.; Peden, J. C., (2001). Design and characterization of ionizing radiation-tolerant CMOS APS image sensors up to 30 Mrd (Si) total dose, *IEEE Transactions on Nuclear Science*, vol. 48, no. 6, Dec. 2001, pp. 1796-1806, ISSN 0018-9499

- Fossum, E. R., (1999). *Quantum Efficiency Improvements in Active Pixel Sensors*, US Patent No. 6,005,619, 1999.

- Fossum, E. R. (1993). Active Pixel Sensors: Are CCD's Dinosaurs, in Charge-Coupled Devices and Solid State Optical Sensors III, Proceedings of SPIE, vol. 1990, Feb. 1993, pp. 2-14, ISBN: 9780819411334.

- Ghazi, A., Zimmermann, H., Seegebrecht, P. (2000). CMOS Photodiode With Enhanced Responsivity for the UV/Blue Spectral Range, *IEEE Transaction on Electron Devices*, vol. 49, no. 7, July 2000, pp.1124-1128, ISSN: 0018-9383.

- Gonzo, L., Stopa, D., Simoni, A., and Dalla Betta, G. (2002). Novel CMOS Image sensor with a 132-db dynamic range, *IEEE Journal on Solid State Circuits*, vol. 37, no. 12, December 2002, pp. 1846–1852, ISSN 0018-9200.

- ITRS (1999). *The International Technology Roadmap for Semiconductors*, Semiconductor Industry Association, San Jose, CA, 1999.

- Krymsky, A. I., VanBlerkom, D., Andersson, A., Bock, N., Mansoorian, B., Fossum, E. R. (1999). A high speed, 500 frames/s, 1024×1024 CMOS active pixel sensor, *Digest of Technical Papers* 1999 *Symposium on VLSI Circuits*, pp. 137-138, ISBN: 4930813956, Kyoto, Japan, 17-19 June 1999.

- Krymski, A. I., Khaliullin, N., Rhodes. H. (2003). A 2e- Noise 1.3 Megapixel CMOS Sensor, *Proceedings of IEEE Workshop on CCDs and Advanced Image Sensors*, pp13-18, Elmau, Bavaria, Germany, May 15-17, 2003.

- Lee, J. S., Hornsey, R.I. (2001). CMOS Photodiodes with Substrate Openings for Higher Conversion Gain in Active Pixel Sensors, *Proceedings of IEEE Workshop on CCDs and Advanced Image Sensors*, pp. 173-175, Crystal Bay, Nevada, June 2001.

Lee, J. S., Hornsey, R. I., Renshaw, D. (2003). Analysis of CMOS Photodiodes—Part II: Lateral Photoresponse, *IEEE Transaction on Electron Devices*, vol. 50, no. 5, May 2003, pp. 1239-1245, ISSN:00189383.

- Mendis, S., Kemeny, S. E., Gee, R. C., Pain, B., Kim, Q., Fossum, E. R., (1997). CMOS active pixel image sensors for highly integrated imaging systems, *IEEE Journal of Solid-State Circuits*, vol. 32, no. 2, February 1997, pp. 187-197, ISSN: 00189200.

- Meynants, G., Dupont, B., Witvrouwen, N., Wolfs, B., Schippers, G., Maher, K., Dierickx, B., Lee, B., Arnzen, D., Lee S. (2005). A 9 Megapixel APS-size CMOS image sensor for digital still photography, *IEEE Workshop on CCDs and Advanced Image Sensors*, R-40, Tokyo, Japan, June 2005

- Nixon, R. H., Kemeny, S. E., Pain, B., Staller, C. O., Fossum, E. R., (1996). 256x256 CMOS active pixel sensor camera-on-a-chip, *IEEE Journal of Solid-State Circuits*, vol. 31, no. 12, December 1996, pp. 2046-2050, ISSN:00189200.

- Packan, P.A., (2000). Scaling Transistors into the Deep-Submicron Regime, MRS Bulletin, Volume 25, No. 6, p. 18, June 2000.

- Theuwissen, A.J.P. (1995). *Solid-State Imaging with Charge-Coupled Devices*, Kluwer Academic, ISBN:0792334566, Boston.

Edited by Prof. Gian Franco Dalla Betta

ISBN 978-953-307-163-3 Hard cover, 466 pages Publisher InTech Published online 22, March, 2011 Published in print edition March, 2011

Photodiodes, the simplest but most versatile optoelectronic devices, are currently used in a variety of applications, including vision systems, optical interconnects, optical storage systems, photometry, particle physics, medical imaging, etc. Advances in Photodiodes addresses the state-of-the-art, latest developments and new trends in the field, covering theoretical aspects, design and simulation issues, processing techniques, experimental results, and applications. Written by internationally renowned experts, with contributions from universities, research institutes and industries, the book is a valuable reference tool for students, scientists, engineers, and researchers.

#### How to reference

In order to correctly reference this scholarly work, feel free to copy and paste the following:

Suat U. Ay (2011). Performance Improvement of CMOS APS Pixels using Photodiode Peripheral Utilization Method, Advances in Photodiodes, Prof. Gian Franco Dalla Betta (Ed.), ISBN: 978-953-307-163-3, InTech, Available from: http://www.intechopen.com/books/advances-in-photodiodes/performance-improvement-of-cmos-aps-pixels-using-photodiode-peripheral-utilization-method

# INTECH open science | open minds

#### InTech Europe

University Campus STeP Ri Slavka Krautzeka 83/A 51000 Rijeka, Croatia Phone: +385 (51) 770 447

Fax: +385 (51) 686 166 www.intechopen.com

# InTech China

Unit 405, Office Block, Hotel Equatorial Shanghai No.65, Yan An Road (West), Shanghai, 200040, China 中国上海市延安西路65号上海国际贵都大饭店办公楼405单元

Phone: +86-21-62489820 Fax: +86-21-62489821 © 2011 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the <u>Creative Commons Attribution-NonCommercial-ShareAlike-3.0 License</u>, which permits use, distribution and reproduction for non-commercial purposes, provided the original is properly cited and derivative works building on this content are distributed under the same license.