We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

186,000

200M

Our authors are among the

TOP 1% most cited scientists

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

# Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

# 3-D Quantum Numerical Simulation of Transient Response in Multiple-Gate Nanowire MOSFETs Submitted to Heavy Ion Irradiation

Daniela Munteanu and Jean-Luc Autran IM2NP Laboratory,

CNRS (Centre National de la Recherche Scientifique), Aix-Marseille University France

# 1. Introduction

The bulk MOSFET scaling has recently encountered significant limitations, mainly related to the gate oxide (SiO<sub>2</sub>) leakage currents (Gusev et al., 2006; Taur et al., 1997), the large increase of parasitic short channel effects and the dramatic mobility reduction (Fischetti & Laux, 2001) due to highly doped Silicon substrates precisely used to reduce these short channel effects. Technological solutions have been proposed in order to continue to use the "bulk solution" until the 32 nm ITRS node (ITRS, 2009). Most of these solutions envisage the introduction of high-permittivity gate dielectric stacks (to reduce the gate leakage, (Gusev et al., 2006; Houssa, 2004), midgap metal gate (to suppress the Silicon gate polydepletioninduced parasitic capacitances) and strained Silicon channel (to increase carrier mobility (Rim et al., 1998). However, in parallel to these efforts, alternative solutions to replace the conventional bulk MOSFET architecture have been proposed and studied in the recent literature. These options are numerous and can be classified in general according to three main directions: (i) the use of new materials in the continuity of the "bulk solution", allowing increasing MOSFET performances due to their dielectric properties (permittivity), electrostatic immunity (SOI materials), mechanical (strain), or transport (mobility) properties; (ii) the complete change of the device architecture (e.g. Multiple-Gate devices, Silicon nanowires MOSFET) allowing better electrostatic control, and, as a result, intrinsic channels with higher mobilities and currents; (iii) the exploitation of certain new physical phenomena that appear at the nanometer scale, such as quantum transport, substrate orientation or modifications of the material band structure in devices/wires with nanometer dimensions (Haensch et al., 2006; Hiramoto et al., 2006).

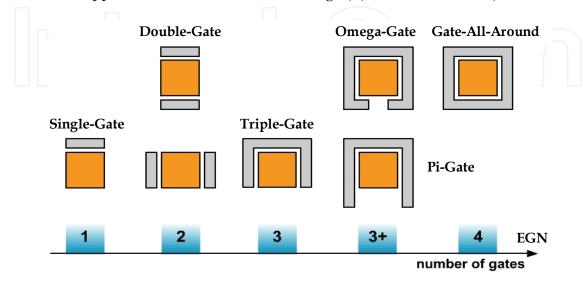

Multiple-Gate nanowire MOS transistors (Fig. 1) are now widely recognized as one of the most promising solutions for meeting the roadmap requirements in the deca-nanometer scale (Park & Colinge, 2002). A wide variety of architectures, including planar Double-Gate (DG) (Frank et al., 1992; Harrison et al, 2004), Vertical Double-Gate, Triple-Gate (Tri-gate) (Guarini et al., 2001; Park & Colinge, 2002), FinFET (Choi et al., 2001; Kedzierski et al., 2002), Omega-Gate ( $\Omega$  -Gate) (Park et al., 2001), Pi-Gate ( $\pi$  -Gate) (Yang et al., 2002),  $\Delta$ -channel SOI MOSFET (Jiao & Salama, 2001), DELTA transistor (Hisamoto et al., 1989), Gate-All-Around (GAA) (Colinge et al., 1990; Park & Colinge, 2002), Rectangular or Cylindrical nanowires

(Jimenez et al., 2004), has been proposed in the literature. These structures exhibit a superior control of short channel effects resulting from an enhanced electrostatic coupling between the conduction channel and the surrounding gate electrode. It has been shown that the electrostatic control is enhanced when increasing the "Equivalent Number of Gates" (EGN) from 2 (for Double-Gate devices, Fig. 1) to 4 (for Gate-All-Around devices where the gate electrode is wrapped around the entire channel, Fig. 1) (Bescond et al., 2004).

Fig. 1. Schematic cross-sections of the Multiple-Gate devices classified as a function of the "Equivalent Number of Gates" (EGN)

The scaling of Multiple-Gate MOSFET requires the use of an increasingly thinner Silicon film, for which new phenomena have to be taken into account, such as quantum-mechanical confinement. These phenomena induce a strong subband splitting and the carrier confinement in the narrow potential well formed by the Silicon film (Taur & Ning, 1998). Quantum effects sensibly modify the three dimensional (3-D) carrier distribution in the channel, the most important effect being the shift of the charge centroid away from the interfaces into the Silicon film. The inversion charge and then the drain current are reduced in the quantum case with respect to the "classical" case (i.e. without quantum effects). Quantum-mechanical confinement is stronger when the film is thinner. It has been shown that the energy quantization becomes important for channels below 10 nm thick, for which it becomes mandatory to take into account quantum effects in the device simulation (Bescond et al., 2004). In Single-Gate or Double-Gate configurations the carriers are confined in a single direction (vertically, perpendicular to the gate electrode and to the source-to-drain axis). In multiple-gate architectures, and especially in Gate-All-Around devices, the quantum-mechanical confinement is stronger because the carrier energy is quantified in two directions (vertically but also horizontally, in both directions perpendicular to the gates electrodes and to the source-to-drain axis). Then, the carrier confinement and its effects (such as the reduction of the total inversion charge) are stronger in Multiple-Gate devices with EGN≥3 than for single-gate or double-gate architectures.

As the MOSFET is scaling down, the sensitivity of integrated circuits to radiation, coming from the natural space or present in the terrestrial environment, has been found to seriously increase (Baumann, 2005; Dodd, 1996; Dodd & Massengill, 2003; Dodd, 2005). In particular, ultra-scaled memory ICs are more sensitive to single-event-upset (SEU) and digital devices

are more subjected to digital single-event transient (DSETs). Single-event-effects (SEE) are the result of the interaction of highly energetic particles, such as protons, alpha particles, or heavy ions, with sensitive regions of a microelectronic device or circuit. These SEE may perturb the device/circuit operation (e.g., reverse or flip the data state of a memory cell, latch, flip-flop, etc.) or definitively damage the circuit (e.g. gate oxide rupture, destructive latch-up events).

Modeling and simulating the effects of ionizing radiation has long been used for better understanding the radiation effects on the operation of devices and circuits. In the last two decades, due to substantial progress in simulation codes and computer performances which reduce computation times, simulation reached an increased interest. Due to its predictive capability, simulation offers the possibility to reduce radiation experiments and to test hypothetical devices or conditions, which are not feasible (or not easily measurable) by experiments. Physically-based numerical simulation at device-level presently becomes an indispensable tool for the analysis of new phenomena specific to short-channel devices (non-stationary effects, quantum confinement, quantum transport), and for the study of radiation effects in new device architectures (such as multiple-gate, Silicon nanowire MOSFET), for which experimental investigation is still limited. In these cases, numerical simulation is an ideal investigation tool for providing physical insights and predicting the operation of future devices expected for the end of the roadmap. A complete description of the modeling and simulation of SEE, including the history and the evolution of this research domain, have been presented in the reference survey papers by Dodd (Dodd, 1996; Dodd & Massengill, 2003; Dodd, 2005) and Baumann (Baumann, 2005).

In a previous work (Munteanu et al., 2006), we investigated the impact of the quantum effects on the transient response of 50 nm gate length Fully-Depleted (FD) Single-Gate MOSFET with 11 nm thick Silicon film. In that work, we found an excellent agreement between experimental bipolar gain values (measured by heavy ions experiments) and simulated bipolar gain obtained by quantum-mechanical simulation. The results were also consistent with experimental data obtained by pulsed laser irradiation performed on 50 nm gate length transistors fabricated with the same technology (Ferlet-Cavrois et al., 2005). The study presented in (Munteanu et al., 2006) illustrated the importance of taking into account quantum effects in the simulation of the device response when submitted to heavy ion irradiation. The simulation results also showed that even if the impact of quantum effects can be considered as limited in these 11 nm thick FD Single-Gate devices, it will become important for thinner films and for double-gate architectures.

The transient response of Multiple-Gate nanowire MOSFETs under heavy ion irradiation has been already addressed (Castellani et al., 2006; Francis et al., 1995), but to the best of our knowledge, all the previous studies considered the "classical" approach. In this work we use 3D quantum numerical simulation for investigating the drain current transient produced by the ion strike in Multiple-gate nanowire MOSFETs with ultra-thin channels ( $\leq 10$  nm). We firstly consider devices with a gate length of 32 nm and 10 nm-thick Silicon film. For these devices we compare the classical and quantum simulation in terms of drain current transient induced by the ion strike, carrier density and bipolar amplification. Three different Multiple-Gate configurations are considered: Double-Gate, Triple-Gate and Gate-All-Around. In a second step, the devices scaling is addressed and the impact of the quantum effects is analyzed for two cases: (a) 32 nm gate length devices with thinner film (8 nm and 5 nm) and (b) completely scaled devices with 25 nm gate length (8 nm thick film) and 20 nm gate length (5 nm thick film). For each point the classical and the quantum results are compared and the differences between the four architectures from the view-point of the devices immunity to heavy ion irradiation are analyzed.

This chapter is organized as follows: section 2 presents a detailed description of simulated devices and section 3 describes the simulation code, including the modelling of quantum confinement effects and the simulation of the effects of an ion strike. Section 4 details the simulation of transient effects in Multiple-Gate MOSFET submitted to heavy-ion irradiation. Static and transient characteristics calculated in both quantum and classical cases are presented and compared. Finally, a detailed study concerns the impact of device scaling on the transient response to radiation effects.

## 2. Simulated devices

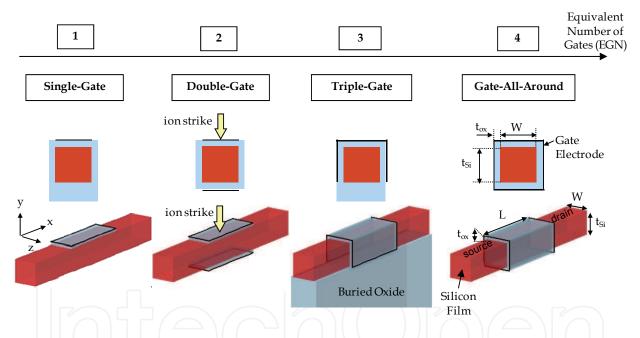

In this work, we simulate square cross-section nanowire Double-Gate, Triple-Gate and Gate-All-Around MOSFETs with 32 nm, 25 nm and 20 nm physical gate lengths. The description of the 3-D architectures considered in the simulation and the definition of their geometrical parameters are represented in Fig. 2.

Fig. 2. Schematic description of the 3-D simulated Double-Gate, Triple-Gate and Gate-All-Around structures and their main geometrical parameters considered in this work. The Single-Gate structure is also shown for comparison. The devices are classified as a function of the "Equivalent Number of Gates" (EGN). The schematic cross-sections in the (y-z) plane are also shown. For all the simulated structures, there is no gate overlap with the S/D regions and the S/D doping concentration is  $10^{20}$ cm<sup>-3</sup>. The position of the ion strike is also indicated by the arrow; the ion strikes vertically in the middle of the channel (between the source and drain region) and in a direction parallel to the y axis. The Silicon substrate was simulated for the Triple-Gate structures. All structures have Silicon film with square section ( $t_{Si}$ =W)

All devices have been calibrated to fill the ITRS requirements for Low Power Technology in terms of drain current in the off-state ( $I_{OFF}$ <5×10-3 A/µm) (ITRS, 2009). The Silicon film and

the gate oxide have the following dimensions: (a)  $t_{Si}$ =W=10 nm and  $t_{ox}$ =1.2 nm for devices with L=32 nm gate length, (b)  $t_{Si}$ =W=8 nm and  $t_{ox}$ =1 nm for devices with L=25 nm and (c)  $t_{Si}$ =W=5 nm and  $t_{ox}$ =0.9 nm for devices with L=20 nm. All devices have intrinsic channel and mid-gap gate, and the thickness of the buried oxide is 100 nm. The supply voltage is 0.8 V for devices with L=32 nm and L=25 nm and 0.7 V for devices with L=20 nm.

# 3. Description of the simulation code

3-D numerical simulations have been performed with both 3-D Sentaurus code (Sentaurus, 2009) and with our full quantum homemade Fortran code BALMOS3D (Munteanu & Autran, 2003). The physical models considered in the Sentaurus code include the SRH and Auger recombination models and the Fermi-Dirac carrier statistics.

Concerning the transport modelling, the drift-diffusion (DD) model was for many years the standard level of solid-state device modelling, mainly due to its simple concept and short simulation times. This approach is appropriate for devices with large feature lengths. This model considers that carrier energy does not exceed the thermal energy and carrier mobility is only a local function of the electric field (mobility does not depend on carrier energy). These assumptions are acceptable as long as the electric field changes slowly in the active area, as is the case for long devices (Munteanu & Autran, 2008). When the device feature size is reduced, the electronic transport becomes qualitatively different from the DD model since the average carrier velocity does not depend on the local electric field. In short devices steep variations of electric field take place in the active area of the devices. Then, nonstationary phenomena occur following these rapid spatial or temporal changes of high electric fields. Since these phenomena play an important role in small devices, new advanced transport models become mandatory for accurate transport simulation. The hydrodynamic model, obtained by taking the first three moments of the Boltzmann Transport Equation (BTE), represents the carrier transport effects in short devices more accurately than the DD model. The hydrodynamic model is a macroscopic approximation to the BTE taking into account the relaxation effects of energy and momentum. This model removes several limiting assumptions of DD: the carrier energy can exceed the thermal energy and all physical parameters are energy-dependent (Munteanu & Autran, 2008). In this work we use the hydrodynamic model for the transport modelling. Then, both the impact ionization and the carrier mobility depend on carrier energy calculated with the hydrodynamic model. The mobility model also includes the dependence on the lattice temperature and on the channel doping level. The mobility also depends on the doping level and the lattice temperature. Quantum confinement effects have been considered in the simulation using the Density Gradient model, as explained in section 3.1.

# 3.1 Modeling of quantum effects

The aggressive scaling-down of bulk MOSFETs in the deep submicrometer domain requires ultrathin oxides and high channel doping levels for minimizing the drastic increase of short channel effects. The direct consequence is a strong increase of the electric field at Si/SiO<sub>2</sub> interface, which creates a sufficiently steep potential well for inducing the quantization of carrier energy (Munteanu & Autran, 2008). In bulk architecture, carriers are then confined in a vertical direction in a quantum well (formed by the Silicon conduction band bending at the interface and the oxide/Silicon conduction band-offset) having feature size close to the electron wavelength. This gives rise to a splitting of the energy levels into subbands (two-

dimensional (2-D) density of states) (Hareland et al., 1998), such that the lowest of the allowed energy levels for electrons (resp. for holes) in the well does not coincide with the bottom of the conduction band (resp. the top of the valence band). In addition, the total density of states in a 2-D system is less than that in a three-dimensional (3-D) (or classical) system, especially for low energies. Carriers occupying the lowest energy levels behave like quantized carriers while those lying at higher energies, which are not as tightly confined in the potential well, can behave like classical (3-D) particles with three degrees of freedom (Munteanu & Autran, 2008). As the surface electric field increases, the system becomes more quantized as more and more carriers become confined in the potential well. The quantummechanical confinement considerably modifies the carrier distribution in the channel: the maximum of the inversion charge is shifted away from the interface into the Silicon film (Munteanu & Autran, 2008). Because of the smaller density of states in the 2-D system, the total population of carriers will be smaller for the same Fermi level than in the corresponding 3-D (or classical) case. This phenomenon affects the net sheet charge of carriers in the inversion layer, thus requiring a larger gate voltage in order to populate a 2-D inversion layer to have the same number of carriers as the corresponding 3-D system. This leads to an increase of the threshold voltage of a MOSFET, which is an important issue, especially as the power supply voltages drop to lower levels. The gate capacitance and carrier mobility are also modified by quantum effects. These considerations indicate that the wave nature of electrons and holes can no longer be neglected in ultra-short devices and have to be considered in simulation studies. Quantum confinement becomes also important for the device response to single events.

Various methods have been suggested to model these quantum effects. Among the approaches that are compatible with classical device simulators based on the drift-diffusion (or hydrodynamic) approach, the physically most accurate method is to include the Schrödinger equation into the self-consistent computation of the device characteristics (Stern, 1972). However, solving the Schrödinger equation in itself is very much time-consuming. Various simpler methods have been suggested, such as the Van Dort model or the Hansch model. The van Dort model (van Dort, 1994) expresses the quantum effect by an apparent band edge shift that is a simple function of the electric field. The model is based on the expression for the lowest eigenenergy of a particle in a triangular potential and reproduces the characteristics obtained with the Schrödinger equation quite well. However, this model does not give the correct charge distribution in the device. The Hansch (Hansch et al., 1989] model proposes a quantum correction of the density of states as a function of depth below the Si/SiO<sub>2</sub> interface. The charge distribution is better reproduced, but the model strongly overestimates the impact of quantum effects on the drain current characteristics.

Other alternative to take into account quantum confinement of carriers is the Density-Gradient model (Ancona & Iafrate, 1989; Grubin et al., 1993; Wettstein & al., 2002), coupled with the Drift-Diffusion or the hydrodynamic transport equations. The Density-Gradient model considers a modified equation of the electronic density including an additional term dependent on the gradient of the carrier density. To include quantization effects in a classical device simulation, a simple approach is to introduce an additional potential-like quantity  $\Lambda$  in the classical electron density formula, as follows (Sentaurus, 2009):

$$n = N_{\rm C} \exp\left(\frac{E_{\rm Fn} - E_{\rm C} - \Lambda}{kT}\right)$$

(1)

72

where n is the electron density, T is the carrier temperature, k is the Boltzmann constant,  $N_C$  is the conduction band density of states,  $E_C$  is the conduction band energy, and  $E_{Fn}$  is the electron Fermi energy. The impact of the quantum confinement on the carrier density in the device can be taken into account by properly modelling the quantity  $\Lambda$ . For the Density Gradient model,  $\Lambda$  is given in terms of a partial differential equation:

$$\Lambda = -\frac{\gamma\hbar}{6m} \frac{\nabla^2 \sqrt{n}}{\sqrt{n}}$$

(2)

where  $\hbar = h/2\pi$  is the reduced Planck constant, m is the density of states mass, and  $\gamma$  is a fit factor. An equation similar to (1) applies for the holes density. These new equations for electrons and holes density are then used in the self-consistent resolution of the Poisson equation and of the transport equation (Drift-Diffusion or hydrodynamic model), as explained in (Munteanu & Autran, 2008).

## 3.2 Calibration of the simulation code

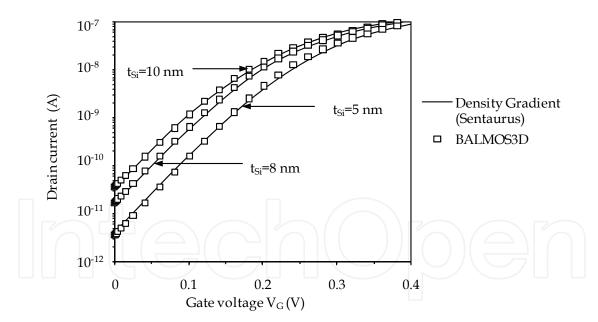

It has been shown that the Density Gradient model can accurately account for quantum carrier confinement in Single-Gate SOI and Double-Gate devices with an appropriate calibration step of the fit factor  $\gamma$  (Wettstein & al., 2002). In this work, we have used the exact solution of the Schrödinger –Poisson system of equations (as given by BALMOS3D) for calibrating the Density Gradient model.

Fig. 3. Calibration of the Density-Gradient model (Sentaurus, 2009) on BALMOS3D. The simulated devices are 32 nm gate length Double-Gate MOSFETs with three Silicon thicknesses ( $t_{Si}$ =10 nm, 8 nm and 5 nm). For better illustration, the figure only shows the subthreshold region of the drain current characteristics. V<sub>D</sub>=0.8 V

BALMOS3D (Munteanu & Autran, 2003) is a homemade full quantum Fortran simulator, which solves self-consistently the Schrödinger equation and the Poisson equations on a 3-D-grid. The solution of this system of equation is coupled with the Drift-Diffusion transport equation in the channel. A finite difference scheme with a non-uniform mesh has been

considered on a 3-D domain, which includes the channel, the source and drain regions, the gate oxide layers and the gate electrodes. Electric field penetration in the source/drain and electron wave-function penetration in the gate oxide can be also taken into account.

A calibration step of the Density Gradient model on BALMOS3D has been performed on each simulated device, for obtaining the fit factor  $\gamma$ . This factor has different values as a function of the film thickness and gate length. For each particular device, the drain current static characteristics as a function of the gate bias,  $I_D(V_G)$ , has been computed with BALMOS3D. The same device (with identical geometry) has been implemented in the 3D Sentaurus code and its  $I_D(V_G)$  characteristic has been simulated, taken into account the Density Gradient model. The fit factor  $\gamma$  has been then finely tuned in order to obtain a perfect match between the characteristics calculated with BALMOS3D and that simulated by Sentaurus. Figure 3 shows an example of the calibration step on 32 nm gate length Double-Gate MOSFET with three different Silicon film thicknesses.

## 3.3 Modeling the effect of a particle strike

The physical parameters calibrated previously have been further used in the simulation of drain current transients produced by an ion strike on the sensitive regions of the device. The drain current transients have been simulated in two cases: the classical case (i.e. without quantum effects) and in the quantum case (using Density Gradient model with the fit factor  $\gamma$  as calibrated on BALMOS3D).

The radiation effects have been simulated using the HeavyIon module (Sentaurus, 2009), considering an electron-hole pair column centred on the ion track axis to model the ion strike. The ion track structure to be used as input in simulation is presently a major issue for device simulation. The first representations included a simple cylindrical charge generation with a uniform charge distribution and a constant LET along the ion path. However, the real ion track structure is radial and varies as the particle passes through the matter. When the particle strikes a device, highly energetic primary electrons (called  $\delta$ -rays) are released. They further generate a very large density of electron-hole pairs in a very short time and a very small volume around the ion trajectory, referred as the ion track. These carriers are collected by both drift and diffusion mechanisms, and are also recombined by different mechanisms of direct recombination (radiative, Auger) in the very dense core track, which strongly reduces the peak carrier concentration. All these mechanisms modify the track distribution both in time and space. As the particle travel through the matter, it loses energy and then the  $\delta$ -rays become less energetic and the electron-hole pairs are generated closer to the ion path. Then, the incident particle generates characteristic cone-shaped charge plasma in the device (Dodd, 2005).

The real ion track structure has been calculated using Monte-Carlo methods (Hamm et al., 1979; Martin et al., 1987; Oldiges et al., 2000). These simulations highlighted important differences between the track structure of low-energy and high-energy particles, even if the LET is the same (for details see (Dodd et al., 1998; Dodd, 2005)). High-energy particles are representative for ions existing in the real space environment, but they are not available in typical laboratory SEU measurements (Dodd, 1996). Then the investigation of the effects of high-energy particles by simulation represents an interesting opportunity, which may be difficult to achieve experimentally.

Analytical models for ion track structure have been also proposed in the literature and implemented in simulation codes. One of the most interesting models is the "non-uniform

74

power law" track model, based on the Katz theory (Kobetich & Katz, 1968) and developed by Stapor (Stapor & McDonald, 1988). In this model, the ion track has a radial distribution of excess carriers expressed by a power law distribution and allows the charge density to vary along the track (Dussault et al., 1993). Other analytical models propose constant radius nonuniform track or Gaussian distribution non-uniform track.

In commercial simulation codes, the effect of a particle strike is taken into account as an external generation source of carriers. The electron-hole pair generation induced by the particle strike is included in the continuity equations via an additional generation rate. This radiation-induced generation rate can be connected to the parameters of irradiation, such as the particle Linear Energy Transfer (LET). The LET is the energy lost by unit of length (dE/dI), which is expressed here in MeV cm<sup>2</sup>/mg ( $1pC/\mu m \approx 100$ MeV cm<sup>2</sup>/mg). The particle LET can be converted into an equivalent number of electron-hole pairs by unit of length using the mean energy necessary to create an electron-hole pair ( $E_{ehp}$ ) (Roche, 1999):

$$\frac{\mathrm{dN}_{\mathrm{ehp}}}{\mathrm{dl}} = \frac{1}{\mathrm{E}_{\mathrm{ehp}}} \frac{\mathrm{dE}}{\mathrm{dl}} \tag{3}$$

where  $N_{ehp}$  is the number of electron-hole pairs created by the particle strike. By associating two functions describing the radial and temporal distributions of the created electron-hole pairs, the number of electron-hole pairs is included in the continuity equations (Munteanu & Autran, 2008) via the following radiation-induced generation rate:

$$G(\mathbf{w}, \mathbf{l}, \mathbf{t}) = \frac{dN_{ehp}}{dl}(\mathbf{l}) \cdot R(\mathbf{w}) \cdot T(\mathbf{t})$$

(4)

where R(w) and T(t) are the functions of radial and temporal distributions of the radiation induced pairs, respectively. Equation (4) assumes the following hypothesis: the radial distribution function R(w) depends only on the distance traversed by the particle in the material and the generation of pairs along the ion path follows the same temporal distribution function in any point. Since function G must fill the condition:

$$\int_{w=0}^{\infty} \int_{\theta=0}^{2\pi} \int_{t=-\infty}^{\infty} Gw \, dw \, d\theta \, dt = \frac{dN_{ehp}}{dl}$$

(5)

functions R(w) and T(t) are submitted to the following normalization conditions:

$$2\pi \int_{w=0}^{\infty} R(w)w \, dw = 1 \tag{6}$$

$$\int_{t=-\infty}^{\infty} T(t) dt = 1$$

(7)

The ion track models available in commercial simulation codes usually propose a Gaussian function for the temporal distribution function T(t):

$$T(t) = \frac{e^{-(\frac{t}{t_{\rm C}})^2}}{t_{\rm C} \sqrt{\pi}}$$

(8)

where  $t_c$  is the characteristic time of the Gaussian function which allows one to adjust the pulse duration. The radial distribution function is usually modelled by an exponential function or by a Gaussian function:

$$R(w) = \frac{e^{-(\frac{w}{r_{c}})^{2}}}{\pi r_{c}^{2}}$$

(9)

where  $r_C$  is the characteristic radius of the Gaussian function used to adjust the ion track width. Previous works have demonstrated that the different charge generation distributions used for the radial ion track does affect the device transient response, but the variation is typically limited to ~5% for ion strikes on bulk p-n diodes (Dodd, 2005; Dussault et al., 1993). Considering a LET which is not constant with depth along the path has a more significant impact on the transient response in bulk devices. The key parameters of the single event transient (peak current, time to peak and collected charge) have up to 20% variation when LET is allowed to vary with depth compared to the case of a constant LET (Dussault et al., 1993). Nevertheless, the LET variation with depth has no influence on the transient response of actual SOI devices with thin Silicon film.

In this work, the irradiation track simulated in vertical incidence has a Gaussian shape with narrow radius (14 nm) and a Gaussian time dependence, centred on 10 ps and with a characteristic width of 2 ps. The ion strikes in the middle of the channel. The deposited charge is calculated considering the Gaussian distribution of the ion track and the 3D geometry of the Silicon film. The collected charge is given by the integration of the drain current over the transient duration and the bipolar amplification is finally calculated as the ratio between the collected and deposited charges, as it will be shown in section 4.3.

## 4. Simulation of multiple-gate devices

#### 4.1 Static characteristics

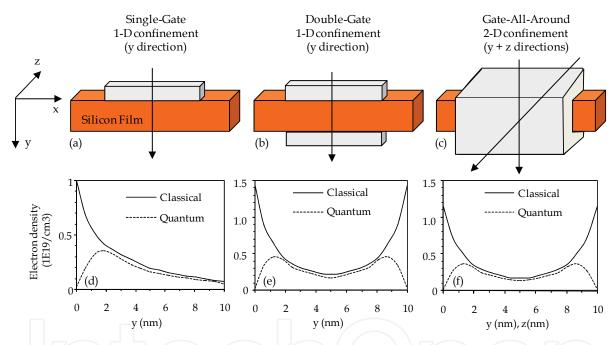

Figure 4 shows the quantum confinement directions in three different generic configurations: Single-Gate, Double-Gate and Gate-All-Around devices. The impact of quantum effects on the electron density extracted along a cut-line parallel to the confinement directions is also illustrated for the three devices.

In the Single-Gate devices carriers are confined in a very narrow triangular potential well, formed at the  $Si/SiO_2$  interface. The quantum carrier density in the y direction is then modified as compared to the classical one: the classical electron density is maximal at the  $Si/SiO_2$  interface, since the quantum density profile show a maximum shifted inside the Silicon film at several nanometers depth. Then, the electron density near the interface (as well as the total electron charge in the conduction channel) is strongly reduced. In the case of a Double-Gate archtecture, the potential well is rectangular and its dimension is now controlled by the Silicon film thickness, which becomes a key parameter in the quantum effects analysis. Similar to the Single-Gate configuration, the electron density is maximum at

the two interfaces in the classical case. In the quantum case, the density profile has two maxima situated within the Silicon film at several nanometers depth from each interface. Our results are in perfect concordance with (Majkusiak et al., 2002), where quantum effects are simulated using the solution of the 1-D Schrödinger equation. The drain current is splitted in two separate channels, but they are no more located at the interface as in the classical case. Finally, in the Gate-All-Around structure, carriers are confined in a double rectangular potential well (along the y and the z directions), which considerably enhances the quantum confinement effects. The carrier motion is no more free in the z direction (as is the case of the Single-Gate and the Double-Gate devices), but their energy is quantized as in the y direction. Both the gate electrode width (W) and the Silicon film thickness control here the quantum effects. The quantum electron density in the z direction is no more maximal at the interface but has two maxima moved into the Silicon film as for the carrier density in the y direction. Then the total inversion charge is lower than in the Double-Gate configuration.

Fig. 4. Schematically representation of the quantum-mechanical confinement directions in (a) Single-Gate, (b) Double-Gate and (c) Gate-All-Around configurations. The profile of the carrier density in a cut-line along the film thickness is also reported for both classical and quantum cases: (d) Single-Gate, (e) Double-Gate and (f) Gate-All-Around.  $V_D=V_G=0.8 \text{ V}$ , L=32 nm

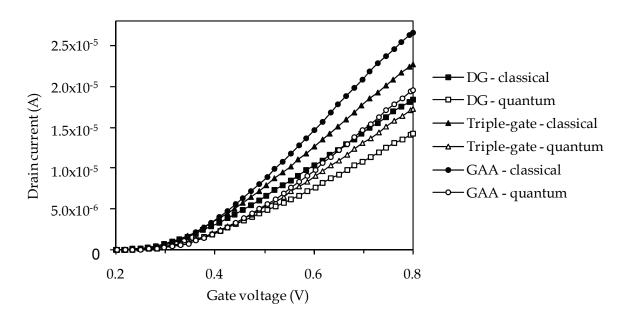

The  $I_D(V_G)$  curves for the different 32 nm Multiple-Gate MOSFET architectures simulated in the classical and quantum cases are shown in Fig. 5.

The results show that increasing the "equivalent number of gates" reduces the off-state current (Munteanu et al., 2007) and improves the subthreshold swing S (S = 70 mV/dec for Double-Gate, S = 68.5 mV/dec for Triple-Gate and S = 61.5 mV/dec for Gate-All-Around). This is due to the better electrostatic control of the gate over the channel that reduces short channel effects. At the same time, the on-state current increases with EGN (Fig. 5), due to the multiple-channel conduction. As expected, the quantum current is lower than the classical

one, because the total inversion charge is reduced in the quantum case. Figure 5 also shows that the difference between the classical and the quantum off-state current increases when going from Double-Gate to Gate-All-Around device. The ratio between the classical and quantum off-state currents is reported in Table 1 for the three considered configurations.

Fig. 5. Drain current  $I_D(V_G)$  characteristics in classical and quantum-mechanical cases for 32 nm Double-Gate, Triple-gate,  $\Omega$ -Gate and Gate-All-Around architectures ( $V_D$ =0.8 V). The quantum drain current was simulated using the Density-Gradient model calibrated on BALMOS3D numerical results

|                         | t <sub>Si</sub> =W=10 nm<br>L=32 nm | t <sub>si</sub> =W=8 nm<br>L=25 nm | t <sub>si</sub> =W=5 nm<br>L=22 nm |

|-------------------------|-------------------------------------|------------------------------------|------------------------------------|

| Double-Gate (EGN=2)     | 1.91                                | 2.02                               | 3.01                               |

| Triple-Gate (EGN=3)     | 2.24                                | 2.3                                | 3.66                               |

| Gate-All-Around (EGN=4) | 2.36                                | 2.67                               | 4.11                               |

Table 1. Ratio Ioff\_cl/Ioff\_q of the off-state currents in classical (Ioff\_cl) and quantum (Ioff\_q) approaches for the three technological nodes studied in this work. The quantum drain current has been calculated using the Density Gradient model calibrated on BALMOS3D for each configuration.

We remark that this ratio increases with EGN for a given technology node. This effect can be explained by the dimensionality of the confinement. In Double-Gate, carriers are confined in one direction (y direction), since in Triple-Gate and Gate-All-Around carriers are confined in two directions (y and z), which strongly enhances the energy quantization with respect to the Double-Gate case.

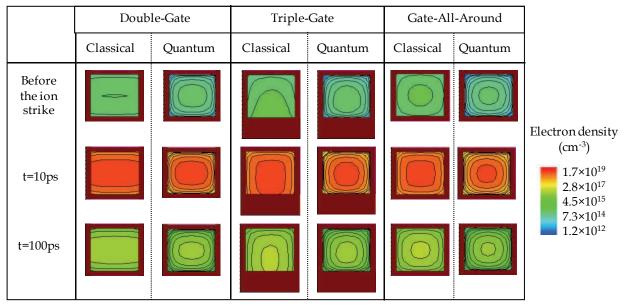

# 4.2 Transient simulation results

The time evolution of the electron density distribution in a vertical cross-section (y-z plane) in the middle of the channel is represented in Fig. 6 for three configurations: Double-Gate, Tri-Gate and Gate-All-Around. We observe that for all devices the quantum electron charge is centred in the middle of the film and the electron density has lower values than in the classical case. In off-state bias condition, the carrier conduction in all devices is mainly dominated by the volume inversion phenomenon: carriers flow from source to drain over the entire Silicon film thickness. In consequence, the off-state current is directly proportional to the film thickness. In the quantum case the volume inversion phenomenon is reinforced because the quantum carrier density becomes more centred in the middle of the film (Fig. 6). This effect is enhanced when EGN increases from 2 (Double-Gate) to 4 (Gate-All-Around), as illustrated in Fig. 6.

Fig. 6. Classical and quantum electron density (expressed in cm<sup>-3</sup>) in a vertical cross-section (y-z plane) in the middle of the channel of 32 nm Double-Gate, Triple-Gate and Gate-All-Around at different times before and after the ion strike. The devices are biased in the off-state at  $V_G=0$  V and  $V_D=0.8$  V. The brown regions represent the gate oxide (in Double-Gate and Gate-All-Around devices) and the gate and buried oxide in Triple-Gate devices

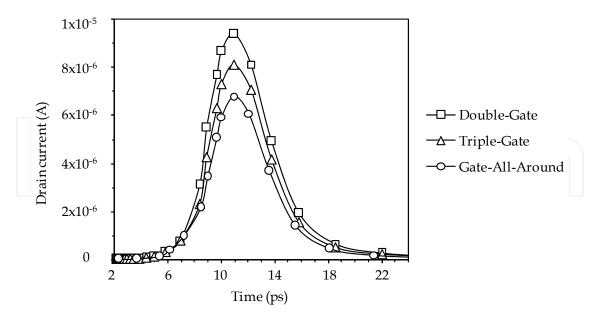

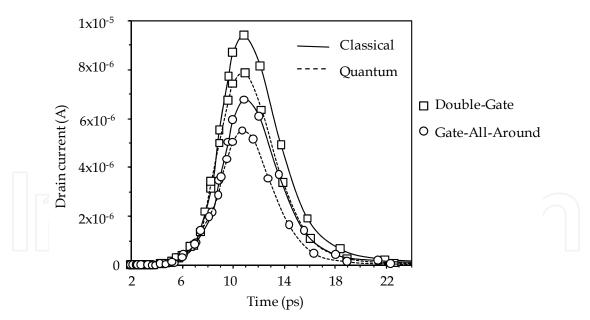

The drain current transients produced by the ion strike are illustrated in Fig. 7 for the classical case and for a LET value of 1 MeV/(mg/cm<sup>2</sup>). The four configurations corresponding to the 32 nm gate length ITRS LP technology node are simulated in the off-state. The peak value of the drain current transient is reduced when EGN increases. When EGN increases, the channel is better controlled by the gate and the floating body effects are strongly reduced. Then the drain current transient tail is shorter when going from Double-Gate to Gate-All-Around devices. Figure 8 compares the classical and the quantum drain current transient for two configurations: Double-Gate and Gate-All-Around devices with 32 nm gate length. As expected, the peak of the quantum drain current transient is lower than the classical one for both configurations, due to the quantum confinement which induces lower quantum off-state current.

Fig. 7. Drain current transients induced by an ion strike vertically (y direction) in the middle of the Silicon film (classical simulation). The ion track generation has a Gaussian shape versus time (characteristic time of 2 ps), centred at 10 ps and a LET=1 MeV/(mg/cm<sup>2</sup>). The simulated devices are 32 nm gate length MOSFETs. All devices are off-state biased (V<sub>G</sub>=0 V,  $V_D$ =0.8 V)

Fig. 8. Drain current transients induced by an ion strike vertically (y direction) in the middle of the Silicon film. Comparison between classical and quantum simulation in Double-Gate and Gate-All-Around MOSFETs. All devices are off-state biased ( $V_G=0 V$ ,  $V_D=0.8 V$ )

### 4.3 Bipolar amplification

The bipolar amplification is a phenomenon specific to partially-depleted SOI devices and its basic mechanism was largely explained and simulated in previous works (Ferlet-Cavrois et

al., 2002; Ferlet-Cavrois et al., 2004; Schwank et al., 2003). Bipolar amplification can also occur in fully depleted devices, as those studied here.

The bipolar transistor mechanism in fully depleted devices has been explained in (Brisset et al., 1994) using Monte Carlo simulations of 0.25  $\mu$ m fully depleted SOI transistors: after irradiation of a n-channel MOSFET biased in its off state, excess holes are accumulated in the channel (mainly near the gate oxide) and lower the potential barrier; then electrons diffuse from source to drain to maintain the electrical neutrality. This mechanism is comparable to the bipolar transistor effect in partially depleted SOI transistors (Massengill et al., 1990). Because bipolar amplification is less important for fully depleted than for partially depleted devices, circuits based on fully depleted transistors are less sensitive to single-event upset than partially depleted circuits (Ferlet-Cavrois et al., 2002).

The effect of the parasitic bipolar transistor in SOI devices is quantified using the bipolar gain,  $\beta$ . The bipolar gain corresponds to the amplification of the deposited charge and is given by the ratio between the total collected charge,  $Q_{coll}$ , at the drain electrode and the deposited charge,  $Q_{dep}$ :

$$\beta = \frac{Q_{coll}}{Q_{dep}} \tag{10}$$

The total collected charge at drain electrode is given by:

$$Q_{coll} = \int_{0}^{\infty} I_{D} dt$$

(11)

The deposited charge in a SOI device is calculated as a function of the particle LET using the following equation (Ferlet-Cavrois, 2004; Munteanu & Autran, 2008):

$$Q_{dep}[fC] = 10.3 \times LET[MeV / (mg / cm2)] \times t_{si}[\mu m]$$

(12)

where  $t_{Si}$  is the Silicon film thickness and 10.3 is a multiplication factor for Silicon calculated using the Silicon density and the energy needed for creating an electron-hole pair in Silicon (- 3.6 eV) (Ferlet-Cavrois, 2004; Munteanu & Autran, 2008). In this equation a normal incident ion strike is considered and the LET is supposed constant along the ion path in the active Silicon film.

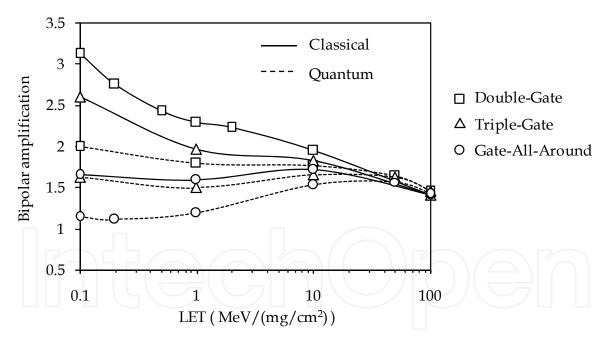

The bipolar gain for 32 nm gate length Multiple-Gate devices in both classical and quantum cases is shown in Fig. 9 as a function of the LET value. The bipolar amplification decreases when increasing EGN due to less floating body effects. However, at high LET (>2 MeV/(mg/cm<sup>2</sup>)), the classical bipolar gain becomes the same for all configurations. This can be explained by the huge deposited charge by the ion which masks the impact of other phenomena such as the electrostatic control by the gate.

Previous experimental and theoretical studies showed that, generally, fully depleted SOIbased devices (with either single- or double-gate configuration) present reduced floating body effects and then lower bipolar amplification of the collected charge than partiallydepleted SOI devices (Ferlet-Cavrois et al., 2002; Ferlet-Cavrois et al., 2005). In Multiple-Gate devices the control of the channel by the gates is naturally reinforced, and reduces even more the floating body effects. Then very low values are obtained for the bipolar gain. Our results are consistent with simulation data from (Munteanu et al., 2006) and (Castellani et al., 2006), but they are very low compared with those expected by extrapolation from simulations in (Dodd et al., 2004). This is probably due to the partially depleted SOI Single-Gate structures used in (Dodd et al., 2004), whereas ultra-thin fully-depleted devices and multiple-gate configurations are considered here.

The quantum bipolar gain is lower than the classical one, excepted at very high LET (Fig. 9). Our results show that two phenomena, with opposite effects on the bipolar gain, are to be considered. On one hand, the lower off-state current in the quantum case leads to a lower quantum bipolar amplification (Castellani et al., 2006). On the other hand, in the quantum case, the electron density is lower leading to slower recombination process (reflected in a longer transient tail) and then to a higher collected charge. Depending on the injection regime, one phenomenon or the other prevails. At low injection regime, the generated charge is not very high and carriers recombine rapidly. Then the bipolar gain follows the off-state current behaviour, both being lower for a quantum approach than for a classical one. In very high injection conditions, the electron charge in the film is not sufficient to recombine the enormous generated charge and then, the recombination process is sensibly slower. This has been verified by simulation: the recombination rate in the Silicon film is higher in the classical case than in the quantum case. As a consequence, the quantum collected charge and the quantum bipolar amplification are higher than in the classical ones.

Fig. 9. Simulated classical and quantum bipolar gain as a function of LET in 32 nm gate length Multiple-Gate MOSFET. The transistors are biased in the off-state at  $V_G$ =0 V and  $V_D$ =0.8 V

# 5. Device scaling

The effects of the carrier confinement become more important when the Silicon film is thinned because the energy subband splitting is directly proportional with the reverse of the square of the potential well dimension (equal to the film thickness). The ratio between the

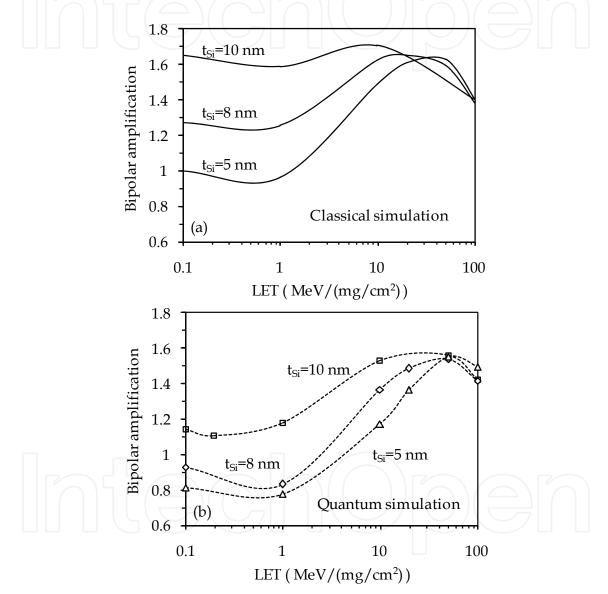

classical and quantum off-state currents, reported in Table 1 as a function of  $t_{Si}$ , confirms that the quantum confinement is strongly enhanced when the film is thinned down. The collected charge and the bipolar gain (shown in Figs. 10(a) and 10(b)) are lower for thinner channel, in both quantum and classical cases, because the off-state current decreases with the film thickness. The maximal value of the gain is shifted to higher LET values when Silicon film thickness decreases. Our results also indicate that, in the quantum approach, the difference in the bipolar gain when reducing the film thickness (at the same LET) is lower than in the classical case.

Fig. 10. Bipolar gain variation when reducing the Silicon film thickness in Gate-All-Around MOSFET with 32 nm gate length (the gate width is W=10 nm): (a) classical simulation; (b) quantum simulation. The transistors are biased in the off-state at  $V_G$ =0 V and  $V_D$ =0.8 V

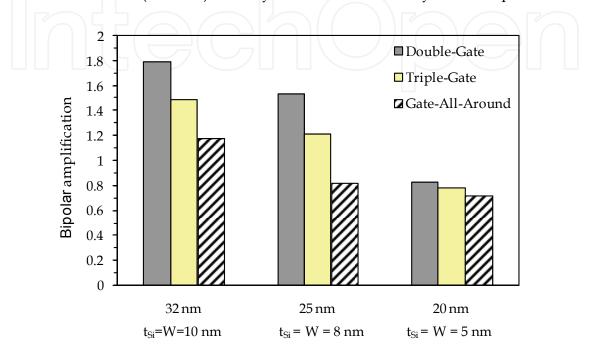

The quantum bipolar gain for Multiple-Gate devices scaled down to 20 nm gate length and 5 nm Silicon film cross-section was also predicted. As shown in Fig. 11, the difference between the three architectures is reduced for devices with 20 nm gate lengths compared to those with 32 nm and 25 nm gate lengths, due to the very thin square wire cross-section ( $t_{Si}=W=5$

nm). When decreasing the cross-section, the influence of the gate configuration is attenuated and the values of the bipolar gain for the different structures are almost the same. This behaviour can be explained by the fact that, around 5 nm and below, the combination of gate electrostatic control and quantum-mechanical confinement leads to similar carrier density distributions in the film for all gate configurations (Bescond et al., 2004). At this ultimate scale of integration, it should be expected that the sensitivity of all Multiple-Gate nanowire architectures (EGN  $\geq$  2) to heavy ion irradiation sensibly become equivalent.

Fig. 11. Bipolar gain calculated in the quantum case for Multiple-Gate nanowire MOSFETs with different gate lengths. The dimensions of the Silicon film cross-section are also indicated. The ion strikes vertically (parallel to the y direction) in the middle of the film

# 6. Conclusion

In this work we analyzed the impact of quantum confinement on single-event transient immunity of several Multiple-Gate architectures. We showed that the 3-D carrier distribution is strongly affected by the quantum effects, which not only reduces the drain current but also modifies the recombination rate and the charge collection compared to the classical case. Increasing the "number of equivalent gates" induces less floating body effects and then lowers the bipolar gain. Our simulations also showed that when the Silicon channel cross-section is thinned down (around 5nm and below), the bipolar amplification of Multiple-Gate nanowire architectures (EGN  $\geq$  2) sensibly becomes the same mainly due to carrier quantum confinement.

# 7. References

Ancona, M.G. & Iafrate, G.J. (1989). Quantum correction to the equation of state of an electron gas in a semiconductor. *Physical Review B*, Vol. 39, No. 13, (May 1989) pp. 9536-9540.

- Baumann, R. C. (2005). Radiation-Induced Soft Errors in Advanced Semiconductor Technologies. *IEEE Transactions on Device Material Reliability*, Vol. 5, no. 3, (Sept. 2005) pp. 305-316.

- Bescond, M.; Nehari, K.; Autran, J.L.; Cavassilas, N.; Munteanu, D. & Lannoo, M. (2004). 3D Quantum-Modeling and Simulation of Multi-Gate Nanowire MOSFETs. *Proceedings* of IEDM Technical Digest, pp. 617-620, Washington, USA, Dec. 2004, IEEE.

- Brisset, C.; Dollfus, P.; Musseau, O.; Leray, J. L. & Hesto, P. (1994). Theoretical study of SEU's in 0.25-pm fully-depleted CMOS/SOI technology. *IEEE Transactions on Nuclear Science*, Vol. 41, No. 6, (1994) pp. 2297-2303.

- Castellani, K.; Munteanu, D.; Autran, J.L.; Ferlet-Cavrois, V.; Paillet, P. & Baggio, J. (2006). Investigation of 30 nm Gate-All-Around MOSFET Sensitivity to Heavy Ions: a 3-D Simulation Study. *IEEE Transactions on Nuclear Science*, Vol. 53, No. 4, (Aug. 2006) pp. 1950-1958.

- Choi, Y.; Lindert, N.; Xuan, P.; Tang, S.; Ha, D.; Anderson, E.; King, T.; Bokor, J. & Hu, C. (2001). Sub-20nm CMOS FinFET technologies. *Proceedings of IEDM Technical Digest*, pp. 421-424, Washington, USA, Dec. 2001, IEEE.

- Colinge, J. P.; Gao, M. H.; Romano-Rodríguez, A.; Maes, H. & Claeys, C. (1990). Silicon-oninsulator "Gate-all-around device". *Proceedings of IEDM Technical Digest*, pp. 595-598, Washington, USA, Dec. 1990, IEEE.

- Dodd, P. E. (1996). Device Simulation of Charge Collection and Single-Event Upset. *IEEE Transactions on Nuclear Science*, Vol. 43, No. 2, (1996) pp. 561-575.

- Dodd, P. E.; Musseau, O.; Shaneyfelt, M. R.; Sexton, F. W.; D'hose, C.; Hash, G.L.; Martinez, M.; Loemker, R. A.; Leray, J.-L. & Winokur, P. S. (1998). Impact of ion energy on single-event upset. *IEEE Transactions on Nuclear Science*, Vol. 45, No. 6, (Dec. 1998) pp. 2483–2491.

- Dodd, P.E. & Massengill, L.W. (2003). Basic mechanisms and modeling of single-event upset in digital microelectronics. *IEEE Transactions on Nuclear Science*, Vol. 50, No. 3, (Jun. 2003) pp. 583–602.

- Dodd, P. E.; Shaneyfelt, M. R.; Felix, J. A. & Schwank, J. R. (2004). Production and propagation of single-event transients in high-speed digital logic ICs. *IEEE Transactions on Nuclear Science*, Vol. 51, No. 6, (Dec. 2004) p. 3278-3284.

- Dodd, P. E. (2005). Physics-Based Simulation of Single-Event Effects. *IEEE Transactions on Device Material Reliability*, Vol. 5, No. 3, (Sept. 2005) pp. 343-357.

- Dussault, H.; Howard, Jr., J. W.; Block, R.C.; Pinto, M. R.; Stapor, W. J. & Knudson, A. R. (1993). Numerical simulation of heavy ion charge generation and collection dynamics. *IEEE Transactions on Nuclear Science*, Vol. 40, No. 6, (Dec. 1993) pp. 1926–1934.

- Ferlet-Cavrois, V.; Gasiot, G.; Marcandella, C.; D'Hose, C.; Flament, O.; Faynot, O.; du Port de Pontcharra, J. & Raynaud, C. (2002). Insights on the Transient Response of Fully and Partially Depleted SOI Technologies Under Heavy-Ion and Dose-Rate Irradiations. *IEEE Transactions on Nuclear Science*, Vol. 49, No.6, (Dec. 2002) pp. 2948-2956.

- Ferlet-Cavrois, V.; Vizkelethy, G.; Paillet, P.; Torres, A.; Schwank, J. R.; Shaneyfelt, M. R., Baggio, J.; du Port de Pontcharra, J. & Tosti, L. (2004). Charge enhancement effect in NMOS bulk transistors induced by heavy ion irradiation—Comparison with SOI. *IEEE Transactions on Nuclear Science*, Vol. 51, No. 6, (Dec. 2004) pp. 3255–3262.

- Ferlet-Cavrois, V.; Paillet, P.; McMorrow, D.; Torres, A.; Gaillardin, M.; Melinger, J. S.; Knudson, A. R.; Campbell, A. B.; Schwank, J. R.; Vizkelethy, G.; Shaneyfelt, M. R.; Hirose, K.; Faynot, O.; Jahan, C. & Tosti, L. (2005). Direct Measurement of Transient Pulses Induced by Laser Irradiation in Deca-Nanometer SOI Devices. *IEEE Transactions on Nuclear Science*, Vol. 52, No. 6, (Dec. 2005) pp. 2104-2113.

- Fischetti, M. V. & Laux, S. E. (2001). Long-Range Coulomb Interactions in Small Si Devices. Part I: Performance and Reliability. *Journal of Applied Physics*, Vol. 89, No. 2, (2001) pp. 1205–1231.

- Francis, P.; Colinge, J.P. & Beger, G. (1995). Temporal Analysis of SEU in SOI/GAA SRAMs. *IEEE Transactions on Nuclear Science*, Vol. 42, No.6, (Dec. 1995) pp. 2127-2137.

- Frank, D.J.; Laux, S.E. & Fischetti., M.V. (1992). Monte Carlo simulation of a 30nm dual-gate MOSFET: How short can Si go?. *Proceedings of IEDM Technical Digest*, pp. 553-556, Washington, USA, Dec. 1992, IEEE.

- Grubin, H.L.; Govindan, T.R.; Kreskovsky J.P. & Stroscio, M.A. (1993). Transport via the Liouville equation and moments of quantum distribution functions. *Solid-State Electronics*, Vol. 36, (Dec. 1993) pp. 1697–1709.

- Guarini, K. W.; Solomon, P. M.; Zhang, Y.; Chan, K. K.; Jones, E. C.; Cohen, G. M.; Krasnoperova, A.; Ronay, M.; Dokumaci, O.; Bucchignano, J. J.; Cabral Jr., C.; Lavoie, C.; Ku, V.; Boyd, D. C.; Petrarca, K. S.; Babich, I. V.; Treichler, J.; Kozlowski, P. M.; Newbury, J. S.; D'Emic, C. P.; Sicina, R. M. & Wong, H. (2001). Triple-selfaligned, planar double-gate MOSFETs: Devices and circuits. *Proceedings of IEDM Technical Digest*, pp. 425-428, Washington, USA, Dec. 2001, IEEE.

- Gusev, E. P.; Narayanan, V. & Frank, M. M. (2006). Advanced high-k dielectric stacks with polySi and metal gates: Recent progress and current challenges. *IBM Journal of Research and Development*, Vol. 50, No. 4/5, (2006) pp. 387–410.

- Haensch, W.; Nowak, E. J.; Dennard, R. H.; Solomon, P. M.; Bryant, A.; Dokumaci, O.H.; Kumar, A.; Wang, X.; Johnson, J. B. & Fischetti, M. V. (2006). Silicon CMOS devices beyond scaling. *IBM Journal of Research and Development*, Vol. 50, No. 4/5, (2006) pp. 339-361.

- Hamm, R. N.; Turner, J. E.; Wright, H. A. & Ritchie, R. H. (1979). Heavy ion track structure in Silicon. *IEEE Transactions on Nuclear Science*, Vol. 26, No. 6, (Dec. 1979) pp. 4892– 4895.

- Hansch, W.; Vogelsang, T.; Kirchner, R. & Orlowski, M. (1989). Carrier Transport Near the Si/SiO2 Interface of a MOSFET. *Solid State Electronics*, Vol. 32, No. 10, (Oct. 1989) pp. 839-849.

- Hareland, S. A.; Jallepalli, S.; Shih, W.-K.; Wang, H.; Chindalore, G. L.; Tasch, A. F. & Maziar, C. M. (1998). A Physically-Based Model for Quantization Effects in Hole Inversion Layers. *IEEE Transactions on Electron Devices*, Vol. 45, No. 1, (Jan. 1998) pp. 179-186.

- Harrison, S.; Coronel, P.; Leverd, F.; Cerutti, R.; Palla, R.; Delille, D.; Borel, S.; Descombes, S.; Lenoble, D.; Talbot, A.; Villaret, A.; Monfray, S.; Mazoyer, P.; Bustos, J.; Brut, H.; Cros, A.; Munteanu, D.; Autran, J-L. & Skotnicki, T. (2004). Highly performant double gate MOSFET realized with SON process. *Proceedings of IEDM Technical Digest*, pp. 449-452, Washington, USA, Dec. 2004, IEEE.

- Hiramoto, T.; Saitoh M.; & Tsutsui, G. (2006). Emerging nanoscale Silicon devices taking advantage of nanostructure physics. *IBM Journal of Research and Development*, Vol. 50, No. 4/5, (2006) pp. 411-418.

- Hisamoto, D.; Kaga, T.; Kawamoto, Y. & Takeda, E. (1989). A fully depleted lean-channel transist or (DELTA)-a novel vertical ultra thin SOI MOSFET. *Proceedings of IEDM Technical Digest*, pp. 833–836, Washington, USA, Dec. 1989, IEEE.

- Houssa, M. (2004). Fundamental and Technological Aspects of High-k Gate Dielectrics, Institute of Physics, London.

- ITRS 2009. International Technology Roadmap for Semiconductors. Available online: http://public.itrs.net.

- Kedzierski, J.; Nowak, E.; Kanarsky, T.; Zhang, Y.; Boyd, D.; Carruthers, R.; Cabral, C.; Amos, R.; Lavoie, C.; Roy, R.; Newbury, J.; Sullivan, E.; Benedict, J.; Saunders, P.; Wong, K.; Canaperi, D.; Krishnan, M.; Lee, K.; Rainey, B. A.; Fried, D.; Cottrell, P.; Wong, H. P.; Ieong, M. & Haensch, W. (2002). Metal-gate FinFET and fully-depleted SOI devices using total gate silicidation. *Proceedings of IEDM Technical Digest*, pp. 247-250, Washington, USA, Dec. 2002, IEEE.

- Kobetich, E. J. & Katz, R. (1968). Energy Deposition by Electron Beams and δ Rays. *Physical Review*, Vol. 170, No. 2, (1968) pp. 391-396.

- Jiao, Z. & Salama, C. A. T. (2001). A fully depleted ∆-channel SOI nMOSFET. *Proceedings of the Electrochemical Society*, Vol. 2001–3, (2001) pp. 403–408.

- Jiménez, D.; Iniguez, B.; Suné, J.; Marsal, L.F.; Pallarès, J.; Roig, J. & Flores, D. (2004). Continuous Analytic I–V Model for Surrounding-Gate MOSFETs. *IEEE Electron Device Letters*, Vol. 25, No. 8, (Aug. 2004) pp. 571-573.

- Majkusiak, B.; Janik, T. & Walczak, J. (2002). Semiconductor Thickness Effects in the Double-Gate SOI MOSFET. *IEEE Transactions on Electron Devices*, Vol. 45, No. 5, (May 2002) pp. 1127-1134.

- Martin, R. C.; Ghoniem, N. M.; Song, Y. & Cable, J. S. (1987). "The size effect of ion charge tracks on single event multiple-bit upset", *IEEE Transactions on Nuclear Science*, Vol. 34, No. 6, (1987) pp. 1305–1309.

- Massengill, L. W.; Kerns, D. V.; Kerns, S. E. & Alles, M. L. (1990). Single-Event Charge Enhancement in SOI Devices, *IEEE Electron Device Letters*, Vol. EDL-11, (Feb. 1990) pp. 98-99.

- Munteanu, D. & Autran, J.L. (2003). Two-dimensional Modeling of Quantum Ballistic Transport in Ultimate Double-Gate SOI Devices. *Solid State Electronics*, Vol. 47, No. 7, (2003) pp. 1219-1225.

- Munteanu, D.; Ferlet-Cavrois, V.; Autran, J.L.; Paillet, P.; Baggio, J.; Faynot, O.; Jahan, C. & Tosti, L. (2006). Investigation of Quantum Effects in Ultra-Thin Body Single- and Double-Gate Devices Submitted to Heavy Ion Irradiation. *IEEE Transactions on Nuclear Science*, Vol. 53, No. 6, (Dec. 2006) pp. 3363-3371.

- Munteanu, D.; Autran, J.L.; Ferlet-Cavrois, V.; Paillet, P.; Baggio, J.; & Castellani, K. (2007).

3-D Quantum Numerical Simulation of Single-Event Transients in Multiple-Gate Nanowire MOSFETs. *IEEE Transactions on Nuclear Science*, Vol. 54, No. 4, (Aug. 2007) pp. 994-1001.

- Munteanu, D. & Autran, J.L. (2008). Modeling of digital devices and ICs submitted to transient irradiations. *IEEE Transactions on Nuclear Science*, Vol. 55, no. 4, (Aug. 2008) pp. 1854-1878.

- Oldiges, P.; Dennard, R.; Heidel, D.; Klaasen, B.; Assaderaghi, R. & Ieong, M. (2000). Theoretical determination of the temporal and spatial structure of α-particle induced electron-hole pair generation in Silicon. *IEEE Transactions on Nuclear Science*, Vol. 47, No. 6, (Dec. 2000) pp. 2575–2579.

- Park, J.T.; Colinge, J.P. & Diaz, C.H. (2001). Pi-Gate SOI MOSFET. *IEEE Electron Device Letters*, Vol. 22, No.8, (2001) pp.405-406.

- Park, J.T. & Colinge, J.P. (2002). Multiple-gate SOI MOSFETs: device design guidelines. *IEEE Transactions on Electron Devices*, Vol. 49, No. 12, (Dec. 2002) pp. 2222-2229.

- Rim, K.; Hoyt, J. L. & Gibbons, J. F. (1998). Transconductance Enhancement in Deep Submicron Strained-Si 12-MOSFETs. *Proceedings of IEDM Technical Digest*, pp. 707– 710, Washington, USA, Dec. 1998, IEEE.

- Roche, P. (1999). Etude du basculement induit par une particule ionisante dans une mémoire statique en technologie submicronique, Phd Thesis, 1999, in french.

- Schwank, J. R.; Ferlet-Cavrois, V.; Shaneyfelt, M. R.; Paillet, P. & Dodd, P. E. (2003). Radiation effects in SOI technologies. *IEEE Transactions on Nuclear Science*, Vol. 50, No. 3, (Jun. 2003) pp. 522–538.

- Stapor, W. J. & McDonald, P. T. (1988). Practical approach to ion track energy distribution. *Journal of Applied Physics*, Vol. 64, No. 9, (1988) pp. 4430-4434.

- Stern, F. (1972). Self-consistent results for n-type Si inversion layers. *Physical Review B*, Vol. 5, (Jun. 1972) pp. 4891–4899.

- Sentaurus (2009). Sentaurus TCAD Manuals, Synopsis, 2009.

- Taur, Y.; Buchanan, D.; Chen, W.; Frank, D.; Ismail, K.; Lo, S.-H.; Sai-Halasz, G.; Viswanathan, R.; Wann, H.-J. C.; Wind, S. & Wong, H.-S. (1997). CMOS scaling into the nanometer regime. *Proceedings of IEEE*, Vol. 85, (1997) pp. 486–504.

- Taur, Y. & Ning, TH. (1998). Fundamentals of Modern VLSI Devices. Cambridge Univ. Press, Cambridge, UK.

- van Dort, M. J.; Woerlee, P. H. & Walker, A. J. (1994). A simple model for quantization effects in heavily-doped silicon MOSFET's at inversion conditions. *Solid-State Electronics*, Vol. 37, No. 3, (1994) pp. 411-414.

- Wettstein, A.; Schenk, A. & Fichtner, W. (2002). Quantum device-simulation with Density-Gradient model. *IEEE Transactions on Electron Devices*, Vol. 48, No. 2, (Feb. 2002) pp. 279-284.

- Yang, F.; Chen, H.; Chen, F.; Huang, C.; Chang, C.; Chiu, H.; Lee, C.; Chen, C.; Huang, H.; Chen, C.; Tao, H.; Yeo, Y.; Liang, M. & Hu, C. (2002). 25nm CMOS Omega FETs. *Proceedings of IEDM Technical Digest*, pp. 255-258, Washington, USA, Dec. 2002, IEEE.

Numerical Simulations - Applications, Examples and Theory Edited by Prof. Lutz Angermann

ISBN 978-953-307-440-5 Hard cover, 520 pages Publisher InTech Published online 30, January, 2011 Published in print edition January, 2011

This book will interest researchers, scientists, engineers and graduate students in many disciplines, who make use of mathematical modeling and computer simulation. Although it represents only a small sample of the research activity on numerical simulations, the book will certainly serve as a valuable tool for researchers interested in getting involved in this multidisciplinary ï¬eld. It will be useful to encourage further experimental and theoretical researches in the above mentioned areas of numerical simulation.

## How to reference

In order to correctly reference this scholarly work, feel free to copy and paste the following:

Daniela Munteanu and Jean-luc Autran (2011). 3-D Quantum Numerical Simulation of Transient Response in Multiple-Gate Nanowire MOSFETs Submitted to Heavy Ion Irradiation, Numerical Simulations - Applications, Examples and Theory, Prof. Lutz Angermann (Ed.), ISBN: 978-953-307-440-5, InTech, Available from: http://www.intechopen.com/books/numerical-simulations-applications-examples-and-theory/3-d-quantum-numerical-simulation-of-transient-response-in-multiple-gate-nanowire-mosfets-submitted-t

## InTech Europe

University Campus STeP Ri Slavka Krautzeka 83/A 51000 Rijeka, Croatia Phone: +385 (51) 770 447 Fax: +385 (51) 686 166 www.intechopen.com

## InTech China

Unit 405, Office Block, Hotel Equatorial Shanghai No.65, Yan An Road (West), Shanghai, 200040, China 中国上海市延安西路65号上海国际贵都大饭店办公楼405单元 Phone: +86-21-62489820 Fax: +86-21-62489821 © 2011 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the <u>Creative Commons Attribution-NonCommercial-ShareAlike-3.0 License</u>, which permits use, distribution and reproduction for non-commercial purposes, provided the original is properly cited and derivative works building on this content are distributed under the same license.