# We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

6,900

186,000

200M

Downloads

154

Countries delivered to

Our authors are among the

TOP 1%

most cited scientists

12.2%

Contributors from top 500 universities

#### WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected.

For more information visit www.intechopen.com

## Pulse generator design

S. Bourdel, R. Vauché and J. Gaubert Aix-Marseille University, IM2NP, and CNRS, IM2NP (UMR 6242), France

## 1. Analysis of the current state of the art

The techniques normally used for generating pulses in low-cost monolithic technology (CMOS or BiCMOS) are different from those usually used in hybrid technologies. The latter mainly use edge combination methods generated from SRD diodes via quarter-wave lines or stubs (Jeongwoo Han et al., 2004). In a low-cost context, these techniques are not possible, as they cannot be integrated into the desired technologies. We shall present here only the following techniques:

- Baseband pulse transposition

- Baseband pulse filtering

- Synthesis by pulse combination.

This analysis is performed using circuits that have been built and measured and that can be found in the literature. Before commencing this analysis, it is necessary to point out that the figure of merit often used in pulse generation is the energy consumed by the pulse. This criteria is subject to a caveat, as it often fails to take into account the power consumed between two pulses, which means it is only relevant if the system is combined with power management (sometimes difficult to achieve, depending on the topology of the circuit). This is why we shall be presenting, wherever possible, an estimate of the total energy consumed by the pulse ( $\text{Ec}_t = P_{DC}/D_S$ ) that take into account the average consumption between two pulses. The energy consumed per pulse will then be used to quantify the energy consumed during the pulse alone ( $\tau$ ), and if this is not given, it will be approximated as follows:  $\text{E}_c = P_{DC} * \tau$ . Moreover, in order to be completely suitable, the energy consumed by the total pulse must be compared to the energy of the pulse produced ( $\text{E}_p$ ) by way of the energy efficiency per pulse ( $\text{n} = \text{E}_p/\text{Ec}_t$ ). As this energy is rarely given, it will be estimated by assuming that the pulse is a sinusoid modulated by a gate of width  $\tau$  and amplitude  $V_p$  ( $\text{E}_p = \tau \cdot V_p^2/2R_0$ ).

## 1.1. Baseband pulse transposition

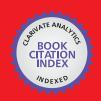

This technique, described in Fig. 1, makes it possible to transpose a baseband pulse in a frequency band. This technique has the great advantage of being able to change the frequency band by varying the local oscillator (LO) frequency, as well as varying the bandwidth by the width of the baseband pulse. Furthermore, the doubling of the spectrum

due to the frequency transposition allows the use of baseband pulses with a width of  $\tau$ =2/BW. In addition, these techniques are not very sensitive to LO phase noise which only degrades the spectral purity of the lines of the discrete spectrum and does not affect the Power Spectral Density (PSD) envelope.

Fig. 1. Principle of frequency transposition architectures

A first transposition technique is based on the use of a switching circuit (Rui Xu et al., 2006), usually a CMOS switch or a mixer. The performance of these architectures is mainly determined by the switching circuit, since the control signal gives the envelope of the baseband pulse transmitted. The performance of these architectures mainly depends on the off-on switching time (Tr), the on-off switching time (Tf), the insertion losses (IL), and the isolation between the LO and the output, as all these parameters influence the spectrum of g(t) (G(f) in Fig. 1). The simplest architecture found in literature is based on the use of a single transistor. This topology is very limited, as its sizing makes it impossible to optimize all the performance criteria at the same time. Indeed, reducing the insertion losses involves increasing the size of the transistor, leading to increased stray capacitances, which degrades the insertion losses at high frequencies and reduces isolation from the output (Rui Xu et al., 2006).

The switching circuit can also be achieved using a double balanced mixer similar to a Gilbert cell (Wentzloff & Chandrakasan, 2006) (Datta et al., 2007). In (Wentzloff & Chandrakasan, 2006), the currents in the differential pairs are summed in order to cancel out LO leakage and improve isolation. Moreover, this topology makes it possible to generate BPSK signals by switching the baseband signal between the + or – inputs. In addition, the use of a mixer allows a better control of the signal spectrum by changing the baseband pulse shape. In (Datta et al., 2007), a passive Gaussian filter is used to shape the baseband pulse and a Gilbert cell is used to generate the bipolar signals. However, because of the LO leakages, these structures require small signals to be used for the switching (LO input). As shown in Table 1, this results in low output amplitudes and implies the use of power amplifiers (PA). In addition, the switching times of these architectures are greater than those of a single transistor. This difficulty in producing wideband mixers prevents the generation of very short (<1 ns) pulses using this topology.

Even though none of the circuits here includes the LO, the consumption is poor because of the consumption of the mixers. This implies the use of power management to turn off the LO between two pulses.

These considerations concerning LO power management have given rise to a technique that consists of switching the LO directly (On/Off LO or Switched LO) rather than its output, solving not just the problem of consumption between two pulses, but also the leakage problem. This method allows performance to be achieved (see Table 1) that represents the state of the art in 2009 in terms of consumption and amplitude, for generating 500 MHz

bandwidth signals in the 3–5 GHz band. In the case of an LC LO, (Phan et al., 2008) shows that the rise and fall times ( $t_r$  and  $t_f$ ) can be equal and give rise to 3.5 ns wide pulses with component values that can be integrated into the technology used (0.18  $\mu$ m CMOS). Furthermore, the use of switched capacitors makes it possible to change the oscillation frequency and to address different channels, making this technique applicable for systems to the 802.15.4 standard. The major drawback of this technique lies in the low pulse amplitude.

To improve start-up time, (Barras et al., 2006) proposes a structure that gives the LO initial conditions that are greater than those generally produced by noise. This technique also allows the modification of the start phase, thereby offering the possibility of performing BPSK modulation. As reported in Table 1, this technique makes it possible to achieve very good performance in terms of amplitude.

In order to mitigate the excessively long start-up times for LC LOs, (Sanghoon Sim et al., 2009) proposes using ring oscillators. This structure allows the pulse widths to be around 0.5 ns. Furthermore, the digital structure of these LOs makes it possible to use inverters as output buffers with better performance than voltage followers, allowing amplitudes greater than  $600 \text{ mV}_{pp}$  for a consumption of 27 pJ/Pulse in the 6-10 GHz band.

| Ref. | Arch.                    | LO<br>leakage<br>PWM6 | τ<br>(ns)       | $V_{pp}$  | Ec<br>(pJ/<br>P) | Ec <sub>t</sub><br>(pJ/<br>P) | Ep<br>(pJ/P) | n                  | Pcons                | Size<br>(mm²) | Techn.       | Mod. | Integ.     |

|------|--------------------------|-----------------------|-----------------|-----------|------------------|-------------------------------|--------------|--------------------|----------------------|---------------|--------------|------|------------|

| 0    | Gated-<br>LO<br>(SW)     | 10                    | 0.4             | 1.2       | 0.7*             | 120                           | 1.44         | 0.012              | 1.8 mW<br>@ 15 MHz   | 0.6           | 0.18<br>CMOS | оок  | Ext.<br>LO |

| 0    | Gated-<br>LO<br>(Mix)    | ~10                   | 1.7<br>-<br>3.3 | 0.25      | 100*             | 313                           | 0.52         | 0.0016             | 31.3 mW<br>@ 100 MHz | nc            | 0.18<br>SiGe | BPSK | Ext.<br>LO |

| 0    | Gated-<br>LO<br>(Mix)    | 5                     | 1               | 0.01<br>4 | 15*              | 120                           | 0.0005       | 4.10 <sup>-6</sup> | 15 mW<br>@ 125 MHz   | nc            | 0.25<br>SiGe | BPSK | Full       |

| 0    | On/Off-<br>LO<br>(LC)    | 0                     | 3.5             | 0.18      | 18               | 18                            | 0.284        | 0.016              | 6.52 mW<br>@ 125 MHz | 0.39          | 0.18<br>CMOS | ООК  | Full       |

| 0    | On/Off-<br>LO<br>(LC)    | 0                     | 2.5             | 0.9       | 180              | 180                           | 5.06         | 0.028              | 1.8 mW<br>@ 10 Mp/s  | 0.57          | 0.18<br>CMOS | BPSK | Full       |

| 0    | On/Off-<br>LO<br>(rings) | 0                     | 0.5             | 0.67<br>3 | 27               | nc                            | 0.56         | 0.021**            | nc                   | 0.11          | 0.18<br>CMOS | оок  | Full       |

<sup>\*</sup> Estimate (Ec=Pdc\* $\tau$ ), \*\* (Ec/Ep)

Table 1. Main characteristics of LO switching generators.

Table 1 lists the key characteristics of the works presented. With this technique, efficiencies of the order of 1 % and levels below 1 V are reached. Let us note here that only the works presented in <sup>0</sup> and <sup>0</sup> consume no power between two pulses (Ec=Ec<sub>t</sub>).

## 1.2. Baseband pulse filtering

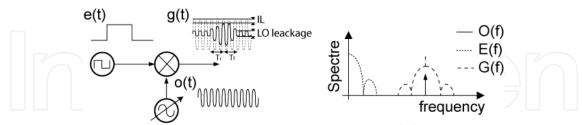

The principle of this technique, represented in Fig. 2, is based on the excitation of a filter by one or more baseband pulses produced by the combination of logic edges.

Fig. 2. Principle of baseband pulse filtering.

The expression of the generated pulse (g(t)) and its Fourier transform (G(t)) are dependent on the baseband pulses (e(t)) and the filter's transfer function in the manner described by 0 and 0. In particular, the filter makes it possible to adapt the signal's spectrum to a particular frequency band.

$$g(t) = e(t) * h(t)$$

(1)

$$G(f) = E(f).H(f)$$

(2)

This technique is particularly interesting for a low cost on package integration (System on Package – SoP) of the generator (Lee et al., 2008), as the generation of baseband pulse can be easily achieved in CMOS (here, 0.35  $\mu$ m CMOS) and the filter can easily be produced "Off Chip" with coplanar or micro-strip technology at the same time as the interconnection with the antenna. In this work, excitation is achieved by a 2 ns wide pulse with an amplitude of 2.8 V, produced by a logic edge combiner which is described in Fig. 2. The signal is then filtered by a stub filter integrated onto a low-cost substrate (FR4). This technique makes it possible to generate pulses of substantial amplitude (0.65  $V_{pp}$ ) thanks to the filter's modest insertion loss (2.3 dB) and the strong excitation. Moreover, the total SoP size does not exceed 40 mm \* 40 mm.

In order to be independent of the production of the chip carrier inherent to SoP technologies, it is possible to implement this technique in a System on Chip (SoC) with 0.13 µm CMOS technology (Bourdel et al., 2009). Indeed, in the case of UWB signals occupying the whole FCC band, the constraints on the filter are fairly minimal, and a 3<sup>rd</sup>-order is enough to meet the FCC mask, which leads to reasonable losses despite the poor quality of passive circuits of these technologies. Here, the filter is current driven by a C class biased transistor, which reduces the consumption (Ec) to 2.2 pJ/Pulse for a 1 V<sub>pp</sub> pulse. Moreover, the authors show that the use of SoP technology would improve generator performance and that the use of conventional (non-ECL) logic would reduce the static consumption to 0 W. This performance represents the state of the art in terms of pulses generation covering the whole FCC band, and will be presented in detail in this chapter. However, these techniques are limited when the filter order increases in order to generate

However, these techniques are limited when the filter order increases in order to generate pulses with lower spectral occupation (Bourdel et al., 2007). Filtering a 75 ps elementary

pulse requires a 5<sup>th</sup> order to meet the ECC mask. It is then necessary to use an active filter in order to compensate the integrated filter's losses, which heavily penalizes the consumption, as shown by the circuit characteristics presented in Table 2. Furthermore, such a filter requires a significant number of inductors, which greatly increases the circuit's size.

In order to relax the constraints on the filtering, it is possible to use a sequence of elementary pulses instead of a single pulse (Smaini et al., 2006). In this way, it is possible to concentrate the pulse energy around the pseudo frequency of the sequence, thereby making filtering around this frequency easier. This technique can be used to generate pulses with a bandwidth of 500 MHz for applications in the 802.15.4 standard (Wentzloff & Chandrakasan, 2007). Eleven 120 ps elementary pulses at 120 ps spacing make it possible to generate a pulse in Channel 2 (4.05 GHz) after a simple filtering of the DC component. Varying the width, spacing, and number of pulses makes it possible to address different bands. Here, the consumption increases compared with the previous works presented, but it remains acceptable when compared with the energy of the pulse produced. However, it is not possible to achieve the consumption performance of the LO swintching designed for this same type of application using this technique, whereas small size (0.08 mm²) can be achieved due to the absence of inductors.

Table 2 summarizes the main characteristics of generators using pulse filtering. Here too, efficiencies are of the order of 1 % and levels do not exceed 1 V. However, this technique makes it possible to achieve higher bandwidths than those obtained with LO switching.

| Ref. | t<br>(ns) | BW<br>(GHz) | Vpp<br>(V)    | Ep<br>(pJ/P) | Ep<br>(pJ/P) | Ep<br>(pJ) | n      | Pdc           | Size<br>(mm²) | Techn.    | Mod. | Integ. |

|------|-----------|-------------|---------------|--------------|--------------|------------|--------|---------------|---------------|-----------|------|--------|

| 0    | 2         | nc          | 0.65          | nc           | nc           | 2.11       | nc     | nc            | 0.5           | 0.35 CMOS | ООК  | SoP    |

| 0    | 0.6       | 4.3         | 1             | 2.25         | 13.5         | 2.16       | 0.16   | 2.7mW@200MHz  | 0.54          | 0.13 CMOS | оок  | SoC    |

| 0    | 1.8       | 2.5         | 0.35          | 23.6*        | 52.4         | 0.55       | 0.01   | 13.1mW@250MHz | 1.02          | 0.13 CMOS | BPSK | SoC    |

| 0    | 0.6-0.8   | 2-4         | 0.35–<br>0.45 | 8*           | 62.5         | 0.41       | 0.006  | 10mW@160MHz   | 1.56          | 0.13 CMOS | BPSK | SoP    |

| 0    | 3         | 0.5         | 0.65          | 47           | nc           | 3.17       | 0.07** | nc            | 0.08          | 0.09 CMOS | BPSK | SoC    |

<sup>\*</sup> Estimate (Ec=Pdc\*τ), \*\* Ep/Ec

Table 2. Performance of baseband pulse filtering generators.

## 1.3. Synthesis by pulse combination

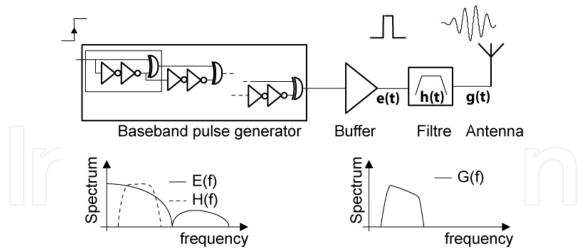

This technique is based on the principle (described in Fig. 3) that multi-cycle pulses s(t) are a combination of elementary single-cycle pulses  $e_n(t)$ .

Fig. 3. Principle of synthesis by pulse combination.

It appears that varying the shape of the elementary pulse has little influence on the final spectrum, and that only its amplitude and width have any real influence (Vauché et al., 2009). Hence it is possible to synthesize a complex pulse using a same pulse e(t) delayed and amplified. The major advantage of this technique lies in the fact that it is no longer necessary to use filters or oscillators and that it can be achieved without inductors. This gives to this technique a great deal of potential, particularly with the developments of submicronic technologies. The other major interest of this technique lies in its programmability. Indeed, it then becomes possible to adapt the pulse to a channel, to change its frequency band, to produce predistortion, or to compensate for process variation associated with manufacturing. However, this technique is not mature and few circuits have so far been produced.

The main studies carried out to date use the same technique for generating elementary pulses, namely an edge combiner based on a voltage controlled delay line (VCDL). However, these studies are characterized by the use of different combination methods. The elementary pulses can be current-combined by transistors of different sizes (Kim et al., 2004). The nature of the transistor (P or N) makes it possible to achieve the positive or negative alternation of the pulses. The consumption is very good (15 mW @ 500 MHz) as the output stage is unbiased and operates in switching mode. It is also possible with this technique to address different frequency bands by varying the combiner delays (Kim et al., 2006) (Kim et al., 2005). However, this topology remains limited in terms of programmability, as it is not possible to change the number of amplitude of the elementary pulses.

It is also possible to use current combination with differential pairs, which makes it possible to control the amplitude of the pulses by varying the biasing of the pairs (Bourdel et al., 2007). The positive and negative alternation of the pulses is achieved by cross-connecting the path of the differential pairs. Here, the number and amplitude of the pulses are not limited, which gives a great deal of latitude in programming. However, an output stage configured as a voltage follower is necessary to drive the power into a 50  $\Omega$  load. This output stage limits the performance in terms of amplitude (0.6V<sub>pp</sub> simulated using a 0.13  $\mu$ m CMOS Design Kit) and static consumption. The energy consumed per pulse remains acceptable (26.4 pJ/P) if high-performance power management is used, otherwise the circuit consumes 202 pJ/P @ 100 Mbs<sup>-1</sup>.

The principle of current summing using differential pairs can be used to produce bipolar pulses, or to relieve the constraints on the filtering in order to be able to achieve complete integration (SoC), using only an integrated output transformer (Demirkan et al., 2008). The circuit's consumption is substantial (71 pJ/P) because of the high data rate. However, the principle of this approach is validated with a measured pulse amplitude of 220 mV<sub>pp</sub>.

Triangular pulses and a charge pump can also be used to vary the amplitudes of the elementary pulses (Norimatsu et al., 2007). The value of the current in the charge pump sets the amplitude of the triangle. This circuit produces a pulse using just digital cells, and the size of the circuit reaches  $0.4~\text{mm}^2$  in  $0.18~\mu m$  CMOS technology. Moreover, the circuit achieves good performance in terms of amplitude and pulse width ( $1.24V_{pp}$  measured for a width of 1.75~ns). The main limitations lie in the consumption (29.7~mW @ 36~MHz) and the use of a discrete transformer for the positive and negative alternations of the elementary pulses.

| Ref. | t (ns) | BW<br>(GHz) | Vpp  | Ec<br>(pJ/P) | Ect<br>(pJ/P) | Ep<br>(pJ) | n     | Pdc                | Size<br>(mm²) | Techn.    | Mod. | Integ. |

|------|--------|-------------|------|--------------|---------------|------------|-------|--------------------|---------------|-----------|------|--------|

| 0    | 0.38   | 7.2         | 0.7  | 5.7*         | 30            | 0.47       | 0.015 | 15 mW @ 500 MHz    | nc            | 0.18 CMOS | оок  | No     |

| 0    | 0.38   | 7.2         | 0.92 | 0.74*        | 23.41         | 0.84       | 0.034 | 1.88 mW @ 77 MHz   | 0.78          | 0.18 CMOS | BPSK | No     |

| 0    | 0.36   | 6           | 0.6  | 26.4         | 202           | 0.32       | 0.002 | 20.24 mW @ 100 MHz | nc            | 0.13 CMOS | BPSK | No     |

| 0    | 0.53   | 4           | 0.22 | 68.4*        | 71.7          | 0.06       | 0.008 | 129 mW @ 1.8 GHz   | 2.83          | 0.09 CMOS | BPSK | SoC    |

| 0    | 1.75   | 1.4         | 1.24 | 52*          | 825           | 6.73       | 0.008 | 29.7mW @ 36 MHz    | 0.4           | 0.18 CMOS | BPSK | SoP    |

<sup>\*</sup> Estimate (Ec=Pdc.τ)

Table 3. Main characteristics of pulse synthesis generators.

## 1.4. Conclusions on the state of the art

This analysis of the state of the art highlights the major efforts that have been made to reduce pulse generator consumption, since the energy efficiency per pulse produced has gone from around 0.10 % to nearer 10 % in just a few years. In this context, baseband pulse filtering seems to have the greatest potential in terms of efficiency. It proves capable of generating pulses of large amplitude and of widths making it possible to address different bands, and particularly the broadest bands. However, "narrowband" (500 MHz) generation, particularly at higher frequencies, requires the use of a significant number of delays and logic functions in the combiner. This worsens consumption, as well as integration because of the balance needed for each path when designing the masks. For applications in the 500 MHz bands, the LC LO switching techniques yield the best results. However, the times response and the output buffers limit the pulse amplitude as well as efficiency, preventing these architectures from being able to address the highest bands. The use of a ring VCO (Sim et al., 2009) is an interesting example of convergence between these two techniques (pulse filtering and LO switching). Indeed, on the one hand the long delay lines needed for generating in the 500 MHz bands of the high band (> 6.5 GHz) seem destined to be replaced by switched ring VCOs, while on the other, using this type of function requires a shaping filter because of the high energy levels it generates in the lower bands. As far as pulse synthesis is concerned, this is currently slightly behind in terms of efficiency. The future of these techniques depends on the development of the technologies or on the needs of applications which may justify this increase in consumption that is inherent in pulse programming.

## 2. Analysis of the FCC and ECC standards

This section gives an analysis of the FCC and ECC standards using theoretical models, in order to evaluate the potential of UWB-IR systems in terms of range and data rate. In the case of switched signals, it appears that PSD increases as a function of the level of the pulse and as a function of the data rate. It is then possible to reduce the data rate in order to increase pulse amplitude (and hence detection) while maintaining a PSD that meets the standard. However, there is also a restriction on the peak value of the transmitted signal with the peak PSD limit, in order to restrain this practice. By analysing the average PSD (PSD<sub>av</sub>) and peak PSD (PSD<sub>pk</sub>) together we can evaluate the maximum amplitude value  $(g_{0max})$  allowed for a given modulation and the associated data rate. This analysis is

performed in the case of linear modulations (OOK, BPSK, PAM) for which the transmit signal (s(t)) and its PSD ( $S_{ss}(f)$ ) are expressed as:

$$s(t) = \sum_{k=0}^{K-1} q_k g\left(t - kT_k\right) \tag{4}$$

$$S_{ss}(f) = \frac{\sigma_q^2}{T_s} |G(f)|^2 + \frac{\mu_q^2}{T_s^2} |G(f)|^2 W_{Fs}(f)$$

(5)

where  $q_k$  is a random sequence with mean value  $\mu_q$  and variance  $\sigma_q$ , g(t) is the pulse waveform, and G(f) its Fourier transform. This analysis especially gives the potential of OOK and BPSK modulations in terms of detection and data rate in order to see which types of applications they are compatible with. Lastly, we assume here an ideal pulse with a spectrum defined by the FCC or ECC masks, in order to evaluate the maximum theoretical amplitude value and the associated data rate value.

## 2.1. Mean PSD

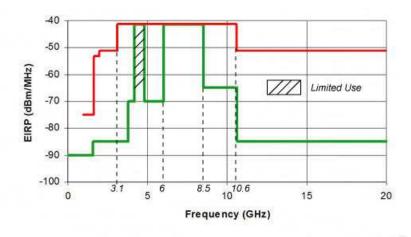

The mean PSD of a UWB signal is limited by the masks shown in Fig. 4

Fig. 4. FCC and ECC masks

If we ignore the power in the unallocated bands, the spectrum of the signal with the best spectral occupation is given by equation (3). It is a square function with a width (BW<sub>TOT</sub>) defined by the allocated band, and which is centred on the middle of this band (f<sub>0</sub>). Its inverse Fourier transform gives the ideal base pulse (equation 0).

$$G(f) = G_0 \left[ \Pi_{BW_{TOT}} \left( f - f_0 \right) + \Pi_{BW_{TOT}} \left( f + f_0 \right) \right]$$

$$\tag{6}$$

$$g(t) = 2.G_0.BW_{TOT}.\operatorname{sinc}(\pi BW_{TOT}t).\cos(2\pi f_0 t)$$

(7)

with (for the FCC standard):  $BW_{TOT} = 7.5$  GHz and  $f_0 = 6.85$  GHz and (for the ECC standard):  $BW_{TOT} = 2.5$  GHz and  $f_0 = 7.25$  GHz. The peak amplitude of the ideal pulse is then given by:

$$g_0 = 2G_0 B W_{TOT} \tag{8}$$

The ECC and FCC standards require the use of a spectrum analyser whose resolution filter bandwidth ( $RBW_{av}$ ) is set to 1 MHz. The measured PSD (single-sided) can then be expressed as follows, from 0:

$$DSP_{av}^{+}(f) = 2\frac{|G(f)|^{2}}{Z_{0}}D_{s}\left\{RBW_{av}.\sigma_{q}^{2} + D_{s}\mu_{q}^{2}W_{FS}\right\}$$

(9)

For both standard, the maximum value of the average PSD is set to −41.3 dBm/MHz and can be expressed as follows:

$$DSP_{\text{max}} = \max \left\{ \frac{2\sigma_q^2}{Z_0} D_s RBW_{av} G_0^2; \frac{2\mu_q^2}{Z_0} D_s^2 G_0^2 \right\} = 10^{-7.13}$$

(10)

Using 0 and 0, it is then possible to establish a relationship between the maximum amplitude allowed by the standard and the symbol rate as follow:

$$g_{0\text{max}} = \min \left\{ \left( \frac{2BW_{TOT}^2 Z_0.DSP_{\text{max}}}{D_s RBW_{av} \sigma_q^2} \right)^{1/2}, \left( \frac{2BW_{TOT}^2 Z_0.DSP_{\text{max}}}{D_s^2 \mu_q^2} \right)^{1/2} \right\}$$

(11)

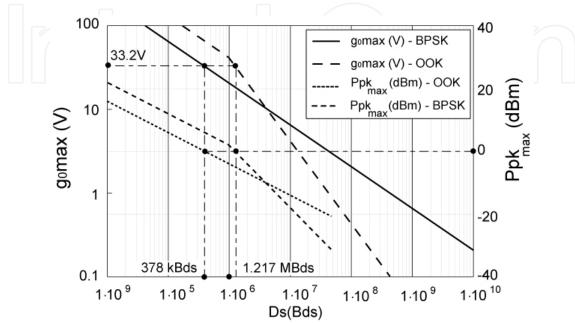

In Fig. 6,  $g_{0max}$  is represented as a function of  $D_s$  for OOK and BPSK modulation. However, it appears that if we consider only the limit imposed by the mean PSD, the maximum magnitude allowed value for data rates of the order of  $10 \text{ kbs}^{-1}$  exceeds 100 V. It is then necessary to evaluate the peak PSD.

## 2.2. Peak PSD

The ECC and FCC standards limit the peak power as follows. The peak PSD of the transmitted signal must be measured using a spectrum analyser in "peak detection" mode and in a 50 MHz resolution bandwidth ( $RWB_{pk}$ ). At the frequency where the mean PSD is maximum, the peak PSD must not exceed 0 dBm. This measurement can be interpreted in the following way: the peak power of an elementary pulse filtered by an ideal 50 MHz bandpass filter centred on  $f_0$  must not exceed 0 dBm. This interpretation is only valid where the symbol data rate is less than the spectrum analyser's RBW. Above this limit, the filter does not have the time to respond and the peak detector measures the power of the filter response to several pulses. However, it is at lower data rates (< 50 MHz) that this measurement is most meaningful, and this area of validity is sufficient for estimating the maximum allowed pulse magnitude.

Since the spectrum of the ideal pulse defined above is flat, the spectrum of the pulse filtered by the resolution filter (assumed to be ideal) together with its inverse Fourier transform can be expressed as follows:

$$G_{pk}(f) = G_0 \left[ \Pi_{RBW_{pk}} \left( f - f_0 \right) + \Pi_{RBW_{pk}} \left( f + f_0 \right) \right]$$

(12)

$$g_{pk}(t) = 2G_0.RBW_{pk}.\operatorname{sinc}\left(\pi RBW_{pk}t\right).\cos(2\pi f_0 t)$$

(13)

From 0, the peak power of the resolution filter output signal (which is the image of the peak PSD defined by the standard) can be expressed with  $G_0$  as follow:

$$P_{pk} = \frac{4.G_0^2.RBW_{pk}^2}{Z_0} = DSP_{pk} \text{ for Ds} < 50 \text{ MHz}$$

(14)

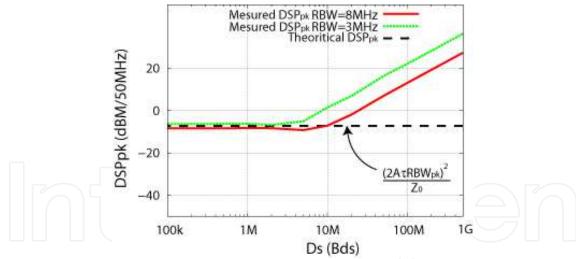

This interpretation of the evaluation of the peak PSD is validated by the measurements given in Fig. 5. Here, the peak PSD obtained from (11) is compared to the measurement, performed under the conditions imposed by the FCC standard, of an OOK sequence using RZ (Return to Zero) pulses of width  $\tau$  = 1 ns and amplitude A = 1 V. Let us note that the standard allows this measurement to be performed using an RBW lower than 50 MHz (but necessarily greater than 1 MHz). In this case, the measurement must be corrected by a factor equal to 20 log (RBW/50 MHz).

Fig. 5. Comparison of the model of the peak PSD and its measurement for OOK modulation using RZ pulses with an amplitude of A=1 V and a width of  $\tau$ =1 ns.

From 0 and (11), the peak PSD can be expressed as a function of  $D_s$  in the case where the pulse amplitudhe is adjusted to achieve the maximum allowed PSD ( $g_0 = g_{0max}$ ).

$$P_{pk} = \min \left\{ \frac{2.DSP_{\text{max}}.RBW_{pk}^{2}}{D_{s}\sigma_{q}^{2}.RBW_{av}}; \frac{2.DSP_{\text{max}}.RBW_{pk}^{2}}{D_{s}^{2}\mu_{q}^{2}} \right\}$$

(15)

## 2.3. Interpretation

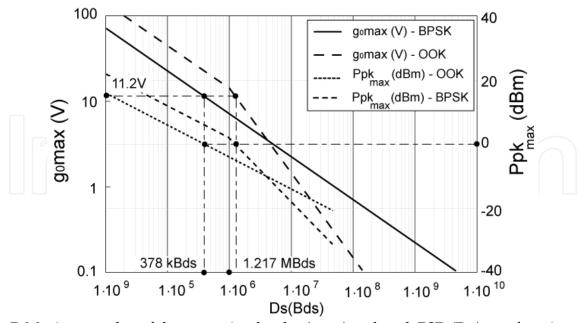

Fig. 6 and Fig. 7 (for the FCC and ECC standards respectively) show the maximum value of the ideal emitted pulse ( $g_{0max}$ ) given by 0 and the peak PSD ( $P_{pk}$ ) given by 0 in the case where the value of the mean PSD is the maximum allowed by the standards (DSP<sub>max</sub> =  $10^{-7.13}$ ). OOK and BPSK modulations are being considered here to compare their potential for low-cost applications.

Fig. 6. Maximum value of the transmitted pulse ( $g_{0max}$ ) and peak PSD ( $P_{pk}$ ) as a function of the data rate (Ds) for PSDav<sub>max</sub> =  $10^{-7.13}$  in the case of the FCC standard.

Fig. 7. Maximum value of the transmitted pulse ( $g_{0max}$ ) and peak PSD ( $P_{pk}$ ) as a function of the data rate (Ds) for PSDav<sub>max</sub> =  $10^{-7.13}$  in the case of the ECC standard.

Looking at  $g_{0max}(D_s)$ , the discontinuous spectrum limit in the case of OOK modulation appears clearly for data rates greater than RBW<sub>av</sub>. In fact, for data rates above 4 Mbs<sup>-1</sup>, BPSK modulation has greater potential. However, it is possible to generate pulses greater than 1 V in OOK u to 40 Mbs<sup>-1</sup> for the FCC standard and 14 Mbs<sup>-1</sup> for ECC For data rates below 4 Mbs<sup>-1</sup>, OOK modulation has greater potential than BPSK, because of the different variance. Let us note, moreover, that the values permitted by the FCC standard are higher than those of the ECC standard, since as the band is wider, the pulse energy is lower.

Observing the peak PSD shows that it is possible to reduce the data rate in order to increase the amplitude of the pulse up to 1.217 Mbs<sup>-1</sup> in OOK and 378 kbs<sup>-1</sup> in BPSK. Beyond these values, it is no longer possible to increase the amplitude by reducing Ds due to the peak power limitation. For these limit values, the pulse amplitude is 33.2 V in FCC and 11.2 V in ECC. In the case of 500MHz bandwidth signals, this value drop to 2V. Here again, OOK modulation has the greater potential.

In conclusion, it is preferable to choose OOK modulation when the intended data rates are lower than 4Mbs<sup>-1</sup> and BPSK when data rates are above 40 Mbs<sup>-1</sup> in FCC and 14 Mbs<sup>-1</sup> in ECC. The choice between the two may be influenced by the application needs and technical constraints. In an integrated circuit context where it is difficult to generate pulse amplitudes exceeding 1 V, OOK modulation is sufficient to achieve such a level up to 40 Mbs<sup>-1</sup> (or 14 Mbs<sup>-1</sup> in ECC). If application requirements in terms of detection (range) or data rate is more stringent so demand, BPSK modulation may be considered, at the expense of increased complexity.

## 3. Designing an FCC generator using elementary pulse filtering

The technique described here has been used in various works (Bourdel et al., 2009) (Bourdel et al. 2010) (Bachelet et al., 2006) and performs the best results in terms of amplitude and energy per pulse for frequency bandwidth above a few GHz. The principle of this technique is that given in Fig. 2. It is applied for the whole FCC band for an application requiring a data rate of  $36 \, \mathrm{Mbs^{-1}}$  and an amplitude  $g_0 > 1 \, \mathrm{V}$ .

## 3.1. Sizing

The first step in the design of the device shown in Fig. 2 consists in sizing the transmit filter. Several combinations of filters (h(t)) and baseband pulses (e(t)) can meet the FCC mask. In the case where e(t) is modelled by a square function ( $\pi_{\tau}(t)$ ) of width  $\tau$  and amplitude A, g(t) and its Fourier transform are:

$$g(t) = \frac{A}{\sqrt{l}} \pi_{\tau}(t) * h_{e}(t)$$

(16)

$$G(f) = \frac{A\tau \operatorname{sinc}(\pi\tau f).H_e(f)}{\sqrt{l}}$$

(17)

where h(t) is the ideal pulse response of the filter, and l the power losses.

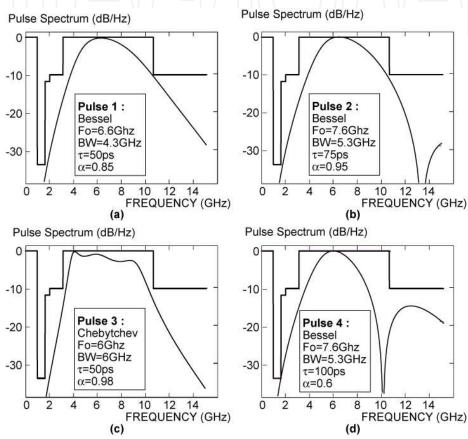

Fig. 8 shows the spectrum, evaluated from 0, of four pulses defined for different h(t) and different  $\tau$ . Because of its very broad nature, the FCC mask can be satisfied using low-order

filters, which is a major advantage for monolithic design in CMOS technology, where inductances have substantial losses.

Of all these different pulses, *pulse* 2 (Fig. 8b) exhibits the best compromise. First of all, it has good voltage efficiency ( $\alpha$ ), which represents the ratio between the amplitude (A) of the drive pulse (e(t)) and the amplitude (g<sub>0</sub>) of the filter output pulse (g(t)). Furthermore, the value of  $\tau$  is higher, which relaxes the constraints on the baseband generator. Lastly, the component values needed to produce it (Table 4) are compatible with the intended technology.

Fig. 8. Normalized spectral density ( $|G(f)|^2/G_0$ ) for different 3<sup>rd</sup>-order filters and different pulse widths.

The Fig. 6 shows that it is theoretically allowed to generate pulses exceeding 1 V magnitude with a data rate of  $36 \text{Mbs}^{-1}$  when using OOK modulation. For the case study presented here, the same analysis as presented in section 2 can be performed with a pulse g(t) given by 0 instead of 0 (Bourdel et al., 2010). From this analysis, a more accurate specification for the generator characteristics can then be deduced. In the case of *pulse* 2, we then have  $g_0 = 1.73 \text{ V}$ . 0 enables us then to evaluate the amplitude of e(t): A = 2.56 V.

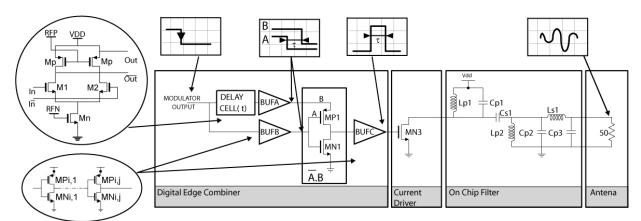

## 3.2. Design

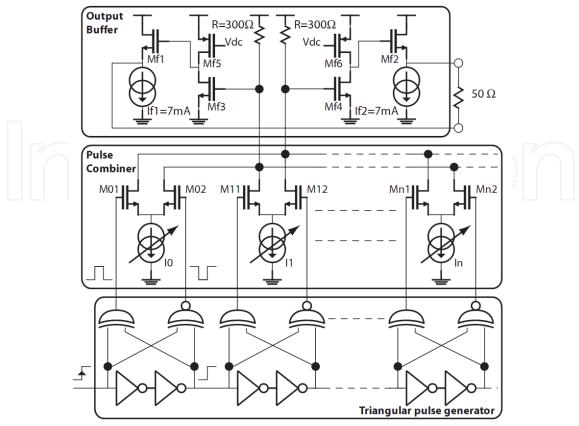

The architecture of the circuit presented is given in Fig. 9. The generator consists of a digital edge combiner (also referred to as a triangular pulse generator) producing the baseband

pulse, a driver, and an integrated filter. The filter is driven in current mode in order to provide an amplitude (A) at its input greater than the supply voltage ( $V_{DD}$  = 1.2V).

Fig. 9. Architecture of the FCC generator.

The design of the integrated filter is highly determined by the performances of the passive circuits available in the technology, especially the inductors. A preliminary study must be achieved to evaluate these performances. Inductor losses and self-resonance frequencies (srf) are actually heavily dependent on the inductor value (L). In the technology used in this design (0.13  $\mu$ m CMOS), best performance is achieved by inductors with 0.4nH<L<1.5 nH. For these values, the Q remains greater than 10 over the whole FCC band and the srf remains above 15 GHz. The capacitors exhibit better RF performance, as the range of values that ensure proper operation (Q > 50 and srf > 24 GHz) is from 100 fF to 2 pF. However, for higher values, a significant discrepancy between the nominal value and the value at 7 GHz is noted (10 % for 2 pF) and will need to be taken into account during the design.

The narrow range of possible inductor values imposes the major restriction on the choice of filter. Very fortunately, the relative bandwidth of the FCC band is close to unity, which limits the spread of component values. For any one filter, several topologies are possible, and the choice is determined by the value of the components they require. The topology chosen here (which is not a classic ladder filter topology) gives the component values given in Table 4.

| Lp1  | Cp1 (pF) | Cp1 (pF) | Cs1  | Ls1  | Lp2  | Cp2  | C3   |

|------|----------|----------|------|------|------|------|------|

| (nH) | (ideal)  | (Real)   | (fF) | (nH) | (nH) | (fF) | (fF) |

| 460  | 1.43     | 0.5      | 677  | 1.15 | 1.08 | 420  | 260  |

Table 4. Component values for the integrated filter.

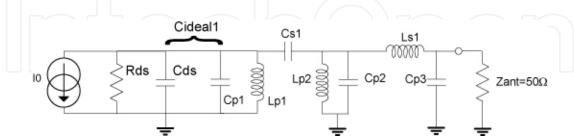

From the filter values it is then possible to size the current driver (MN3). The size of the transistor depends on A and the filter's input impedance  $R_{in}$ , for which this filter topology is the same as  $R_{out}$  = 50  $\Omega$  (antenna impedance). As the baseband pulse (0-V<sub>DD</sub>) is applied to the gate of MN3, the current supplied to the filter by the transistor during the conduction time ( $\tau$ ) can be approximated according to the small signal theory. The size of the transistor can then be expressed as follows:

$$W = \frac{L.A_{\text{max}}}{R_{IN}.\mu_0.C_{ox}(V_{DD} - V_t)^2}$$

(18)

The current needed to drive 2.56 V into 50  $\Omega$  is  $I_0$  = 51 mA, leading to a very large transistor. For such a transistor, the output impedance ( $R_{ds}$  and  $C_{ds}$  shown in Fig. 10) must be matched to the filter.

Fig. 10. Equivalent circuit of the driver and transistor.

Due to the high capacitance value in the first resonator, the effect of  $C_{ds}$  can easily be compensated for with  $C_{p1}$ . However, using such a simple topology, power matching  $(R_{ds}=R_{in})$  cannot be achieved independently of the value of  $I_0$ . The size of the transistor then becomes a compromise between the value of  $I_0$ , the matching  $(R_{ds})$ , and the driver consumption (size of MN3), which is the highest in the circuit. The size finally adopted  $(W=100~\mu m)$  provides a current of 58 mA (close to  $A_{max}/R_{out}$ ) leading to an output of  $g_0=1.73~V$ . The value of  $R_{ds}$  is 122  $\Omega$ . Better matching would have been obtained with a larger transistor, at the expense of an increased consumption.

The edge combiner's delay cells are made using mode current differential logic (MCDL) as shown in Fig. 9. The main interest of this logic is its speed, together with its low dynamic consumption. The delays can be varied by applying a control voltage to the gates of the P transistor, thereby modifying their dynamic resistance. Each cell produces a delay that can vary from 17 ps to 300 ps, thereby making it possible to compensate for variations in the manufacturing process and achieve the desired value of  $\tau$ . The edge combination is performed in a logic cell  $(A.\overline{B})$  using only two transistor, in this way making it possible to generate pulses of up to 50 ps. Lastly, buffers are needed to match the sizes of the transistors between the logic circuits, which use smaller transistors, and the driver. In order not to place all the constraint on buffer C, an initial series of buffers (buffers A and B) are placed between the delays and the logic function.

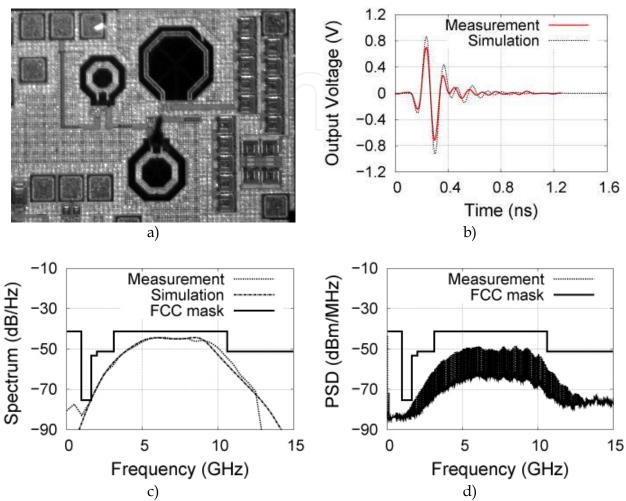

## 3.3. Results

The main measurement results are given in Fig. 11. The circuit (shown in Fig. 11a) occupies  $0.54~\rm mm^2$ . Pulse amplitude is  $1.4~\rm V_{pp}$  with a  $1.2~\rm V$  supply as presented in Fig. 11b and the spectrum of the generated pulses is FCC compliant as shown in Fig. 11c. Moreover, the FCC mask is satisfied for a  $36~\rm Mbs^{-1}$  data rate (Fig. 11d). The mean consumption is  $3.8~\rm mA~@~100~\rm MHz$ . The energy consumed per pulse is estimated at 9 pJ, especially due to the driver (MN3), which operates in C class. However, this performance can only be achieved if power management is used, as this estimation does not take DC consumption

between two pulses into account. Indeed, like most of previous published works present in the literature, this generator dissipates DC power, making the total energy consumed per pulse ( $E_{c_t}$ ) dependent on the data rate.

Fig. 11. Measurement results for the FCC generator.

## 4. Designing a pulse synthesizer for the FCC band

## 4.1. Principle

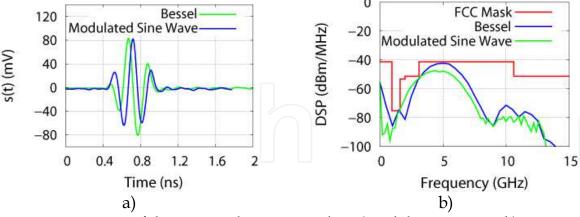

The principle of the pulse synthesizer is shown in Fig. 12. It uses the elementary pulse combination method presented in section 1.3. With this technique different pulse shapes can be synthesized using a single generator, in particular to compensate for PVT variations. The study presented here demonstrates the effectiveness of this technique in terms of programming and integration. The synthesizer is dimensioned to enable generation of the 5th derivative of a Gaussian pulse, together with the impulse responses of a Bessel filter presented in Fig. 3. In order to achieve this, the generator must include six stages in order to generate the six elementary pulses shown in Fig. 3Error! Reference source not found.

Fig. 12. Principle of combination using cross-connected differential pairs.

One of the main difficulties in pulse combination lies in the need to alternate the polarity of successive elementary pulses. The use of cross-connected differential pairs resolves this issue. Current summing is achieved into a load and each output is alternately cross-connected with the next in order to achieve the polarity alternation. The bias current  $(I_n)$  in each pair then sets the absolute value of  $g_n$ .

## 4.2. Design

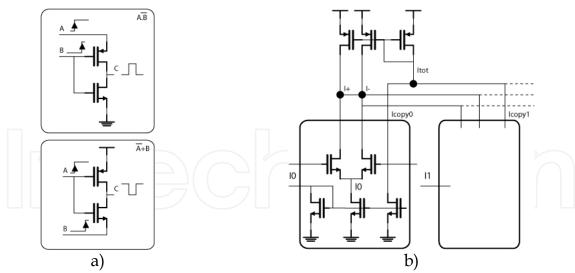

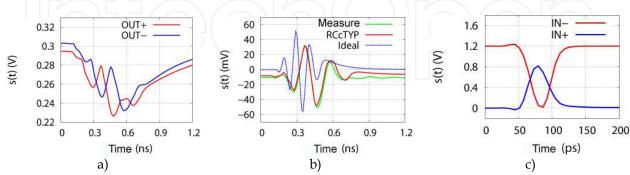

The use of differential pairs implies the use of a differential elementary pulse. In principle, this necessity does not prevent the use of a logic combiner. However, this introduces an asymmetry into the combiner, which has to use complementary logic functions to produce the positive pulse and its complement. Given that the width needed for a Gaussian pulse  $(\tau_n = 75 \text{ ps})$  is close to the minimum achievable in the considered technology (0.13  $\mu$ m CMOS), this asymmetry (represented in Fig. 14c) will lead to an imperfection in the driving of the differential pairs and the generation of a common mode. The delay cells used in the combiner are the ones given in Fig. 9 of the section 3. The complementary logic functions (shown in Fig. 13a) are  $(A.\overline{B})$  and  $(A.\overline{A})$  because these can be achieved using only two transistors, involving high speed performances.

Fig. 13. Generating the elementary pulse and its complement (a), current mirroring (b).

Moreover, driving a high-amplitude signal into the  $50 \Omega$  load imposed by the antenna constitutes one of the main constraints of this design. Indeed, insofar the use of inductors must be avoided to optimize integration, the gain-bandwidth product of the active cells that can be achieved in 0.13 µm CMOS technology considerably limits the amplitude of the transmitted pulse. In fact, the size of the transistors needed to drive such a load imposes cutoff frequencies well below 10 GHz. Several solutions have been implemented to mitigate this problem. First of all, the differential structure imposed by the combination structure is maintained right up to the antenna, thereby making it possible to double the output voltage. Common-mode rejection can be problem in a differential structure, however here, the distortion introduced by this common mode can be compensated for by the value of the g<sub>n</sub> co-efficients. In our case, the time constant for establishing this common mode, represented Fig.14a, is much slower than the elementary pulse, which leads to stretching of the final pulse s(t). This stretching can be cancelled out by adding an extra stage with a gain inverse to the common-mode value observed at the end of the pulse. The comparison of the current values I<sub>n</sub> with the normalized value of g<sub>n</sub> (given in Table 5) highlights this common-mode compensation. This specific feature demonstrates this structure's ability to compensate for distortions.

Fig. 14. ("post-layout") simulation of the single (a) and differential (b) output pulses and the drive (c).

| Ī | N                   | 0     | 1     | 2   | 3   | 4    | 5     | 6   |

|---|---------------------|-------|-------|-----|-----|------|-------|-----|

| Ī | $g_n$               | 0.06  | -0.43 | 1   | -1  | 0.43 | -0.06 | 0   |

| Ī | I <sub>n</sub> (mA) | 0.005 | 0.82  | 2.2 | 3.4 | 2.28 | 0.63  | 0.1 |

Table 5. Comparison of g<sub>n</sub> and I<sub>n</sub> values for the 5<sup>th</sup> derivative of a Gaussian pulse.

The differential pairs are combined into an active load biased by the mirroring of the  $I_n$  currents (shown in Fig.13b) making it possible to ensure a constant output stage gate voltage (Mf3 and Mf4), regardless of the values of  $g_n$  required to produce the pulse. The differential pair transistors are dimensioned to ensure the maximum gain into a high-impedance load, leading to a small size (3  $\mu$ m).

The output stage allows matching to the antenna. Several circuit arrangements have been envisaged. The voltage follower (SF) used in (Bourdel et al., 2007) was ultimately replaced by a common source (CS) circuit with a resistive load. Indeed, even though the SF circuit offers an output impedance of  $r_0$  =  $1/g_m$  over a very wide bandwidth (allowing it to perform "active" matching, coupling it to the CS buffering circuit (Mf3/Mf5 and Mf4/Mf6) leads to a total gain (CS plus SF) of significantly less than unity (Razavi, 2001). Furthermore, the DC current required by the output stage (7 mA) to achieve  $1/g_m$  close to  $50\,\Omega$  degrades the consumption performance.

Lastly, the measurements of this structure, given in Fig. 15, show an amplitude of  $160 \, \text{mV}_{pp}$  ( $200 \, \text{mV}_{pp}$  allowing for the  $2 \, \text{dB}$  loss in the measuring cable) for pulses meeting the FCC mask. These voltage levels are obtained using a modest technology ( $0.13 \, \mu m$  CMOS), without the use of inductors, and for signals with a  $10 \, \text{dB}$  bandwidth of  $3.5 \, \text{GHz}$ , which constitutes a good performance. However, these levels are still low and do not make it possible to achieve the ranges necessary for the intended applications. Hence other structures need to be studied in order to get over this limit.

Fig. 15. Measurement of the various elementary pulses a) and their spectrum b).

The circuit's total consumption is 38.4 mW @ 100 MHz, while the consumption per pulse during the pulse time (achievable assuming the use of power management) is 72 pJ. This performance is lower than that of the non-programmable structure. However the area occupied is very small (0.06 mm²) as no inductors are used and the programming ability offers the possibility of compensating for PVT variations or transmission distortion. This shows the great potential of this approach if the consumption bottleneck is overcame.

## 5. Conclusion

In this chapter, several aspects relating to the generation of UWB pulse signals have been addressed. The bibliographic study presented at the beginning of this chapter shows the advantages and limitations of the various techniques that are mainly being used. It also shows the significant effort put in to reducing the consumption of the generators and their great potential in terms of power saving, but also the limitations imposed by the technologies on the pulse amplitude and programming.

The standards appear to have a considerable effect on transmitter design. They have a high incidence not only on the spectrum of the transmitted pulse, but also on the modulation, the data rate, and the amplitude of the transmitted signal. Especially, understanding the relationship between the data rate and pulse amplitude enables the designer to best select the modulation required for an application, as well as to best size the generator.

Substantial research effort has recently been devoted to optimizing consumption and pulse amplitude in order to meet the requirements of low-cost and low-power applications. In this context, the generation technique based on exciting an integrated filter shows a great deal of potential. This technique makes it possible to produce pulse generators with the lowest dynamic consumption quoted in the literature to date for output amplitudes over 1 V, also giving them the best dynamic efficiency (Bourdel et al., 2009) (Bourdel et al., 2010).

In the field of programmable generators, research efforts have recently been begun with the aim of producing generators able to generate different pulse shapes, at high amplitudes, and occupying a limited area of silicon. Pulse programming needs to make it possible to address several frequency bands, as well as to compensate for PVT variations. An initial study based on pulse synthesis shows the feasibility making fully-programmable generator that consumes very small silicon area.

## 6. References

- Rui Xu; Jin, Y.; Nguyen, C.; (2006). Power-efficient switching-based CMOS UWB transmitters for UWB communications and Radar systems. *Microwave Theory and Techniques*, *IEEE Transactions on*, Volume 54, Issue 8, Aug. 2006 Page(s): 3271–3277.

- Wentzloff, D.D.; Chandrakasan, A.P. (2006). *Gaussian pulse Generators for subbanded ultrawideband transmitters*; Microwave Theory and Techniques, IEEE Transactions on; Volume 54, Issue 4, Part 2, June 2006 Page(s): 1647–1655.

- Datta, P.K.; Xi Fan; Fischer, G. (2007). *A Transceiver Front-End for Ultra-Wide-Band Application*; Circuits and Systems II: Express Briefs, IEEE Transactions on; Volume 54, Issue 4, April 2007 Page(s): 362–366.

- Phan, A. T.; Lee, J.; Krizhanovskii, V.; Le, Q.; Han, S.-K.; Lee, S.-G. (2008). *Energy-Efficient Low-Complexity CMOS Pulse Generator for Multiband UWB Impulse Radio*; Circuits and Systems I: Regular Papers, IEEE Transactions on; Volume 55, Issue 11, Dec. 2008 Page(s): 3552–3563.

- Barras, D.; Ellinger, F.; Jackel, H.; Hirt, W.(2006). *Low-power ultra-wideband wavelets generator with fast start-up circuit*; Microwave Theory and Techniques, IEEE Transactions on; Volume 54, Issue 5, May 2006 Page(s): 2138–2145.

Sanghoon Sim; Dong-Wook Kim; Songcheol Hong. (2009). *A CMOS UWB Pulse Generator for 6–10 GHz Applications*, Microwave and Wireless Components Letters, IEEE; Volume 19, Issue 2, Feb. 2009 Page(s): 83–85.

- Lee, J.; Park, Y. J.; Kim, M.; Yoon, C.; Kim, J.; Kim, K. H. (2008). System On Package Ultra-Wideband transmitter using CMOS impulse generator; Microwave Theory and Techniques, IEEE Transactions on; Volume 54, Issue 4, Apr. 2008 Page(s): 1667–1673.

- S. Bourdel, J. Gaubert, O. Fourquin, R. Vauche, and N. Dehaese, (2009). CMOS UWB Pulse Generator Co-Designed with Package Transition, IEEE Radio Frequency Integrated Circuits (RFIC) Symposium 2009, Publication Year: 2009, Page(s): 539 542.

- Bourdel, S.; Gaubert, J.; Battista, M.; Bachelet, Y.; Bas, G. (2007). *CMOS UWB transceiver for Impulse Radio*; Ultra-Wideband, 2007. ICUWB 2007. IEEE International Conference on 24–26 Sept. 2007 Page(s): 188–193.

- Smaini, L.; Tinella, C.; Helal, D.; Stoecklin, C.; Chabert, L.; Devaucelle, C.; Cattenoz, R.; Rinaldi, N.; Belot, D. (2006). *Single-chip CMOS pulse generator for UWB systems*; Solid-State Circuits, IEEE Journal of; Volume 41, Issue 7, July 2006 Page(s): 1551–1561.

- Wentzloff, D.D.; Chandrakasan, A.P. (2007). *A 47 pJ/pulse 3.1-to-5 GHz All-Digital UWB Transmitter in 90 nm CMOS*; Solid-State Circuits Conference, 2007. ISSCC 2007. Digest of Technical Papers. IEEE International; 11–15 Feb. 2007 Page(s): 118–591.

- H. Kim, D. Park, and Y. Joo, (2004). *All-Digital Low-Power CMOS Pulse Generator for UWB system*, Electronic Letters, vol. 40, November 2004. pp no. 24, 25

- Kim, H.; Joo, Y.; Jung, S. (2006). *A Tunable CMOS UWB Pulse Generator*; Ultra-Wideband, The 2006 IEEE 2006 International Conference on, 24–27 Sept. 2006 Page(s): 109–112.

- Hyunseok Kim; Youngjoong Joo; Sungyong Jung. (2005). *Digitally controllable bi-phase CMOS UWB pulse generator*; Ultra-Wideband, 2005. ICUWB 2005. 2005 IEEE International Conference on; 5-8 Sept. 2005 Page(s): 442–445

- S. Bourdel, Y. Bachelet, J. Gaubert, M. Battista, M. Egels, N. Dehaese, (2007). *Low-Cost CMOS Pulse Generator for UWB Systems*, Electronic Letters, vol. 43, issue 25, pp. 1425–1427, 6 December 2007.

- Demirkan, M.; Spencer, R.R. (2008). *A 1.8 Gpulses/s UWB Transmitter in 90 nm CMOS;* Solid-State Circuits Conference, 2008. ISSCC 2008. Digest of Technical Papers. IEEE International; 3–7 Feb. 2008 Page(s): 116–600

- Norimatsu, T.; Fujiwara, R.; Kokubo, M.; Miyazaki, M.; Maeki, A.; Ogata, Y.; Kobayashi, S.; Koshizuka, N.; Sakamura, K. (2007). *A UWB-IR Transmitter With Digitally Controlled Pulse Generator*; Solid-State Circuits, IEEE Journal of; Volume 42, Issue 6, June 2007 Page(s): 1300–1309

- R. Vauché, S. Bourdel, N. Dehaese, O. Fourquin, J. Gaubert; (2009). Fully Tunable UWB Pulse Generator with Zero DC Power Consumption; ICUWB 2009. IEEE International Conference on; Publication Year: 2009, Page(s): 418 422

- Cubillo, J. R.; Gaubert, J.; Bourdel, S.; Barthelemy, H. (2008). RF Low-Pass Design Guiding Rules to Improve PCB to Die Transition Applied to Different Types of Low-Cost Packages; Advanced Packaging, IEEE Transactions on; Volume 31, Issue 3, Aug. 2008 Page(s): 527–535

Bachelet, Y.; Bourdel, S.; Gaubert, J.; Bas, G.; Chalopin, H. (2006). *Fully integrated CMOS UVVB pulse generator*, Electronics Letters, Volume 42, Issue 22, Oct. 26 2006, Page(s): 1277–1278

- Jia-Sheng Hong, M.J. Lancaster; (2001). *Microstrip Filters for RF/Microwave Application*, Wiley-Interscience Publication.

- Behzad Razavi (2001) "Design of CMOS Integated Circuit" McGrawHill pub.

- S. Bourdel, Y. Bachelet, J. Gaubert, R. Vauché, O. Fourquin, N. Dehaese, and H. Barthelemy; (2010). *A 9 pJ/Pulse 1.42 Vpp OOK CMOS UWB Pulse Generator for the 3.1–10.6 GHz FCC Band* Microwave Theory and Techniques, IEEE Transaction on; Volume: 58, Issue: 1, Publication Year: 2010, Page(s): 65 73.

- Jeongwoo Han; Cam Nguyen. (2004). *Ultra-wideband electronically tunable pulse generators*; Microwave and Wireless Components Letters, IEEE; Volume 14, Issue 3, March 2004 Page(s): 112–114.

Edited by Boris Lembrikov

ISBN 978-953-307-139-8

Hard cover, 458 pages

Publisher Sciyo

Published online 17, August, 2010

Published in print edition August, 2010

Ultra wideband technology is one of the most promising directions in the rapidly developing modern communications. Ultra wideband communication system applications include radars, wireless personal area networks, sensor networks, imaging systems and high precision positioning systems. Ultra wideband transmission is characterized by high data rate, availability of low-cost transceivers, low transmit power and low interference. The proposed book consisting of 19 chapters presents both the state-of-the-art and the latest achievements in ultra wideband communication system performance, design and components. The book is addressed to engineers and researchers who are interested in the wide range of topics related to ultra wideband communications.

## How to reference

In order to correctly reference this scholarly work, feel free to copy and paste the following:

Jean Gaubert and Sylvain Bourdel (2010). Design of CMOS UWB Pulse Generators, Ultra Wideband, Boris Lembrikov (Ed.), ISBN: 978-953-307-139-8, InTech, Available from: http://www.intechopen.com/books/ultra-wideband/design-of-cmos-uwb-pulse-generators

## InTech Europe

University Campus STeP Ri Slavka Krautzeka 83/A 51000 Rijeka, Croatia Phone: +385 (51) 770 447

Fax: +385 (51) 686 166 www.intechopen.com

#### InTech China

Unit 405, Office Block, Hotel Equatorial Shanghai No.65, Yan An Road (West), Shanghai, 200040, China 中国上海市延安西路65号上海国际贵都大饭店办公楼405单元

Phone: +86-21-62489820 Fax: +86-21-62489821 © 2010 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the <u>Creative Commons Attribution-NonCommercial-ShareAlike-3.0 License</u>, which permits use, distribution and reproduction for non-commercial purposes, provided the original is properly cited and derivative works building on this content are distributed under the same license.