We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

185,000

200M

Our authors are among the

TOP 1% most cited scientists

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

# Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

## Chapter

# Memristor Synapses for Neuromorphic Computing

Sanghyeon Choi, Seonggil Ham and Gunuk Wang

## Abstract

Neuromorphic computing, which imitates the principle behind biological synapses with a high degree of parallelism, has recently emerged as a promising candidate for novel and sustainable computing technologies. The first step toward realizing a massively parallel neuromorphic system is to develop an artificial synapse capable of emulating synapse functionality, such as analog modulation, with ultralow power consumption and robust controllability. We begin this chapter with a simple description of neuromorphic systems and memristor synapses. Further, we introduce and evaluate the state-of-the-art neuromorphic hardware technology in terms of novel functional materials and device architectures toward the implementation of fully neuromorphic computers, which have been extensively explored in recent years. Finally, we briefly describe artificial neural networks based on memristor synapse in forms of crossbar arrays.

**Keywords:** memristor, artificial synapse, neuromorphic, bio-inspired, memristive systems

## 1. Introduction

Modern computers and electronics, such as smartphones and supercomputers, have been developed in accordance with Moore's law [1], which implies improvement in cost, speed, and power consumption by scaling down devices. However, the fundamental physical limits and increased fabrication costs pose a hindrance to sustainable development of computing technology [2, 3]. Moreover, with the advent of the big data era, unstructured data and data complexity explosively increases, imposing constraints on the conventional computing technology owing to the von Neumann bottleneck [4, 5]. Neuromorphic systems [6, 7], which mimic the nervous system in the brain, have recently become known as strong candidates to overcome these technical and economic limitations owing to their proficiency in cognitive and data-intensive tasks, together with their low power consumption. To successfully implement these neuromorphic systems, it is of utmost importance to research and develop artificial synapses capable of synapse functions, high reliability, low energy consumption, etc. [8, 9]. In the plethora of possible devices, memristors have gained the spotlight because of their desirable characteristics as artificial synapses [10–12], including device speed [13], footprint [14], low energy consumption [15], and analog switching [16, 17].

In this chapter, we introduce the basic concepts of neuromorphic systems and memristor synapses. We also describe diverse examples for state-of-the-art artificial synapses in terms of novel functional materials and device architecture. We then briefly review the implemented neuromorphic systems based on memristor synapses.

## 2. Neuromorphic systems and memristor synapses

## 2.1 Neuromorphic systems

Conventional computing architecture, that is, von Neumann architecture, forms the groundwork for modern computing technologies [3, 18]. Despite tremendous growth in computing performance, classical architecture currently suffers from the von Neumann bottleneck, which results from data movements between the processor and the memory unit [4, 5]. The memory wall issue, causing high power consumption and low speed, hinders the continuous development of computing technologies [4, 5, 9]. Moreover, artificial neural network (ANN) algorithms, such as deep learning [19], deal with image classification [20, 21], sound recognition [22, 23], specific complex tasks (e.g., the AlphaGo [24]) and so on. Although the ANN algorithms have exhibited superior performance over the conventional computing technologies, they are, at present, constructed on the von Neumann architecture; hence, considerable time and energy resources are required for their operation [8, 9]. Neuromorphic architecture [6, 7], a bio-inspired computing architecture, is one of the most promising candidates to resolve these problems. The neuromorphic systems take advantage of the cerebral nervous system, which consists of a massive parallel connectivity between the neurons (i.e., processor) and the synapses (i.e., memory), indicating the absence of the von Neumann bottleneck [8, 9]. Figure 1 shows the shift of the computing architecture from von Neumann architecture (Figure 1a) to neuromorphic architecture (Figure 1b). The von Neumann architecture shows that the processor and memory are separate, leading to the von Neumann bottleneck. In contrast, in the case of neuromorphic architecture, the neurons and synapses are combined, alleviating the bottleneck issue. The neurons are uncomplicated computing units, the synapses are local memory units, and the communication channels (red line) connect numerous neurons and synapses. It should be noted that the practical purpose of neuromorphic systems is not to replace the von Neumann architecture completely, but to supplement the conventional architecture to make up its leeway, especially for intelligent tasks such as image recognition and natural language processing.

### Figure 1.

(a) Conventional computing architecture (von Neumann architecture). Data transfer is performed through the bus (memory wall). (b) Neuromorphic architecture. In contrast to von Neumann architecture, von Neumann bottleneck does not exist.

### 2.2 Memristor synapses

Memristors that consist of a storage layer inserted between the top and bottom electrodes can undergo dynamic reconfiguration within the storage layer with the application of electrical stimuli, resulting in resistance modulation referred to as memory effect [16, 17]. The changed resistance state can be retained even after electrical inputs are removed, and memristors are based on the history of applied electrical stimuli. These capabilities lead to analog switching, which resembles biological synapses where the strength (or synaptic weight) can increase or decrease depending on the applied action potential [25, 26]. When neuromorphic architecture is implemented on the conventional computing architecture, the synaptic weights are stored in the memory unit and are continuously read into the processor unit to transfer information to post-neurons. In other words, practically, the von Neumann bottleneck still remains challenged. However, in case of memristor synapse-based neuromorphic systems, the synapses can not only store a specific weight but also naturally transmit information into post-neurons, overcoming the von Neumann bottleneck and improving system efficiency [8, 9]. In addition to analog switching, memristors have exhibited desirable device properties, including nanoscale footprint [14], long endurance and retention [17, 27], nanosecond switching speed [13, 15], and low power consumption [15]. Owing to these characteristics, memristors have emerged as promising candidates for artificial synapses. However, it should be noted that no specific material/device system has shown all-encompassed characteristics so far.

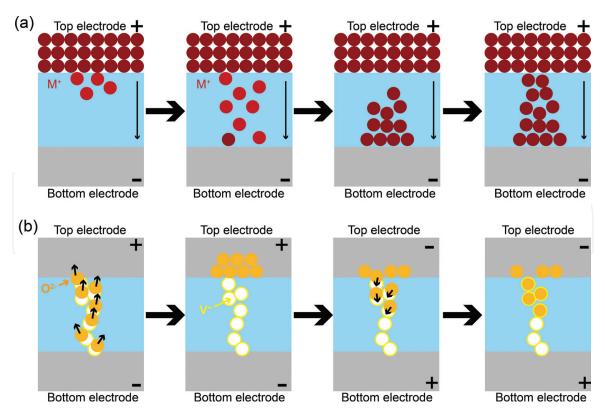

### 2.3 Switching mechanisms

Depending on their storage layer and electrode, memristors can be broadly classified into two categories: cation-based devices and anion-based devices. It is widely believed that cation-based devices are based on migration of metallic cations (see Figure 2a) [17, 28]. They employ electrochemically active materials such as Ag or Cu as an electrode [29–32]. The counter electrode is usually an electrochemically inert material, such as Pt, Au, or W, and the storage layer consists of a solidelectrolyte like  $Ta_2O_5$ , SiO<sub>2</sub>, or Cu<sub>2</sub>S. For example, when a positive voltage is applied to an Ag top electrode, the atoms from this electrode are electrochemically oxidized to Ag<sup>+</sup> cations because of anodic reaction, which are then dissolved into a solidelectrolyte layer. The Ag<sup>+</sup> cations migrate across the solid-electrolyte layer toward the counter electrode (e.g., Pt) depending on electric field. At the Pt electrode, the Ag<sup>+</sup> cations are electrochemically reduced to Ag atoms because of cathodic reaction and are deposited on its surface. Thus, conductive filaments grow toward the Ag top electrode, and eventually the filaments bridge the anode and the cathode, indicating that the device switches into ON state (low resistance state) as shown in Figure 2a. In contrast, when a negative voltage is applied to the Ag top electrode, the Ag filament begins to dissolve anodically, starting from the interface of the Ag top electrode/Ag filament, which results in OFF state (high resistance state). Owing to this process, cation-based devices are referred to as electrochemical metallization memories and conductive bridging random access memories. It should be noted that the initial formation of conductive filaments is called the electroforming process, which needs a voltage higher than a switching voltage.

Anion-based devices usually require the initial electroforming process and are switched depending on the  $O^{2-}$  anions (or positively charged oxygen vacancy V) induced into the storage layer by soft-breakdown (see **Figure 2b**). These devices consist of a sub-stoichiometric storage layer made of HfO<sub>x</sub> [33, 34], TaO<sub>x</sub> [35, 36], WO<sub>x</sub> [37, 38], etc. When a positive forming voltage is applied to the top electrode,

Figure 2.

(a) Cation-based devices: Through electrochemical reaction, metal cations  $M^+$  migrate toward the counter electrode and form conductive filaments between the top and bottom electrodes. (b) Anion-based devices: During electroforming, the soft-breakdown leads to  $O^{2^-}$  ions (oxygen vacancies V), and the oxygen vacancies form conductive filaments between the top and bottom electrodes.

the induced  $O^{2^-}$  ions migrate toward it. This anion motion causes a change in the valence state of the cation to keep the charge neutral; hence, these devices are also referred to as valance change memories. Throughout the process, the oxygen vacancies continue to form conductive filaments in the storage layer. When the filaments bridge the top and bottom electrodes, current flows through the filaments, with the result that the device switches to ON state. Contrastingly, when a negative voltage is applied to the top electrode, the  $O^{2^-}$  ions either recombine with oxygen vacancies present in the filaments or oxidize the cation precipitates, with the result that the device switches to OFF state. Thus, memristors could be understood to some extent based on cation- and anion-based mechanisms. However, identifying the precise mechanism of a specific device is a challenge because of the presence of mingled mechanisms and different driving forces or locations. Therefore, further studies are necessary for a deeper understanding of the switching mechanism.

## 2.4 Desirable properties of memristor synapses

Various properties of memristor synapses that affect the performance of neuromorphic computing need to be discussed in detail. Among them, representative characteristics such as the linearity in weight update, multilevel states, dynamic range (ON/OFF ratio), variation, retention, endurance, and footprint will be addressed in this section as they can substantially affect computing achievements [8, 35]. The linearity of the weight update indicates the linear relationship between synaptic weight change ( $\Delta$ w) and programming pulse. In other words, the conductance of the memristor synapse changes linearly in accordance with the number of programming pulses, which is associated with the mapping of weight in the algorithms for conductance in memristor synapses. Hence, the linearity of weight update affects the performance (e.g., accuracy). Notably, most memristor synapses

*Memristor Synapses for Neuromorphic Computing* DOI: http://dx.doi.org/10.5772/intechopen.85301

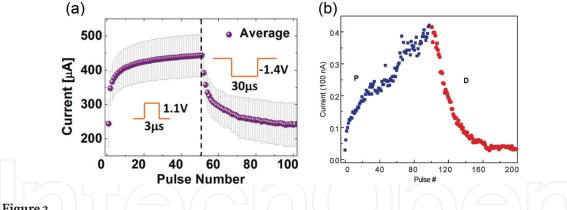

Figure 3.

(a, b) Nonlinearity of weight update. Current abruptly changes in initial pulses and gradually saturates. Most memristors exhibit a nonlinear relationship. All figures are reproduced with permission from Ref [39, 10], respectively. Copyright (2017, 2010) American Chemical Society.

show a nonlinear weight update, where the conductance change gradually saturates, as shown in **Figure 3**. Hence, the nonlinearity of weight update should be improved to achieve highly efficient computing.

The resolution capability of storage is influenced by multilevel states and dynamic ranges because numerous conductance states can distinguishably store individual pixels of input patterns. Moreover, variations, including cycle-to-cycle and device-to-device variations, could degrade neuromorphic computing, particularly in large-scale systems. However, considering that neuromorphic computing exhibits the fault-tolerant property, neuromorphic architectures could be immune to the variation to some extent, and this is supported by several papers [8, 35, 52]. In addition, memristor synapses are repeatedly updated during the training process and should retain the trained weights (i.e., final conductance). Subsequently, the larger the endurance cycles and retention time, the better are the achievements of the neuromorphic network. Last but not least, it is desirable that device's footprint is below sub-10 nm because high density leads to more synaptic devices that store learned information under a specific area [8].

Furthermore, it is efficient to improve the characteristics of memristor synapses depending on individual neuromorphic networks, because a desirable memristor synapse capable of being employed into neuromorphic systems is yet to be reported. Supervised learning-based networks [35, 40–44], for example, are less vulnerable to cycle-to-cycle and device-to-device variations. This is because memristor synapses are updated according to calculated errors under known target values. By contrast, the networks based on unsupervised learning [39, 45–47] are directly affected by the variation owing to unknown target values. Therefore, memristor synapses need to be designed or selected depending on individual neuromorphic networks.

# 3. Artificial synapses in terms of device architecture and novel functional materials

Memristors for synaptic devices with two-terminal (e.g., vertical/planar-type and gap-type) and three-terminal (e.g., field-effect transistor and lateral coupling type) structures are manufactured by well-established processing technologies [7–12, 35, 39–55].

In the case of a two-terminal structure, when different voltages are applied to each of the two electrodes, resulting in current flow through the insulator, varying the conductance of the device enables emulation of biological synapse functions such as synapse plasticity [10–12, 16, 35, 48]. In particular, the crossbar array of

two-terminal devices has received attention because of its characteristics relevant to synaptic devices, such as scalability for high density, simple fabrication process, low cost of fabrication, parallel connection structure, low power, fault-tolerance, and compactness. Thus, they are expected to provide an appropriate structure to support synaptic electronics. The type of two-terminal memristors that are being reffered to as the artificial synapses includes resistive random-access memory, phase change memory, conductive bridge memory, and spin-based memory. Although two-terminal devices are attracting much attention because of their ease of implementation of crossbar arrays, a two-terminal device, as a matter of fact, requires a select device to eliminate the sneak path that occurs in a crossbar array configuration. Additionally, it is difficult to imitate complex synaptic functions such as hetero-synaptic plasticity (e.g., modulatory input-dependent plasticity).

Three-terminal structures (e.g., field effect transistor memory and floating/gate transistor memory) with tunable conductance of channels between the source and the drain are also considered as synaptic devices [49–51]. The gate electrode acts as the pre-synapse, transferring the stimulus to the insulating layer, indicating the cleft of the synapse, and modulates the conductance of the channel representing the synaptic strength. Although the three-terminal structure is more complicated than the two-terminal structure and is disadvantageous in terms of density, the terminal for the signal transmission process and the learning terminal are separated such that simultaneous signal processing is possible, and complex synapse functions such as hetero-synaptic plasticity can be mimicked. Moreover, they do not require an additional selector device to reduce sneak current in an integrated array architecture.

Recently, going beyond simply implementing a synapse function, researchers have demonstrated advanced concepts of synapse device functions, including selfrectification, photo-assisted synaptic plasticity and neuromodulation to achieve more delicate imitation of the human brain and learning-and energy-efficiency in neurocomputing.

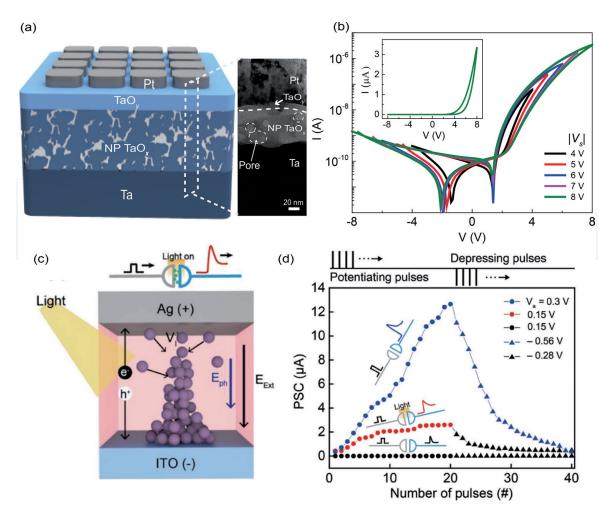

In [35], Choi et al. fabricated a self-rectifying memristor synapse through a twoterminal structure (Pt/TaO<sub>y</sub>/nanoporous TaO<sub>x</sub>/Ta), which is capable of suppressing unwanted leakage pathways and then a 16 x 16 crossbar array using only the devices without an additional selector (see **Figure 4a** and **b**). The mechanism of memristive switching and synaptic functions, including long-term potentiation (LTP), STDP (spike-timing dependent plasticity), and long-term depression (LTD) were caused by the migration of  $O^{2-}$  ions with oxygen vacancies V by applied electric field in the TaO<sub>x</sub>. In addition, the asymmetric interface contacts of Pt/TaO<sub>y</sub> and TaO<sub>x</sub>/Ta prevent the undesired signal by performing the self-rectification function without the selector.

In [51], Huh et al. reported a synapse device that performs the neuromodulator function of a barristor structure using 2D material as shown in **Figure 4c**. The three-terminal device consisted of a vertically integrated monolithic tungsten oxide memristor, and a variable-barrier tungsten selenide/graphene Schottky diode, termed as a "synaptic barrister." This synaptic barristor could implement fundamental synaptic functions, including short-term plasticity (STP), paired pulse facilitation (PPF), LTP, and LTD, with external gate controllability, termed as a neuromodulator in bio-synapse. This architecture potentially offers considerable power-saving benefits while significantly tuning the synaptic weights and intrinsically modifying the synaptic plasticity, in comparison with conventional two-neuronal-based synaptic architectures.

In [52], Ham et al. fabricated an organo-lead halide perovskite (OHP)-based photonic synapse in which the synaptic plasticity is modified by both electrical pulses and light illumination. The switching mechanism originates from the presence of a conductive filament by iodine-vacancy mediator, with its switching states controlled by electric-field domination (see **Figure 4d**). Using diverse electrical stimuli and

*Memristor Synapses for Neuromorphic Computing* DOI: http://dx.doi.org/10.5772/intechopen.85301

#### Figure 4.

(a) Schematic of a self-rectifying memristor with a Pt/TaO<sub>y</sub>/nanoporous TaO<sub>x</sub>/Ta and cross-sectional image of a memristor synapse. (b) I-V curves of the self-rectifying memristor synapse. (a, b) are reproduced with permission from Ref [35] under a Creative Commons Attribution 4.0 International License. (c) Schematics of the suggested mechanism of how a conductive switching filament is formed by the iodine vacancy migration in the presence of light. (d) Synaptic potentiation and depression behavior of the OHP-based synaptic device. (c and d) are reproduced with permission from Ref [52]. Copyright (2018) John Wiley and Sons.

relative timing between the input pulses, essential synaptic functionalities such as STP, LTP, and LTD were successfully demonstrated. In addition, owing to the accelerated migration of the iodine vacancy inherently existing in the coated OHP film under light illumination, the OHP synaptic device exhibits light-tunable synaptic functionalities with very low programming inputs ( $\approx 0.1$  V) as shown in **Figure 4d**. The ability of high-order tuning of the photo-assisted synaptic plasticity in an artificial synapse can offer significant improvements in the processing time, low-power recognition, and learning capability in a neuro-inspired computing system (**Figure 4e**).

In [12], Wang et al. designed a diffusive memristor for STP synapses and threshold neurons. The devices contain a switching layer doped with Ag nanoclusters (MgO<sub>x</sub>:Ag, SiO<sub>x</sub>N<sub>y</sub>:Ag, and HfO<sub>x</sub>:Ag) using the co-sputtering method. The switching mechanism is based on the growth and relaxation of Ag nanoclusters depending on whether the voltage pulse is applied, which was experimentally verified by in-situ high-resolution transmission electron microscopy (HRTEM). The designed device mimicked STP under PPF and PPD. Moreover, the device was used as a threshold neuron along with drift memristor synapse based on TaO<sub>x</sub> to emulate STDP learning rule. Because the conductance of the device gradually increases according to applied voltage and then abruptly decreases under no applied voltage, the device can be used as a threshold neuron. The results give a potential application for simple artificial neurons as compared with CMOS artificial neurons [53, 54].

# 4. Neuromorphic systems based on crossbar array of memristor synapses

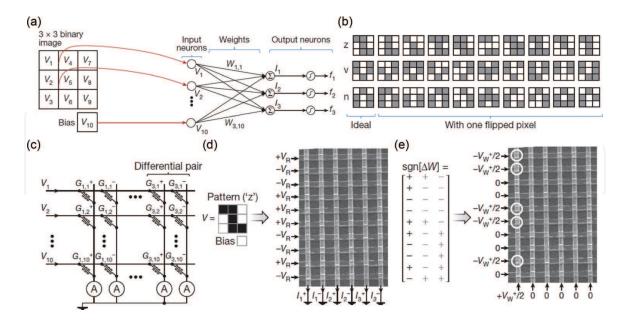

Prezioso et al. experimentally demonstrated neuromorphic networks based on memristor synapses (see [55]). In their paper,  $Al_2O_3/TiO_{2-x}$  memristor was used to fabricate a 12 × 12 crossbar array to implement a single-layer network [56]. The single-layer network architecture was schematically described as shown in Figure 5a, where 10 input neurons and 3 output neurons are fully linked by  $10 \times 3 = 30$ synaptic weights  $(W_{i,j})$ . Notably, this ANN architecture naturally corresponds to a crossbar array [9, 35]. Input voltages  $(V_{i=1...9})$  assigned from pixels of the  $3 \times 3$  input images (see Figure 5b) were applied to each input neuron. After being applied into the network, the input voltages were individually weighted depending on each synaptic weight. Note that  $V_{10}$  is a bias voltage to control the degree of activation of the output neurons. The output neurons received each weighted voltage through linked weights and then integrated the weighted voltages  $(\sum W_{i,j}V_j)$ , where *j* and *i* represent the input (j = 1-9) and output (i = 1-3)neurons respectively. The output neurons converted each integrated voltage into output ( $f_i$ ) ranging from -1 to 1 according to the nonlinear activation function:  $f_i = \tanh(\beta I_i)$ , where  $\beta$  adjusts the nonlinearity of the activation function and  $I_i = \sum W_{i,i}V_i$ . The activation function can be considered as the threshold firing function in a biological neuron. The synaptic weights were represented by a pair of adjacent memristors ( $W_{i,j} = G_{i,j}^+ - G_{i,j}^-$ ) for the effectiveness of weight update. The number of selected memristor synapses in  $12 \times 12$  array were  $30 \times 2 = 60$ , due to a pair of memristors (Figure 5c). When the network was under the training process, as shown in Figure 5d and e, memristor synapses between input and output neurons were updated based on the Manhattan update rule, which is classified as supervised learning:  $\Delta W_{ij} = \eta \operatorname{sgn} \sum [(t_i(n) - f_i(n)) \times df/dI \times V_j(n)],$

#### Figure 5.

(a) Input voltages corresponding to an input image  $(V_{i=1...9})$  and a bias voltage  $(V_{10})$ . These voltages are fed into the single-layer network where 10 input neurons and 3 output neurons are linked by synaptic weights. (b) The "z," "v," and "n" input images. Aside from ideal images, other images contain one noise pixel. (c) The schematic of implemented 10 × 6 crossbar array, a pair of adjacent memristors provide one synaptic weight. (d) When an image (e.g., "z") is fed into network, pixels for black give  $V_R$  (read voltage) to the network, otherwise,  $-V_R$  is applied into the network. (e) An instance of weight update according to Manhattan update rule. The synaptic weights corresponding to sign + should be increased, so that the memristors representing  $G_{1,1}$ ,  $G_{1,2}$ ,  $G_{1,5}$ ,  $G_{1,6}$ , and  $G_{1,9}$  are applied by set voltage. All figures are reproduced with permission from Ref [55]. Copyright (2015) Springer Nature.

### *Memristor Synapses for Neuromorphic Computing* DOI: http://dx.doi.org/10.5772/intechopen.85301

where  $\eta$  is the learning rate,  $t_i(n)$  is the target value,  $f_i(n)$  is the output value, and n is the n<sup>th</sup> input image. After the training process was complete, the memristor synapses retained their final conductance, and the test process was performed without weight update (see **Figure 5d**). From the test process, the neuromorphic network exhibited perfect classification for the first time in 21 epochs (note that one epoch indicates one training process). Although simple and few input images were used to train/test the neuromorphic network, this work greatly contributed to neuromorphic systems based on memristor synapses in terms of experimental demonstration using crossbar arrays.

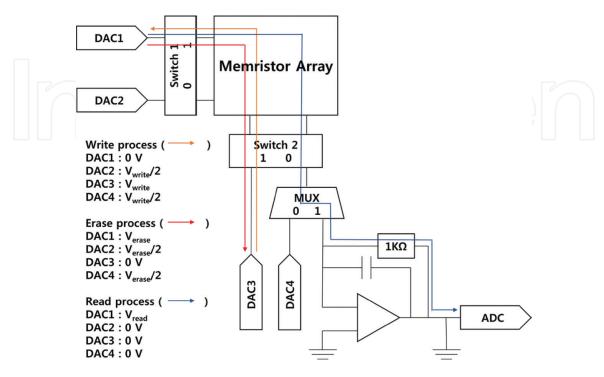

It should be noted that the circuit that acquires sgn[ $f_i(n)$ ] = sgn[ $\sum W_{i,j}V_j$ ] = sgn  $\left[\sum (G_{i,j}^{+} - G_{i,j})V_{j}\right]$  could be implemented by a virtual ground circuit and a differential amplifier [43, 57]. Then, the output value is compared with the target value by circuits using a comparator. According to calculated  $\Delta W_{i,j}$ , programming memristors of the array, for example, could be performed as shown in Figure 6 [39]. The test board contains four digital-to-analog converters (DACs) providing voltage pulses through the DACs. The DACs 1–4 represent the chosen bottom line, the unchosen bottom line, the chosen top line, and the unchosen top line, respectively. Using matrix switches (Switch 1 and 2), individual memristor is assigned to the corresponding DAC. The multiplexer (MUX) is operated to obtain currents that flow through memristors in the array by delivering the currents into the analog-to-digital converter (ADC). The ADC obtains the applied voltage of the resistor  $(1 \text{ k}\Omega)$ , and the voltage is changed into the current. The arrows of Figure 6 represent the current flowing through a chosen memristor in case of write, erase, and read processes. Notably, there are non-idealities such as sneak currents and wire resistance in array-level, which could degrade the performance of neuromorphic computing [35, 44, 58–60]. The sneak currents affect learning accuracy and epochs because of undesired information, especially large-scale array. In Figure 6, in order to avoid sneak currents during read process, unchosen rows and columns are grounded [39]. Moreover, wire resistance consumes input voltages, so that memristors far from points of input voltage could be applied by smaller voltage than input voltage.

#### Figure 6.

Circuit scheme for write, erase, and read processes. The figure is reproduced with permission from Ref [39]. Copyright (2017) American Chemical Society.

This influences output currents, leading to degradation of learning performance. The non-idealities in array-level could be overcome by device functions [35, 44], operational scheme [39, 58–60], or learning algorithms [35, 40–44] to some degree.

## 5. Conclusion

Neuromorphic systems are one of the most promising candidates to deal with the von Neumann bottleneck caused by the memory wall between memory and process units. Using memristor synapses simply classified into cation- and anionbased devices can resolve this bottleneck owing to their storage and transmittance capabilities. To obtain higher performance of neuromorphic systems, representative characteristics, including the linearity of weight update, large multilevel states and dynamic range (ON/OFF ratio), variation and endurance, and retention need to be improved. In this context, different memristor synapses based on novel materials and device structures were introduced. Finally, we have briefly explained neuromorphic networks based on crossbar arrays of memristor synapses, and the network demonstrated perfect classification after 21 epochs. We believe that this chapter offers a deep understanding of the field of memristor synapses.

## Acknowledgements

This work was supported by the National Research Foundation of Korea (NRF-2016R1C1B2007330 and NRF-2019R1A2C2003704), KU-KIST Research Fund, Samsung Electronics, and a Korea University Future Research Grant.

## **Conflict of interest**

The authors declare no competing interests.

## **Author details**

Sanghyeon Choi, Seonggil Ham and Gunuk Wang<sup>\*</sup> KU-KIST Graduate School of Converging Science and Technology, Korea University, Seoul, Republic of Korea

\*Address all correspondence to: gunukwang@korea.ac.kr

## IntechOpen

© 2019 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Memristor Synapses for Neuromorphic Computing DOI: http://dx.doi.org/10.5772/intechopen.85301

## References

[1] Lundstrom M. Moore's law forever? Science. 2003;**299**:210-211. DOI: 10.1126/science.1079567

[2] Frank DJ, Dennard RH, Nowak E, Solomon PM, Taur Y, Wong H-SP. Device scaling limits of Si MOSFETs and their application dependencies. Proceedings of the IEEE. 2001;**89**:259-288. DOI: 10.1109/5.915374

[3] International Technology Roadmap for Semiconductors 2.0 (ITRS). Beyond CMOS [Internet]. 2015. Available from: http://www.itrs2.net/ [Accessed: January 29, 2019]

[4] Backus J. Can Programming be Liberated from the von Neumann Style?: A Functional Style and its Algebra of Programs. Pennsylvania Plaza, New York: ACM; 2007. DOI: 10.1145/1283920.1283933

[5] Sally A. Reflections on the memory wall. In: Conference on Computing Frontiers; 14-16 April 2004; Italy. New York: ACM; 2004. p. 162

[6] Mead C. Neuromorphic electronic systems. Proceedings of the IEEE. 1990;**78**:1629-1636. DOI: 10.1109/5.58356

[7] Kuzum D, Yu S, Wong HP. Synaptic electronics: Materials, devices and applications. Nanotechnology. 2013;24:382001. DOI: 10.1088/0957-4484/24/38/382001

[8] Yu S, editor. Neuro-Inspired Computing Using Resistive Synaptic Devices. Gewerbestrasse, Cham, Switzerland: Springer; 2017. DOI: 10.1007/978-3-319-54313-0

[9] Zidan MA, Strachan JP, Lu WD. The future of electronics based on memristive systems. Nature Electronics. 2018;**1**:22. DOI: 10.1038/ s41928-017-0006-8 [10] Jo SH, Chang T, Ebong I, Bhadviya BB, Mazumder P, Lu W. Nanoscale memristor device as synapse in neuromorphic systems. Nano Letters.

2010;**10**:1297-1301. DOI: 10.1021/ nl904092h

[11] Ohno T, Hasegawa T, Tsuruoka

T, Terabe K, Gimzewski JK, Aono

M. Short-term plasticity and longterm potentiation mimicked in single inorganic synapses. Nature Materials.

2011;10:591. DOI: 10.1038/nmat3054

[12] Wang Z, Joshi S, Savel'ev SE, Jiang H, Midya R, Lin P, et al. Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. Nature Materials. 2017;**16**:101. DOI: 10.1038/nmat4756

[13] Torrezan AC, Strachan JP,

Medeiros-Ribeiro G, Williams

RS. Sub-nanosecond switching

of a tantalum oxide memristor.

Nanotechnology. 2011;22:485203. DOI:

10.1088/0957-4484/22/48/485203

[14] Lee M-J, Lee CB, Lee D, Lee SR, Chang M, Hur JH, et al. A fast, highendurance and scalable non-volatile memory device made from asymmetric  $Ta_2O_{5-x}/TaO_{2-x}$  bilayer structures. Nature Materials. 2011;**10**:625. DOI: 10.1038/ nmat3070

[15] Zhou J, Cai F, Wang Q, Chen

B, Gaba S, Lu WD. Very lowprogramming-current RRAM with selfrectifying characteristics. IEEE Electron Device Letters. 2016;**37**:404-407. DOI: 10.1109/LED.2016.2530942

[16] Strukov DB, Snider GS, Stewart DR,Williams RS. The missing memristorfound. Nature. 2008;453:80. DOI:10.1038/nature06932

[17] Yang JJ, Strukov DB, Stewart DR. Memristive devices for computing.

Nature Nanotechnology. 2013;8:13. DOI: 10.1038/nnano.2012.240

[18] Von Neumann J. The principles of large-scale computing machines. IEEE Annals of the History of Computing.

1988;10:243-256. DOI: 10.1109/ MAHC.1981.10025

[19] LeCun Y, Bengio Y, Hinton G. Deep learning. Nature. 2015;**521**:436

[20] Krizhevsky A, Sutskever I, Hinton GE. Imagenet classification with deep convolutional neural networks. In: Advances in Neural Information Processing Systems. Pennsylvania Plaza, New York: ACM; 2012. pp. 1097-1105. DOI: 10.1145/3065386

[21] Russakovsky O, Deng J, Su H, Krause J, Satheesh S, Ma S, et al. Imagenet large scale visual recognition challenge. International Journal of Computer Vision. 2015;**115**:211-252. DOI: 10.1007/s11263-015-0816-y

[22] Collobert R, Weston J. A unified architecture for natural language processing: Deep neural networks with multitask learning. In: Proceedings of the 25th International Conference on Machine learning; 05-09 July 2008; Helsinki, Finland. New York, ACM; 2008. pp. 160-167

[23] Hinton G, Deng L, Yu D, Dahl GE, Mohamed AR, Jaitly N, et al. Deep neural networks for acoustic modeling in speech recognition: The shared views of four research groups. IEEE Signal Processing Magazine. 2012;**29**:82-97. DOI: 10.1109/MSP.2012.2205597

[24] Silver D, Huang A, Maddison CJ, Guez A, Sifre L, Van Den Driessche G, et al. Mastering the game of go with deep neural networks and tree search. Nature. 2016;**529**:484. DOI: 10.1038/nature16961

[25] Choi J-H, Sim S-E, Kim J-I, Choi DI, Oh J, Ye S, et al. Interregional synaptic maps among engram cells underlie memory formation. Science. 2018;**360**:430-435. DOI: 10.1126/ science.aas9204

[26] Whitlock JR, Heynen AJ, Shuler MG, Bear MF. Learning induces longterm potentiation in the hippocampus. Science. 2006;**313**:1093-1097. DOI: 10.1126/science.1128134

[27] Kim K-H, Hyun Jo S, Gaba S, Lu W. Nanoscale resistive memory with intrinsic diode characteristics and long endurance. Applied Physics Letters. 2010;**96**:053106. DOI: 10.1063/1.3294625

[28] Prakash A, Jana D, Maikap S. TaO<sub>x</sub>based resistive switching memories:

Prospective and challenges. Nanoscale

Research Letters. 2013;8:418. DOI:

10.1186/1556-276X-8-418

[29] Sun H, Liu Q, Li C, Long S, Lv H,

Bi C, et al. Direct observation of conversion between threshold switching and memory switching induced by conductive filament morphology.

Advanced Functional Materials.

2014;24:5679-5686. DOI: 10.1002/ adfm.201401304

[30] Liu Q, Long S, Lv H, Wang W, Niu J, Huo Z, et al. Controllable growth of nanoscale conductive filaments in solid-electrolyte-based ReRAM by using a metal nanocrystal covered bottom electrode. ACS Nano. 2010;4:6162-6168. DOI: 10.1021/nn1017582

[31] Yang Y, Gao P, Li L, Pan X, Tappertzhofen S, Choi S, et al. Electrochemical dynamics of nanoscale metallic inclusions in dielectrics. Nature Communications. 2014;**5**:4232. DOI: 10.1038/ncomms5232

[32] Wu S, Tsuruoka T, Terabe K, Hasegawa T, Hill JP, Ariga K, et al. A polymer-electrolyte-based atomic switch. Advanced Functional Materials. 2011;**21**:93-99. DOI: 10.1002/ adfm.201001520 Memristor Synapses for Neuromorphic Computing DOI: http://dx.doi.org/10.5772/intechopen.85301

[33] Yu S, Chen H-Y, Gao B, Kang J, Wong H-SP. HfO<sub>x</sub>-based vertical resistive switching random access memory suitable for bit-cost-effective three-dimensional cross-point architecture. ACS Nano. 2013;7: 2320-2325. DOI: 10.1021/nn305510u

[34] Long S, Perniola L, Cagli C, Buckley J, Lian X, Miranda E, et al. Voltage and power-controlled regimes in the progressive unipolar RESET transition of HfO<sub>2</sub>-based RRAM. Scientific Reports. 2013;**3**:2929. DOI: 10.1038/ srep02929

[35] Choi S, Jang S, Moon J-H, Kim JC, Jeong HY, Jang P, et al. A self-rectifying TaO<sub>y</sub>/nanoporous TaO<sub>x</sub> memristor synaptic array for learning and energyefficient neuromorphic systems. NPG Asia Materials. 2018;**10**:1097. DOI: 10.1038/s41427-018-0101-y

[36] Stevens JE, Lohn AJ, Decker SA, Doyle BL, Mickel PR, Marinella MJ. Reactive sputtering of substoichiometric  $Ta_2O_x$  for resistive memory applications. Journal of Vacuum Science & Technology, A: Vacuum, Surfaces, and Films. 2014;**32**:021501. DOI: 10.1116/1.4828701

[37] Chien W, Chen Y, Lai E, Yao Y, Lin P, Horng S, et al. Unipolar switching behaviors of RTO WO<sub>x</sub> RRAM. IEEE Electron Device Letters. 2010;**31**: 126-128. DOI: 10.1109/ LED.2009.2037593

[38] Kim S, Biju KP, Jo M, Jung S, Park J, Lee J, et al. Effect of scaling WO<sub>x</sub>-based RRAMs on their resistive switching characteristics. IEEE Electron Device Letters. 2011;**32**:671-673. DOI: 10.1109/ LED.2011.2114320

[39] Choi S, Shin JH, Lee J, Sheridan P, Wei DL. Experimental demonstration of feature extraction and dimensionality reduction using memristor networks. Nano Letters. 2017;**17**:3113-3118. DOI: 10.1021/acs.nanolett.7b00552 [40] Negrov D, Karandashev I, Shakirov V, Matveyev Y, Dunin-Barkowski W, Zenkevich A. An approximate backpropagation learning rule for memristor based neural networks using synaptic plasticity. Neurocomputing. 2017;**237**:193-199. DOI: 10.1016/j. neucom.2016.10.061

[41] Hasan R, Taha TM. Enabling back propagation training of memristor crossbar neuromorphic processors. In: International Joint Conference on Neural Networks (IJCNN); 6-11 July 2014; China. Bejing: IEEE; 2014. pp. 21-28. DOI: 10.1109/IJCNN.2014.6889893

[42] Khalid M, Singh J. Memristor crossbar-based pattern recognition circuit using perceptron learning rule. In: IEEE International Symposium on Nanoelectronic and Information Systems (iNIS); 19-21 December 2016; India. Gwalior: IEEE; 2016. pp. 236-239. DOI: 10.1109/iNIS.2016.061

[43] Alibart F, Zamanidoost E, Strukov DB. Pattern classification by memristive crossbar circuits using ex situ and in situ training. Nature Communications. 2013;4:2072. DOI: 10.1038/ncomms3072

[44] Choi S, Tan SH, Li Z, Kim Y, Choi C, Chen P-Y, et al. SiGe epitaxial memory for neuromorphic computing with reproducible high performance based on engineered dislocations. Nature Materials. 2018;17:335. DOI: 10.1038/s41563-017-0001-5

[45] Serb A, Bill J, Khiat A, Berdan R, Legenstein R, Prodromakis T. Unsupervised learning in probabilistic neural networks with multi-state metaloxide memristive synapses. Nature Communications. 2016;7:12611. DOI: 10.1038/ncomms12611

[46] Kim S, Choi B, Lim M, Yoon J, Lee J, Kim H-D, et al. Pattern recognition using carbon nanotube synaptic transistors with an adjustable weight update protocol. ACS Nano. 2017;**11**:2814-2822. DOI: 10.1021/ acsnano.6b07894

[47] Jeong Y, Lee J, Moon J, Shin JH, Lu WD. K-means data clustering with memristor networks. Nano Letters. 2018;**18**:4447-4453. DOI: 10.1021/acs. nanolett.8b01526

[48] Wang L, Wang Z, Zhao W, Hu B, Xie L, Yi M, et al. Controllable multiple depression in a graphene oxide artificial synapse. Advanced Electronic Materials. 2017;**3**:1600244. DOI: 10.1002/ aelm.201600244

[49] Yang CS, Shang DS, Liu N, Shi G, Shen X, Yu RC, et al. A synaptic transistor based on quasi-2D molybdenum oxide. Advanced Materials. 2017;**29**:1700906. DOI: 10.1002/adma.201700906

[50] Zhu LQ, Wan CJ, Guo LQ, Shi Y, Wan Q. Artificial synapse network on inorganic proton conductor for neuromorphic systems. Nature Communications. 2014;5:3158. DOI: 10.1038/ncomms4158

[51] Huh W, Jang S, Lee JY, Lee D, Lee D, Lee JM, et al. Synaptic barristor based on phase-engineered 2D heterostructures. Advanced Materials. 2018;**30**:1801447. DOI: 10.1002/adma.201801447

[52] Ham S, Choi S, Cho H, Na SI, Wang G. Photonic organolead halide Perovskite artificial synapse capable of accelerated learning at low power inspired by dopamine-facilitated synaptic activity. Advanced Functional Materials. 2019;**29**:1806646. DOI: 10.1002/adfm.201806646

[53] Payvand M, Rofeh J, Sodhi A, Theogarajan L. A CMOS-memristive self-learning neural network for pattern classification applications. In: Proceedings 2014 IEEE/ACM International Symposium on Nanoscale Architectures; 8-10 July 2014; France. Paris: ACM; 2014. pp. 92-97. DOI: 10.1109/NANOARCH.2014.6880486

[54] Ebong IE, Mazumder P. CMOS and memristor-based neural network design for position detection. Proceedings of the IEEE. 2012;**100**:2050-2060. DOI: 10.1109/JPROC.2011.2173089

[55] Prezioso M, Merrikh-Bayat F, Hoskins B, Adam G, Likharev KK, Strukov DB. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. Nature. 2015;**521**:61. DOI: 10.1038/ nature14441

[56] Hertz J, Krogh A, Palmer RG, editors. Introduction to the Theory of Neural Computation. Florida: CRC Press; 1991. DOI: 10.1119/1.17491

[57] Alibart F, Gao L, Hoskins BD, Strukov DB. High precision tuning of state for memristive devices by adaptable variation-tolerant algorithm. Nanotechnology. 2012;**23**:075201. DOI: 10.1088/0957-4484/23/7/075201

[58] Liu B, Li H, Chen Y, Li X, Huang T, Wu Q, et al. Reduction and IR-drop compensations techniques for reliable neuromorphic computing systems. In: Proceedings 2014 IEEE/ ACM International Conference on Computer-Aided Design. IEEE Press; 2014. pp. 63-70. DOI: 10.1109/ ICCAD.2014.7001330

[59] Mittal S. A Survey of ReRAM-based architectures for processing-in-memory and neural networks. Machine Learning and Knowledge Extraction. 2018;**1**: 75-114. DOI: 10.3390/make1010005

[60] Li Y, Wang Z, Midya R, Xia Q, Yang JJ. Review of memristor devices in neuromorphic computing: materials sciences and device challenges. Journal of Physics D: Applied Physics. 2018;**51**:503002. DOI: 10.1088/1361-6463/aade3f