We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

186,000

200M

Our authors are among the

TOP 1% most cited scientists

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

# Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

# Introductory Chapter: Need of SiC Devices in Power Electronics - A Beginning of New Era in Power Industry

# Yogesh K. Sharma

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/intechopen.79487

# 1. Introduction

## 1.1. Development in device technology

Germanium (Ge) was used as a material to manufacture the first semiconductor device. Ge was touted as the semiconductor material of the future. But after the arrival of silicon (Si), it turned out to be more suitable for several reasons [1–4]. The main reason is to get the high-purity Si from silica, which is widely available. Also, it is easy to modify Si into n-type, p-type, and semi-insulating materials [5]. In addition to this, Si can easily be converted into its native oxide, SiO<sub>2</sub>, with the help of thermal oxidation at the relatively low temperature of around 900°C [6–8]. These features make Si, as a material, semiconductor industry favorite. Global semiconductor industry, and currently, is worth more than \$430 billion [9]. Around 9–10% of this worth is in smart-integrated circuits and electronic power devices [10, 11]. These power devices processed more than 50% of our electricity [12, 13]. It has been reported that by 2025, Power Electronics market size will be worth \$39.22 billion [9]. As we can envision, power devices have a larger impact on the economy of any country. Power semiconductor devices are crucial to determine the cost and efficiency of electronic systems.

In power systems, diodes (uncontrolled switch) and transistors (controlled switch) play a major role. A small increase in their efficiency and power-handling capability make the systems more powerful and energy efficient. In the early 1950s, the advent of solid-state devices like bipolar transistors led to the phasing-out of vacuum tubes [13, 14]. These Si devices created the second wave of electronic revolution possible, with Si as the material of choice. Power devices had played a vital role in electronics industry. There is a rich history about the evolution of power devices. Initially, there were only bipolar devices with a blocking capability of 500 V (or so) and high-current capabilities. But after sometime, in the 1970s, International

# IntechOpen

© 2018 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Rectifier Inc. launched the first metal-oxide-field effect transistor (MOSFET) [15]. The idea was to switch to MOSFETs from BJTs in high-power applications. The MOSFET is a unipolar device, meaning there is only one type of carriers (electrons) which participate during conduction and thus has a high switching speed. Another advantage the MOSFET has is a voltage control device and hence it is easy to switch (on-state to off-sate). On the other hand, the BJT is a current control device and as a result not so easy to control. Voltage control instead of current control means that less internal energy loss occurs in a device. Also, with an increasing switching speed, other components of the system like filters (consist of capacitors/inductors) can be reduced in size. Si-MOSFETs could be designed to handle voltages up to 1000 V and in special case (super-junction) to 1200 V [13, 16, 17]. At voltages higher than 1000 V, the on-state losses of silicon MOSFET start increasing drastically and hence no longer able to perform efficiently. The performance predicament between bipolar and MOSFET devices was solved with the invention of an insulated gate bipolar transistor (IGBT). This is a new device structure where the best electrical features of bipolar (BJT) and unipolar (MOSFET) devices were combined together. With this new device structure, it is possible to cover the blocking voltage range from 750 to 6500 V. Like BJTSs, IGBTs are also able to carry high-forward current.

#### 1.2. Diode and transistor

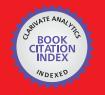

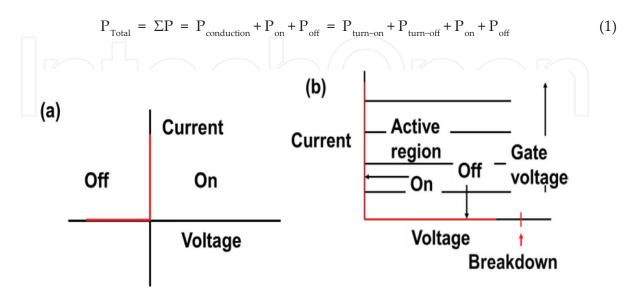

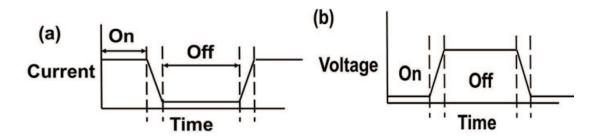

In power electronics to build electrical systems, we need both a rectifier and a transistor. The features of an ideal rectifier and a transistor are shown in **Figure 1**. For an ideal rectifier, there is no voltage drop in on-state and no current flows in off-state. Hence, there is no power loss during the operation of a rectifier, **Figure 1(a)**. Similarly, in the case of an ideal transistor, there is no power dissipation during commutation from on- to off–states, **Figure 1(b)**. The waveforms of an ideal power switching system are shown in **Figure 2**. But in reality, this is not the case, either with devices or power systems. The characteristics of a real (non-ideal) rectifier/transistor are shown in **Figure 3**, and the corresponding waveforms of a power system are shown in **Figure 4**. The total power loss occurred in a switch (P<sub>Total</sub>) and is given by:

Figure 1. Ideal current-voltage characteristics of a diode (a) and a transistor (b).

Introductory Chapter: Need of SiC Devices in Power Electronics - A Beginning of New Era... 3 http://dx.doi.org/10.5772/intechopen.79487

Figure 3. Real (nonideal) current-voltage characteristics of a diode (a) and a transistor (b).

Figure 4. Switching waveforms in a real (nonideal) power system, (a) Current versus Time and (b) Volatge versus Time.

At high frequencies, the switching power loss dominates, so fast switching power devices are desirable. At low frequencies, on-state power loss dictates, so power devices with a low on-state resistance are vital.

#### 1.3. Conduction mechanism of a power device

As mentioned previously with the help of an IGBT, it is possible to increase the operating voltage range of a power transistor without compromising its on-state losses. In unipolar devices like Schottky diode (SBD), MOSFET, the blocking capability of the device increases with an increasing drift region thickness. With an increasing thickness, the conduction losses of a device also increase. In a bipolar device, because of conduction modulation (injection of minority carriers (holes mainly) into the n-type drift region), this is not true, and the conduction losses are low despite a thick drift layer. For example, the specific on-resistance ( $R_{pin}$ ) of a drift layer (blocking layer) for a unipolar device, n-type Schottky diode', is given by [18].

$$R_{\rm pin} = T_{\rm driff} / q N_{\rm drift} \left( \mu_{\rm n+} \, \mu_{\rm p} \right) \tag{2}$$

where  $T_{drift}$  = thickness of the drift layer;  $N_{drit}$  = doping concentration of the n drift layer;  $\mu_n/\mu_p$  = bulk mobility of electrons/holes in semiconductor.

For an n-type pin diode, the specific on-resistance (R<sub>pin</sub>) under high-current density condition is given by

$$R_{pin} = T_{drift} / q\mu_n N_{drift} + q(\mu_{n+} \mu_p) \Delta p$$

(3)

Because of the extra term, q ( $\mu_{n+} \mu_p$ )  $\Delta p$ , in the pin diode, the specific resistance will be lower as compared to Si Schottky diode. In the case of high injection  $\Delta p >> N_{drift'}$  the resistance will decrease considerably during conduction. Now, in order to get the diode into the blocking mode, minority carriers (corresponding to  $\Delta p$ ) have to be removed from the drift region. These minority carriers in the drift region cause stored charge in the device and hence increase the switching losses. As a result, the operating switching frequency limit for bipolar devices (PIN or BJT) is lower, as compared to unipolar device (SBD or MOSFET). With the help of a wideband semiconductor material like SiC, there is no need to switch to Si IGBT, as we can realize a high-blocking capability (>1200 V) SiC MOSFET without increasing the on-state losses. The specific on-résistance ( $R_{or}$ ) of a MOSFET is given by [19, 20].

$$R_{on} = 4 V_{blocking}^2 / \mu_n \varepsilon_s E_{critical}^3$$

(4)

where  $\mu_n$  = bulk mobility of SiC;  $\varepsilon_s$  = permittivity of SiC;  $E_c$  = critical electric field of breakdown for SiC;  $V_{blocking}$  = the desired blocking voltage.

Bulk electron motilities are similar for low-doped Si and SiC (900–1200 cm<sup>2</sup>/Vs) [24]. However,  $E_{critical}^{sic} = 7 E_{critical}^{si}$ , so that for a given blocking voltage, the specific on-resistance can be a factor of 343 times lower for SiC devices. This is the reason why we need a wide-band gap semiconductor material for power device.

# 2. Application of SiC devices in hybrid module technology

There are a plethora of applications where these devices had been used and have shown their positive impact, and many more potential applications are on the horizon [21–23]. Although there are different kinds of SiC devices available, the most interesting ones are Schottky diodes and MOSFETs. These devices can be used to build either full SiC modules or hybrid SiC modules. In a hybrid SiC module, conventional Si diodes are replaced by Schottky diodes while the transistors are still Si IGBTs. With hybrid approach, we can maintain the cost of an electronic system down but the power saving would not be as much as it can be by using full SiC modules. The fabrication of SiC devices is more complicated and costly as compared with Si counterparts. The situation is more compounded for SiC MOSFETs. SiC MOSFETs are not only more expensive than SiC Schottky diodes but also there are only few suppliers who can provide these devices with limited current ratings. As a result, it makes more sense to build

Introductory Chapter: Need of SiC Devices in Power Electronics - A Beginning of New Era... 5 http://dx.doi.org/10.5772/intechopen.79487

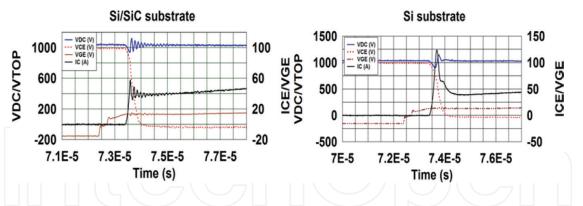

**Figure 5.** Output waveforms obtained for hybrid 1.7 kV SiC (a) and Si substrates (b) obtained during the first turn-on of the IGBT. These devices were tested at 150°C.

hybrid systems. Also at present, hybrid approach strikes a good balance between cost and efficiency achieved by these modules [24–27]. Also, it is worthwhile to point out that although SiC diodes and MOSFETs are available at 1.7 kV and lower voltages, there is no MOSFET supplier at 3.3 kV. Also, SiC diode technology is more matured and has been around for some time as compared to SiC MOSFETs. SiC diodes were made available commercially in early 2000s, while the first SiC MSOFET came to the market in 2011 (by CREE).

#### 2.1. 1700 V Si/SiC hybrid technology

The results of a double-pulse test done on a hybrid substrate, built using 1 GBT and 1 diode (Si or SiC), are shown in **Figure 5**. These substrates are manufactured to conduct only 50A. By executing this test, we can evaluate the transient behavior of both IGBT and diode. In our case, we are interested in SiC Schottky diode's transient behavior and power losses suffered by it. The external gate resistors,  $R_{gon} = R_{goff} = 6 \Omega$ , and the value of inductance (L) used is 260 µH. The waveforms during the second turn-on of the IGBT are recorded and are shown in **Figure 5**. The input voltage used for the test is around 1050 V. **Figure 5** shows that the peak reverses recovery current overshoot ( $I_{rr}$ ) increases significantly to 87A, if Si diode is used instead of an SiC diode. The values of  $I_{rr}$  for Si and hybrid SiC substrates are listed in **Table 1**. Although the value of  $I_{rr}$  is lower for hybrid substrate, some oscillations in the current waveform are observed. The reverse recovery charge,  $Q_{rr'}$  is minute (3µC) in the case of SiC diode. This low  $Q_{rr}$  can be transformed into a low-energy loss during a switching event. Also, for hybrid SiC substrate, the reverse recovery energy ( $E_{rec'}$ ) is 1 mJ. The corresponding value for Si substrate is 11 mJ. All these tests are done at 150°C. The test setup used to perform a double-pulse test is shown in **Figure 6**.

#### 2.2. 3300 V Si/SiC technology

In order to build 3.3 kV hybrid SiC substrates, two 1.7 kV, 50 A diodes are packaged in series. Again, the idea of using these diodes is to reduce the overall losses as compared with Si modules. These 3.3 kV modules can be used in wind power, solar energy, and rail-car applications. Like 1.7 kV hybrid modules, new system topologies can be realized with the help of these modules. Because of the limited availability of 3.3 kV SiC diodes, 1.7 kV SiC diodes are used to realize this high-voltage hybrid technology. All the diodes used to build these substrates are chosen carefully (e.g., the devices with similar  $V_F$ ) so that there is no problem during current sharing in SiC diodes. This is very crucial for the reliability of these substrates.

| At 150 °C, 1.7kV            | Full Si | Hybid Si/SiC |

|-----------------------------|---------|--------------|

| V <sub>line</sub> (V)       | 1049    | 1056         |

| dV <sub>ce</sub> /dt (V/µs) | 1372    | 1319         |

| I <sub>rr</sub> (A)         | 87      | 21           |

| Q <sub>rr</sub> (µC)        | 22      | 3            |

| E <sub>rec</sub> (J)        | 0.011   | 0.001        |

**Table 1.** Comparison of various parameters extracted for Si and hybrid 1.7 kVSiC substrates at 150°C from a double-pulse test.

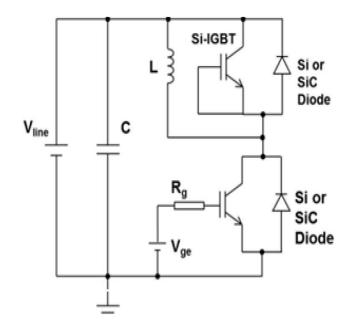

Figure 6. The schematic of a double-pulse test bench used to test devices.

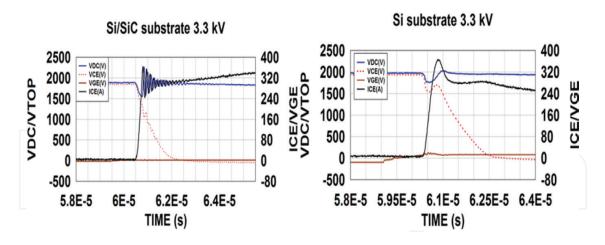

during the second turn-on of the IGBT at 150°C are recorded and are shown in **Figure 7**. For a di/dt = 1100 or 1388 A/µs, a reverse recovery current overshoot ( $I_{rr}$ ) of 128 A is observed for an Si substrate, which is higher than that of a hybrid SiC substrate (65A). The reverse recovery energy loss occurred in a substrate during the transient is  $E_{rec}$ , and the values for  $E_{rec}$  (SiC) are 0.199 and 0.01 J, respectively. This represents a reduction of about 95% for hybrid substrate. Other transient parameters for the substrates, namely  $Q_{rr}$ ,  $E_{on}$ , and  $E_{off}$  (J), are also listed in **Table 2**. **Figure 8** shows the picture of a 3.3 kV, 200A hybrid SiC substrate. Again, like 1.7 kV hybrid substrates, 3.3 kV hybrid substrates are prone to electromagnetic interference (EMI), caused by the oscillations observed in the output waveforms.

#### 3. Processing challenges of SiC devices

The fabrication of SiC devices is more demanding and complicated as compared with Si devices. Intrinsic properties of SiC make the devices suitable for high operating temperatures

Introductory Chapter: Need of SiC Devices in Power Electronics - A Beginning of New Era... 7 http://dx.doi.org/10.5772/intechopen.79487

**Figure 7.** Output waveforms obtained for hybrid 3.3 kV SiC (a) and Si substrates (b) obtained during the first turn-on of the IGBT. These devices were tested at 150°C.

| At 150 °C, 3.3kV            | Full Si | Hybid Si/SiC |  |

|-----------------------------|---------|--------------|--|

| V <sub>line</sub> (V)       | 1800    | 1800         |  |

| dl <sub>ce</sub> /dt (A/µs) | 1100    | 1388         |  |

| I <sub>rr</sub> (A)         | 128     | 65           |  |

| Q <sub>rr</sub> (µC)        | 167     | 13           |  |

| E <sub>rec</sub> (J)        | 0.199   | 0.01         |  |

**Table 2.** Comparison of various parameters extracted for Si and hybrid 3.3 kVSiC substrates at 150°C from a double-pulse test.

(>200°C). But at the same time, due to its intrinsic properties, it is difficult to perform any electrical and physical change to the material at temperatures lower than 1000°C. That means in order to fabricate an SiC device, different set of tools are required as compared to Si device world [28–31]. The electrical and physical properties of Si and SiC are listed in **Table 3**.

## 3.1. Oxidation of SiC

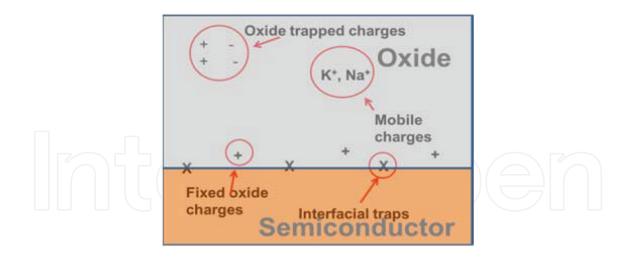

In an oxide/semiconductor system, there are different types of charges which are present in the system. These charges are not desirable and greatly influence the electrical properties of a device. For example, the threshold voltage of a MOSFET and the breakdown voltage of a power, device, could change significantly because of these charges. These charges are divided into four types—mobile oxide charge, fixed oxide charge, oxide trapped charge, and interface trapped charge—and are shown in **Figure 9** [32].

At present, interface trapped charge is a key hurdle for the silicon carbide MOS R&D community. The origin of these charges is not well understood but may be related to mainly siliconand carbon-dangling bonds, carbon clusters, carbon dimers in the SiC, and oxygen vacancies in the oxide very near to the interface [33–36]. Interfacial traps create localized energy levels in the energy band gap of SiC. These interface traps form potential wells that capture electrons

Figure 8. A picture of a 200 a, 3.3 kV hybrid SiC substrate.

| Semiconductor                                                            | Si      | 3C-SiC | 6H-SiC                                                 | 4H-SiC                                                    |

|--------------------------------------------------------------------------|---------|--------|--------------------------------------------------------|-----------------------------------------------------------|

| Bandgap (eV)                                                             | 1.12    | 2.4    | 3.03                                                   | 3.26                                                      |

| Breakdown Field<br>(MV/cm)                                               | 0.25    | >1.5   | 2.4 parallel to c-axis<br>> 1, perpendicular to c-axis | 2.2 parallel to c-axis                                    |

| Intrinsic Carrier<br>Conc.(cm <sup>-3</sup> )                            | 1.45e10 | 1.5e-1 | 1.6e-6                                                 | 5e-9                                                      |

| Electron Mobility<br>@ n <sub>d</sub> =10 <sup>16</sup> cm <sup>-3</sup> | 1430    | 800    | 60 parallel to c-axis<br>400 perpendicular to c-axis   | 900 parallel to c-axis<br>800 perpendicular to c-<br>axis |

| Hole Mobility , @ n <sub>a</sub><br>=10 <sup>16</sup> cm <sup>-3</sup>   | 480     | 40     | 90                                                     | 115                                                       |

| Saturated Electron Vel<br>(10 <sup>7</sup> cm/s)                         | 1       | 2.5    | 2                                                      | 2                                                         |

| Thermal Conductivity<br>(W/cm-K)                                         | 1.5     | 3.2    | 3.0-3.8                                                | 3.0-3.8                                                   |

Table 3. Electrical and physical properties of Si, 3C-SiC, 6H-SiC and 4H-SiC.

and holes. In addition, charge traps also act as Columbic scattering centers [37]. These two effects decrease the effective channel mobility in a MOSFET. In Si world, a typical oxidation temperature employed to grow an oxide layer is 1050 (dry oxidation) or 850°C (wet oxidation). The oxidation step is followed by an annealing step in  $H_2$  gas ambient at 800°C for 30 min. In 4H-SiC, typical oxidation temperature to grow a layer of native oxide is 1150°C. In some cases, it could be as high as 1300 or 1500°C which requires special oxidation furnaces, not the conventional quartz furnaces used for Si oxidation [38–41]. To use SiC devices to their full potential, we must continue to work to improve the electrical characteristics of the oxide/SiC

Introductory Chapter: Need of SiC Devices in Power Electronics - A Beginning of New Era... 9 http://dx.doi.org/10.5772/intechopen.79487

Figure 9. Different types of charges in oxide/semiconductor system [10].

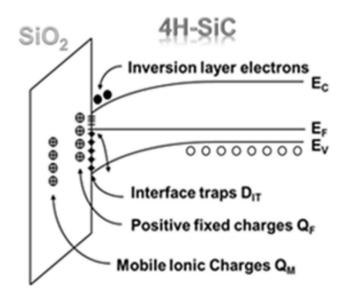

Figure 10. Energy band diagram of an SiC MOS system in inversion and location (qualitative) of different types of charges.

interface by developing more effective processes to passivate defects at the interface formed during the oxidation process. These defects give rise to interface trap density,  $D_{IT}$  (cm<sup>-2</sup> eV<sup>-1</sup>) and is shown in **Figure 10**. Depending upon the surface potential, these traps can be charged positively or negatively charged.

As mentioned previously, these traps decrease the effective channel mobility of electrons significantly. At present, there is a standard passivation process based on post-oxidation annealing in nitric/nitrous oxide (NO/N<sub>2</sub>O) for 2 h at 1175°C. [42, 43]. This post-oxidation annealing (passivations) increases the inversion electron channel mobility of an SiC-MOSFET from single digits, ~ 8 cm<sup>2</sup>V<sup>-1</sup>·s<sup>-1</sup>, to around 30 cm<sup>2</sup>/V·s. Although these processes have made the commercialization of SiC MOSFETs possible, there is still room for significant improvement. This inversion channel mobility value is only around 4% of bulk mobility value of SiC. In case of Si, the inversion channel mobility can be as much as 50% of bulk mobility [29]. In addition to standard  $N_2O$  annealing, there are different types of annealing which can increase the channel mobility significantly, but these annealings degrade some important parameters of a MOSFET and hence cannot be used [44–50]. More work is still needed in this field to improve the performance of SiC MOSFETs.

#### 3.2. Ohmic contacts

In SiC, there is no or very little diffusion as a result, it is not possible to use temperature annealing process to drive in the dopants into the material. To get a desired doping profile in SiC, dopants are implanted using a high-energy implanter (typically 50-500 keV), and sometimes, wafers are needed to be at high temperature (~500°C) during this step. Implantation of dopants is followed by a dopant activation step, which requires a very high temperature. Typically, n-dopants get electrically activated at 1550°C, while p-dopants require a temperature of as high as 1700°C, which is very challenging to achieve. With n-dopants, the electrical activation rate of more than 90% can be attained, but in p-dopants, it is tough to realize an activation rate of more than 50%. The reason why lower activation temperature is required for n-dopants as compared to p-dopants is because of the difference in the location of respective dopant energy levels in SiC. For n dopants (N), the donor energy level is located at 0.3 eV (shallow) below the conduction band edge and hence not much energy is required to electrically activate these donors. In the case of p dopants (Al), the position of the acceptor level is 0.7 eV (deep) above the valance band edge. Hence, more energy is needed to electrically activate them. Even at present, various research groups are working on p-type ohmic contacts [51–56]. Also, high temperature and special metallization processes are necessary to form ohmic and Schottky contacts on SiC.

## 4. EMI problems

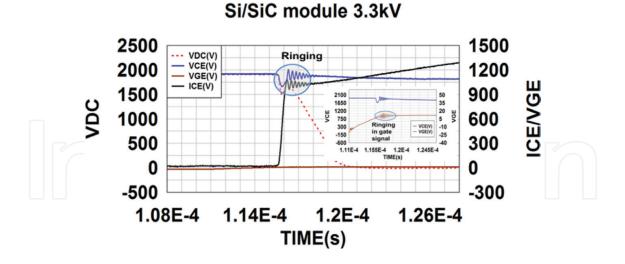

Due to fast switching speed of SiC devices (Schottky diodes, MOSFETs), some undesirable effects are observed during the switching (from on-state to off-state and vice versa) of these devices. The oscillations observed in the output current waveform, Figure 11, are the result of the fast switching behavior of 1.7 kV, 50 A SiC diodes, which are used to build 3.3 kV, 1200 A hybrid SiC modules. From the application point of view, this is problematic and can lead to EMI with neighboring electrical systems. Sometimes, it can also lead to a premature breakdown of the module during operation. In full SiC module, it is common measure to slow the switching speed of the devices (by increasing the gate resistance) to reduce/eliminate the oscillations. From Figure 11, we can clearly see that the oscillations are present, both in current and in voltage waveforms. Also, these oscillations are present in the gate signal, which is used to control Si IGBT (clear from the inset in Figure 11) in the module. Because of these oscillations, the gate signal voltage in some cases may shoot up/down to +40 to -40 V, much higher than the recommended voltage range (-15 to +15 V) of the gate signal. We can imagine how detrimental this would be for Si IGBTs. If new design ideas are used for the substrate layout of these modules, then the parasitic elements (stray inductance and capacitance) could be minimized, and, hence, there will be no necessity of compromising on the switching speed of SiC devices.

**Figure 11.** The ringing/oscillations observed in the output waveforms of a 3.3 kV, 1200A SiC hybrid module due to an underdamped response to an RLC circuit formed among the diode depletion capacitance, parasitic inductance, and SiC diode during the second turn-on event.

# 5. Conclusions

SiC device technology has a promising future. Different types of more efficient power systems have already been built using SiC devices and demonstrated in real applications around the world. This technology materializes the possibility of new topologies for inverter and converter, which were not possible in the past. Various fields including automotive, traction-train, renewable energy, geothermal energy, and so on have already been benefitted from SiC technology. Despite all these advantages, this technology is relatively new and hence poses some challenges. New control strategies, and more suitable module designs and packaging options are needed to be developed for the optimal use of these devices. The cost of SiC device is still a bit high, although, in the past couple of years, it has come down significantly. Even with all these challenges, new technology like SiC is indispensable to achieve the goal of a greener planet.

## Acknowledgements

The author would like to thank his collogues at Dynex Semiconductors for their help and support provided, during this project. Also, I would like to specially thank my old colleagues and partners at the University of Warwick (UK) and Auburn University (USA).

## Author details

Yogesh K. Sharma

Address all correspondence to: aceyogesh83@gmail.com

R&D Centre: Semiconductors, Dynex Semiconductor Ltd., Lincoln, UK

# References

- [1] Pfann WG, Scaff JH. The p-germanium transistor. Proceedings of the IRE. 1950;**38**(10): 1151-1154

- [2] Valdes LB. Effect of electrode spacing on the equivalent base resistance of point-contact transistors. Proceedings of the IRE. 1952;40(11):1429-1434

- [3] Ball JA. The Harvard minicorrelator. IEEE Transactions on Instrumentation and Measurement. 1973;**22**(2):193-196

- [4] Lécuyer C. Making Silicon Valley: Innovation and the Growth of High Tech. Cambridge, Massachusetts, USA; MIT Press; 2006. pp. 1930-1970

- [5] O'Mara W, Herring RB, Hunt LP. Handbook of Semiconductor Silicon Technology. Park Ridge, NJ, USA: Noyes Publications; 1990

- [6] Deal BE, Grove AS. General relationship for the thermal oxidation of silicon. Journal of Applied Physics. 1965;**36**(12):3770-3778

- [7] Mott NF, Rigo S, Rochet F, Stoneham AM. Oxidation of silicon. Philosophical Magazine Part B. 1989;60(2):189-212

- [8] Kao DB, Mcvittie JP, Nix WD, Saraswat KC. Two-dimensional thermal oxidation of silicon. II. Modeling stress effects in wet oxides. IEEE Transactions on Electron Devices. 1988;35(1):25-37

- [9] https://www.prnewswire.com/news-releases/global-semiconductor-market-forecast-2017-2024-300541299.html

- [10] http://www.icinsights.com

- [11] http://www.electroiq.com/articles/sst/print/volume-54/issue-7.html

- [12] http://www.power-mag.com/news.detail.php?NID=38

- [13] Baliga BJ. Fundamentals of Power Semiconductor Devices. USA: Springer Science & Business Media; 2010

- [14] Warner RM. Microelectronics: Its unusual origin and personality. IEEE Transactions on Electron Devices. 2001;48(11):2457-2467

- [15] http://www.irf.com/60anniversary/index.html#1970s

- [16] Lin Z, Hu S, Yuan Q, Zhou X, Tang F. Low-reverse recovery charge superjunction MOSFET with a p-type Schottky body diode. IEEE Electron Device Letters. 2017;38(8):1059-1062

- [17] Udrea F, Deboy G, Fujihira T. Superjunction power devices, history, development, and future prospects. IEEE Transactions on Electron Devices. 2017;64(3):720-734

- [18] Morisette DT, Cooper JA. Theoretical comparison of SiC PiN and Schottky diodes based on power dissipation considerations. IEEE Transactions on Electron Devices. 2002;49(9):1657-1664

- [19] Baliga BJ. Trends in power semiconductor devices. IEEE Transactions on Electron Devices. 1996;43(10):1717-1731

- [20] Sharma Y. Advanced SiO<sub>2</sub>/SiC interface passivation [doctoral dissertation]; 2012

- [21] She X, Huang AQ, Lucía Ó, Ozpineci B. Review of silicon carbide power devices and their applications. IEEE Transactions on Industrial Electronics. 2017;**64**(10):8193-8205

- [22] Piasecki S, Kazmierkowski MP. Applications of SiC MOSFETs in AC–DC converters dedicated for distributed generation systems. In: Analysis and Simulation of Electrical and Computer Systems. Cham: Springer; 2018. pp. 1-14

- [23] Morya A, Moosavi M, Gardner MC, Toliyat HA. Applications of wide bandgap (WBG) devices in AC electric drives: A technology status review. In: 2017 IEEE International Electric Machines and Drives Conference (IEMDC); IEEE. 2017. pp. 1-8

- [24] Ishikawa K, Ogawa K, Yukutake S, Kameshiro N, Kono Y. Traction inverter that applies compact 3.3 kV/1200 A SiC hybrid module. In: 2014 International Power Electronics Conference (IPEC-Hiroshima 2014-ECCE-ASIA); IEEE. 2014. pp. 2140-2144

- [25] Yuan L, Li J, Gu Q, Zhao Z, Shen Y. Power losses of Si/SiC semiconductors in medium voltage energy router sub-modules with hybrid topology. In: 2017 20th International Conference on Electrical Machines and Systems (ICEMS); IEEE. 2017. pp. 1-6

- [26] Kranz L, Minamisawa RA, Knoll L, Matthias S, Mihaila A, Papadopoulos C, et al. Robust SiC JBS diodes for the application in hybrid modules. In: Proceedings of PCIM Europe 2017; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management; VDE. 2017. pp. 1-6

- [27] Sharma YK, Jiang H, Zheng C, Dai X, Wang Y, Deviny I. Impact of design and process variation on the fabrication of SiC diodes. Journal of Semiconductors. Manuscript ID 18020011.R1 (in press)

- [28] Grossner U, Alfieri G, Nipoti R. SiC device manufacturing: How processing impacts the material and device properties. In: Materials Science Forum. Vol. 821. Switzerland: Trans Tech Publications Ltd.; 2015. p. 381

- [29] Kimoto T. Material science and device physics in SiC technology for high-voltage power devices. Japanese Journal of Applied Physics. 2015;54(4):040103

- [30] Bonyadi Y, Gammon PM, Sharma YK, Baker G, Mawby PA. An investigation into the impact of surface passivation techniques using metal-semiconductor interfaces. In: Materials Science Forum. Vol. 897. Switzerland: Trans Tech Publications Ltd.; 2017. pp. 443-446

- [31] Liu G, Tuttle BR, Dhar S. Silicon carbide: A unique platform for metal-oxide-semiconductor physics. Applied Physics Reviews. 2015;2(2):021307

- [32] Sze SM, Ng KK. Physics of Semiconductor Devices. Hoboken, New Jersey, USA: John Wiley & Sons Inc.; 2006

- [33] Afanas'ev VV, Ciobanu F, Dimitrijev S, Pensl G, Stesmans A. Band alignment and defect states at SiC/oxide interfaces. Journal of Physics: Condensed Matter. 2004;**16**(17):S1839

- [34] Tuttle BR. Dangling bond defects in SiC: An ab initio study. Physical Review B. 2018;97(4):045203

- [35] Jayawardhena IU, Jayawardena A, Isaacs-Smith T, Dhar S. Effect of wafer orientation on near-interface oxide traps in 4H-SiC metal-oxide-semiconductor capacitors. In: Meeting Abstracts, No. 23; The Electrochemical Society. 2018. pp. 1441-1441

- [36] Jiao C, Ahyi AC, Dhar S, Morisette D, Myers-Ward R. Interface trap profiles in 4H-and 6H-SiC MOS capacitors with nitrogen-and phosphorus-doped gate oxides. Journal of Electronic Materials. 2017;46(4):2296-2300

- [37] Pérez-Tomás A, Brosselard P, Godignon P, Millán J, Mestres N, Jennings MR, et al. Fieldeffect mobility temperature modeling of 4H-Si C metal-oxide-semiconductor transistors. Journal of Applied Physics. 2006;100(11):114508

- [38] Ramamurthy RP, Morisette DT, Amarasinghe V, Feldman LC. Thermal-oxidation-free dielectrics for SiC power devices. In: 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA); IEEE. 2017. pp. 242-245

- [39] Thomas SM, Jennings MR, Sharma YK, Fisher CA, Mawby PA. Impact of the oxidation temperature on the interface trap density in 4H-SiC MOS capacitors. In: Materials Science Forum. Vol. 778. Switzerland: Trans Tech Publications Ltd.; 2014. pp. 599-602

- [40] Thomas SM, Sharma YK, Crouch MA, Fisher CA, Perez-Tomas A, Jennings MR, Mawby PA. Enhanced field effect mobility on 4H-SiC by oxidation at 1500 C. IEEE Journal of the Electron Devices Society. 2014;2(5):114-117

- [41] Jia Y, Lv H, Song Q, Tang X, Xiao L, Wang L, et al. Influence of oxidation temperature on the interfacial properties of n-type 4H-SiC MOS capacitors. Applied Surface Science. 2017;397:175-182

- [42] Chung GY, Tin CC, Williams JR, McDonald K, Chanana RK, Weller RA, et al. Improved inversion channel mobility for 4H-SiC MOSFETs following high temperature anneals in nitric oxide. IEEE Electron Device Letters. 2001;22(4):176-178

- [43] Li HF, Dimitrijev S, Harrison HB, Sweatman D. Interfacial characteristics of N<sub>2</sub>O and NO nitrided SiO<sub>2</sub> grown on SiC by rapid thermal processing. Applied Physics Letters. 1997;70(15):2028-2030

- [44] Modic A, Sharma YK, Xu Y, Liu G, Ahyi AC, Williams JR, et al. Nitrogen plasma processing of SiO<sub>2</sub>/4H-SiC interfaces. Journal of Electronic Materials. 2014;43(4):857-862

- [45] Okamoto D, Sometani M, Harada S, Kosugi R, Yonezawa Y, Yano H. Effect of boron incorporation on slow interface traps in SiO<sub>2</sub>/4H-SiC structures. Applied Physics A. 2017;**123**(2):133

- [46] Liu G, Ahyi AC, Xu Y, Isaacs-Smith T, Sharma YK, Williams JR, et al. Enhanced inversion mobility on 4H-SiC (1120) using phosphorus and nitrogen interface passivation. IEEE Electron Device Letters. 2013;34(2):181-183

- [47] Sharma YK, Ahyi AC, Issacs-Smith T, Shen X, Pantelides ST, Zhu X, et al. Phosphorous passivation of the SiO<sub>2</sub>/4H–SiC interface. Solid-State Electronics. 2012;68:103-107

- [48] Sharma YK, Ahyi AC, Isaacs-Smith T, Modic A, Park M, Xu Y, et al. High-mobility stable 4H-SiC MOSFETs using a thin PSG interfacial passivation layer. IEEE Electron Device Letters. 2013;34(2):175-177

- [49] Zheng Y, Isaacs-Smith T, Ahyi AC, Dhar S. 4H-SiC MOSFETs with borosilicate glass gate dielectric and antimony counter-doping. IEEE Electron Device Letters. 2017;38(10): 1433-1436

- [50] Cabello M, Soler V, Rius G, Montserrat J, Rebollo J, Godignon P. Advanced processing for mobility improvement in 4H-SiC MOSFETs: A review. Materials Science in Semiconductor Processing. 2018;78:22-31

- [51] Vivona M, Greco G, Bongiorno C, Nigro RL, Scalese S, Roccaforte F. Electrical and structural properties of surfaces and interfaces in Ti/Al/Ni Ohmic contacts to p-type implanted 4H-SiC. Applied Surface Science. 2017;420:331-335

- [52] Fedeli P, Puzzanghera M, Moscatelli F, Minamisawa RA, Alfieri G, Grossner U, Nipoti R. Ni-Al-Ti Ohmic contacts on Al implanted 4H-SiC. In: Materials Science Forum. Vol. 897. Switzerland: Trans Tech Publications Ltd.; 2017. pp. 391-394

- [53] Zhang Y, Guo T, Tang X, Yang J, He Y, Zhang Y. Thermal stability study of n-type and p-type ohmic contacts simultaneously formed on 4H-SiC. Journal of Alloys and Compounds. 2018;731:1267-1274

- [54] Gammon PM, Pérez-Tomás A, Shah VA, Vavasour O, Donchev E, Pang JS, et al. Modelling the inhomogeneous SiC Schottky interface. Journal of Applied Physics. 2013;114(22):223704

- [55] Jennings MR, Fisher CA, Walker D, Sanchez A, Pérez-Tomás A, Hamilton DP, et al. On the Ti<sub>3</sub>SiC<sub>2</sub> metallic phase formation for robust p-type 4H-SiC ohmic contacts. In: Materials Science Forum. Vol. 778. Switzerland: Trans Tech Publications Ltd.; 2014. pp. 693-696

- [56] Baliga BJ, Sung WJ, Han KJ, Harmon J, Tucker A, Syed S. PRESiCETM: Process engineered for manufacturing SiC electronic devices. In: Materials Science Forum. Vol. 924. Switzerland: Trans Tech Publications Ltd.; 2018. pp. 523-526

IntechOpen