We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

186,000

200M

Our authors are among the

TOP 1% most cited scientists

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

# Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

## **Abrasive for Chemical Mechanical Polishing**

## Hong Jin Kim

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/intechopen.75408

#### Abstract

Chemical mechanical polishing (CMP) is one of the most essential processes in semiconductor manufacturing. Its importance becomes highly underscored at the advanced device toward sub 14 nm scaling. The fundamental mechanism of CMP is to create soften surface layer by chemical reaction and then, mechanical force by abrasive particles remove soften layer. The role of CMP is not only material removal, but also planarization, surface smoothening, uniformity control, defect reduction and more. Moreover, semiconductor yield enhancement is sensitively influenced by CMP processing. Surface scratching, which is generated by CMP in nature, is considered as 'killer defect' in semiconductor manufacturing. Hence, to achieve proper CMP performance without surface scratching, understanding and development of abrasive particles are crucially important. In this chapter, CMP fundamentals, applications and challenges associated with abrasive particle technology including synthesis (up to nanoparticle scale), tribochemical reaction, abrasive surface zeta potential behavior, particle size and its distribution will be discussed.

**Keywords:** semiconductor manufacturing, chemical mechanical polishing (CMP), slurry, silica abrasive, ceria abrasive, alumina abrasive, advanced abrasive materials

## 1. Introduction

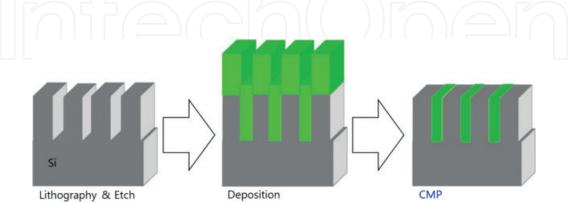

Chemical mechanical polishing (CMP) has been used for several decades in semiconductor manufacturing since its development at 1980s [1–5]. The original purpose of CMP is to planarize wafer surface both locally and globally, which enable subsequent lithographic patterning with proper depth of focus [1–5]. However, as device shrinkage continues, it has become critical process for device fabrication, and its applications play a pivotal role in semiconductor process since transistor scaling becomes beyond 14 nm [5–9]. The role of CMP and planarized wafer associated with lithography patterning is shown in **Figure 1** schematically [1, 4].

## IntechOpen

© 2018 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Surface topography hinders conformal deposition of photoresist, leading to distorted patterning. Furthermore, advantages of employment of CMP in semiconductor manufacturing are [4, 5]: (1) elimination of step coverage burden, (2) defect removal from prior process steps, (3) surface smoothening in wafer scale, and (4) enablement of metal gate formation at sub 14 nm device. The fundamental mechanism of CMP process is [1–4]: (1) Material surface becomes soften by chemical reaction with slurry, (2) Mechanical force by abrasive particle in the slurry removes soften layer and step height reduction, (3) Material surface reacts with slurry chemical to make surface soften layer again and repeat (1) – (3). Therefore, chemistry and abrasive particles in the slurry determines CMP performances. This procedure is given in **Figure 2**. With this process, fast material removal across the wafer with planarization can be achieved. From the abrasive perspective, abrasive-wafer contact model on removal rate has been published in many literatures which emphasize abrasive particle size (and size distribution) and shape, and abrasive hardness. Although CMP application had started from planarization of excessed dielectric materials, its utilization have been widely accepted in shallow trench isolation, contact and metal interconnection formation [1–10]. Recently, sub 14 nm semiconductor scaling has developed device integration scheme to 3-dimensional transistor formation such as fin field-effect transistor, therefore device process flow becomes much more complicated than previous device node [6–9, 11, 12]. Hence, application of CMP extends to transistor formation, and importance of CMP process becomes highly underscored.

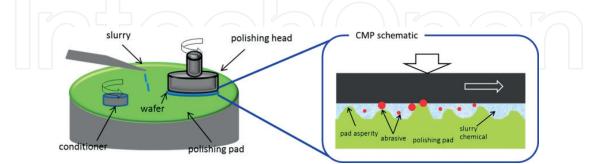

**Figure 3(a)** shows polisher equipment and wafer polishing processing. Polishing head holds wafers by vacuum and it rotates on the polishing pad. Slurry is delivered by slurry arm and polishing pad conditioner refreshes polishing pad surface as each wafer processing, which results in global planarization and polishing. Whereas, in microscale observation, complicated interaction among pad asperity-slurry (abrasive and chemistry)-wafer surface occurs during CMP processing, which is depicted in **Figure 3**. According to semiconductor process development, CMP process itself has developed its equipment, consumables, polishing functions and slurries to improve performance.

CMP performances are defined by removal rate (throughput), selectivity, planarization (planarity), within wafer non-uniformity, surface topography (roughness), corrosion and post CMP defects. The definitions of them are:

**Figure 1.** The concept of chemical mechanical polishing (CMP). Non-planarized topography becomes planarized surface by CMP.

Figure 2. The schematic mechanism of material removal by CMP.

Figure 3. The schematic of conventional CMP equipment.

Removal Rate (RR) = (pre CMP thickness-post CMP thickness)/(polishing time)

Within Wafer Uniformity = Film thickness sigma post CMP/Film mean thickness post CMP

Selectivity (A:B) = RR of A material/RR of B material

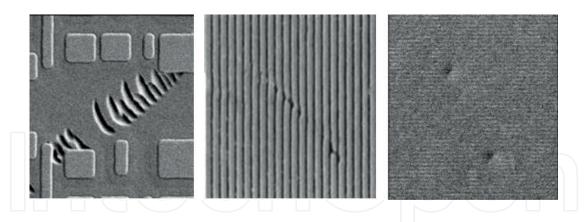

Planarization is commonly measured by step height reduction rate. These performances are closely related with device yield and electrical performances. For example, CMP-induced microscratch defect (**Figure 4**) is detrimental to device yield [3, 5]; transistor resistance is strongly influenced by post CMP uniformity, and residual material blocks subsequent patterning. CMP performances are determined by multiple CMP process factors; however, CMP slurry is the most influencing parameter. CMP slurry consists of abrasive particles and chemical components such as pH adjuster, dispersant, polymeric additives, oxidizer, and passivation agent, depending on polishing purpose to provide proper surface modification of material.

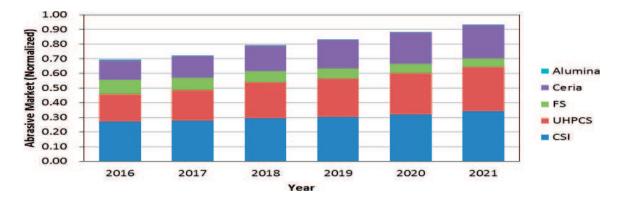

As described in **Figure 3**, direct contact between abrasive particle and wafer surface removes material, thus, properties and characteristics of abrasive particle and their understanding are inevitable to optimize CMP process. Although a lot of different kinds of abrasives have been tried for CMP applications, three abrasives have been employed successfully until recent device manufacturing. They are silica-based abrasive, ceria-based abrasive, and alumina-based abrasive. However, CMP is indispensable process for future semiconductor fabrication and it needs development of new abrasives for the success of new designed device and matured manufacturing. **Figure 5** shows CMP abrasive market trend in semiconductor industry [14]. Its growth expectation for the next 4 years is about 30% increase from 2016. This chapter introduces abrasive particles and their applications to CMP process for semiconductor manufacturing.

Figure 4. The examples of CMP-induced microscratch images [13].

**Figure 5.** Slurry abrasive market trend (Reprinted from Ref. [14] with permission from author. Copyright Linx-consulting). FS is fumed silica, UHPCS is ultra-high purity colloidal silica and CSI is colloidal silica abrasive.

## 2. Abrasive for dielectric CMP

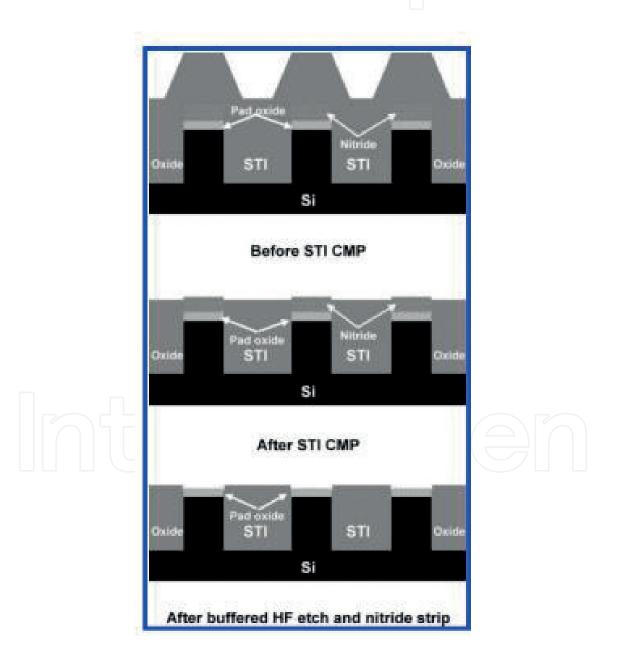

A dielectric material in semiconductor processing refers to insulating materials and mostly it indicates all kinds of silicon oxide materials [5]. Most dielectric CMP applications focus on transistor formation, which is called as front end of the line (FEOL) process. And dielectric CMP requires either oxide bulk CMP or CMP stop on 'stopper' material. For the stop on CMP case, oxide material is removed by CMP and CMP stops when stopper material is exposed. Shallow trench isolation (STI) CMP and interlayer dielectric (ILD) CMP are representative dielectric CMP applications. STI CMP process (stop on 'silicon nitride') is described in **Figure 6** [3] as an example of dielectric CMP. The stopper materials are mostly silicon nitride or polysilicon in FEOL process. For dielectric CMP purpose, two – three major abrasives are used in the advanced node semiconductor manufacturing.

#### 2.1. Silica-based slurry and silica abrasive

As briefly described in the introduction, CMP mechanism is soft layer removal by abrasive particle. This section introduces silica particle as slurry abrasive. During dielectric CMP process, silicon oxide surface reacts with  $OH^-$  from the slurry solution and forms silicon hydroxide,  $Si(OH)_4$ . The hydration reaction is.

$$(SiO_2)_x + 2H_2O \rightarrow (SiO_2)_{x-1} + Si(OH)_4$$

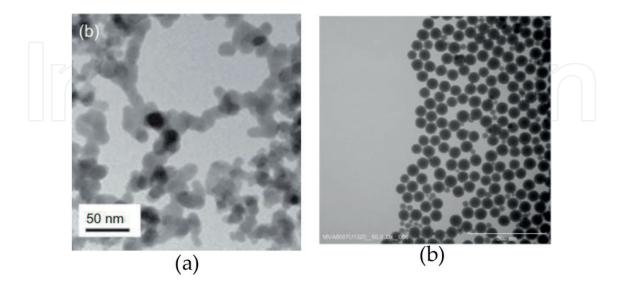

And this soften Si(OH)<sub>4</sub> is mechanically removed by silica abrasive [3, 15]. Then silicon oxide surface is exposed and hydration occurs again. This process is repeating until silicon oxide disappears. From **Figure 2**, soft layer can be considered as Si(OH)<sub>4</sub> in this case. The hydration rate is influenced by the concentration of OH<sup>-</sup> ions in the solution, thus alkaline environment can accelerate surface hydration and make fast material removal by fast reaction [2, 15–16]. Therefore high pH silica-abrasive slurry is favorable to obtain high removal rate. Two common synthesizing methods of silica abrasives are commercially used in the semiconductor industry. One is fumed process and the other is colloidal process [5, 17–19]. The typical abrasive images

**Figure 6.** Procedure of shallow trench isolation (STI) CMP. Polishing stop on silicon nitride (Reprinted with permission from Ref. [3]. Copyright 2010 American Chemical Society).

of silica abrasive by each synthesis methods are shown in **Figure 7** [20, 21]. Fumed silica synthesis uses flame reaction of chlorosilane at high temperature, which is summarized at.

$$SiCl_4 + 2H_2 + O_2 \rightarrow SiO_2 + 4HCl$$

With this method, early development of silica abrasive particle size is larger than 300 Å, but development of filtration and post treatment enables to control the abrasive size below 150 Å. The commercial fumed silica abrasive slurry for dielectric CMP has high abrasive concentration to achieve enough removal rate. However, high abrasive concentration caused scratch defects, easy to agglomerate and clogging problem in slurry delivery system or filter.

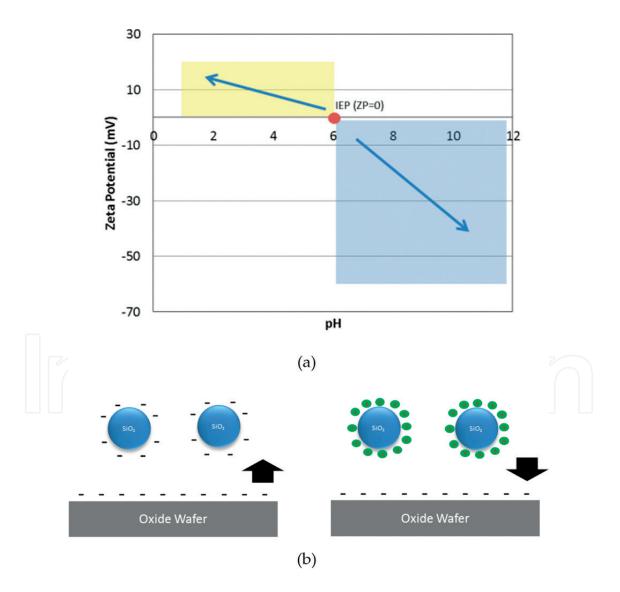

Figure 8 shows example of clogged silica abrasive, which leads to significant defects on the wafer at post CMP. The whitish particles are silica abrasive in the slurry loop system. Therefore recent device manufacturing use high percentage of fumed silica abrasive slurry less and less, and forecast expects less usage of fumed silica abrasive as shown in Figure 5. Contrary to fumed method, colloidal abrasive is synthesized by liquid phase growth process via precursor [5, 16, 18–25]. Commonly, colloidal silica is made from sodium silicate (Na<sub>2</sub>SiO<sub>3</sub>) or sodium meta-silicate (NaHSiO<sub>3</sub>). By ion exchange, sodium ion is eliminated and colloidal silica is formed to be used as CMP slurry abrasive. Colloidal silica abrasive slurry has much lower removal rate than fumed silica abrasive although it gives much lower scratch defect performance by its spherical shape and small size. To enhance removal rate of dielectric material by colloidal silica, organic cation is added as removal booster [16]. It changes colloidal silica abrasive surface charge from negative into positive and coulombic attraction force between abrasive and dielectric surface, which is negative, accelerates removal rate. As shown in Figure 9(a), surface zeta potential behavior with respect to pH [26] can support this mechanism. Schematic of enhanced removal rate by colloidal silica abrasive is given in the same Figure. pH control is critical to this case. Recently, several attempts to new synthesis of silica abrasive to add

**Figure 7.** TEM images of (a) fumed (Reprinted by permission from [20], Copyright 2012 American Chemical Society) and (b) colloidal silica abrasive [21].

Figure 8. The clogged silica abrasive in slurry delivery loop.

**Figure 9.** (a) Zeta potential of  $SiO_{2'}$  and (b) silica abrasive without surface treatment and with surface treatment with organic cation at acidic region.

more stable particle distribution have been reported [26–29]. For instance, Pan et al. presented silane modified silica abrasive particle preparation to mitigate gelation of colloidal silica due to high chemically active hydroxyl group from silica surface. The siloxane groups in silane and hydroxyl groups in silica surface generate hydrolysis condensation reaction, which results in surface zetapotential change to improve dispersion stability [27].

#### 2.2. Ceria abrasive for dielectric CMP slurry

Although high removal rate, low cost of ownership and effective planarization are obtained by silica abrasive, selectivity control and low scratch defect requirements bring ceria-based abrasive to be universally used in dielectric CMP of advanced node semiconductor manufacturing. And recent dielectric CMP uses ceria-based slurry much more than before (refers to **Figure 5**). The CMP mechanism by ceria-based slurry is different from silica-based slurry. Instead of mechanical removal by silica abrasive, ceria abrasive uses surface interaction with silicon oxide dominantly, which is.

$-Ce - OH + -SiO^{-} \rightarrow -Si - O - Ce + OH^{-}$

Strong bonding between Ce and hydrated silicate detach silicon oxide and Si-O-Ce lump is removed from the surface [15, 30]. Ceria CMP process is shown in **Figure 10**.

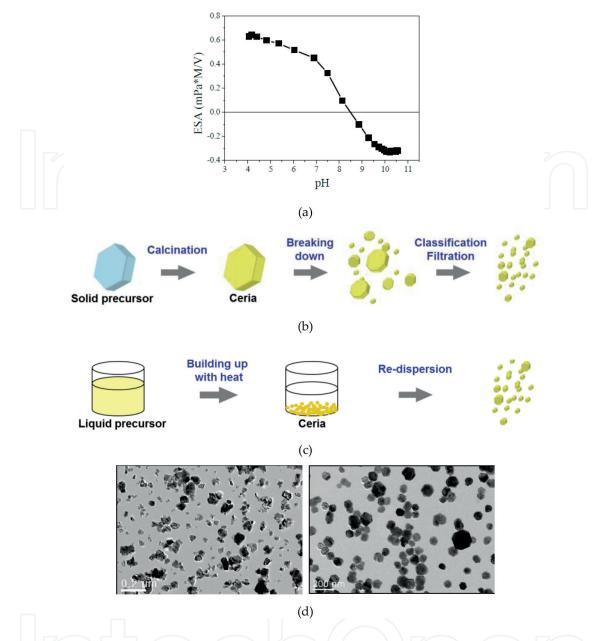

Therefore, ceria abrasive surface charge control is important in determining CMP performance. The surface charge behavior can be indicated by ceria zeta potential property [31]. As shown in **Figure 11(a)**, isoelectric point (IEP) of ceria is ~pH 8 (at acidic: positive charge, at alkaline: negative charge) and surface potential is opposite to silicon oxide at acidic environment. Thus, most ceria-abrasive slurry pH is less than 8 to facilitate Si-O-Ce formation. Similar to silica abrasive synthesis, two types of ceria-base abrasive are commonly synthesized for CMP applications [5, 31, 32]. They are calcined ceria abrasive and wet (or colloidal) ceria abrasive. Calcined synthesis is based on solid-state oxidation process. Raw ceria material is oxidized followed by mechanical crushing to make them small particles. And filtration removes large particles. Depending on crushing condition and filtration, calcined ceria abrasive size can be controlled. On the other hand, wet process uses precipitation procedure in liquid state. Seed ceria nuclei in an aqueous cerium solution grows and forms ceria (or cerium hydroxide) particles. Ceria abrasive made by wet process has spherical shape and narrow particle size distribution compared with calcined process. These synthesis methods and typical ceria abrasive images from each method are shown in **Figure 11(b)–(d)** schematically

Figure 10. The schematic mechanism of oxide removal rate by ceria abrasive.

**Figure 11.** (a) Zeta potential curve of conventional ceria abrasive, (b) synthesis of calcined ceria abrasive, (c) synthesis of colloidal ceria abrasive, (d) TEM images of calcined (left) and colloidal (right) ceria abrasives ((a) & (d) reprinted by permission from mater. & interfaces, Jihoon Seo et al. [35], Copyright 2014 American Chemical Society) ((b)&(c) Reprinted from Ref. [34] with permission from authors)).

[31, 33–35]. The overall property comparison between calcined processed ceria abrasive and colloidal ceria abrasive is summarized in **Table 1** [31]. Calcined ceria abrasive slurry provides steady removal rate. Wet ceria abrasive slurry shows relatively lower removal rate than calcined ceria abrasive, however, the most critical advantage of wet ceria abrasive slurry is scratch defect improvement due to small and regular shape of abrasive particle. Recent study by Seo revealed Ce surface oxidation state had significant influence on the CeO<sub>2</sub> interaction to silicate and they investigated the effect of concentration of Ce<sup>3+</sup> ions on the affinity to silicate ions and wet ceria particle size effect on the adsorption of silicate [35, 36]. Higher concentration of Ce<sup>3+</sup> ions increased adsorption affinity with silicate ions and larger ceria abrasive has

| Colloidal CeO <sub>2</sub>        |

|-----------------------------------|

| Mean particle size (nm): 120–170  |

| Relatively low oxide removal rate |

| Spherical shape                   |

| Uniform size distribution         |

| High cost                         |

| Relatively low scratch            |

|                                   |

|                                   |

|                                   |

Table 1. Properties of calcined CeO<sub>2</sub> and colloidal CeO<sub>2</sub> (Reprinted from Ref. [31] with permission from author).

higher Ce<sup>3+</sup> ions due to higher surface to volume ratio. In addition to calcined and wet process, flux method to synthesize ceria abrasive particle has proposed to overcome limitation of calcined or wet process [37]. It uses cerium nitrate hexahydrate (Ce(NO<sub>3</sub>)<sub>3</sub>·6H<sub>2</sub>O) and potassium hydroxide (KOH) as starting material and ethylene glycol (C<sub>2</sub>H<sub>6</sub>O<sub>2</sub>)-DI mixture as solvent. Through precipitation, hydrothermal reaction and centrifuging process, narrow size distribution with desirable characteristics ceria abrasives synthesis are demonstrated [37]. Ceria or ceria-based slurry application in CMP is increasing and advanced slurries with ceria abrasive are emerging in the semiconductor industry. Ultrafine (or nano-sized) ceria abrasive and composite abrasive will be introduced in Section 5.

## 3. Abrasive for tungsten CMP

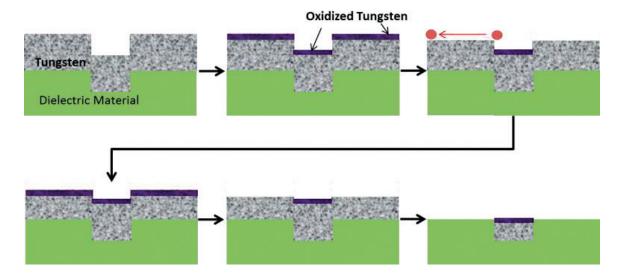

Tungsten has been used for metal interconnection and contact formation. Many candidate metals have been developed to replace tungsten; however, tungsten is still standard metal for sub 14 nm contact formation due to its excellent electromigration and diffusion barrier performance [3, 38]. The CMP mechanism of tungsten was proposed by Kaufmann firstly [39]. A pristine tungsten surface is oxidized by oxidizer at acidic condition and it transforms to tungsten oxide (WO). The formation of oxide depends on solution and chemistry. Tungsten oxide plays a role as passivation layer to protect subsurface tungsten from dissolution or corrosion. And tungsten oxide is easy to be removed by mechanical force of abrasive since its hardness is less than pure tungsten. This process is repeated until CMP stops. Therefore, role of chemistry (in particular oxidizer) is important in tungsten CMP. Among many kinds of oxidizer, ferric nitrate ( $Fe(NO_3)_3$ -) is the most successful one [3, 5]. The schematic description of tungsten CMP mechanism is given in Figure 12. The common and commercially available slurry for tungsten CMP has alumina-base and silica-base abrasives [3, 5]. At sub 14 nm logic device fabrication, tungsten CMP is the most important process to enable transistor formation. It requires superior planarity and extremely accurate uniformity control. For this purpose, alumina abrasive showed better planarity and selectivity performance. Hence its utilization for bulk tungsten CMP is commonly adopted in advanced device manufacturing.

Figure 12. The mechanism of tungsten CMP.

Alumina abrasive has been synthesized by alum process and calcination [18]. For CMP application, alpha-alumina abrasive is commonly used. Hardness of alumina abrasive is much higher than tungsten and tungsten oxide, therefore it is easy to make scratch defect on the surface. Moreover, due to the surface charge difference between alumina and tungsten at acidic region, attractive force retains alumina abrasive on the wafer surface. Recently, composite alumina abrasive with polymeric material has been introduced in the industry due to defect concern at advanced node semiconductor [38]. Silica base slurry utilization on tungsten CMP is usually for non-selective CMP purpose (polishing both tungsten and dielectric material) because its selectivity with oxide is not as high as alumina abrasive slurry. Tungsten CMP is driven by chemical effect more than mechanical abrasion, removal rate strongly depends on chemical components (oxidizer, surfactant, and stabilizer) and activation condition (for example, process temperature) [39–41]. Therefore adequate combinations among them are essential to provide desired CMP performances. Although removal rate is linearly increasing with abrasive concentration in the slurry, loading effect (very low removal rate or non-linear removal rate behavior at the early stage of CMP) is more significant in tungsten CMP than dielectric CMP. Yttrium, ceria, zirconium and composite abrasives have been tried and under development for tungsten CMP applications [3].

## 4. Abrasive for copper CMP

Copper is introduced in semiconductor manufacturing for metal interconnection application mid-1990s and now it is standard metal for back end of the line interconnection [2–4, 10]. Accordingly, CMP for copper has been highlighted due to its process challenges. Like tungsten CMP, copper CMP mechanism is based on Kaufman's model. Chemical reaction from slurry produces oxidized copper and abrasive particle removes oxidized copper. The major components of copper CMP slurry are abrasive, oxidizer, inhibitor, surfactant and chelating agent. The challenges of copper CMP are scratch defects and copper corrosion. Corrosion is

mostly induced by chemical in the slurry and most of scratch defects are driven by abrasive particle. In particular, hardness of copper is lower than most abrasive particles. Therefore, smaller size of abrasive with spherical shape and less abrasive content are favorable to the slurry formulation. The common copper CMP abrasives are alumina and colloidal silica [3, 10]. However, at advanced semiconductor manufacturing, colloidal silica abrasive becomes prevalent because it has appreciable polish rate of barrier material (tantalum/tantalum nitride). The copper removal rate and CMP performances are sensitively influenced by chemistries and components in slurry in conjunction with silica abrasive characteristics. Most of copper CMP slurry researches have focused on chemistry perspective instead of abrasives.

## 5. Advanced abrasives for future CMP applications

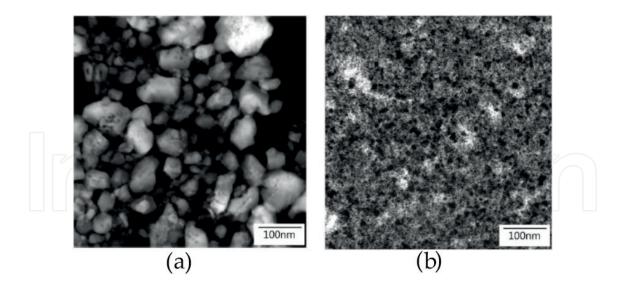

One of the most important requirements of CMP process in semiconductor application is scratch defect reduction, which has mentioned in this chapter several times. For abrasive perspective, smaller size abrasive particle is favorable for scratch defect. Therefore, recent abrasive technology has focused on nano-sized abrasive synthesis with minimized agglomeration. For dielectric CMP, nano-sized cerium hydroxide (or ultrafine cerium hydroxide or nano-ceria) abrasive slurry has been introduced due to its potential scratch defect reduction [33–34, 42–43]. The synthesis procedure of nano-sized cerium hydroxide abrasive is given in **Figure 13**.

Transmission electron microscope image of calcined ceria abrasive and nano-sized abrasive is compared in **Figure 14** [44]. Single abrasive size becomes as small as 5 nm. Even agglomerated abrasive size is less than 20 nm. Tanaka et al., showed removal rate and selectivity control by changing additives [33–34]. However, CMP mechanism of nano-sized cerium hydroxide abrasive is not clearly understood yet. Han et al. reported polishing pad surface roughness control is critical to maintain removal rate stability with nano-sized cerium hydroxide abrasive [44]. Kim proposed particle coverage model on the wafer as material removal mechanism with nano-sized cerium hydroxide abrasive [43]. In order to apply nano-sized cerium hydrox-ide abrasive for dielectric CMP, role of chemistry to enhance removal rate with selectivity control needs to be further explored.

Composite abrasive has drawn attention to the semiconductor industry recently. Each abrasive has its own unique properties. Some of them are very attractive and some of them are not good for desired CMP performances. Tries to combine advantages only from different abrasives have triggered ceria-silica composite abrasive development [45–48]. Researchers have paid attention to ceria-coated silica as next generation CMP slurry abrasive. Zhao et al.

Figure 13. Synthesis of nano-sized cerium hydroxide abrasive (reprinted from Ref. [33] with permission from authors).

**Figure 14.** TEM images of (a) calcined ceria abrasive and (2) nano-sized cerium hydroxide abrasive (reprinted by permission from Ref. [44], Copyright 2013 Springer Nature).

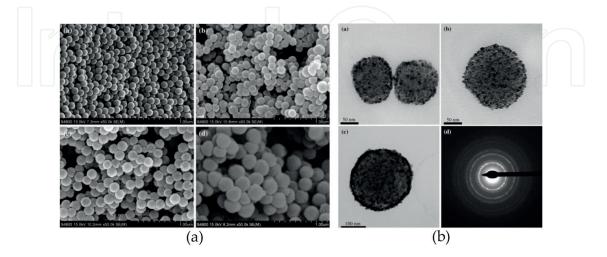

uses sol-gel method to synthesize ceria-coated silica abrasive [48]. They prepared tetraethylorthosilicate and ammonia as raw materials, and composite nanoparticles are synthesized through precipitation procedure. About 150-200 nm spherical ceria-coated silica abrasives are successfully synthesized. Shell ceria size is 10 nm. Peedikakkandy et al. synthesized monodispersed ceria coated silica nanoparticles by micro-emulsion method and chemical precipitation process [46]. About~10 nm crystalline ceria over silica with spherical shape and overall particle size <100 nm abrasive is successfully obtained. Zhang et al. synthesized ceria-coated silica abrasive by precipitation process using ammonium cerium nitrate and urea as precipitant with poly(vinylpyrrolidone) (PVP) as assistant [45]. With optimized synthesis conditions, <200 nm ceria-coated silica abrasive is obtained. In their study, X-ray diffraction confirms face centered cubic CeO, nanoparticle encapsulate core silica. Scanning electron microscope (SEM) shows uniformly distributed particles with spherical shape. Transmission electron microscope (TEM) directly shows evidence of homogenous nucleation of ceria particles and heterogeneous nucleation of silica particle with uniform, distinctive and crystalline ceria shell. With ceria-coated silica composite abrasive, higher removal rate than pure silica abrasive and comparable surface roughness is demonstrated on glass substrate CMP. Likewise ceria-coated ceria abrasive, Chen et al. reported composite abrasive containing solid silica core with silica mesoporous shell structure [29]. The advantage of mesoporous silica is its significant elastic recovery ability combined with ductile behavior. Chen et al. synthesized solid silica core via conventional Stöber procedure and shell silica encapsulating the core by means of modified Stöber process. It uses vinyltrimethoxysilane (VTMS) as silica source and cetyltrimethylammonium bromide as structure directing agent. Well defined spherical shape abrasives are successfully achieved and it shows clearly core-shell structure. The thickness of mesoporous silica shell is controlled by VTMS amount during synthesis. With this abrasive, higher removal rate of thermal silicon dioxide film and lower surface roughness are exhibited. Polymeric composite has drawn attention to CMP society due to its potential scratch defect reduction. Chen et al. reported polymer based core-shell abrasive aiming to reduce scratch defect by CMP. The core abrasive is spherical polystyrene (PS) and ceria is selected as shell abrasive [49]. The mechanism of low scratch and minimize wafer damage is cushion effect of soft polymer core abrasive. In-situ chemical precipitation with mixture of deionized water, PS spheres, cerium nitrate hexahydrate (Ce(NO<sub>3</sub>)<sub>3</sub>·6H<sub>2</sub>O), and hexamethyleneteramine is used for this hybrid abrasive synthesis. As shown in **Figure 15**, it is clearly observed uniformly distributed ceria particles on the PS core, indicating the formation of core/shell structured abrasive particle. The ceria particle size is about 10 nm and face centered cubic structure which is confirmed by XRD and SAED pattern. Based on CMP test with thermal oxide film, PS/ceria hybrid abrasive slurry demonstrates lower removal rate, fewer scratches, and lower surface roughness are compared with ceria abrasive slurry.

Nano-sized ceria abrasive is already used in the semiconductor manufacturing. Ceria-silica or silica-silica composite abrasive is still under development stage although several unique synthesizes are suggested and demonstrate promising CMP data. Most of literatures with composite abrasive focus on material removal rate and surface quality. However, CMP application needs more performances. In order to be utilized in the industry, composite abrasives have to avoid agglomeration, need to robust abrasive stability, require optimized chemistry, and more CMP performances such as selectivity and defectivity must be fulfilled.

New materials CMP has emerged along with new device introduction and device node shrinkage, from ultra-soft materials such as porous low-k and photoresist to highly non-reactive metal such as ruthenium (Ru) [3–5, 50, 51]. Ultra-soft material CMP needs very soft abrasive or even abrasive-free slurry development [5]. Ru is little chemical reactive metal with high hardness. And it relies more on mechanical force to remove Ru layer than chemical dissolution. Moreover,  $RuO_4$ , which can be produced by slurry chemistry, is toxical gas [50, 51]. Therefore Ru CMP has a lot of limitation to achieve enough removal rate by CMP. Cobalt (Co) is the most potential candidate metal for replacing tungsten as contact metal (or replacing Ta/TaN as barrier metal) and its CMP slurry abrasive development is upmost challenge for device fabrication [52–54]. Known issues by Co CMP are residual abrasive particle defects and Co corrosion. More difficulties on these materials are not only target material CMP but

**Figure 15.** (a) SEM images and (b) TEM images of PS/ceria composite abrasive (Reprinted by permission from Ref. [49], Copyright 2016 Springer Nature).

also neighboring materials CMP for proper selectivity. Most of new materials CMP slurry is based on silica abrasive and chemistry optimization has been underscored. However, it still has a lot of opportunities to develop abrasives as well. Carbon based materials (either carbon nanotube or graphene) have drawn intense interests to the semiconductor industry for a long time. For CMP perspective, carbon-based material polishing, which has been rarely reported, is big challenge to abrasive development due to its high hardness.

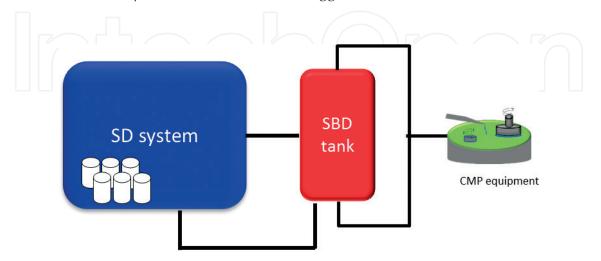

## 6. Abrasive control in semiconductor fab

The role of abrasive in CMP application is to obtain enough material removal rate, desired selectivity and low defect (residual particle and scratch) performance. In addition to develop advanced abrasive material and synthesis, abrasive size distribution and dispersive ability in the solution has been developed to control large particle count. Particle size distribution is raw abrasive material nature resulting from synthesis, however, slurry distribution system and filtration can control large particles and agglomeration from the slurry without CMP performance degradation. In high volume semiconductor manufacturing fab, slurry distribution system is considered as infrastructure instead of equipment [18, 55]. It consists of (1) slurry drum, (2) agitation of drum (drum tumbling), (3) slurry blending and dispense, (4) daytank (or standby tank) with stirrer, (5) looping to tools. Figure 16 shows simplified distribution system. Slurry is being circulated in the loop until it is used for CMP. Abrasive agglomeration is induced by shear stress, temperature change and chemistry variation if proper filtration is not implemented [56]. The location of filters from slurry distribution system is selected carefully. More filtration drops slurry flow pressure quickly by filter itself. Very fine filter will removes most abrasives, which results in low removal rate. Different slurry needs different type of filter and filtration at different locations; however global loop filtration and point of use (POU) filtration at polishing equipment are quite standard [18, 56, 57]. Global filter size is normally >10 µm, which is bigger than POU filter to avoid flow pressure drop. POU filter size is smaller than 1 µm. Yi Wei et al., showed agglomeration behavior of different slurries.

**Figure 16.** Slurry delivery facilities in semiconductor manufacturing fab. (SD = slurry dispense, SBD = standby distribution).

Colloidal silica abrasive agglomeration is more sensitive to shear stress than ceria abrasive. The most important challenge of filtration is plugging by abrasives. Three plugging mechanisms in filtration are well known, which are cake formation, gradual plugging, and complete plugging [58]. Cake formation is driven by particles build up on the filter surface, gradual plugging is induced by particles building up on the pore, and compete plugging indicates pore blocking by particles. Depending on particle size, deformability, and agglomeration, filtration procedure can be optimized. The most commonly used filter in CMP slurry is 'graded density depth' type. It has multi-layers of fibrous media and there is retention gradient along with flow direction. Commonly, large particles are captured first at outer layer and small particles are retained at inner layer. However, more advanced filter and filtration researches are reported recently. Nano-fiber based advanced filter to remove large abrasive as well as avoid agglomeration is reported. Morby et al., suggested composite/rigid structured filter which consists of thermally bonded polyolefin bi-component coarse fiber matrix and microfiber-glass web as next generation filter to retain slurry flow pressure and remove large abrasive effectively [59]. In addition to filtration, dispersant in the slurry prevents abrasive from agglomeration. For high abrasive content slurry case, abrasive particles are easy to sediment and agglomerate by particle charge interaction. Along with slurry abrasive development, advanced filter development and prevention of sediment of abrasive are required in slurry preparation.

## 7. Conclusion

This chapter reviews abrasives for CMP applications in semiconductor manufacturing. It includes abrasive types, abrasive synthesis, CMP mechanism and role of abrasives, and opportunities of new abrasive developments. Semiconductor business increases explosively and various semiconductor structures with high performance have been developed according to market requirement. In order to achieve mature semiconductor manufacturing, CMP process development is critical and abrasives in slurry play a pivotal role in determining CMP performances. The most common abrasive in dielectric CMP is either silica-based or ceria-based one. For metal CMP (tungsten and copper), silica is the most popular abrasive. Advanced synthesis for silica or ceria abrasives, new abrasive materials, and composite abrasives have studied for high performance CMP and new material CMP. Furthermore, the control of slurry abrasive in the looping is emphasized. Advanced filtration is critical to maintain abrasive size distribution. The applications of CMP are mostly focused on semiconductor industry; however its utilization expands to display industry, M/NEMs, automobile industry and biotechnology. The key of each application is noble abrasive development with proper chemistries.

## Author details

Hong Jin Kim

Address all correspondence to: hongjin.kim@globalfoundries.com

Advanced Module Engineering, GLOBALFOUNDRIES, Malta, NY, USA

### References

- Li Y, edited. Microelectronic Applications of Chemical Mechanical Planarization. USA: John Wiley & Sons Inc; 2008

- [2] Steigerwald JM, SP Murarka, Gutmann RJ. Chemical Mechanical Planarization of Microelectronic Materials. USA: John Wiley & Sons Inc; 1997

- [3] Krishnan M et al. Chemical Reviews. 2010;110:178-204

- [4] Zantye PB, Kumar A, Sikder AK. Materials Science and Engineering R: Reports. 2004; 45:89-220

- [5] Babu S. Advances in chemical mechanical planarization (CMP). In: Woodhead Publishing Series in Electronic and Optical Materials. 2017

- [6] Tsujimura M. Japanese Journal of Applied Physics. 2016;55:06JA01

- [7] Hoffmann TY. Solid State Technology. 2010;53:20-23

- [8] Feeney P. Solid State Technology. 2010;53(10):14

- [9] Kim HJ et al. Proceedings of Advanced Metallization Conference: 27th Asian Session 2017. pp. 92-93

- [10] Ein-Eli Y, Starosvetsky D. Electrochemica Acta. 2007;52:1825-1838

- [11] Steigerwald JM. Proceedings of IEDM. 2008:37-40

- [12] Chi M-h. Challenges in Manufacturing FinFET at 20nm node and beyond. Technology Development, GlobalFoundries; 2014. http://www.rit.edu/kgcoe/eme/sites/default/files/Minhwa%20Chi%20-%20abstract\_%20Challenges%20in%20Manufacturing%20FinFET.pdf

- [13] Kim HJ. International Conference on Planarization/CMP Technology. AZ USA: Pheonix; 2010

- [14] http://www.linx-consulting.com/

- [15] Cook LM. Journal of Non-Crystalline Solids. 1990;120:152-171

- [16] White ML, Jones L, Romine R. The mechanism of low pH silica based oxide slurries. Cabot Microelectronics Technical Paper (https://www.cabotcmp.com/cmp-research/cmptechnical-papers/)

- [17] Tutorial, Planarization Processes for ULSI Fabrication to the Year 2002 (SEMICON WEST, July 16, 1997) p. 51

- [18] Li SH, Miller RO. Chemical Mechanical Polishing in Silicon Processing. USA: Academic Press; 2000

- [19] Doering R, Nishi Y. Handbook of Semiconductor Manufacturing Technology. 2nd ed. USA: CRC Press; 2008

- [20] Zhant H et al. Journal of the American Chemical Society. 2012;134(38):15790-15804

- [21] Gert Roebben et al. Frontier in Chemistry, Technical Report, Oct. 19, 2015 (https://www.researchgate.net/publication/283302479\_Reference\_materials\_and\_representative\_test\_materials\_to\_develop\_nanoparticle\_characterization\_methods\_The\_NanoChOp\_project\_case)

- [22] Zhang KL et al. Journal for Nanoscience and Nanotechnology. 2009;9(2):1054-1057

- [23] Qin F, Liu W. Proceedings of 2015 International Conference on Planarization/CMP Technology (ICPT). pp. 119-122

- [24] Kao MJ, Hsu FC, Peng DX. Advances in Materials Science and Engineering. 2014;2014:1-8

- [25] Ming-ShyongTsai. Materials Science and Engineering: B. 15 January 2004;106(1):52-55

- [26] Park K-W et al. Journal of the Korean Physical Society. 2007;51(1):214-223

- [27] Shun G et al. Wear. 2011;273:100-104

- [28] Posthumus W et al. Journal of Colloid and Interface Science. 2004;269:109-116

- [29] Chen A et al. Journal of Alloys and Compounds. 2016;663:60-67

- [30] Hoshino T et al. Journal of Non-Crystalline Solids. 2001;283:129-136

- [31] Seo J. Surface Chemistry of Ceria Nanoparticles for CMP Applications. CAMP's 22th International Symposium on CMP; 2017

- [32] Raghavan S, Keswani M, Jia R. Kona Powder and Particle Journal. 2008;26:94

- [33] Tanaka T et al. Proceedings of 2014 International Conference on Planarization/CMP Technology (ICPT). pp. 22-24

- [34] Minami H. Polishing Selectivity Control for Scratch Free Nano Size Cerium Hydroxide Slurry. CAMP's 19th International Symposium on CMP; 2014

- [35] Seo J et al. ACS Applied Materials & Interfaces. 2014;6:7388-7394

- [36] Seo J et al. Applied Surface Science. 2016;389:311-315

- [37] Myoung-Hwan O et al. Powder Technology. 2011;206:239-245

- [38] Broadbent EK et al. IEEE Transactions on Electron Devices. 1988;35:952-956

- [39] Kaufman FB et al. Journal of the Electrochemical Society. 1991;138(11):3460-3464

- [40] Kim HJ et al. ECS Journal of Solid State Science and Technology. 2014;3(10):P310-P314

- [41] Palla BJ et al. IEEE/CPMT International Electronics Manufacturing Technology Symposium. 1998. 155-163

- [42] Kim HJ, Qin L, Lee T. TechConnect World Innov. Conf. Washington DC, USA; 2015

- [43] Kim HJ, Lee TH, Ryan A. ECS Transactions. 2016;72(18):27-36

- [44] Han S et al. Electronic Materials Letters. 2013;9(2):155-159

- [45] Zhang Z et al. Applied Surface Science. 2010;257:1750-1755

- [46] Peedikakkandy L et al. Applied Surface Science. 2015;357:1306-1312

- [47] Chen G et al. Applied Surface Science. 2015;359:664-668

- [48] Zhao X et al. Microelectronic Engineering. 2010;87:1716-1720

- [49] Chen A et al. Journal of Materials Science: Materials in Electronics. 2016;27:2919-2925

- [50] Ruthenium CMP. Integration for Dual-Damascene Copper Interconnects. Cabot Microelectronics Technical Paper (https://www.cabotcmp.com/cmp-research/cmp-technical-papers/)

- [51] Cheng J et al. Proceedings of 2016 International Conference on Planarization/CMP Technology (ICPT). pp. 195-198

- [52] Alety SR et al. ECS Journal of Solid State Science and Technology. 2017;6(9):P671-P680

- [53] Changhong W et al. ECS Transactions. 2017;77(5):93-97

- [54] Turk MC et al. ECS Journal of Solid State Science and Technology. 2016;5(2):P88-P99

- [55] Mason M. CMP metrics improved by undiluted slurry data. Solid State Technology (http://electroiq.com/blog/2011/06/cmp-metrics-improved-by-undiluted-cmp-slurry-data/)

- [56] Lu Y et al. Proc. of 2014 International Conference on Planarization/CMP Technology (ICPT). pp. 291-295

- [57] Wu M et al. Proceedings of 2017 International Conference on Planarization/CMP Technology (ICPT), pp. 323-328

- [58] Yang HJ, et al. Semiconductor Technology International Conference (CSTIC), 2015. China: 2158-2297

- [59] Morby J, Entezarian M, Gieger B. Proceedings of 2015 International Conference on Planarization/CMP Technology (ICPT). pp. 128-131

IntechOpen