### We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

6,900

186,000

200M

Downloads

154

Countries delivered to

Our authors are among the

$\mathsf{TOP}\:1\%$

12.2%

most cited scientists

Contributors from top 500 universitie

#### WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

## Introductory Chapter: Complementary Metal Oxide Semiconductor (CMOS)

Kim Ho Yeap and Humaira Nisar

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/intechopen.73145

#### 1. Introduction

In 1970s, the number of transistors in an integrated circuit (IC) chip was not more than 10,000 and the feature lengths of the transistor were larger than 1  $\mu$ m. The Motorola 6800 microprocessor, for instance, had only a count of 4100 transistors in it with a feature length of 6.0  $\mu$ m. In less than half a century time, however, the IC industries have undergone a dramatic revolution. Nowadays, the number of transistors in a chip can possibly hit 10 billion and the feature length may be as small as 10 nm. The significant increase in the number of transistors has enabled more functionalities to be installed in a chip. This is to say that, the chip found in an electronic device today is much smaller and, yet, more powerful [1]. Since the circuits in a typical chip are designed by incorporating two types of transistors that complement each other, the fundamental building block that powers up electronic circuits is known as a complementary metal oxide semiconductor field effect transistor or CMOS device. To provide readers with an overview of the CMOS device, this chapter gives a concise but complete illustration on the historical development and the operation of the device.

#### 2. A brief history

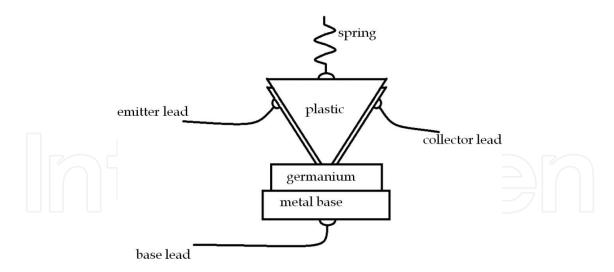

When transistors were first introduced in early 1900s, they were actually made of vacuum tubes. The vacuum tube transistors were large and cumbersome to be used. In December 1947, John Bardeen, Walter Brattain and William Shockley from the Bell laboratory invented the point-contact germanium transistor. As can be seen in **Figure 1**, this transistor was much smaller in size. It also consumed significantly less power, operated at lower temperature and gave quicker response time. Because of this reason, the vacuum tube transistor was swiftly replaced by its solid-state counterpart. The solid-state transistor is obviously more convenient to be used.

Figure 1. A point-contact transistor.

Very soon after its introduction, the electronic industries went through a dramatic revolution. Because of this significant contribution, the three scientists from the Bell laboratory shared the Nobel Prize in Physics in 1956.

The first commercially available silicon transistors were manufactured by Gordon Teal in 1954. Since silicon gives better performance than germanium, the substrate material for transistors was gradually changed to silicon. In 1955, the first diffused silicon transistor made its appearance. To reduce the resistivity of the collector, an epitaxy was deposited onto the transistor in 1960. In the same year, the planar transistor was proposed by Jean Hoerni [2, 3].

Without knowing each other and using their own methods, Jack Kilby from Texas Instruments and Robert Noyce from Fairchild invented independently the integrated circuits (ICs) in late 1950s. Kilby's IC was merely a simple 0.5 inch germanium bar, with a transistor, a capacitor and three resistors connected together using fine platinum wires; whereas, Noyce's was closer to the look of an IC today – the transistors were etched on a 4-inch silicon wafer. Both Kilby and Noyce shared the patent right for the invention of the integrated circuit. In 2000, Kilby was awarded the Nobel Prize in Physics "for his part in the invention of the integrated circuit".

#### 3. MOSFET

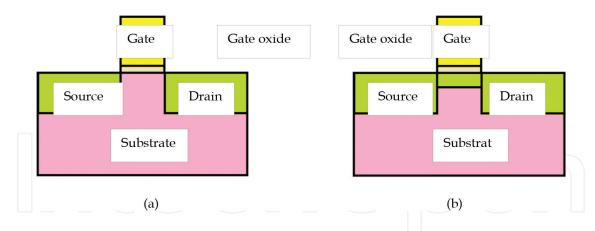

The Metal Oxide Semiconductor Field Effect Transistor or MOSFET acts as an electronic switch or amplifier in circuitries. There are two types of MOSFETs, namely the enhancement-type MOSFET (E-MOSFET) and the depletion-type MOSFET (D-MOSFET). **Figure 2** depicts the basic structure for both types of MOSFETs. As can be observed from the figure, both devices are similar to each other. They comprise four terminals: the drain, source, gate and substrate terminals. The drain and source terminals of the E-MOSFET are separated apart from each other. Unlike the E-MOSFET, however, a channel connecting the two terminals is physically implanted in the D-MOSFET.

Figure 2. The cross sections of an (a) enhancement mode and a (b) depletion mode MOSFET.

When no voltage is applied to the gate terminal, the E- and D-MOSFETs act like an open and a closed switch, respectively. This is to say that voltage is to be applied to the D-MOSFET in order to have it switched off. Since the E-MOSFET does not require this additional voltage to be switched off, it consumes less power and is popularly used in the IC industries. Hence, the term MOSFET is generally used to refer to the E-MOSFET.

Basically, the device is composed of three layers: a polysilicon layer (i.e. the gate terminal), an oxide layer (i.e. the gate oxide) and a single crystal semiconductor layer (i.e. the substrate). In the early days, the gate terminal was made of aluminum. Indeed, the term MOSFET is coined from these three layers of materials and the fact that it relies on electric field to dictate its switching function. In mid 1970s, however, the gate material was replaced with polysilicon. The high temperature stability of the polysilicon gate is used as a mask to form the self-aligned source and drain terminals via ion implantation, rendering higher accuracy for the formation of these two terminals. Although the gate today is no longer made of aluminum, the term MOSFET has been so widely accepted that it stays until today [2].

#### 3.1. NMOS and PMOS transistors

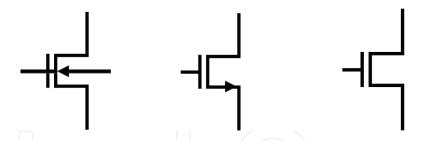

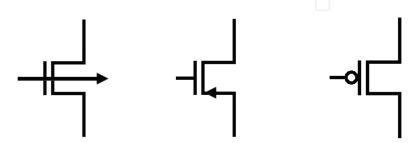

A MOSFET can be classified into two types, depending on the dopant at the drain, source and substrate regions. When the drain and source terminals are heavily doped with donator ions, such as phosphorous and arsenic, while the substrate is a p-type semiconductor material, the device is known as a negative channel MOSFET or NMOS transistor. On the other hand, when the two terminals are heavily doped with acceptor ions such as boron, and the substrate is an n-type, the device is known as a positive channel MOSFET or PMOS transistor. **Figures 3** and **4** show the symbols of the NMOS and PMOS transistors, respectively. Although the figures show that various symbols have been used to represent the transistors, the third from the left in both figures have been more popularly used in the IC industries.

When voltage  $V_{DS}$  is applied to the drain and source terminals, it requires a conducting channel between the two terminals to form a close circuit. Voltage  $V_{GS}$  connected between the gate and source terminals control the formation of this channel. It therefore acts like a switch of the transistor. When a positive  $V_{GS}$  greater or equivalent to the threshold voltage  $V_{GS(th)}$  is applied to an NMOS transistor, the positive carriers (i.e. holes) accumulated at the gate terminal would

Figure 3. Different symbols for NMOS transistors.

be sufficiently strong to repel holes and attract electrons to form a channel at the substrate-oxide interface. The channel connects both source and drain terminals, forming a closed circuit for electrons to flow. Like the case of the NMOS transistor, a voltage applied at the gate to source terminal is required to form a channel in the PMOS transistor. However, unlike the NMOS transistor, voltage  $V_{\rm GS}$  of the PMOS transistor is negative. This allows negative carriers (i.e. electrons) to be accumulated at the gate terminal. When the magnitude of  $V_{\rm GS}$  exceeds its threshold, electrons at the oxide-substrate interface would be repelled and holes would be attracted to the interface. A conducting channel made of positive carriers is thus formed between the source and drain terminals.

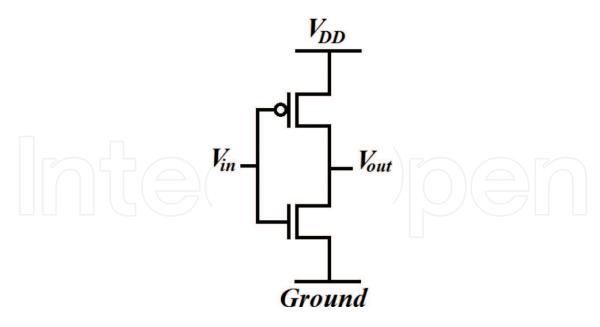

#### 3.2. CMOS devices

Although NMOS and PMOS transistors have been used independently in electronic circuits, they have their own limitations. A PMOS transistor is unable to produce an exact zero output voltage when a logic 0 is required, whereas an NMOS transistor fails to give a full  $V_{DD}$  voltage at the output when a logic 1 is required. Failure to give a full swing from 0 to  $V_{DD}$  has resulted in power loss in circuitries. In order to solve this problem, both NMOS and PMOS transistors are integrated together in IC designs. By connecting the source of the PMOS transistor to the  $V_{DD}$  input voltage and that of the NMOS transistor to the ground, output  $V_{DS}$  can be completely pulled up to  $V_{DD}$  and pulled down to ground when a logic 1 and 0 is to be generated, respectively. Because of this reason, the part of the circuit that is made from PMOS transistors is known as the pull-up network, whereas the part that comprises NMOS transistors is known as the pull-down network. Since these two transistors complement each other, a circuit which is designed from a combination of both is therefore known as a Complementary MOS circuit or CMOS circuit, in short. Each time a CMOS circuit operates, only either of the pull-up or

Figure 4. Different symbols for PMOS transistors.

Figure 5. Schematic of a CMOS inverter.

pull-down network conducts. Take for instance the operation of a CMOS inverter, such as that shown in **Figure 5**. When a logic 1 is to be generated at the output, the PMOS transistor acts like closed switch and the NMOS transistor acts like an open switch. Similarly, when a logic 0 is to be generated, the PMOS and NMOS transistors act like an open and a closed switch, respectively. This allows almost zero power loss during steady states of the circuit.

#### **Author details**

Kim Ho Yeap\* and Humaira Nisar

\*Address all correspondence to: yeapkimho@gmail.com

Tunku Abdul Rahman University, Jalan Universiti, Kampar, Perak, Malaysia

#### References

- [1] Ahmad I, Ho YK, Majlis BY. Fabrication and characterization of a 0.14 μm CMOS device using ATHENA and ATLAS simulators. International Scientific Journal of Semiconductor, Physics, Quantum Electronics, and Optoelectronics. 2006;9:40-44. DOI: https://doi.org/10.15407/spqeo

- [2] Yeap KH, Nisar H. Very Large Scale Integration. InTech: Croatia; 2018

- [3] Lukasiak L, Jakubowski A. History of semiconductors. Journal of Telecommunications and Information Technology. 2010;1:3-9. DOI: 10.1088/0031-9120/40/5/002

## IntechOpen

# IntechOpen