We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

186,000

200M

Our authors are among the

TOP 1% most cited scientists

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

# Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

# New Processes and Technologies to Reduce the Low-Frequency Noise of Digital and Analog Circuits

Philippe Gaubert and Akinobu Teramoto

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/64630

#### Abstract

The chapter is intended to provide the reader with means to reduce low-frequency noise in Metal-Oxide-Semiconductor Field-Effect-Transistor (MOSFET). It is demonstrated that low-resistivity source and drain electrodes can greatly lower the low-frequency noise level by suppressing their contribution to the total noise. Furthermore, new plasma processes having the advantages to work at low electron temperature can achieve a further reduction, thanks to the fabrication of a better gate oxide and to a reduction of damages generally induced by conventional plasma processes. Reducing the impact of the traps on the carrier flowing inside the channel by burying the channel can also achieve a reduction of the noise level, but unfortunately at the cost of a degradation of the electrical performances. Finally, the noise analysis of the lowfrequency noise in accumulation-mode MOSFETs showed that these newly developed devices have a lower noise level than conventional structures, which, in addition to their superiority in term of electrical performances, establishes them as a serious platform for the next Complementary Metal-Oxide-Semiconductor Field-Effect-Transistor (CMOS) technology.

**Keywords:** low-frequency noise, radical oxidation, silicide, series resistances, accumulation-mode, MOSFET, buried-channel, fabrication process

# 1. Introduction

Since the dawn of electronics more than 50 years ago, manufacturers have been providing customers with faster and smaller chips by fabricating increasingly better devices and improving processes. The main strategy adopted has been to shrink the gate size of the MOSFETs to improve chip performances, especially speed. Since the signal-to-noise ratio was large enough, the noise

open science | open minds

© 2016 The Author(s). Licensee InTech. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited. was not an issue and its reduction dragged very little effort among the scientific community. After a steady working frequency doubling every year, the recent downscaling of the dimension has led to high stress and increased variability and, in turn, stagnation of performances of chips. There is no doubt that the increased noise is to blame for that standstill, even if other problems such as the doping concentration could be implicated as well. Nevertheless, the distinction between noise and signal has become critical and the noise issue must be tackled. A suppressed noise level should pave the way to once again lower biases leading to less heat, better reliability, and better performances.

Noise is a fluctuation of a quantity that shifts back and forth with uncertainty. In electronics, it is generally noted as a fluctuation of the voltage or current around its mean value and is ascribed to stochastic events which find their origin at a microscopic level trough the discrete nature of the transport or the Brownian nature of the carrier. There are several types of noises such as thermal noise, shot noise, generation-recombination noise, inter-band noise, and low-frequency noise. They are generally classified upon their origin. Among these, the thermal noise and low-frequency noise are of paramount importance in MOSFETs, with the latter one being of most concern since its origin is still in debate and that its evaluation for a given technology is made extremely difficult. Even if the low-frequency noise has been a limiting factor of performances for analog circuits for several years, it has recently become as well an issue for digital ones. Indeed, even though its limitation applies in the low range of frequency, it is up-converted into phase noise leading to time domain instabilities and therefore problems in the high-frequency range. Its reduction is therefore mandatory not only for analog but also for digital circuits.

In Section 1, the theory of the low-frequency noise in MOSFETs is briefly reviewed. While Sections 2 and 3 present new technologies to suppress it by the means of, respectively, silicide and damage free processes, Sections 4 and 5 introduce improved MOSFETs. Thus, the results regarding buried-channel and accumulation-mode MOSFETs are reported, respectively, in Sections 4 and 5.

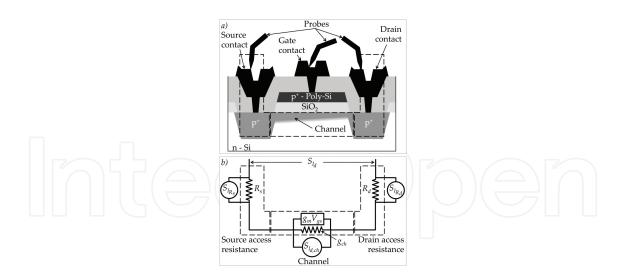

# 2. Low-frequency noise in MOSFETs

The MOSFET is a complex device composed of purely resistive parts surrounding the channel whose resistance is controlled by the bias applied at the gate electrode. It is therefore natural that the noise generated inside each region is propagating up to the source and the drain electrodes. However, the noise stemming from the channel is generally the most dominant one, even though the one coming from the surrounding areas can play an important role and can even take over as the main noise source [1]. **Figure 1(a)** shows a schematic of a MOSFET structure while **Figure 1(b)** represents its equivalent noise circuit. The source access resistance, the drain access resistance, and the channel are the three main regions the noise is coming from and the total measured noise  $S_{Id}$  at a given frequency can be written [2].

New Processes and Technologies to Reduce the Low-Frequency Noise of Digital and Analog Circuits 5 http://dx.doi.org/10.5772/64630

Figure 1. Representation of (a) MOSFET and (b) its equivalent circuit noise.

$$S_{I_{d}}(f) = \frac{S_{I_{d,ch}}(f)}{\left[1 + g_{m}R_{s} + g_{ch}(R_{s} + R_{d})\right]^{2}} + \frac{g_{m}^{2}R_{s}^{2}S_{I_{R_{s}}}(f) + g_{ch}^{2}\left[R_{s}^{2}S_{I_{R_{s}}}(f) + R_{d}^{2}S_{I_{R_{d}}}(f)\right]}{\left[1 + g_{m}R_{s} + g_{ch}(R_{s} + R_{d})\right]^{2}}$$

(1)

where  $S_{Id,ch}$ ,  $S_{IRs}$ , and  $S_{IRd}$  are the noises generated, respectively, inside the channel, the source  $R_s$  and drain  $R_d$  access resistances.  $G_m$  and  $g_{ch}$  are, respectively, the transconductance and conductance of the channel. The left-hand side term is the contribution coming from the channel while the right-hand side one is the contribution coming from the access resistances.

It is worth noticing that  $S_{Id}$  can become equal to  $S_{Id,ch}$  meaning that the measured noise will be the noise of the channel, whereas even if the series resistances are the main noise source, it is their contribution that will be measured and not their pure noise. The noise in a resistive material such as the access resistances of a MOSFET is either thermal noise or 1/f noise at low frequencies [3]. This 1/f noise is known to originate from the fluctuations of the fundamental mobility and it follows the Hooge's empirical formulae [3]:

$$\frac{S_I(f)}{I^2} = \frac{\alpha_H}{fN},\tag{2}$$

which represents the normalized noise of the current *I* while *N* is the number of carriers.  $\alpha_{\rm H}$  is the Hooge parameter suggested to be constant and to reflect the quality of the crystal. After several decades of controversies between the Hooge theory and the Mc. Whorter one [4], the latter explaining the noise in terms of fluctuation of the carrier number, Mikoshiba [5] devel-

oped a new theory able to gather all data into a single model to explain the noise stemming from the channel.

His theory has been confirmed afterward by several researchers and is now well accepted among the scientific community. Within this theory, the noise is given by [6]

$$\frac{S_{\mathrm{I}_{d}}\left(f\right)}{I_{d}^{2}} = \frac{g_{m}^{2}}{I_{d}^{2}} \left(1 \pm \alpha \mu_{\mathrm{eff}} C_{\mathrm{ox}} \frac{I_{d}}{g_{m}}\right)^{2} S_{V_{fb}}\left(f\right),\tag{3}$$

where  $C_{\text{ox}}$  is the gate oxide capacitance,  $g_m$  is the transconductance, and  $\mu_{\text{eff}}$  is the effective mobility of the carriers flowing inside the channel. This theory is known as the insulator and induced mobility fluctuations, and is ascribing the origin of the noise to the traps located inside the gate insulator near the interface. The constant dynamic capture and release of carriers from and to traps generate interfacial insulator charge variation and, in turn, fluctuation of the insulator charge. These fluctuations are equivalently generating flat band variations. These fluctuations are summarized on the left-hand side term in Eq. (3) and are proportional to the flat band voltage fluctuations  $S_{\text{Vfb}}$ , expressed as [6]

$$S_{V_{fb}}\left(f\right) = \frac{\lambda k_{\rm B} T q^2 N_t}{W L C_{\rm ox}^2 f},\tag{4}$$

with  $k_{\rm B}$  being the Boltzmann constant, q the electron charge, T the temperature, and  $\lambda$  the tunnel attenuation length of the traps in the insulator equal to 0.1 nm for  $SiO_2$ . N<sub>t</sub> is the interface trap density. In addition to the variation of the insulator charge, the capture and release mechanism is locally affecting the surface potential at the interface, resulting in a Coulomb interaction between the locally deformed potential surface and the carriers flowing inside the channel. The localized scattering rate will vary and will induce fluctuations of the mobility. These fluctuations are ascribed to the right-hand side term in Eq. (3) and are related to the fluctuations of the insulator charge through the Coulomb parameter  $\alpha$ , which measures the strength between both quantities. With nowadays miniaturization of the gate of the MOSFETs, two kinds of noises are at stake, although they are both explained in the frame of the previous theory. Indeed, it is obvious that in the case of very small gate size involving a very limited number of carriers, the removal or introduction of a single free carrier scared within the total number of free carriers involved in the conduction will have a tremendous impact on the current, making it jump between two or several levels like randomly disposed crenels. This type of noise is called random telegraph noise and is commonly an issue for sensors, especially optical ones [7]. However, when the number of traps is more significant and for a specific distribution of their energy within the bandgap, the resulting noise is commonly called 1/f or even Flicker noise and it follows a distribution, proportional to the inverse of the frequency when plotted as a function of the frequency [1]. This noise is an issue for analog circuits, and even for some digital ones, and will even impact at high frequency due to its conversion into

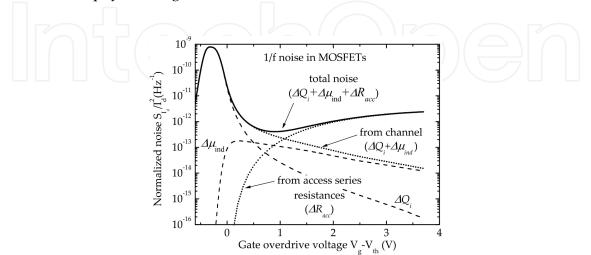

phase noise. Finally, the noise in MOSFETs can be summarized as depicted in **Figure 2**. The noise measured at the electrode of a MOSFET is the sum of three terms: the fluctuation of the insulator charge, induced fluctuation of the mobility, and the contribution coming from the access resistances. It is worth mentioning that there is a fourth term, the cross-correlation term between the fluctuation of the insulator charge and the induced mobility one even though it does not have a physical origin.

Figure 2. Normalized noise in a MOSFET. The several contributions of each noise sources have been reported with the non-full lines.

# 3. Source and drain contacts

When it comes to low-frequency noise, the contribution stemming from the source and drain access series resistances is generally overlooked. This negligence can have tremendous impact on the noise analysis especially at high gate voltage where their contribution will mostly take over as the dominant noise.

As a matter of fact, this is not the noise generated inside the source and drain access series resistances, which is at stake but their contribution. Rather than reducing the noise sources, reducing their contribution is more efficient and easier. Indeed, the reduction of the resistance of the source and drain access contacts does not only mean a better drivability and a better transconductance but can guarantee a reduction of the propagation of the noise generated by the noise sources inside the contacts and, in turn, a reduction of the contribution of the source and drain contact noise to the total measured noise [8]. The performance improvement of CMOS has become of paramount importance with scaled dimension. Much effort is being made to increase the carrier mobility by several means such as strained technology [9], different silicon orientation [10], or even different semiconductor [11]. The reduction of the source and drain electrode series resistances is another means to improve the drivability and silicide has already been used for such purposes. Nitride alloy silicide is widely used to lower the Schottky barrier height to either n<sup>+</sup> or p<sup>+</sup> silicon down with contact resistance as low as  $2 \times 10^{-9} \Omega$  cm<sup>2</sup> in

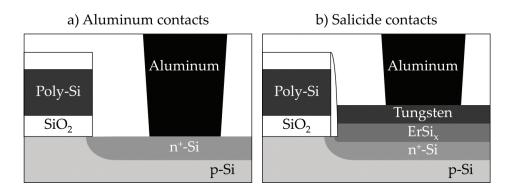

the best case [12]. A new structure [13] and new processes [14] have been developed in order to further lower down the series resistances. Instead of using the same silicide for both p<sup>-</sup> and n-MOSFETs, erbium has been selected to perfectly fit the requirement of n-MOSFETs and palladium for the p-MOSFETs. Additionally, tungsten metal stack above the thin silicide layer was introduced to reduce the sheet resistance and protect erbium from being oxidized. In order to confirm the above statement, two kinds of MOSFETs have been fabricated following the very same process flow, except during the source and drain contact fabrication stage. The source and drain contacts of the reference transistors have been fabricated with aluminum (Al), while erbium silicide associated with tungsten (ErSi<sub>2</sub>/W) has been used for the second set of transistors. The respective structures have been represented in Figure 3(a) and (b). While both wafers followed the same process flow until the contact lithography step, the ErSi<sub>x</sub>/W wafer followed an advanced process entirely developed at New Industry Creation Hatchery Center (NICHe). In this advanced process, the wafer has been loaded in an N<sub>2</sub> sealed cleaning chamber after a total room temperature five-step cleaning, which has been followed by the dipping of the cleaned wafer in O<sub>3</sub> dissolved ultra pure water in order to form a chemical oxide at the silicon surface. The removal of the chemical oxide has been carried out by diluted HF solution and the wafer has been then transferred in clustered sputter equipment, still in N<sub>2</sub> ambient, where the formation of a thin film of erbium followed by the deposition of a tungsten capping layer has been done by Radio Frequency (RF) sputtering.

**Figure 3.** Schematic of the structure of (a) reference contacts fabricated with aluminum (Al) and (b) salicide contacts fabricated with erbium silicide ( $\text{ErSi}_x$ ) and tungsten (W) layer. Copyright 2011 The Japan Society of Applied Physics [8].

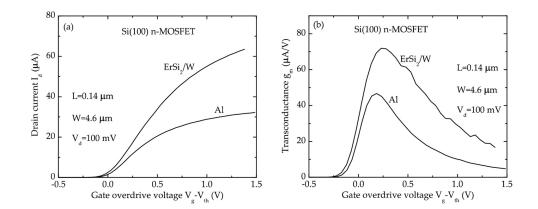

The wafer has been then loaded in lamp annealing chamber to finally form  $\text{ErSi}_x$ . The wafer has been then brought back to the conventional process flow to finally form aluminum contacts. Electric characterization has been carried out and the main results are summarized in **Figure 4(a)** and **(b)**. As expected, the drivability has been improved by a factor of 2 on account of silicide contacts [8]. Furthermore, the maximum of the transconductance also increased and confirms the interest of low-resistivity source and drain contacts to enhance performances of electronic circuits. Noise measurements have been performed in the linear regime and for *f* = 10 Hz. The result is presented in **Figure 5**. When compared with the noise level of the reference transistor, the noise level of the transistor featuring  $\text{ErSi}_x/W$  contacts is greatly reduced for positive gate overdrive voltages while it remains equivalent for lower values. The same noise

level below 0 V is explained by the fact that within this range of measurement the channel is exclusively contributing to the total noise and by the fact that both devices have indeed almost the same channel, since they followed the same process flow with regard to the fabrication of the gate stack. The noise modeling has been carried out and is reported with the lines in **Figure 5**. The modeling reveals that from 0 V the noise from the reference device moves away from the noise stemming from the channel. The contribution of the series resistances to the total noise is increasing and is ultimately taking over as the main contribution. However, the noise of the device featuring ErSi<sub>2</sub>/W contacts is following the curve depicting the noise stemming from the channel and starts to slightly move away at high voltages. The impact of the series resistances on the noise is barely visible. The use of low-resistivity contacts allows a drastic reduction in the contribution of the series resistances to the total noise and let the channel be the sole source of noise over the entire measurement range [8]. About 10 times reduction of the access resistance has led to 100 times reduction of the noise level.

**Figure 4.** (a) Drain current and (b) transconductance versus gate overdrive voltage for n-MOSFETs featuring Al and ErSi<sub>2</sub>/W contacts. Copyright 2011 The Japan Society of Applied Physics [8].

**Figure 5.** Normalized noise of n-MOSFETs with contacts fabricated with either aluminum(Al) or erbium silicide/tung-sten(ErSi<sub>2</sub>/W). (W) layer. Copyright 2011 The Japan Society of Applied Physics [8].

# 4. Radical oxidation

The gate stack, especially, the gate insulator, is the most critical part of the MOSFET, mainly because of the defects that can appear during the fabrication and its tremendous impact on the device performance [15]. It is absolutely true these days that the need of always-faster devices and smaller chips also promote the appearance of undesirable effects such as increase of variability and random telegraph noise. Thermal oxidation has been the way, since the establishment of the MOSFET, to fabricate the gate insulator and while the generated SiO<sub>2</sub> was at the beginning of poor quality, leading to high *S* parameters, the process has greatly evolved since and the growth of quality oxide can be achieved now [15]. Unfortunately, the dimension of nowadays MOSFETs has reached a threshold where *S* parameter and  $V_{\rm th}$  variability are a major issue, as well as, noise level prevision [16].

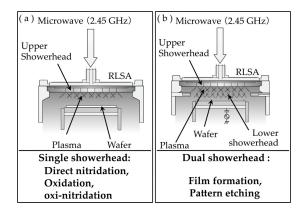

**Figure 6.** Diagrams of (a) single shower plate and (b) double shower plate equipment based radicals formed by the low electron temperature microwave high-density plasma.

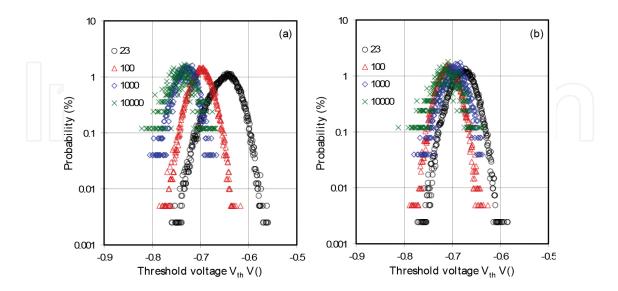

Thermal oxidation, from its intrinsic chemical reaction, cannot be optimized anymore and will always promote the formation of damage (either inside the gate stack or cap layers) and will partly invalidate the flattening process and, in turn, deteriorate the surface roughness of the wafer. Thus, new oxidation processes have been developed to avoid these issues. They are all based on radical oxidation rather than chemical reaction to form  $SiO_2$  [17]. The specificity of the damage-free very low electron temperature microwave exited high-density plasma is, as represented in Figure 6, that it can be employed for oxidation at low temperature, chemical vapor deposition, or even reactive ion etching. Very high quality gate insulator and reduced damages generally occurring during the etching and the fabrication of interconnect can be achieved thanks to this advanced process as shown in Figure 7 [15, 18, 19]. Contrary to the thermal oxidation, the radical oxidation has an oxidation rate that is almost regardless of the orientation of the silicon crystal on which the oxide is grown [20]. Additionally, the radical oxidation does not only help reduce the interface trap density but also help preserve and even improve the flatness of the Si/SiO<sub>2</sub> interface. Two sets of p-MOSFETs have been fabricated in our clean room. They followed almost the same process flow; however, they differed in such a way that the first set featuring a radically grown oxide has been processed exclusively with

advanced plasma equipment, while the second set has been processed using conventional processes, among which the thermal oxidation process.

**Figure 7.**  $V_{\text{th}}$  distributions of p-MOSFETs fabricated by applying (a) conventional plasma processes and (b) radial line slot antenna plasma processes plotted for antenna ratio of 23, 100, 1000, and 10,000.

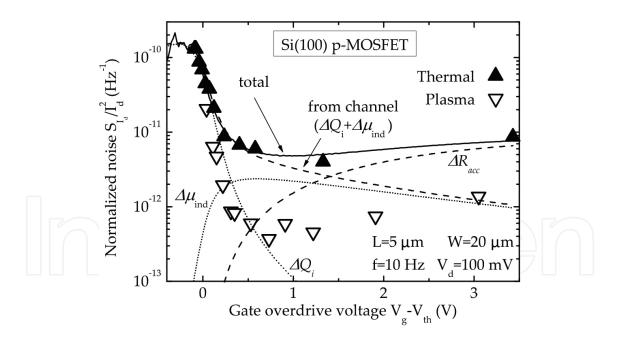

**Figure 8.** Normalized noise of p-MOSFETs with a gate oxide fabricated by either thermal or plasma oxidation as a function of the gate overdrive voltage. The modeling, reported with the lines, refers exclusively to the transistor with a gate oxide thermally grown. Copyright 2011 The Japan Society of Applied Physics [8].

Noise measurements have been performed in the linear and saturated region and for different gate sizes. The noise analysis has been carried out at 10 Hz. Results are presented in **Figure 8**, and they clearly indicate that the p-MOSFET with a gate oxide fabricated by radical oxidation

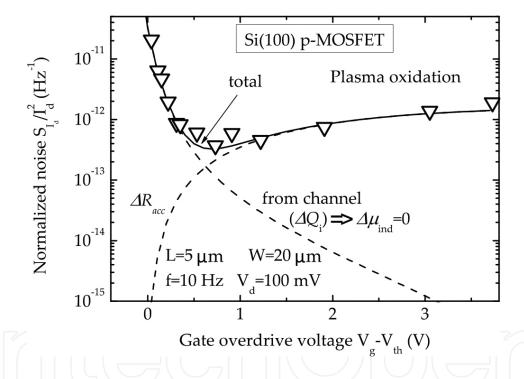

has a lower noise level than when the thermal oxidation process is used used, with a maximal reduction of over a decade. As expected, the noise stemming from series resistances and the noise from the channel are both contributing to the total noise, with the latter one being ascribed to the insulator charge and induced mobility fluctuations. In order to understand the origin of the noise reduction, the modeling of the p-MOSFETs, featuring a gate oxide, fabricated by radical oxidation has been carried out. The result is reported in **Figure 9** and it revealed an unexpected behavior, i.e., no induced mobility fluctuations. The contribution of the series resistances added to the sole insulator charge fluctuations has been enough to model the total noise. Even though the trapping/release mechanism at the origin of the 1/*f* noise induces fluctuation of the mobility, these fluctuations. The interface trap density has been extracted for both sets of devices and revealed a three-time reduction in favor of the transistors fabricated using plasma processes with  $N_d = 2 \times 10^{16}$  cm<sup>-3</sup> eV<sup>-1</sup>, testifying the high integrity of the oxide when fabricated by radical oxidation.

Figure 9. Normalized noise of p-MOSFETs with a gate oxide fabricated by plasma oxidation as a function of the gate overdrive voltage. Copyright 2011 The Japan Society of Applied Physics [8].

## 5. Buried-channel MOSFETs

#### 5.1. Structure of buried-channel MOSFET

The low-frequency noise, such as 1/*f* noise and random telegraph noise, is basically caused by the defects at the gate insulator and silicon interface in MOSFETs. To reduce the low-frequency

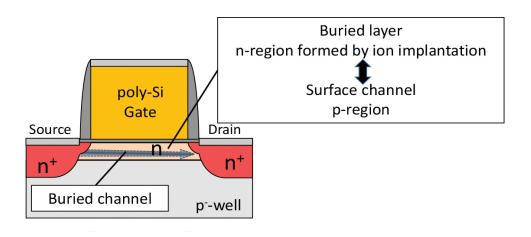

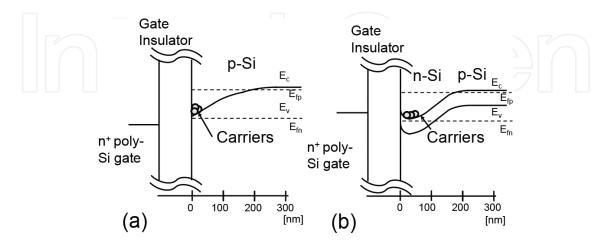

noise, the number of defects or the influence of the defects has to be reduced. Here, the channel of the buried-channel MOSFETs is separated from the gate insulator/Si interface, and then the carriers in the channel are hard to be influenced by the defects at the interface. Usually, the buried-channel MOSFETs are characterized as high mobility but weak short channel Field-Effect-Transistor (FET) [21–23] because the carriers flow through the bulk. In this case, the separated channel location of buried-channel MOSFETs is very important for reducing the low-frequency noise. **Figure 10** shows the schematic illustration of the buried-channel n-MOSFET. The buried layer was formed by the ion implantation at the  $V_{\rm th}$  adjustment process [24, 25]. **Figure 11** shows the band diagram of the conventional surface channel (a) and the buried-channel MOSFETs (b), respectively [25]. The buried layer depth was set as 170 nm from the SiO<sub>2</sub>/Si interface, and the channel was appeared at around 30 nm from the SiO<sub>2</sub>/Si interface at the bias conditions of back bias ( $V_{\rm BS}$ ) =1.5 V and drain current ( $I_{\rm DS}$ ) =100 nA for a gate length (L) of 0.22 µm and a gate width (W) of 0.28 µm MOSFETs.

Figure 10. Schematic illustration of the buried-channel MOSFET.

**Figure 11.** Diagrams of surface channel (a) and buried-channel MOSFETs. The bias condition was set at  $V_{BS}$  = 1.5 V and  $I_{DS}$  = 100 nA.

#### 5.2. Low-frequency noise characteristics

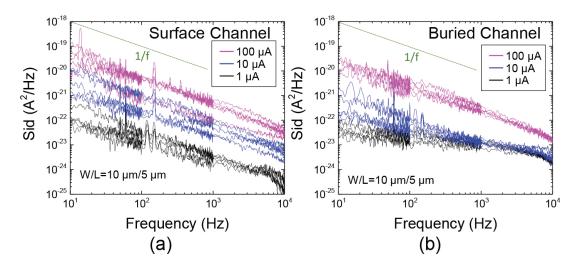

**Figure 12** shows the 1/f noise characteristics for the surface channel and buried-channel MOSFETs. Five samples were measured for each MOSFET. The size (*W/L*) of MOSFETs was 10  $\mu$ m/5  $\mu$ m and bias conditions were set as  $V_{DS} = 1.5$  V,  $V_{BS} = 0$  V,  $I_{DS} = 1$ , 10, and 100  $\mu$ A.  $S_{Id}$  increases as the drain current increasing for both MOSFETs. The noise power  $S_{Id}$  of the surface channel MOSFETs is proportional to 1/f. In contrast,  $S_{Id}$  of the buried-channel MOSFETs for the low  $I_d$  cases is not proportional to 1/f, because the noise level was smaller than the floor noise of the measurement system. For the same drain current  $I_d$ , the noise power of the buried-channel MOSFETs are less than that of the surface channel MOSFETs, especially their differences are observed for the low drain current cases. In this experiment, the gate voltage controlled the drain current. When the gate voltage increases, the distance between the channel and the interface decreases, and then it influences the defects. This indicates that the noise reduction of buried channel is very effective for the low gate voltage conditions.

Figure 12. 1/f noise characteristics of (a) surface channel and (b) buried-channel MOSFETs.

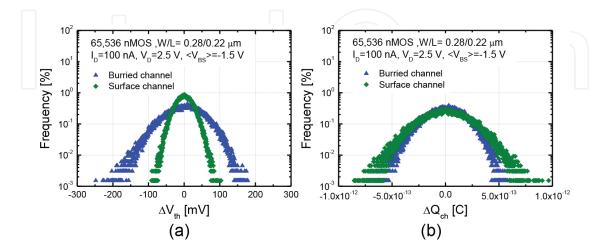

## 5.3. V<sub>th</sub> variability

In the previous section, it is described that the noise can be reduced by introducing the buriedchannel MOSFETs because the channel is separated from the SiO<sub>2</sub>/Si interface. However, this means the gate capacitance becomes lower compared to the surface channel MOSFETs. Then, the  $V_{th}$  control becomes difficult compared with the surface channel. **Figure 13** shows distributions of (a)  $V_{th}$  and (b) the channel charge ( $Q_{ch}$ ) with 65536 MOSFETs for the buriedand surface channel MOSFETs [24]. These distributions are measured by the array test circuit, which can measure the  $V_{th}$  variation and the random telegraph signal for many MOSFETs (>1 million MOSFETs) during very short time (<1 s) [26–29]. The horizontal axis of both the graphs shows the difference values between the average values of all MOSFETs (65536 MOSFETs). The  $V_{th}$  variability of the buried-channel MOSFET is larger than that the surface channel MOSFETs as shown in **Figure 13(a)**. It is considered that the gate capacitance of buried channel is smaller than that of the surface channel. Then, the horizontal axis is converted from  $V_{th}$  to  $Q_{ch}$  by using the gate-channel capacitance. Almost the same distributions are observed, and then the variability is caused by the small capacitance between the gate and the channel. Moreover, it is noticed that the noise increases by the excess capacitance decrease with the other transistor characteristics degradation, such as short channel effect and subthreshold swing degradation [22, 30].

Figure 13. Distributions of (a) V<sub>th</sub> and (b) Q<sub>ch</sub> with 65536 MOSFETs for the buried- and surface channel MOSFETs.

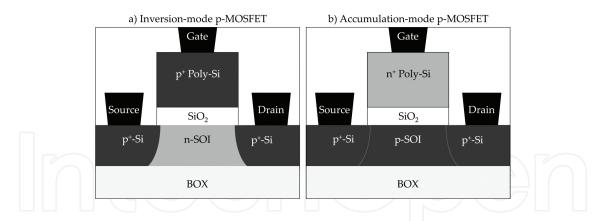

## 6. Accumulation-mode MOSFETs

The separation between the interface and the channel is effective in reducing the noise in buried-channel MOSFETs; however, the controllability of  $V_{\rm th}$  is worse than conventional MOSFETs because the gate capacitance is reduced. Then the introduction of Silicon-on-Insulator (SOI) wafer and a new structure can solve this issue [31, 32]. The so-called accumulation-mode MOSFET has been developed keeping this in mind. As depicted in Figure 14, the accumulation-mode MOSFETs differ from MOSFETs in such a way that the type of the SOI layer is the same as that of the contact. Additionally, the type of polysilicon must also be adjusted as required. Although the working of the conventional inversion-mode MOSFETs is based on the generation of an inversion layer made of the minority carrier, the accumulationmode one is making use of an accumulation layer composed of majority carrier. Actually, the accumulation-mode MOSFET without bias is at first on the off-state since the SOI layer is completely depleted. When a bias is applied at the gate, a thin conductive layer of majority carrier is first generated at the back interface between the Buried Oxide (BOX) and the SOI. Then accumulation-mode MOSFETs become on the on-state. A current at the back interface flows from the source to the drain. A further increase in the bias makes this layer disappear and makes a short portion of the originally depleted SOI layer become neutral. A bulk current is generated on the BOX side. This current continues to increase with the expansion of the neutral region (due to the shrinking of the depleted region) inside the SOI until the bias applied at the gate reaches the flat-band voltage.

Figure 14. Schematic representation of (a) inversion-mode and (b) accumulation-mode p-MOSFETs.

Figure 15. Drivability of accumulation- and inversion-mode p-MOSFETs.

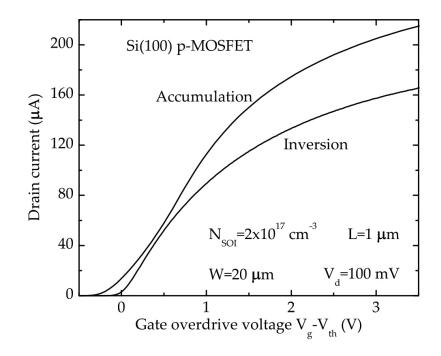

The current generated inside the accumulation layer then adds to the bulk current. Therefore, in addition to, among other things, having an improved reliability [33] and being immune to radiation effects [34], they also have a better drivability than inversion-mode MOSFETs since the total current is the sum of those generated inside the SOI and the accumulation layer [35]. When the bulk current has reached its maximum, corresponding to the SOI completely neutral, the majority carrier accumulates at the front interface between the gate insulator and the SOI. Accumulation-mode fully depleted SOI MOSFETs have been fabricated on Si(100) surface to investigate the noise characteristics. The SOI layer impurity has been adjusted by ion implantation to  $2 \times 10^{17}$  cm<sup>-3</sup>. The thickness of the SOI layer has been reduced down to 50 nm. In order to avoid the increase of noise due to the defects at the front interface and the impact of the surface roughness of the interface, the radical oxidation [17] added to the five-step-cleaning

process [20] has been repeated four times until reaching a flattened interface with a roughness  $R_a$  of 0.08 nm. A 7-nm gate oxide has been formed by radical oxidation using a low electron temperature microwave high-density plasma process at 400°C. As expected and as shown in **Figure 15**, the accumulation-mode MOSFETs feature a better drivability than those of the inversion-mode MOSFETs. The better drivability does not only owe to two distinctive currents but also from the higher carrier mobility thanks to a lower transversal electric field at the front interface [35].

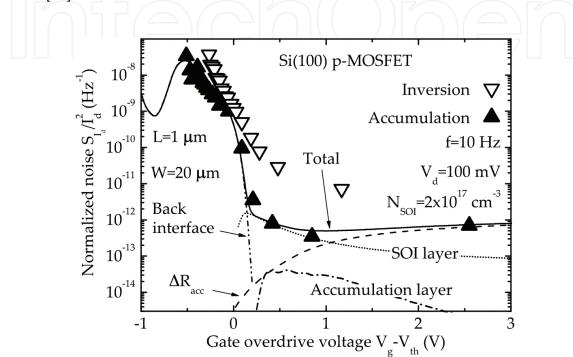

**Figure 16.** Normalized noise of accumulation- and inversion-mode p-MOSFETs. Lines refer to the modeling of the noise of the sole accumulation-mode device and represent the noise generated by each region.

The noise of the inversion- and accumulation-mode MOSFETs has been reported in **Figure 16**. Even though their noise level is similar at low gate overdrive voltage, the superiority of the accumulation-mode MOSFET over the inversion mode one becomes clear for voltage over 0 V. A gap of more than 1 decade is achieved at the best. While the noise of the inversion-mode MOSFET can be ascribed to the interface traps [6] and series resistances at high bias [3], the origin of the noise for the accumulation-mode one must be investigated with care. Indeed, as discussed earlier, three conduction mechanisms generate the current and are therefore generating their own noise. The modeling of each noise and finally the total modeled noise have been reported with lines in **Figure 16**. The noise stemming from the front and back interfaces is originating from the interface traps [5], like for the inversion-mode MOSFET while the noise for the accumulation to the inversion-mode MOSFET while the noise for the accumulation mechanisms generate the current and are therefore generating their own noise. The modeling of each noise and finally the total modeled noise have been reported with lines in **Figure 16**. The noise stemming from the front and back interfaces is originating from the interface traps [5], like for the inversion-mode MOSFET while the noise from the SOI layer and access resistances is explained in terms of fundamental fluctuations of the mobility of the Hooge model [3]. Contrary to the inversion-mode MOSFET, the front interface does not contribute to the total noise. The lower noise can be attributed to a change in the origin of the noise stemming from the channel, with the SOI region becoming the main contributor to the noise with regard to the channel and a significant shift toward the

high gate voltage to turn the accumulation layer on. It is worth mentioning that the advantage of the accumulation-mode MOSFET is effective for high doping concentration; otherwise, the accumulation layer will act like an inversion one [36] since it implies no contribution from either the back interface or the SOI layer to the total current.

# 7. Conclusion

In this chapter, we reviewed several ways to suppress the low-frequency noise of MOSFETs and, in turn, the noise of analog and digital circuits. One of the most underrated approaches is to optimize the contacts and interconnects by the means of low-resistive materials, so that their contribution to the total noise can be drastically reduced. It has also been shown that a great deal must be paid to the fabrication processes. Indeed, the use of processes demonstrating very low damage generation at all the stages of fabrication can lead to MOSFETs with better performances and especially reduced noise level due to a reduction of induced defects located at the gate stack and its surroundings. Additionally, these low-defect processes based on the damage-free, low-temperature, high-density plasma technology achieved a further reduction by means of the disappearance of one component of the low-frequency noise, the induced mobility fluctuations one, bringing the noise of MOSFETs to the sole fluctuations of the insulator charges. Focusing on a different electronic structure can also achieve low-noise MOSFETs. For example, minimizing the interaction carrier-traps by moving away the channel - so that fewer traps are activated and less variations of the insulator charge are generated can achieve a reduced noise. Unfortunately, this reduction is obtained at the cost of a degradation of the electrical performances. So, the most promising structure to suppress noise is in the form of the accumulation-mode MOSFETs. Indeed, in addition to offer reduced lowfrequency noise when compared to conventional MOSFETs, their electrical performances are greatly improved. These devices obviously feature various assets, which should consequently pave the road for a new era of very low noise and high-performance MOSFETs and bring microelectronic manufacturers back to the realization of highly performances and high-speed analog and digital circuits.

# Author details

Philippe Gaubert<sup>1\*</sup> and Akinobu Teramoto<sup>2</sup>

- \*Address all correspondence to: gaubert@m.tohoku.ac.jp

- 1 Graduate School of Engineering, Tohoku University, Sendai, Japan

- 2 New Industry Creation Hatchery Center, Tohoku University, Sendai, Japan

# References

- [1] Gaubert P, Teramoto A, Cheng W, Ohmi T. Relation Between the Mobility, 1/f Noise, and Channel Direction in MOSFETs Fabricated on (100) and (110) Silicon-Oriented Wafers. IEEE Trans Electron Devices. 2010;57(7):1597–607.

- [2] Vandamme EP, Vandamme LKJ, Claeys C, Simoen E, Schreutelkamp RJ. Impact of Silicidation on the Excess Noise Behavior of MOS Structures. Solid-State Electron. 1995;38(11):1893–97.

- [3] Hooge FN. 1/f Noise Sources. IEEE Trans Electron Devices. 1994;41(11):1926–35.

- [4] Mc. Whorter AL. Semiconductor Surface Physics, University of Pennsylvania Press, Philadelphia, PA. 1957:207.

- [5] Mikoshiba H. 1/f Noise in n-Channel Silicon-Gate MOS Transistors. IEEE Trans Electron Devices. 1982;29(6):965–70.

- [6] Ghibaudo G, Roux-dit-Buisson O, Nguyen-Duc Ch, Brini J. Improved Analysis of Low Frequency Noise in Field-Effect MOS Transistors. Solid Stat Solidi A. 1991;124:571.

- [7] Kuroda R, Yonezawa A, Teramoto A, Li TL, Tochigi Y, Sugawa S. A Statistical Evaluation of Random Telegraph Noise of In-Pixel Source Follower Equivalent Surface and Buried Channel Transistors. IEEE Trans Electron Devices. 2013;60(10):3555–61

- [8] Gaubert P, Teramoto A, Kuroda R, Nakao Y, Tanaka H, Sugawa S, et al. Analysis of the Low-Frequency Noise Reduction in Si(100) Metal-Oxide-Semiconductor Field-Effect Transistors. Jpn J Appl Phys. 2011;50:04DC01.

- [9] Von Haartman M, Lindgren AC, Hellstrom PE, Malm BG, Zhang SL, Ostling M. 1/f Noise in Si and Si0.7Ge0.3 pMOSFETs. IEEE Trans Electron Devices. 2003;50(12):2513– 9.

- [10] Teramoto A, Hamada T, Yamamoto M, Gaubert P, Akahori H, Nii K, et al. Very High Carrier Mobility for High-Performance CMOS on a Si(110) Surface. IEEE Trans Electron Devices. 2007;54(6):1438–45.

- [11] Le Royer C. Interfaces and Performance: What Future for Nanoscale Ge and SiGe Based CMOS? Microelectron Eng. 2011;88(7):1541–8.

- [12] Deng F, Johnson RA, Asbeck PM, Lau SS, Dubbelday WB, Hsiao T, et al. Silicidation Process Using NiSi and Its Device Application. J Appl Phys.1997;81(12): 8047–51.

- [13] Kuroda R, Tanaka H, Nakao Y, Teramoto A, Miyamoto N, Sugawa S, et al. Ultra-low Series Resistance W/ErSi<sub>2</sub>/n<sup>+</sup>-Si and W/Pd<sub>2</sub>Si/p<sup>+</sup>-Si S/D Electrodes for Advanced CMOS Platform. IEDM. 2010. Proc. International Electron Devices Meeting; San Francisco, USA; 26.2.1–26.2.4

- [14] Isogai T, Tanaka H, Goto T, Teramoto A, Sugawa S, Ohmi T. Formation and Property of Yttrium and Yttrium Silicide Films as Low Schottky Barrier material for n-Type Silicon. Jpn J Appl Phys. 2008;47(4):3138–41.

- [15] Gaubert P, Teramoto A, Hamada T, Yamamoto M, Kotani K, Ohmi T. 1/f Noise Suppression of pMOSFETs Fabricated on Si(100) and Si(110) Using an Alkali-Free Cleaning Process. IEEE Trans Electron Devices. 2006;53(4):851–6.

- [16] Kumagai Y, Abe K, Fujisawa T, Watabe S, Kuroda R, Miyamoto N, et al. Large-Scale Test Circuits for High-Speed and Highly Accurate Evaluation of Variability and Noise in Metal-Oxide-Semiconductor Field-Effect Transistor Electrical Characteristics. Jpn J Appl Phys. 2011;50:106701 (Copyright © 2011 The Japan Society of Applied Physics).

- [17] Ohmi T, Hirayama M, Teramoto A. New Era of Silicon Technologies Due to Radical Oxidation Based Semiconductor Manufacturing. J Phys D: Appl Phys. 2006;39(1):R1– 17.

- [18] Hamada T, Teramoto A, Akahori H, Nii K, Suwa T, Hirayama M, et al. High Performance Low Noise CMOS Fabricated on Flattened (110) Oriented Si Substrate. Proc. AWAD. 2004:163–166. Proc. Asia–Pacific Workshop on Fundamentals and Applications of Advanced Semiconductor Devices; Nagasaki, Japan; 163–166

- [19] Watabe S, Teramoto A, Abe K, Fujisawa T, Miyamoto N, Sugawa S, et al. Statistical Evaluation of Process Damage Using an Arrayed Test Pattern in a Large Number of MOSFETs. IEEE Trans Electron Devices. 2010;57(6):1310–8.

- [20] Ohmi T. Total Room Temperature Wet Cleaning for Si Substrate Surface. Journal of The Electrochemical Society 1996;143(9):2957–64.

- [21] Nishiuchi K, Oka H, Nakamura T, Ishikawa H, Shinoda M (Eds). A Normally-Off Type Buried Channel MOSFET for VLSI Circuits. International Electron Devices Meeting, San Francisco, CA, USA; 1978.

- [22] Nguyen TN, Plummer JD (Eds). Physical Mechanisms Responsible for Short Channel Effects in MOS Devices. International Electron Devices Meeting, Washington DC, USA; 1981.

- [23] Yuan T, Hu GJ, Dennard RH, Terman LM, Chung-Yu T, Petrillo KE. A Self-Aligned 1mm-Channel CMOS Technology with Retrograde n-Well and Thin Epitaxy. IEEE Trans Electron Devices. 1985;32(2):203–9.

- [24] Suzuki H, Kuroda R, Teramoto A, Yonezawa A, Sugawa S, Ohmi T (Eds). Impact of Random Telegraph Noise Reduction with Buried Channel MOSFET. The 2011 International Conference on Solid State Devices and Materials, Nagoya, Japan; 2011.

- [25] Yonezawa A, Teramoto A, Obara T, Kuroda R, Sugawa S, Ohmi T, editors. The Study of Time Constant Analysis in Random Telegraph Noise at the Sub-Threshold Voltage Region. International Reliability Physics Symposium, Monterey; 2013.

- [26] Watabe S, Sugawa S, Teramoto A, Ohmi T. New Statistical Evaluation Method for the Variation of Metal-Oxide-Semiconductor Field-Effect Transistors. Jpn J Appl Phys. 2007;46(4B):2054–7.

- [27] Kumagai Y, Abe K, Fujisawa T, Watabe S, Kuroda R, Miyamoto N, et al. Large-Scale Test Circuits for High-Speed and Highly Accurate Evaluation of Variability and Noise in Metal-Oxide-Semiconductor Field-Effect Transistor Electrical Characteristics. Jpn J Appl Phys. 2011;50: 106701.1–106701.11.

- [28] Watabe S, Teramoto A, Abe K, Fujisawa T, Miyamoto N, Sugawa S, et al. A Simple Test Structure for Evaluating the Variability in Key Characteristics of a Large Number of MOSFETs. IEEE Trans Semicond Manuf. 2012;25(2):145–54.

- [29] Abe K, Sugawa S, Watabe S, Miyamoto N, Teramoto A, Kamata Y, et al., editors. Random Telegraph Signal Statistical Analysis Using a Very Large-scale Array TEG with 1M MOSFETs. IEEE Symposium on VLSI Technology, Kyoto; 2007.

- [30] Kuroda R, Yonezawa A, Teramoto A, Li TL, Tochigi Y, Sugawa S. A Statistical Evaluation of Random Telegraph Noise of In-Pixel Source Follower Equivalent Surface and Buried Channel Transistors. IEEE Trans Electron Devices. 2013;60(10):3555–61.

- [31] Colinge J-P, Lederer D, Afzalian A, Yan R, lee C-W, Akhavan ND, et al. Properties of Accumulation-Mode Multi-Gate Field-Effect Transistors. Jpn J Appl Phys. 2009;48(3): 034502.

- [32] Cheng W, Teramoto T, Ohmi T. Experimental Demonstration and Analysis of High Performance and Low 1/f Noise Tri-gate MOSFETs by Optimizing Device Structure. Microelectron Eng. 2009;86(6/7):1786–8.

- [33] Kuroda R, Teramoto A, Cheng W, Sugawa S, Ohmi T. Hot Carrier Instability Mechanism in Accumulation-Mode Normally-off SOI n-MOSFETs and Their Reliability Advantages. ECS Trans. 2007;6(4):851–6.

- [34] Akarvardar K, Cristoloveanu S, Dufrene B, Gentil P, Schrimpf R, Blalock B, et al. Evidence for Reduction of Noise and Radiation Effect in g4-FET Depletion All-Around Operation. Proc. 35<sup>th</sup> European Solid-State Device Research Conference; Grenoble, France 2005:89–92.

- [35] Gaubert P, Teramoto A, Sugawa S, Ohmi T. Hole Mobility in Accumulation Mode Metal-Oxide-Semiconductor Field-Effect Transistors. Jpn J Appl Phys. 2012;51:04DC07.

- [36] Gaubert P, Teramoto A, Sugawa, Ohmi T. Low Frequency Noise Assessment of Accumulation Si p-MOSFETs. Proc. SSDM. Proc. International Conference on Solid State Devices and Materials; Kyoto, Japan 2012:839–40.

# IntechOpen