We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

186,000

200M

Our authors are among the

TOP 1% most cited scientists

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

# Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

# **Code Generation From MATLAB – Simulink Models**

Tiago da Silva Almeida, Ian Andrew Grout and Alexandre César Rodrigues da Silva

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/57575

## 1. Introduction

Nowadays, computational tools are indispensable in the design of electronic circuits due to the increase in complexity of electronic circuits and the need to manage large amounts of related data to design. The development of new methodologies and tools has become a strategic area in the development of new technologies, in particular the development of CAD (Computer Aided Design) tools. CAD tools can be best understood as design information management systems, along with the creation of graphic based input and simulations of the designs are created. These simulations can be used, shared, published, republished and reused in different formats, scales and levels of detail.

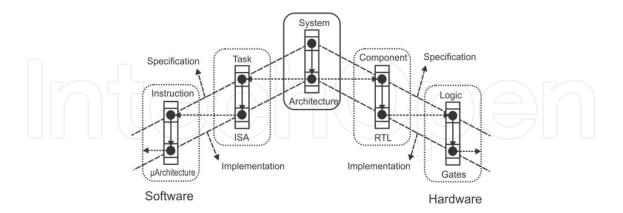

But with so many studies involving different methodologies and computational tools, in [1], it was proposed to form a classification model for design and tools at the Electronic System Level (ESL) of design abstraction. This chapter details the characteristics and approaches that differ between computational tools of design, for modeling at level hardware and software. Figure 1 illustrates the design flow in different levels of abstraction. The design flow, called the Double Roof Model, is considered by [1] as an extended version of the Y diagram presented by [2][3]. However, there are still problems of incompatibility between designs the tools and this identifies a number of weaknesses.

Figure 1 shows the process of designing the top-down methodology in an ideal way. The left side corresponds to the process of software creation, while the right side corresponds to the process of hardware creation. Each side is divided into different levels of abstraction, e.g., Task and Instruction (software) or Components and Logic (hardware). There is a common level of abstraction, named ESL. In this level, we cannot distinguish between hardware and software. At each level, we can run a synthesis step (continuous vertical arrow) and the specification is transformed into an implementation. Horizontal dotted arrows indicate the steps which we

© 2014 The Author(s). Licensee InTech. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

can change the models of individual elements in the implementation directly to the next level of abstraction (lower level abstraction).

Figure 1. Flow design of electronic systems, also known as Double Roof Model.

In this chapter, we present a methodology for ESL designs based in four computational tools. The first one is the SF<sup>2</sup>HDL tool (Stateflow to Hardware Description Language or transition states table). The SF<sup>2</sup>HDL has the ability to convert models of finite state machine (FSM) in Stateflow / Simulink in a corresponding description in VHDL, Verilog or even a text file with a state transition table. The descriptions in the VHDL and Verilog languages are generated at the behavioral abstraction level for the finite state machine. The second computational tool, called MS<sup>2</sup>SV (MATLAB / Simulink to SystemVision), is able to generate descriptions in VHDL-AMS from models described in Simulink and all of model structure design for simulation in SystemVision environment from Mentor Graphics. The descriptions are generated in VHDL-AMS since even in the standard Simulink toolbox. there are many components with different signal representations of a purely digital representation. The third computational tool developed, called BD<sup>2</sup>XML (Block Diagram to XML), is able to generate a textual representation of the architecture of this model in XML markup language, also from models described in Simulink. XML was chosen for its applicability and it can be used as object code by other tools. The fourth and last computational tool described works together with BD<sup>2</sup>XML and it is similar to SF<sup>2</sup>HDL. The tool, called SF<sup>2</sup>XML (Stateflow to XML), is able to capture the relevant information in the Stateflow file and generate a corresponding description in XML. The file resulting from the conversion is according to the standard of XML structure called SCXML (StateChart XML) proposed by the W3C [4].

For acceptance in the community of software development, maintainability and practicality, we chose to develop the translation environment using an object-oriented approach. For robustness, the C++language was chosen. With C++ language is possible create linear and nonlinear data structure, and languages like Java, it is not possible do it. In our tools, we used liner lists to store dynamically the data in memory. Thus, C++language is a better choice for programming language. Another reason for this choice, it is the common features between methods were coupled to objects, so there was created a logical interaction with low representational gap.

As case study designs, the digital-to-analog converters (DAC) design was used to explain the MS<sup>2</sup>SV and BD<sup>2</sup>XML. Data converters are circuits that transform a given representation to another. The ADC (analog to digital converter) is used to convert analog signals to digital data. The digital to analogue converter works in the opposite manner to the ADC, converting digital data input to analogue signal output proportional to value of input digital.

Considering the DAC operation, *n* binary input bits (which can be considered as representing the binary code of a decimal value) are received and there are  $2^n$  possible combinations of binary input. There is also an additional input to the circuit design that is used as a reference signal, represented by  $V_{ref}$  and the reference is a voltage level, which is used to determine the maximum value that converter can generate on its output. The analog value is generated by the weighted sum of *n* inputs, multiplied by the reference voltage. Inputs are weighted according to magnitude of each bit, where *n* is the magnitude of input bit, *x* is total number of inputs, and *b* is DAC input value contained in the bit of *n* magnitude, where  $b_n \in \{0,1\}$ , as described in:

$$V_{P} = \sum_{n=1}^{x} \frac{1}{2^{n}} b_{n}$$

(1)

Using Equation (1), the analogue output voltage from the data converter is obtained by multiplying the result of Equation (1) by the reference voltage to obtain:

$$V_{out} = V_P \times V_{ref} \tag{2}$$

There are several methods possible to implement the DAC operation (i.e., there are several different DAC design architectures possible). One common method used is R/2R ladder circuit, where only two values for resistors in circuit are used (R and 2R), and output current depends on positions of switches that are controlled by inputs [5].

To explain the use of SF<sup>2</sup>HDL and SF<sup>2</sup>XML, we used a HDB3 (High Density Bipolar 3) finite state machine [6]. HDB3 line code, which is a technique for detecting synchronism with bipolar signaling, and it has been used over the years in digital systems. A finite state machine can be represented by state diagrams. State diagrams are used to graphically represent a state transition functions set. Having an input event set, the output event set and the next state set can be determined.

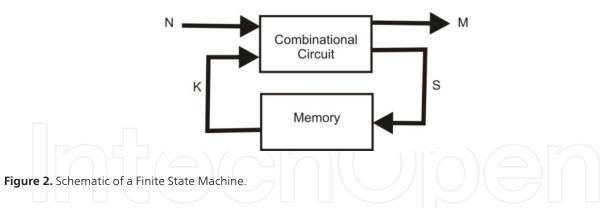

There are also several other forms to represent finite state machine that differ slightly and have different semantic. The State Transition Table and Petri Net are two examples. Figure 2 shows generic schematic of a finite state machine. The circuit has a finite number of inputs, representing all input variable set  $\{N_1, N_2, ..., N_n\}$ . Thus, the circuit has a finite number *m* of outputs, determined by the output set of variables  $\{M_1, M_2, ..., M_m\}$ .

The value in each memory element is called a state variable, and the set denoted by  $\{K_1, K_2, ..., K_k\}$  form the state variable set. The values contained in *k* memory elements define the internal state of finite state machine. The outputs  $\{M_1, M_2, ..., M_m\}$  and internal transition functions  $\{S_1, S_2, ..., S_s\}$  depend on external inputs (input functions) and internal states (state functions) of state machine and they are defined by combinational circuits. The values *S*, which appear in the role of state transitions of machine at time *t*, determine values of state variables at time *t* +1 and therefore define the next state of machine.

The state transition diagram or the state transition table makes the relationship between present state, next state, input and output.

The finite state machines that determine the next state K(t+1) only in the present state K(t) and present input N(t) are called deterministic machines or Markovian. Deterministic machines can be represented by the following equation:

$$K(t+1) = f[K(t), N(t)]$$

(3)

Where, f is a state transition function. The value of output M(t) is obtained through of two ways:

where, *g* is an output function.

A finite state machine with properties described in Equations (3) and (4) is called Moore model and a machine described by equations (3) and (5) is called Mealy model [7].

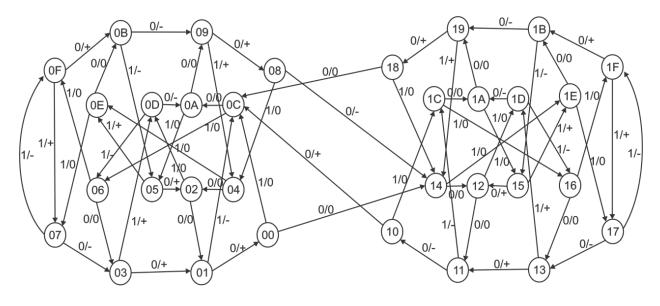

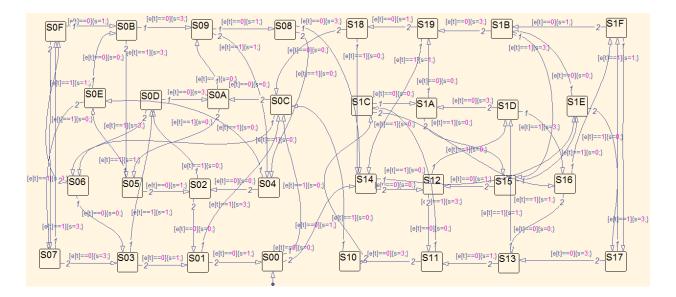

To illustrate the state transition diagram, Figure 3 shows a state transition diagram of HDB3 code line, in hexadecimal representation as proposed in [6]. The encoder needed three parts

of memory to store and to identify four successive 0. After this, it was necessary to use a flipflop to store the polarity of the pulse (0 for+or 1 for-), and finally other flip-flop to store the polarity of the violation. The encoder requests a minimum of 25=32 states. The state 00 represents the initial state of the machine, and the two pairs of state 07 and 0F (in the left) and 1F and 17 (in the right) represent the description AMI, what causes the alternate code between +1 and-1 [6].

# 2. Related research

Project-level electronic systems, also known as ESL (Electronic System Level), require much effort designer. The first work to classify the steps involved in system design at a high level of abstraction [2] subsequently refined to a more current [1] and [3].

Figure 3. State transition diagram for HDB3 line code.

Some studies deal with design optimization or minimization, for example the work in paper [8]. This work explored the computational complexity of logic minimization problem on two levels for digital circuit designs. In [9] was developed a genetic algorithm for synthesis of multi-core architectures. The target system was an implementation of Petri net. In [10] was presented a method of re-engineering the FSM by rebuilding it with a different topology, but with equivalent functionality. The method is mainly concerned with power consumption of the finite state machine and uses a genetic algorithm to find the best solution. This approach facilitates the process of synthesis for optimal implementations of the system.

The representation of electronic systems by means of the FSM facilitates verification of the system and formal methodologies can be developed to assist in the synthesis process. In [11] was presented a tool capable to translate a FSM described in the VHDL. The focus of the work was modeling and the verification. In [12] was developed a conceptual mathematical model

for automatic checking of the FSM by observing the outputs of this particular FSM, allowing checking faulty behavior.

Hardware description languages (HDLs) are widely used in the design of electronic systems and also represent a major means for simulation and project documentation. In [13] was developed an algorithm for automatic generation of analog circuit models for modeling faults in the circuit at a high level. In [14] was developed a methodology for implementing FFT (Fast Fourier Transform) processors in reprogrammable devices using VHDL. In [15] was developed the architecture for implementing a SPICE (Simulation Program with Integrated Circuit Emphasis) simulator using an FPGA (Field Programmable Gate Array)

In [16] the authors proposed a simulator for the VHDL-AMS (Analog and Mixed Signal) language developed in the MATLAB environment. The tool was compared with others simulators available commercially. Another example that can be cited is the tool called SF2VHD, presented in [17]. That tool is capable to translate hierarchical models of finite states machine, modeled in the Stateflow environment, in a code corresponding structural VHDL.

In the work described in [18] was developed a tool called Sim2HDL, which accomplishes the automatic translation of Simulink models in a hardware description language in the attempt to drastically reduce the project time. The generated language can be VHDL or Verilog, at a behavioral level description, and the system can be implemented in FPGAs using commercial synthesizers.

Some commercial modeling tools incorporate the translation need for different forms of modeling. An example is a MATLAB C Compiler tool, developed by Mathworks. That tool translates programs written in MATLAB for a corresponding program in the C language. The functionality and main advantages of these tools are described in [19].

In [20] was proposed an approach to automatic synthesis of additional decoders. The method attempts to find and remove cases where there are no equivalent decoders. To discover all decoders that can exist simultaneously, an algorithm based on functional dependency has also been proposed. To select the correct decoder another algorithm is used to infer formula of each decoder precondition.

In [21] was developed a framework for the synthesis of electronic systems at a high level based on abstract finite state machines. The framework called synASM is capable of generating a CDFG (Control Data Flow Graph) from hardware descriptions based on C language. The authors extended the definitions of abstract state machines to support the parallelism and timing. After generating the CDFG extended, it was possible the automatic generation of optimizable hardware descriptions in VHDL and implementation in a FPGA.

In [22] was presented a complete approach decoder for communication systems. The modelling was based on finite state machines and the method was capable of identifying whether decode exists or not, by observing the input sequence and output of encoder. [23] presented a method of representation and synthesis of Boolean expressions recursively. The method performs a sequence of operations with denial implications using two memristors. With the method, it was proved that it was possible to reduce the number of necessary implications for the expression representation and inference using multiple inputs can reduce the computation of memristor implementation.

In [24] was proposed an algorithm for identifying flowcharts structure. Twelve structures were identified and then the algorithm was used to generate the code flowchart identified using recursion. The technologies and algorithms were used in an integrated development platform. [25] presented an approach of output bit selection based on counter for output response compaction in test systems observable. The hardware implementation requires only a counter and a multiplexer. Thus, the complexity was reduced and the control area was simplified. Furthermore, a change in the ATPG (Automatic Test Pattern Generation) tool was not required. Two output selection algorithms have been developed in several operations which counters can be employed.

In [26] was discussed some work and the importance of developing CAD tools for the synthesis and design of systems and multi-core architectures, highlighting the importance of multi-core optimized and efficient resource allocation. [27] presented revised performance measures of some data type converters ADC (Analog-to-Digital Converter), such as SNR (Signal to Noise Ratio), SINAD (Signal to Noise Ratio and Distortion), SFDR (Spurious free Dynamic Range), THD (Total Harmonic Distortion) and ENOB (Effective Number of Bits). These metrics were analyzed with the case study of an ideal 14-bit converter in MATLAB and a converter with 12-bit commercial manufactured by Analog Devices.

In [28] was presented a methodology for genetic optimization based on VHDL-AMS for Fuzzy Logic controllers. The fuzzy logic controller was used for modeling work in automotive systems in mixed physical domain. A genetic algorithm was developed and simulated in SystemVision environment, is employed in the generation of rough fuzzy sets.

# 3. Generation code methodology of SF<sup>2</sup>HDL

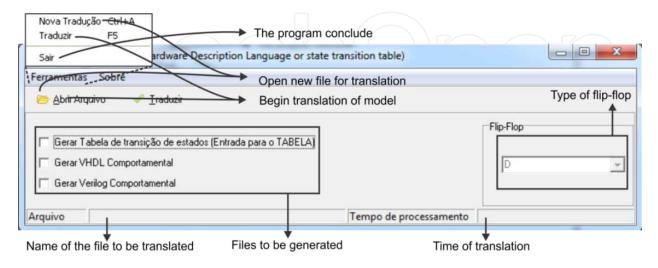

The SF<sup>2</sup>HDL is a computational tool capable to convert a state transition diagram into a hardware description language description. This diagram is described in the Stateflow environment [29]. The Stateflow is toolbox inside Simulink is used to simulate finite state machines in different contexts. The SF<sup>2</sup>HDL tool is a simplified graphical interface that allows the user to select between generate (i) an input file to be processed by TABELA program and (ii) a.*vhd* file with a behavioral VHDL description obtained directly from state transition diagram.

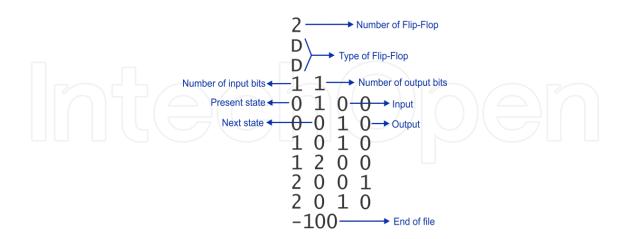

The TABELA program was developed for synthesize of a finite state machine and was implemented in Pascal language by researchers from UNICAMP [7] (Universidade Estadual de Campinas-Brazil). The program generates combinational functions that implement the finite machine described by state transition table. The transition functions and output functions are minimized and the cost of minimization using minterms and maxterms [7]. The transitions are specified on table form using one line per state transition, so: present state, next state, input, output. The description end is represented by notation "-100". Figure 4 shows the standard file for TABELA program input.

The states, the inputs and outputs must be in decimal notation. The finite state machines can be completely or incompletely specified.

Figure 4. Input file for TABELA program.

The TABELA program assembles a state transition table and stores it in output file. From this table are obtained minterms, maxterms and don't care states of transition functions of all internal flip-flops and circuit output functions. Using Quine-McCluskey algorithm, is made the minimization of Boolean functions.

Figure 5 illustrates the main interface of SF<sup>2</sup>HDL program. The SF<sup>2</sup>HDL has a menu called **Ferramentas** (Tools) with the following options: a) **Nova Tradução** (Translation), used to open the file with a finite state machine modeled in Stateflow environment, b) **Traduzir** (Translate), which performs the model translation into one of language was chosen, c) **Sair** (Quit), which terminates the program, and d) **Sobre** (About) option that displays a screen with a brief comment on the tool developed.

Figure 5. Main interface of SF<sup>2</sup>HDL program.

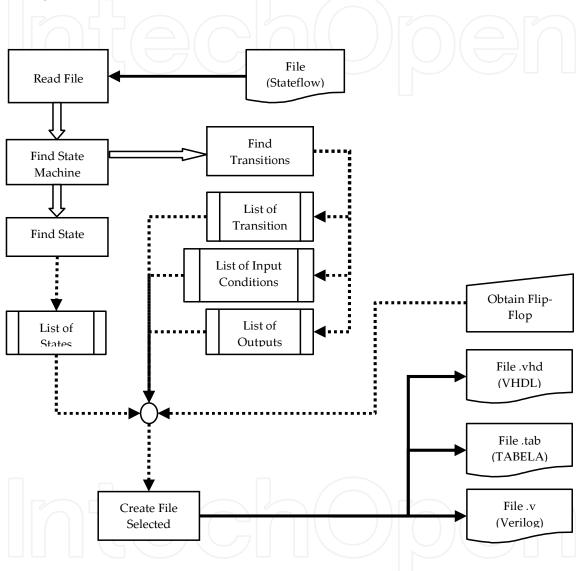

Thus, from all the information found in the.*mdl* (Simulink file) file, it is possible to determine the present state, the next state, the input and output of the finite state machine. According to the structure of each file, all the information is grouped and then is generated the input file for TABELA program and/or the corresponding behavioral VHDL. Figure 6 presents the functional diagram of SF<sup>2</sup>HDL program with all necessary steps to perform the translation, as previously reviewed.

Figure 6. Block diagram of SF<sup>2</sup>HDL.

SF<sup>2</sup>HDL initially reads the file containing finite state machine, simulated in the Stateflow environment. Then, the program finds the state machine structure and it makes a temporary storage of this information. After that, the state location list for all states is generated and through the transition locations is generated a transitions list, identifying the conditions for the inputs and outputs. When the user selects to generate the input file for the TABELA program, there is the need to choose what type of memory element (flip-flop) will be used in the generated file. The memory element type must be put manually by the user.

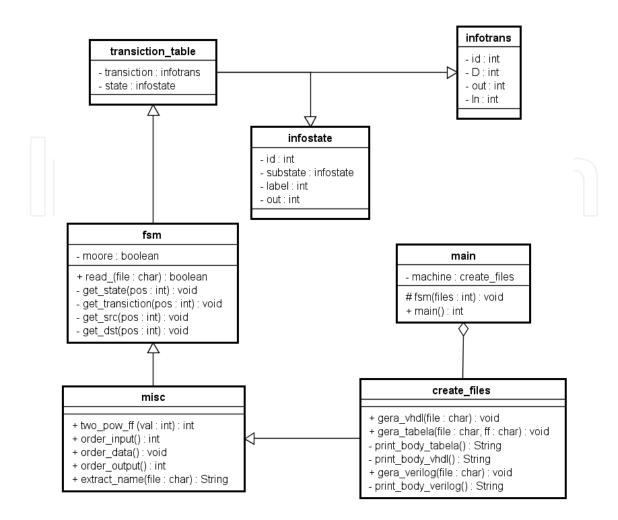

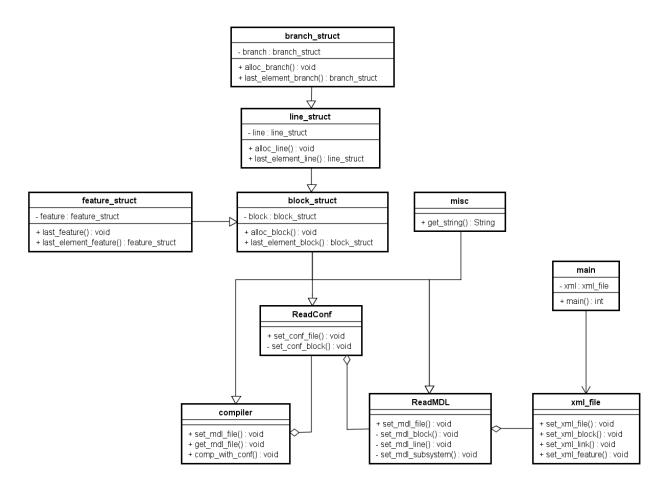

Figure 7 shows the class diagram of SF<sup>2</sup>HDL. The SF<sup>2</sup>HDL was built with many inheritances between the classes. There are two objects to store the structure found in the.*mdl* file; the state information and transition information. This distinction is considered because the differences between a Mealy machine and Moore machine described in Equations (3), (4) and (5). SF<sup>2</sup>HDL is capable of recognizing which machine is used in the model. The **fsm** object is responsible to read the.*mdl* file and to save this information. The **misc** has some operations used many times during running of SF<sup>2</sup>HDL. The **create\_files** object is responsible to create the file that was chosen by user, as illustrate in Figure 7. As SF<sup>2</sup>HDL can create three files at the same time, the **main** class call the **create\_files** more than once, if it is the case.

#### 3.1. Simulation results of HDB3 line code and conversion results

For modeling the state transition diagram on Stateflow environment, some rules must be obeyed, such as the name of the state contained within the symbol should never begin with numeric character (0, 1, 2, 3, 4, 5, 6, 7, 8 or 9), and the condition in the transition to the Mealy model must meet the following syntax:

$$[e[t] == 0]\{s = 0;\}$$

(6)

where *e* represents the variable that will receive input value, *t* is a variable that represents a discrete time and *s* is an output variable. The external bracket represents the input condition in the transition from one state to another to obtain an output. The double equal signs (==) represent the verification of a condition and the equal sign alone (=) represents the allocation of value [30].

For proper functionality of the SF<sup>2</sup>HDL program, is necessary that the values in the transition of model in Stateflow environment, both at input and output, are decimal representations. Figure 8 presents the state diagram of HDB3 code on Stateflow environment.

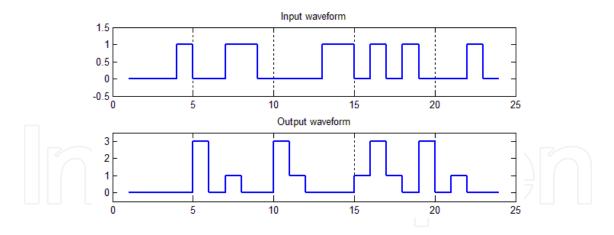

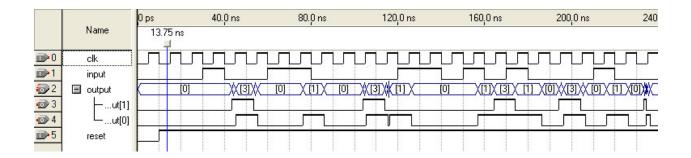

In simulation are used several words with signs and bits from varying sizes. However, it was standardized in using an input word in the simulation of 24 bits being formed by the following bits: 0001001100001101000100. We used this bit stream because with it we can simulate both characteristics of signal encoder, AMI and HDB3, in a real situation. The result of the simulation is presented in the Figure 9.

The TABELA program creates a new file, containing a description of Boolean functions from the circuit already minimized.

Listing 1 was reduced and is shown only important parts of minimization. Each Boolean function in the finite state machine is minimized. As HDB3 has five flip-flops and two output bits, it is possible to see seven functions in Listing 1 (lines 1, 11, 21, 28, 34, 40 and 51). In each function are described the function minterms in decimal, e.g. line 3. The function prime implicants and essentials are shown too, e.g. lines 4-9. And the function cost is shown in lines 10, 20, 27, 33, 39, 50 and 58. The total cost of the circuit is shown in lie 59, for HDB3 case is 95. It is important to highlight that the cost is expressed like sum of product by TABELA.

Figure 7. Class diagram of SF<sup>2</sup>HDL.

Figure 8. Description of HDB3 code on Stateflow.

Figure 9. Results of simulation of HDB3on Stateflow.

```

1. FUNCAD D4

2. #INTERMOS 0; 0; 8; 48; 17; 49; 18; 50; 19; 51; 20; 52; 21; 53; 22; 54; 23; 55; 25; 57; 26;

3. MINTERMOS 0; 0; 8; 748; 17; 49; 18; 50; 19; 51; 20; 52; 21; 53; 22; 54; 23; 55; 25; 57; 26;

4. SESSENCIAL: 10 REDUNDANCIA: 45 -> XLXLXX

7. ESSENCIAL: 17 REDUNDANCIA: 45 -> XLXXX

7. ESSENCIAL: 17 REDUNDANCIA: 45 -> XLXXX

7. ESSENCIAL: 18 REDUNDANCIA: 45 -> XLXXX

7. ESSENCIAL: 19 REDUNDANCIA: 45 -> XLXXX

7. ESSENCIAL: 10 REDUNDANCIA: 45 -> XLXXX

10. ESSENCIAL: 10 REDUNDANCIA: 21 -> OXXXX

110 ESSENCIAL: 10 REDUNDANCIA: 22 -> OLXXXI

110 ESSENCIAL: 10 REDUNDANCIA: 22 -> OLXXXI

111 IMPLICANTES PRIMOS ESSENCIALS 22 -> OLXXXI

112 ESSENCIAL: 10 REDUNDANCIA: 22 -> OLXXXI

113 ESSENCIAL: 10 REDUNDANCIA: 22 -> OLXXXI

114 IMPLICANTES PRIMOS ESSENCIALS 22 -> OLXXXI

115 ESSENCIAL: 10 REDUNDANCIA: 22 -> OLXXXI

115 ESSENCIAL: 10 REDUNDANCIA: 22 -> OLXXXI

116 ESSENCIAL: 10 REDUNDANCIA: 23 -> XLXXX

117 ESSENCIAL: 10 REDUNDANCIA: 23 -> XLXXX

118 ESSENCIAL: 10 REDUNDANCIA: 23 -> XLXXX

119 ESSENCIAL: 10 REDUNDANCIA: 23 -> XLXXXI

119 ESSENCIAL: 10 REDUNDANCIA: 23 -> XLXXXI

120 ESSENCIAL: 10 REDUNDANCIA: 56 -> XXX000

121 CUSTO FFMAL DE 02 = 6

122 FUMCAD D1

133 EXECUTATES PRIMOS ESSENCIALS 11 -> XXXXI

134 EUXCAD D0

135 EXECUTATES PRIMOS ESSENCIALS 11 = XXXXII

135 ESSENCIAL: 1 REDUNDANCIA: 23 -> XXXXX

135 ESSENCIAL: 1 REDUNDANCIA: 24 -> XXXIII

135 ESSENCIAL: 1 REDUNDANCIA: 25 -> XXXXII

136 ESSENCIAL: 1 REDUNDANCIA: 26 -> XXXXII

137 EUXCAD D0

138 EXECUTATES PRIMOS ESSENCIALS 1

139 EXECUTATES PRIMOS ESSENCIALS 1

140 EUXCAD D0

150 EXECUTATES PRIMOS ESSENCIALS 1

151 EXECUTATES PRIMOS ESSENCIALS 1

152 ESSENCIAL: 1 REDUNDANCIA: 26 -> XXXIII

153 ESSENCIAL: 1 REDUNDANCIA: 26 -> XXXIII

154 ESSENCIAL: 1 REDUNDANCIA: 27 -> XXIIII

155 ESSENCIAL: 1 REDUNDANCIA: 27 -> XXIIII

155 ESSENCIAL:

```

Listing 1. Minimization generate by TABELA program for HDB3 study case

After the minimization by TABELA was used the TAB2VHDL program [31] which generated VHDL code in RTL (Register Transfer Level) that is shown in Listing 2. The TAB2VHDL is a tool developed by researchers in UNESP (Universidade Estadual Paulista-Brazil) in C language. The only task TAB2VHDL is generated the VHDL code from TABELA output.

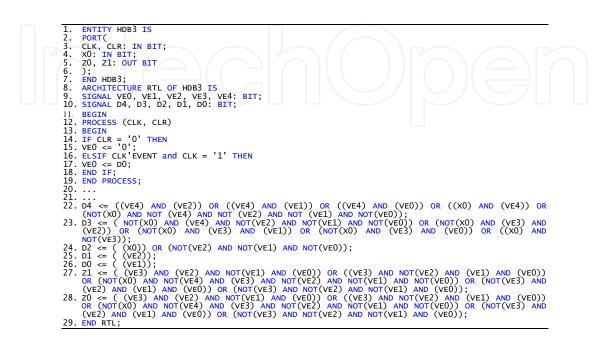

Listing 2. VHDL code generate by TAB2VHDL program for HDB3 study case.

In Listing 2, there is clear distinction in architecture between the flip-flops and the Boolean function to describe the behavior of HDB3. In lines 15-22 are described the flip-flop used (noting that this listing was reduced to presentation in this chapter). Lines 25-31 show the Boolean function of HDB3. This kind of abstraction has better results for synthesis in order to implement the circuit, e.g. in a FPGA (Field Programming Gate Array).

The other option is to generate the behavioral VHDL directly without using TABELA program. In Listing 3 is shown the file with behavioral VHDL code generated.

This description is different between Listing 2 as it is expressed at a behavioral level of abstraction for HDB3. In lines 3 and 4 in the entity, the signal representation is in decimal instead binary. This is a different way that VHDL can support the representation of input and output signals. Lines 14-41 express the behavior of the finite state machine. The reset signal is shown in line 18 and 19 and lines 21-40 show the transitions of HDB3. SF<sup>2</sup>HDL does not use the same label used in Stateflow, such as Figure 8. This case study coincidentally is the same (decimal representation instead hexadecimal), but in other cases then this label will be changed. The last process in description, lines 43-47, describes the update of state by clock signal.

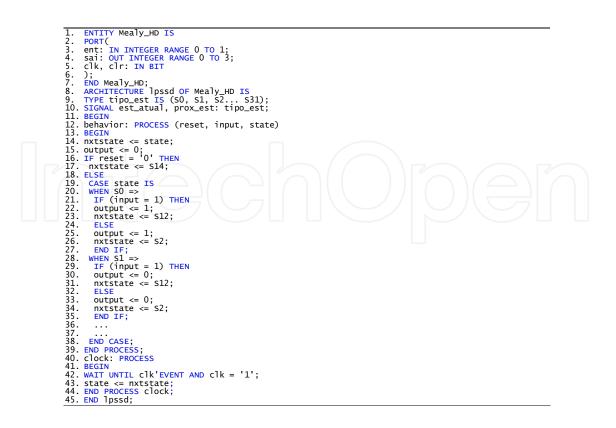

The third description language generated by SF<sup>2</sup>HDL is a behavioral Verilog code [32], which it is shown in Listing 4.

Listing 3. Behavioral VHDL code generate by SF<sup>2</sup>HDL for HDB3 study case.

Listing 4 is very similar to Listing 3, with the difference in the syntax between both languages, VHDL and Verilog. In the same way, lines 18-48 express the behavioral of the finite state machine, the reset signal is shown in line 21 and 23, lines 25-46 is shown the transitions and lines 50-52 describe the update of state by clock signal.

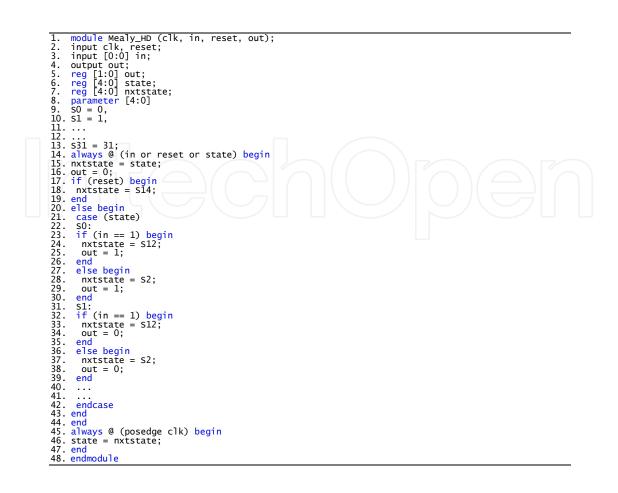

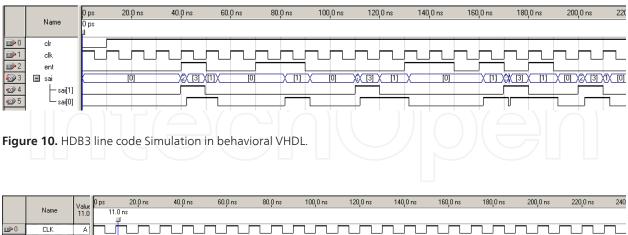

In Figure 10 is shown the simulation of behavioral VHDL code generated by SF<sup>2</sup>HDL on Quartus II environment [33], using the same word of data in the simulation as that in the Stateflow environment to verify accuracy and violation of HDB3 code too in the Quartus II.

There is a short delay in output least significant in Figure 10. But the delay does not disrupt the behavioral of the HDB3 encoder. The behavioral VHDL, RTL VHDL and behavioral Verilog codes were synthesized and implemented on the Cyclone II EP2C20F484C7 FPGA.

Figure 11 shows the simulation waveform of code generated by TAB2VHDL, i.e., using a RTL VHDL code. This is different from Figure 10 and in Figure 11 is possible to see a stranger behavioral of the code. Possibly this is due to some mistakes in TABELA program as the RTL VHDL is same of the optimization realized by TABELA program. Or even, possibly the results of synthesis of Quartus II. At the moment we do not know the cause of the problem.

Figure 12 illustrates the simulation results for behavioral Verilog code. The simulation waveform of Figure 12 is the same waveform in Figure 10, proving that this representation in behavioral Verilog and VHDL, because the level of abstraction in the same too. The synthesis result in FPGA Cyclone II is another equal result.

Listing 4. Behavioral Verilog code generate by SF<sup>2</sup>HDL for HDB3 study case.

| ▶0             | CLK             | A   |     |     |      |     |    |     |       |       |   |     |   |    |     |              |          |       |

|----------------|-----------------|-----|-----|-----|------|-----|----|-----|-------|-------|---|-----|---|----|-----|--------------|----------|-------|

| <b>□&gt;</b> 1 | CLR             | A i |     |     |      |     |    |     |       |       |   |     |   |    |     |              |          |       |

| <b>₽</b> 2     | ×0              | AI  |     |     |      |     |    |     |       |       |   |     |   |    |     |              |          |       |

| <b>⊕</b> 3     | ΞZ              | Α[Ι | [0] | X I | 31 X | [0] | XX | [0] | X [3] | ¥ [0] |   | [0] | X | 3] | [0] | <u>k (3)</u> | 0) 🗱 [0] | 01_XX |

| 💿 4            | -z0             | AI  |     |     |      |     |    |     |       |       | ī |     |   |    |     | J            |          |       |

| <b>⊙</b> 5     | ∟ <sub>Z1</sub> | ΑI  |     |     |      |     |    |     |       |       |   |     |   |    |     | ı            | [        |       |

Figure 11. HDB3 line code Simulation in RTL VHDL.

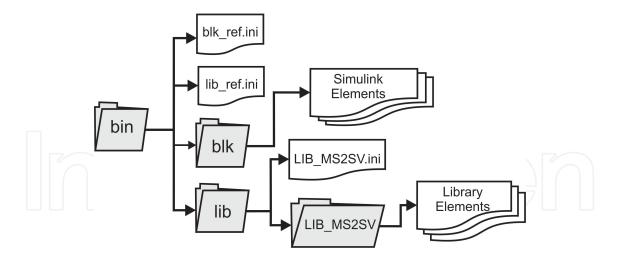

Figure 13. Directory structure and files that are used in configuration and the translation of models in MATLAB / Simulink.

# 4. Generation code methodology of MS<sup>2</sup>SV

The MS<sup>2</sup>SV is capable to convert a simulation model in Simulink to a description in VHDL-AMS [34]. This time, we used a VHDL-AMS description since the models can use different kinds of signals such as electrical, mechanical, hydraulic, etc. MS<sup>2</sup>SV has two key features:

1. The designer is able to add new components from the Simulink libraries. With this feature, the designer can use different elements previously defined in the standard Simulink libraries.

2. The addition of new Simulink libraries developed by the designer with more complex models, or to change the library named LIB\_MS2SV also used in previously paper [36].

Figure 12. HDB3 line code Simulation in behavioral Verilog.

This added flexibility is made possible by creating a directory structure and configuration as shown Figure 13. From the root directory **bin** configuration files are split between configurations of elements from libraries of MATLAB / Simulink (**lib** directory) and elements of toolbox Simulink (**blk** directory) subject to translation. The pseudo-code concerning the VHDL-AMS models are also arranged between directories.

In the main interface, there is the menu containing the following options: a) **Arquivo** (File): In this option, there are two possible actions. With the first action, the user selects the Simulink model to be translated. When this action is selected, the status bar appears on the file name to be translated. The second action is a button to end execution of the tool, b) **Ferramentas** (Tools): In this option, the user is able to select the project location. The process of translation is then initiated. If there are unknown models that the tool is not able to recognize, it will display a message reporting the fact, c) **Configuração** (Configuration): In this option, there is an action called "Adicionar / Remover Componentes (Add / Remove Components)" and another called "Adicionar / Remover Bibliotecas (Add / Remove Libraries)". These options are used to add / remove elements of toolboxes and Simulink libraries developed by the designer, respectively. If there is not a model configuration to be translated, the tool is not able to recognize it and translate it.

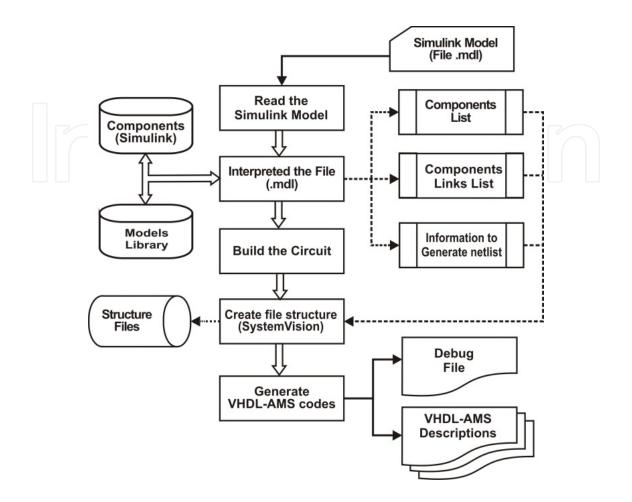

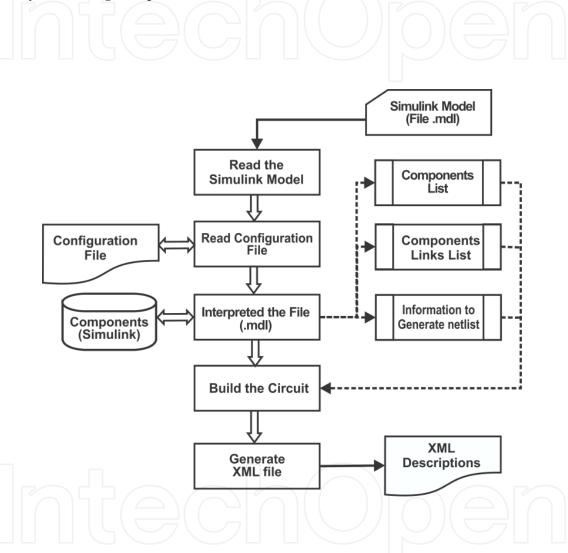

The translation of the model starts with reading a Simulink generated file with an.**mdl** extension. Initially, a check is made of elements and libraries used in model. If there are no unknown libraries or elements, the translation process starts. The tool stores a list of components in model, the list of connections between these components and other important information for generation of circuit netlist. Then, project structure required for simulation and analysis in SystemVision is generated too [35][36]. Finally, all descriptions in VHDL-AMS and files for debugging for project needs are generated. Figure 14 shows the functional diagram of the MS<sup>2</sup>SV tool.

If subsystems are used, a VHDL-AMS model for each subsystem used is generated. The MS<sup>2</sup>SV enables the relationship between elements in the same library by creating hierarchical models.

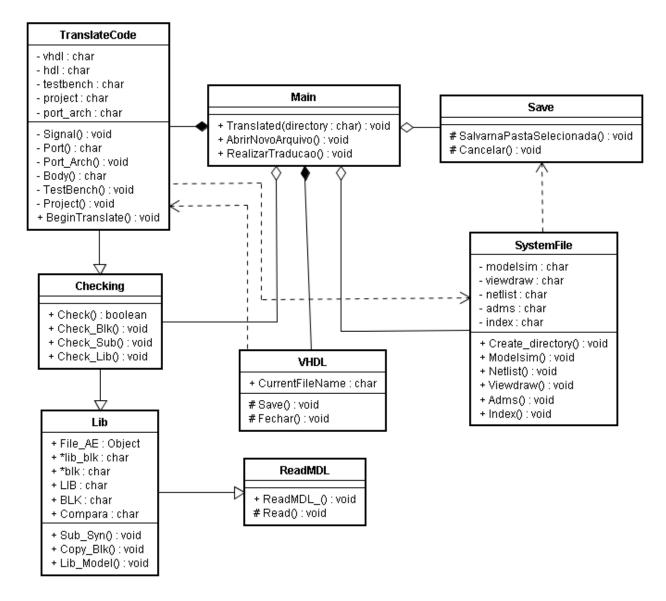

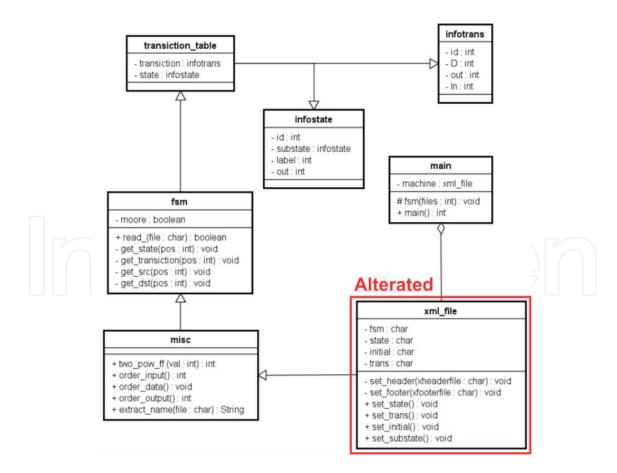

Figure 15 represents the class diagram of tool MS<sup>2</sup>SV in a software perspective. All interface layers are represented since some aspects do not change the MS<sup>2</sup>SV functionality. In Figure 15, only the classes **Main**, **Save** and **VHDL** are in the interface layer. The others class makes the translation inference engine. The **SystemFile** class is responsible to generate all project structure to simulate in SytemVision environment. The **TranslateCode** is responsible to generate all VHDL-AMS files. This class inherits the features of **Checking** class, and **Checking** class checks if there is any primitive of Simulink, user libraries or subsystems. **Checking** inherits the features of **Lib** class and **Lib** class is responsible to reads the models into libraries. Last one, **Lib** inherits the features of **ReadMDL**, it responsible to reads the models in MAT-LAB / Simulink.

The translation process using elements of Simulink toolboxes is started with a verification of elements inside the model using **Checking** class operation. The **Checking** class uses the operation of **ReadMDL** class to read the Simulink file. The reading the Simulink file is done more than once because the interface that controls the inference engine allowing different file being loaded without translation. The process translate of elements inside libraries created by designer is quite similar to elements of Simulink toolboxes, but it includes the Lib class. Lib class copy the descriptions saved into internal libraries in tool MS<sup>2</sup>SV to represent libraries described by designer.

**Figure 14.** Functional diagram of the MS<sup>2</sup>SV tool illustrating the steps involved in translating the model to generate input file structure in SystemVision environment.

# 5. Case study of MS<sup>2</sup>SV and BD<sup>2</sup>XML

The DAC08, AD7524 and AD7528 DAC were chosen to model and simulate to evaluate the proposed methodology. All of them are monolithic data converter with 8 bit resolution used in applications such gain control circuit and stereo audio.

#### 5.1. DAC08

DAC08 is a simpler operating model consisting basically of a converter with a resolution of 8 bit parallel input, which performs the digital to analogue conversion. The conversion of digital data into analog is done using the ladder R/2R where the binary inputs control the switching between the current arrival of resistors and current coming directly from the reference voltage.

Figure 15. Class diagram of translations rules of MS<sup>2</sup>SV.

Based on the specifications found in the datasheet of DAC08 converter [37], it was possible to model it in MATLAB / Simulink. Other details of the implementation on a physical level, such as compatibility with TTL (Transistor-Transistor Logic) and CMOS (Complementary Metal Oxide Semiconductor) technology were not considered since the focus of this work was on modelling at high level of abstraction.

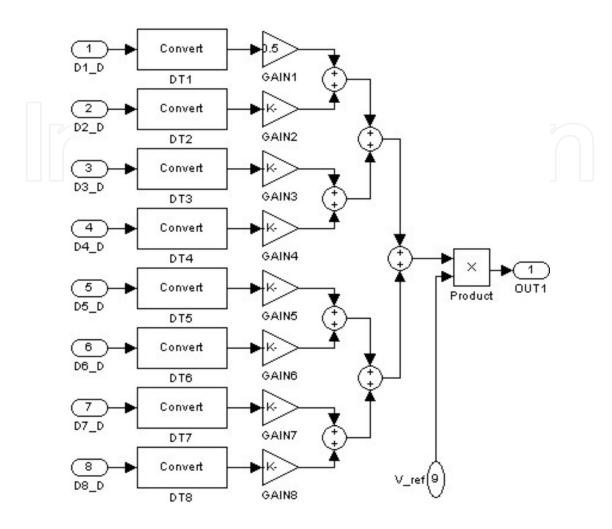

The creation of the R/2R Ladder subsystems involved the use of Equations (1) and (2) in order to adjust the weights of each bit, as shown in Figure 16 [38]. In Figure 16, the Ladder R/2R subsystem was constructed using basic components available in the Simulink libraries. The multiplication between the digital input and weights of each input was made with the "Gain components", the sum with seven "Sum components" of two values and multiplying the result by the reference voltage using "Product component". In this system there are two outputs, the analog signal and the difference between the output and the reference voltage.

Figure 16. Subsystem in Simulink that represents the R/2R ladder using basic components of the Simulink toolbox, such as Product, Sum, Gain and Data Type Conversion.

An aspect that is important to emphasize in the creation of the R/2R ladder model shown in Figure 16 is that there are "Data Type Conversion components". These components are used to change the way representation of the binary signal (logic 0 or 1) for decimal representation (0 V or 1 V) and subsequent multiplication by weight. In MATLAB / Simulink, this component is not necessary. However, in VHDL-AMS, this component becomes important due to different ways of representing a signal in this language (i.e. the signal types used in VHDL and VHDL-AMS).

#### 5.2. AD7524

The AD7524 has internally flip-flops of a latch type capable of storing last digital input, and a logic interface capable of controlling reading and storing digital input. The mode selection is controlled by  $CS_B$  and  $WR_B$  inputs. When  $CS_B$  and  $WR_B$  are at logic low (0) is enabled writing

mode, that is, the analog output representing the binary value at input bus  $DB_0$ - $DB_7$ . But when  $CS_B$  or  $WR_B$  assumes a logic high (1), AD7524 is in hold mode, analog output has the value corresponding to last input in  $DB_0$ - $DB_7$  before  $WR_B$  or  $CS_B$  assume logic high. Table 1 shows the relationship of control inputs and selection mode of AD7524 [39].

|   | CS <sub>B</sub> | WR <sub>B</sub> Selecti | ion mode Comments                                                         |

|---|-----------------|-------------------------|---------------------------------------------------------------------------|

| 0 | 0               | Write                   | The output corresponds to activity on the input bus ( $DB_0$ to $DB_7$ ). |

| 1 | X               | Hold                    | The output corresponds to the last valid entry, stored in flip-flops.     |

| X | 1               | Hold                    |                                                                           |

**Table 1.** Selection mode pins to control the AD7524.

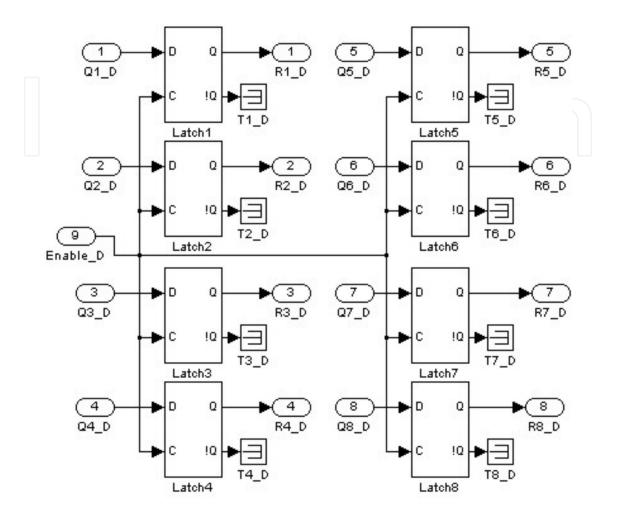

Figure 17 represents the buffers used by the AD7524 to store last valid digital input. This component is basically formed by a set of latches and an input common to all latches to enable the output.

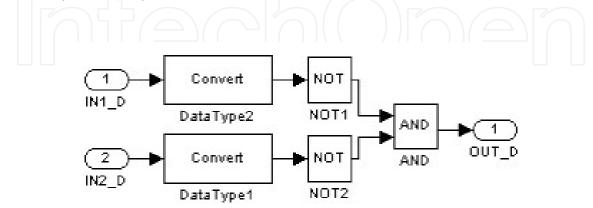

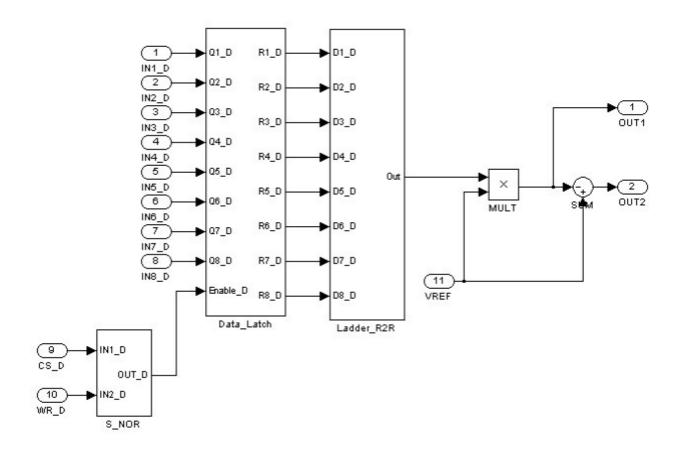

Figure 18 illustrates the circuit capable to represent a selection mode in Table 1. This circuit is minimum using only three logic gates (two NOTs and one AND) and Figure 19 shows a complete AD7524 with a circuit of selection mode, a latch buffer to store last input and Ladder R/2R.

#### 5.3. AD7528

AD7528 is equivalent to two AD7524 converters in a single IC (integrated circuit). The data bus of the AD7528 is also numbered from  $DB_0$  to  $DB_7$ . Each internal converter (DAC A and DAC B) has an individual reference pin. Both can vary ± 25 V. The AD7528 has only three control pins called DACA/DACB,  $CS_B$  and  $WR_B$ . The relationship between control pins is illustrated in the Table 2. At a moment when the AD7528 is in hold mode the last valid input is stored in buffers individually in each internal converter [35].

| O     O     O     Write     Hold       1     0     0     Hold     Write |           |                 |                 |       |       |  |  |

|-------------------------------------------------------------------------|-----------|-----------------|-----------------|-------|-------|--|--|

| 1 0 0 Hold Write                                                        | DACA/DACB | WR <sub>B</sub> | CS <sub>B</sub> | DAC A | DAC B |  |  |

|                                                                         | 0         | 0               | 0               | Write | Hold  |  |  |

| X 1 X Hold Hold                                                         | 1         | 0               | 0               | Hold  | Write |  |  |

|                                                                         | Х         | 1               | Х               | Hold  | Hold  |  |  |

| X X 1 Hold Hold                                                         | Х         | Х               | 1               | Hold  | Hold  |  |  |

**Table 2.** Selection mode pin to control the AD7528 indicating write mode of the DAC A with all pins active low logic level or in write mode DAC B only with pin in DACA/DACB active-high level, any change in the CS<sub>B</sub> pin or WR<sub>B</sub> both converters are in hold mode.

**Figure 17.** Subsystem that represents internal buffers converter AD7524, being formed by components Terminator and Latch output (the  $Q_b$  output from each latch is not used in this work).

Figure 18. Subsystem that represents the logic controller of AD7524 and formed only by using AND and NOT gates.

Figure 19. Complete system AD7524 with all subsystems in Figure 16, 17 and 18.

According to the approach described in [40], we created two identical blocks to represent the R/2R ladder, one for the DAC A and one for the DAC B. Similar to the R/2R ladder subsystem of Figure 16, the subsystem of Figure 16 was used twice in the complete system, i.e. one for each block of the AD7528 internal converter (DAC A and DAC B).

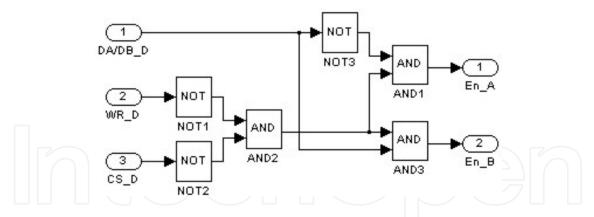

Figure 20 represents the logic controller responsible for the selection of which internal drive will be chosen and if converter is in hold or write mode representing behaviour described in Table 2. This subsystem is basically formed by simple logic gates available in toolbox of Simulink as basic primitive [38].

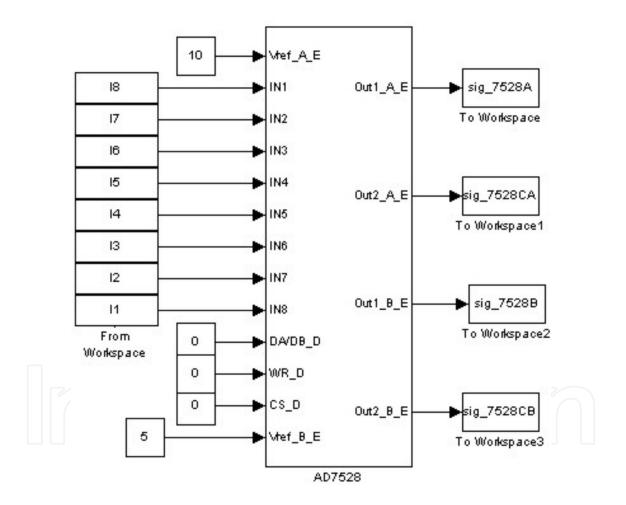

Figure 21 shows the complete AD7528 converter model created in MATLAB / Simulink. In each converter, there are two separate outputs, first one is analog output signal generated by the converter and second one is the difference between analog output and reference voltage. Based on [38] and in order to generate a sine wave signal, MATLAB was able to send the signal to each bit according to its magnitude of the pins of the AD7528 with the "From Workspace" component. Subsequently, the outputs were captured and sent back to MATLAB with the "To Workspace" component to generate the graphic simulation. The reference voltage and the pin configuration for each internal converter were created using "Constant" components (pins DACA/DACB,  $CS_B$  and  $WR_B$ ).

Figure 20. Subsystem that represents logic controller of AD7528 and formed only by using AND and NOT gates.

**Figure 21.** Complete model of AD7528 converter in Simulink with components From Workspace that receive digital signals from MATLAB and sends output back to MATLAB after simulation through To Workspace component.

The DACA/DACB pin could have been used to carry out switching between two converters internally creating two different waveforms from one input. However, as the converters are exactly the same, the kind of simulation does not alter the analysis of signal generated.

#### 5.4. Simulation results of DAC and MS<sup>2</sup>SV conversion results

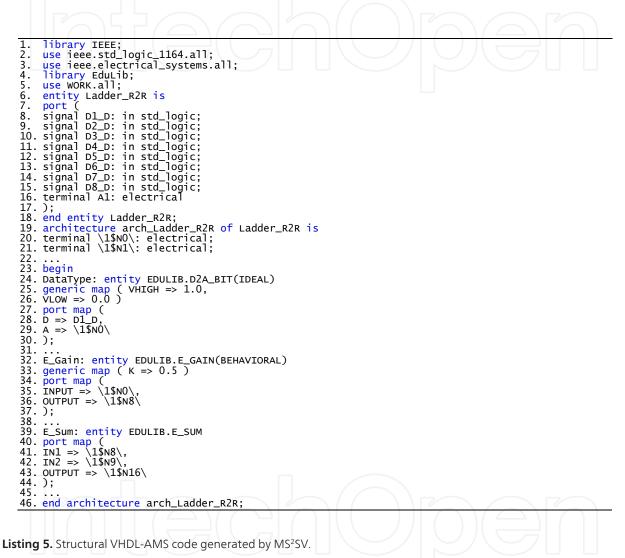

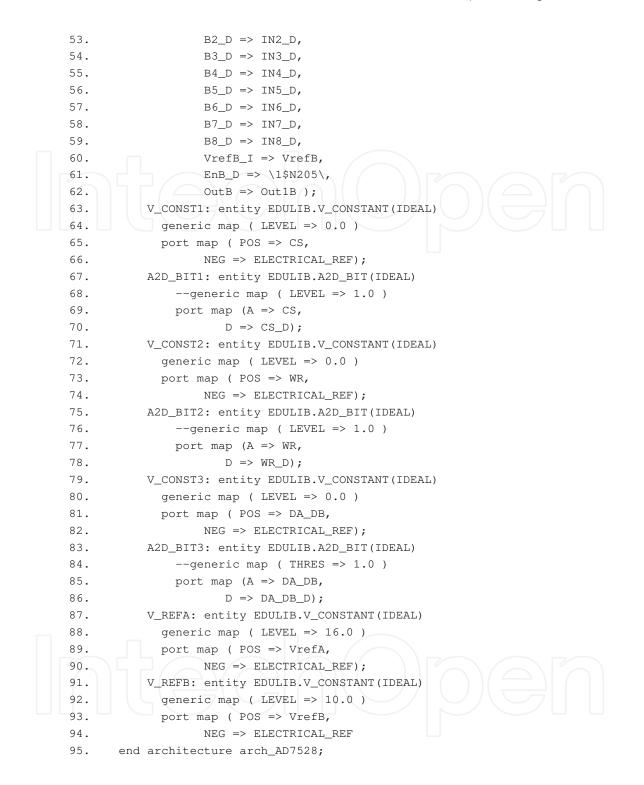

After construction and simulation in MATLAB / Simulink, the MS<sup>2</sup>SV translates model to the SystemVision environment. The hierarchy structure of model in Simulink was maintained in VHDL-AMS codes and MS<sup>2</sup>SV generated the same configuration of components. The Listing 5 is part of code generated by MS<sup>2</sup>SV using ladder R/2R in Figure 16. The remains VHDL-AMS description is listed in Appendix A.

This VHDL-AMS code in Listing 5 has a structural abstraction. It represent the linkage between the components which it has all DAC system, e.g. lines 34-39 represent the ports for Gain block and the linkage between Sum block in lines 41-46 and Data Type Converter block in lines 26-32. The exactly behavior of components are in internal libraries in SystemVision environment named EDULIB (Educational Library).

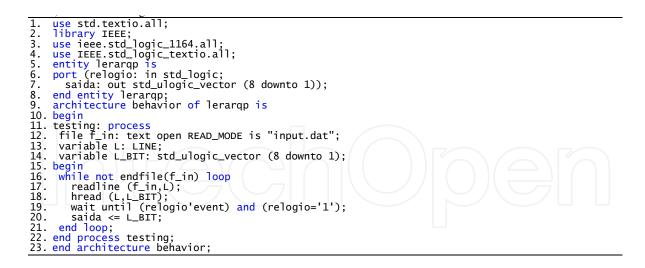

To perform the simulation, SystemVision was used the same input used in MATLAB / Simulink. Thus was created an input file with the extension.*dat*. It was created to an additional VHDL-AMS code to read this file and send the signal each bit input to the converters, as listed in Listing 6.

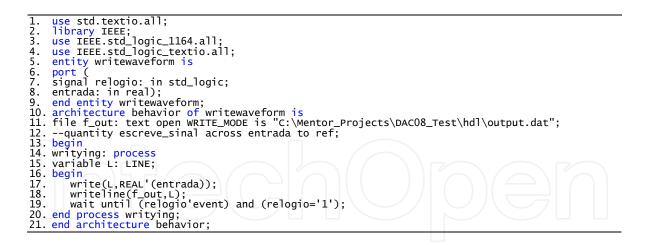

Listing 6. Behavioral VHDL code to read the input simulation file.

In Listing 6 was needed to use a library in order to manipulate files (line 4). It was used for a vector to represent the output which was linked to DAC (line 8). After it was built, a process to read the file and put it into output in lines 13-24 is used.

It was used to save the simulation results in SystemVision in another file with the extension.*dat* so that was possible to analysis the signal generated also in MATLAB, as listed Listing 7.

Listing 7. Behavioral VHDL code to write the output simulation file.

Listing 7 follow the same logic in Listing 6, using the library to manipulate file (line 4), a real signal to represent the input which was linked to DAC (line 9) and a process to read from input and write the file in lines 16-22. By space limits, the remains VHDL-AMS description for AD7524 and AD7528 are listed in Appendix B and C, respectively.

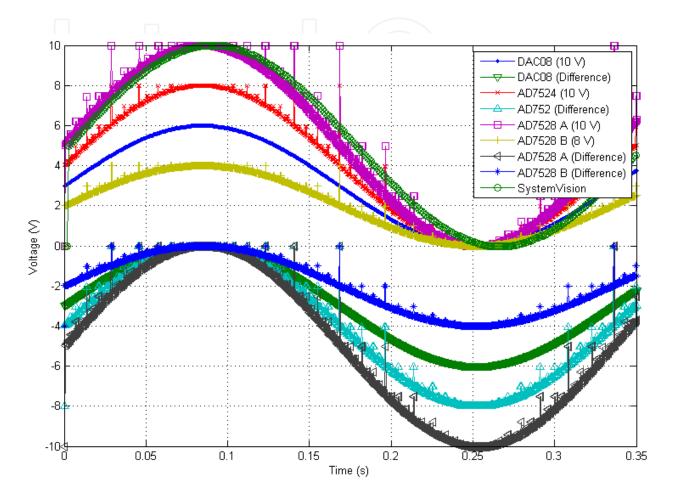

For each case study was used a different reference voltage in simulation: 10V, 8V, 6V and 4V, for DAC08, AD7524, AD7528 A and AD7528 B, respectively. Figure 22 shows the simulation

results for 1 second. The different voltages were used to create a better view waveform in Figure 21. However in the SystemVision environment, only 10V was used for all converters and only one waveform is plotted in Figure 21 as all converters presented the same simulation results. In MATLAB / Simulink, the AD7524, AD7528 A and AD7528 B presented noise in output because the delays in flip-flop of type latch.

**Figure 22.** Result of simulation of all case studies in Simulink and signal from SystemVision in simulation total time of 1 second.

Another difference noted in Figure 22 is low simulation time in SystemVision environment compared with simulation MATLAB / Simulink. This was due to the way in which VHDL-AMS sees the frequency inside the SystemVision environment which is different to MATLAB / Simulink.

#### 5.5. Analysis of simulation in MATLAB / Simulink and VHDL-AMS

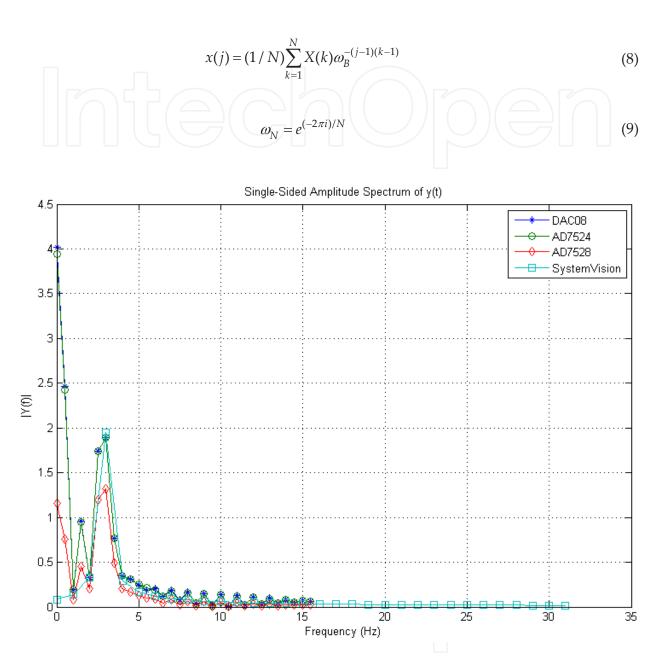

To verify the quality of signal generated, it was made an analysis of signal obtained through simulation. This analysis was performed through power spectral analysis of the signal obtained from discrete Fourier transform (DFT). Figure 23 illustrates amplitude spectrum of y(t) for all case studies, in MATLAB / Simulink and VHDL-AMS. The graph was generated using the discrete Fourier transform described as [41]:

$$X(k) = \sum_{j=1}^{N} x(j) \omega_N^{(j-1)(k-1)}$$

(7)

**Figure 23.** Graph of spectral power all output signals in Simulink and SystemVision with peak in frequency at 2.9297 Hz.

The DC (Direct Current) level of the signal was extracted through shifting the signal along the *y* axis at zero. This resulted in a sine wave signal ranging from-5 to 5 for 10V,-4 to 4 for 8V,-3 to 4 for 6V and-2 to 2 for 4V.

The process of conversion digital to analog represents an interpolation between values of samples provided as inputs, for 20001 points. In this case studies are used linear interpolation,

which points of adjacent samples are connected by a straight line. The system output  $x_r(t)$  is given by:

$$x_r(t) = \sum_{n=-\infty}^{+\infty} x(nT)h(t - nT)$$

(10)

At the same time, the system has unity gain and linear phase. Systems with this frequency response features produce an output that is a shift in the time of input [41]. Importantly, this is a pseudo-conversion to analog, as the conversion happens only while  $V_{ref}$  is constant.

In Figure 23, it is possible to note difference in AD7524, AD7528 A and AD7528 B because of noise in signal. The signal from DAC08 and AD7524 presented a distortion in sine wave showed in Figure 23 too. At the end, the most perfect signal presented by amplitude spectral was the signal from SystemVision environment.

## 6. Generation code methodology of BD<sup>2</sup>XML

The computational tool, called BD<sup>2</sup>XML, is able to read a file block diagram in MATLAB / Simulink and generate a corresponding textual description in XML [42]. A key point of the working methodology is to use a configuration file that allows the user to identify MATLAB / Simulink block to use. This file contains all the blocks readable by the BD<sup>2</sup>XML and the characteristics that are relevant to operation of the blocks. All this information can be extracted by the user from their own MATLAB / Simulink file through the block properties. The file has tokens that are the key point of interpretation. For example, the token & is responsible for the identification of a new block, which has characteristics between the tokens { and }. Since the token # works as a comment in regular language, i.e., every line that has the # is disregarded. If the token # is used before the token & all block is disregarded.

Figure 24 illustrates the functional diagram of BD<sup>2</sup>XML. Initially begins the reading of.*mdl* file in memory. Next is read the configuration file. All of blocks are loaded in memory to compare with the blocks in.*mdl* file. Only afterwards begins the reading of the.*mdl* file. Relevant information is inside.*mdl* file, such as the type of block, values inside the block, linkage between the blocks and some other information is important to create a netlist of circuit. From this point, it is possible to create an XML file with the circuit that can used, and reused in many contexts.

BD<sup>2</sup>XML was developed according to class diagram showed in Figure 25. The classes responsible for creating a logical structure in memory are inherited by classes responsible for read the configuration file and the block diagram file of the MATLAB / Simulink. The **misc** class with routines common to other classes is also inherited by other classes.

Others instances of classes are composition. This facilitates the creation of threads structure in future to speeding of codes performance for generations of multiple objects codes simultaneously. The designer starts the process specifying the diagram which is the target of BD<sup>2</sup>XML.

At first, the configuration file is read into a structure and then the block diagram of the MATLAB / Simulink is read into another structure. A comparison is done block by block to check whether the target block is identifiable. Every block of the configuration file has its own characteristics and the default values for these characteristics. In the case of not being identified in some of the characteristics relevant target block are considered the default values of the configuration file to generate the XML. If any block is not identifiable, XML is generated in the same way discarding that particular block.

Figure 24. Class diagram of the BD2XML tool.

#### 6.1. Conversion results using AD7528

To demonstrate the BD<sup>2</sup>XML, we used the Ladder R/2R case study in Figure 16. Listing 8 is shown a partial description in XML generated by the BD<sup>2</sup>XML from the Ladder R/2R.

The tags **<Diagram>** and **</Diagram>** (lines 2-57) identifying the block diagram. The blocks are identified by tags **<BasicBlock type="..." name="...">** and **</BasicBlock>**, being specified block type and the name used in MATLAB / Simulink, for example, the gain block (lines 30-33).

Figure 25. Class diagram of the BD<sup>2</sup>XML tool.

The data blocks are specified by the tag **<data type="..." value="..."** />. Even in the case of gain, the first tag **data** specifies the kind of signal is used by the block (line 31), e.g., analog. The next type of data (line 32) specifies the gain value that block has.

In the configuration file, the blocks of gain are represented in accordance with the Listing 9 (lines 11-14). The block gain has no specification of input and output ports, because by default a gain always has an input and an output.

The connections between the blocks are made through the tags **<Link>** and **</Link>** (Listing 8, lines 15-20). Inside these tags are two tags named **<OutputPort>** and **</OutputPort>**, that specify the output ports of the block owned by **as="source"** and indicating which is the block output **id="..."**.

The property **id** is understood as the property **name** of the tag **BasicBlock**. Similarly, the entry are specified by the tags **<InputPort>** and **</InputPort>**, and property **as="target"**.

If there are subsystems in the block diagram, they are identified by the tags **<SubSystem** name="..."> and **</SubSystem>**, according to the Listing 8 (lines 7-22, 23-40 and 51-55). All configuration of the subsystem is between two tags and their description is the same as already explained.

```

1.

<?xml version="1.0" encoding="ISO-8859-1"?>

2

<Diagram>

<InBlock name="in1_d">

<data type="mixed"/>

</InBlock>

5.

6.

csubSystem name="datalatch_d">

cdata type="mixed"/>

cdata type="ports" value="9, 8"/>

8.

10. ...

11. <OutBlock name="r7_d">

12. <data type="mixed"/>

13. </OutBlock>

14. ...

15. <Link>

16. <OutputPort as="source" id="q1_d"/>

17. </OutputPort>

18. <InputPort as="target" id="latch1"/>

19. </InputPort>

20. </Link>

22. </SubSystem>

22. </SubSystem>

23. <SubSystem name="ladderr2r">

24. <data type="mixed"/>

25. <data type="ports" value="8, 1"/>

26. <InBlock name="d1_d">

27. <data type="mixed"/>

28. </InBlock>

20

29. ...

30. <BasicBlock type="gain" name="gain">

31. <data type="analog"/>

32. <data type="gain" value="0.5"/>

33. </BasicBlock>

34.

35. <BasicBlock type="sum" name="sum1">

36. <data type="analog"/>

37. <data type="ports" value="2, 1"/>

38. </BasicBlock>

39.

40. </SubSystem>

45. <SubSystem name="snor_d">

46. <data type="mixed"/>

47. <data type="ports" value="2, 1"/>

48.

49. <BasicBlock type="logic" name="and1">

50. <data type="digital"/>

51. <data type="ports" value="2, 1"/>

52. <data type="operator" value="and"/>

53. </BasicBlock>

54....

55. </SubSystem>

56

57. </Diagram>

```

Listing 8. XML description of Ladder R/2R.

Tags to indicate input and output ports of the block diagram are used most commonly in subsystems and they are in accordance with Listing 8 (lines 3-5, 11-13 and 26-28). Tags to represent input ports are specified by **<InBlock name="...">** and **</InBlock>** (lines 3-5).

Similarly, the output ports are specified by the tags **<OutBlock name="…">** and **</OutBlock>** (Listing 8, lines 11-13). In both the tag property **name** identify the block. Also in either case the tag **<data...** /> (Listing 8, lines 4 and 8) are of mixed type, since both blocks can be an input or an output of digital and analog blocks.

All the representation was generated with perfection in one complete file containing all the blocks and subsystems. In this case study AD7528, there are five subsystems representing: the block Ladder R/2R A, Ladder R/2R B, Datalatch A, Datalatch B and Control Logic.

Listing 9. Representation of the blocks in the configuration file used by BD<sup>2</sup>XML.

## 7. Generation code methodology of SF<sup>2</sup>XML

The in this section, the tool called SF<sup>2</sup>XML is presented which is capable to capture relevant information in the Stateflow environment and generate a corresponding description in XML [43]. The resulting file conversion is also in accordance with international standards of default file in case the SCXML proposed by W3C [4].

The SF<sup>2</sup>XML has four classes of objects, an object that makes up the logical structure of storage memory at runtime, an object of reading the file MATLAB/Simulink and extraction of relevant information, an object to generate the syntactic and semantic file XML and other objects to make interfacing with the user. The class diagram to SF<sup>2</sup>XML is shown in Figure 26. In this figure, it is possible to see that the only difference between SF<sup>2</sup>XML and SF<sup>2</sup>HDL is the highlighted **xml\_file** object. Similarly, the functional diagram in Figure 5, is the same to SF<sup>2</sup>XM apart from the files generated.

SF<sup>2</sup>XML is also able to identify sub-finite state machine, so it has recursive methods for hierarchical finite state machine clustering automatically, which generates a certain economy of code and maintenance. There is this feature inside SF<sup>2</sup>HDL too, but a hierarchical FSM can generate instable behavioral in a same file. It could better if SF<sup>2</sup>HDL would generate different files for different finite state machines. SF<sup>2</sup>XML has the follow algorithm, which can be understood for SF<sup>2</sup>HDL:

- 1. Read the MATLAB / Simulink file and identify the FSM;

- 2. Store the state or transitions and its information;

- **a.** If the state has a sub-FSM store the first transition in this sub-FSM, otherwise go to step 2(b).

- **b.** Verify which type this FSM is (Mealy or Moore);

- 3. Start write XML file;

- **a.** a. Seeking relationship between states of the same hierarchical level and which state is the first in highest level;

- **b.** Write the state tags, the transition related to this states;

- **c.** If there is a sub-FSM decrease the level hierarchical and go to step 3(a), otherwise go to step 3(d);

- **d.** While there is a state such that is associated with a transition go to step 3(a).

- 4. Return the XML file.

#### 7.1. Conversion results of HDB3 line code

The tool was able to accurately generate an XML representation corresponding to the diagram shown in Figure 3. Every XML description is according to SCXML specification. Listing 10 below displays the entire description in XML generated by SF<sup>2</sup>XML.

Figure 26. Class diagram of the SF<sup>2</sup>XML tool.

```

1. <?xml version="1.0" encoding="ISO-8859-1"?>

2. <scxml version="1.0" xmlns="http://www.w3.org/2005/07/scxml" initialstate="0">

3. <state id="0">

4. <transition event="INPUT=1">

5. <target next="1" />

6. <assign expr="0UTPUT=1" />

7. </transition>

8. <transition event="INPUT=0">

9. <target next="0" />

10. <assign expr="0UTPUT=0" />

11. </transition>

12. </state>

13. <state id="1">

14. <transition event="INPUT=0">

15. <target next="2" />

16. <assign expr="0UTPUT=0" />

11. </transition event="INPUT=0">

15. <target next="2" />

16. <assign expr="0UTPUT=0" />

17. </transition>

18. </state>

19. ...

20. </scxml>

```

Listing 10. XML code representing the finite state machine of HDB3.

It is important to highlight that states assumed a decimal representation continuously, regardless of whether the state is within another state or not.

Line 1 of Listing 10 specifies that it is an XML file, the XML version and encoding used. The tags of lines 2 and 20, specify the start and end of the finite state machine. In line 2 is also specified the version of SCXML used, the name for the XML document (xmlns) and the initial state of the finite state machine (**initialstate="0**"). The tag **<state id="..."** and **</state>** specifies the state and its identifier (lines 3, 12, 13, 18). The tags **<transition event="..."** and **</transition>** to specify a transition that will occur according to a particular event, e.g. " **INPUT=1**" (line 4). If the transition occurs, the tag **<target next="..."** /> specifies the next state of the FSM according to its identifier. The tag **<assign expr="OUTPUT=..."** /> assigns a new value to the output attribute **expr**. If there are hierarchically nested state, states are chained between the tags **<state id="..."** and **</state>**. However, the initial state is specified by internal tags **<initial>** and **</initial>** within a transition indicating to the initial state.

### 8. Conclusion

The SF<sup>2</sup>HDL program makes the translation of finite state machine, but it does not perform circuit optimization. Hence, it also needs a translation into a file that serves as input to TABELA program that is able to perform this work.

The SF<sup>2</sup>HDL program does not make optimal state assignment to the state machine as well. Thus, it is necessary to use another tool to do that task. In this way circuit synthesis can be really optimize using all the potentialities of developed tools. Future work will extend this tool to also realize the translation of finite state machines for the structural VHDL and Verilog code.

The use of CAD tools and a top-down methodology is a reality that is present in the most electronic circuit design projects, and the development of new computational tools to aid in

project implementation is highly desirable, because the range of CAD tools used introduces incompatibilities that can be time consuming and costly in translating between them. Hence, there is the need for suitable tools to be able to translate models between different representations.

The SF<sup>2</sup>HDL tool was tested in several cases of finite state machines and all have been simulated and synthesized in Quartus II environment and Cyclone II FPGA model EP2C20F484C7, respectively.

For the case study of HDB3 code described in this chapter, SF<sup>2</sup>HDL program was very effective for translation code modeled on Stateflow, a computational low cost, being accurate in VHDL generation code and the input file for TABELA program corresponding with another programs.

Thus, this research generated a tool that allows to the designers to model a finite state machine at high level of abstraction and obtain a corresponding VHDL model which can be synthesized on synthesis tools available commercially. It is also important to say this new translation tools interact with several other tools developed by research group with TABELA program, creating this way a digital synthesis environment.

The MS<sup>2</sup>SV tool proved convenient to use as it allows for the creation of multiple libraries for different projects and also recycle the libraries for use in others projects. This allows a significant savings of time and hence costs.

By analysing power spectral of a discrete-time signal, one can say that the output signals in MATLAB / Simulink and VHDL-AMS are almost identical. This fact allows us to change our vision about the abstraction levels and details in modelling. Even in the same environment (MATLAB / Simulink) we have difference in spectral signal. If the system be simulating in another environment, we will also have different simulations.

The conversion to XML (using BD<sup>2</sup>XML) is convenient because the portability of the language allows a wide applicability of the proposed methodology, e.g., documentation, level synthesis of hardware or software, web publishing, use of XML simulators and as object code for future work. This is the same when using SF<sup>2</sup>XML, which it use a standardized description in SCXML.

The use of the intermediate code (like XML) is very important since it can be used in frameworks generation and optimization of other types of coding. As an example, hardware description languages like VHDL-AMS, Verilog-AMS, SystemC, etc. Or even reprogrammable devices that have analog and digital blocks and PSoC (Programmable System-on-Chip).

This point highlights the importance to explore more alternatives and standard methodologies of electronic circuit design. Nevertheless, our methodology and tools need further investigation and analysis to consider the need for the development of larger and more complex systems.

## Appendix A- DAC08 converter description in structural VHDL-AMS

```

1.

library IEEE;

2.

use ieee.std_logic_1164.all;

З.

use ieee.electrical_systems.all;

4.

library EduLib;

use WORK.all;

5.

6.

entity DAC08 is

7.

end entity DAC08;

architecture arch_DAC08 of DAC08 is

8.

9.

terminal \1$N39\: electrical;

10.

terminal \1$N41\: electrical;

11.

signal DIn1_D: std_logic;

12.

signal DIn2_D: std_logic;

signal DIn3_D: std_logic;

13.

14.

signal DIn4_D: std_logic;

signal DIn5_D: std_logic;

15.

signal DIn6_D: std_logic;

16.

17.

signal DIn7_D: std_logic;

18.

signal DIn8_D: std_logic;

19.

terminal Vref: electrical;

20.

terminal Out1: electrical;

21.

begin

22.

Ladder_R2R: entity WORK.Ladder_R2R(arch_Ladder_R2R)

23.

port map (

24.

D1_D => DIn1_D,

25.

D2_D \implies DIn2_D,

D3_D \implies DIn3_D,

26.

D4_D \implies DIn4_D,

27.

D5_D \implies DIn5_D,

28.

29.

D6_D \implies DIn6_D,

30.

D7_D \implies DIn7_D,

31.

D8_D \implies DIn8_D,

32.

A1 => 1%N39

);

33.

E_MULT: entity EDULIB.E_MULT

34.

port map (

IN1 => 1$N39,

35.

IN2 => Vref,

36.

37.

OUTPUT => Out1

);

38.

V_VREF: entity EDULIB.V_CONSTANT(IDEAL)

39.

generic map ( LEVEL => 10.0 )

port map ( POS => Vref,

40.

41.

NEG => ELECTRICAL_REF);

42.

end architecture arch_DAC08;

```

The complete VHDL-AMS code is listed below for DAC08 case.

# Appendix B- AD7524 converter descriptions in structural VHDL-AMS

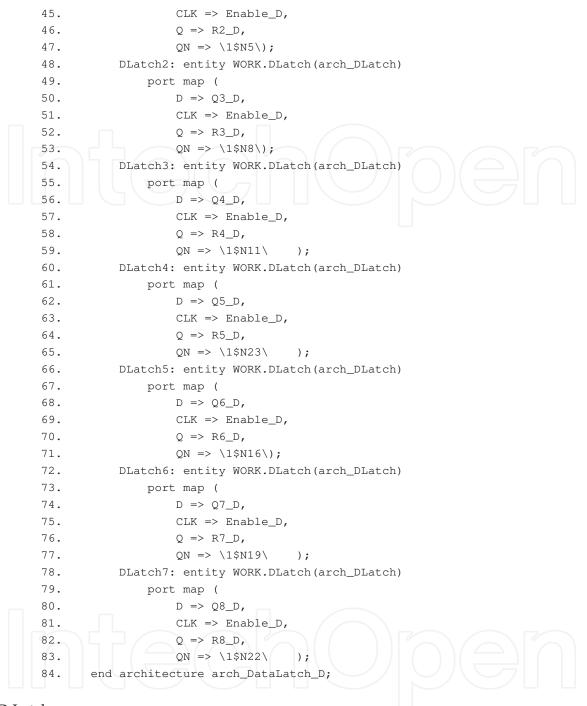

The complete VHDL-AMS code is listed below for Data\_Latch subsystem, SNOR subsystem and AD7524 converter.

• Data\_Latch

```

library IEEE;

1.

use ieee.std_logic_1164.all;

2.

з.

use ieee.electrical_systems.all;

4.

library EduLib;

5.

use WORK.all;

entity DataLatch_D is

6.

7.

port (

8.

signal Q1_D: in std_logic;

9.

signal Q2_D: in std_logic;

10.

signal Q3_D: in std_logic;

11.

signal Q4_D: in std_logic;

12.

signal Q5_D: in std_logic;

13.

signal Q6_D: in std_logic;

14.

signal Q7_D: in std_logic;

15.

signal Q8_D: in std_logic;

16.

signal Enable_D: in std_logic;

17.

signal R1_D: out std_logic;

18.

signal R2_D: out std_logic;

signal R3_D: out std_logic;

19.

20.

signal R4_D: out std_logic;

21.

signal R5_D: out std_logic;

22.

signal R6_D: out std_logic;

23.

signal R7_D: out std_logic;

signal R8_D: out std_logic );

24.

25.

end entity DataLatch_D;

26.

architecture arch_DataLatch_D of DataLatch_D is

27.

signal \1$N2\: std_logic;

signal \1$N5\: std_logic;

28.

29.

signal \1$N8\: std_logic;

signal \1$N11\: std_logic;

30.

31.

signal \1$N23\: std_logic;

32.

signal \1$N16\: std_logic;

signal \1$N19\: std_logic;

33.

34.

signal \1$N22\: std_logic;

35.

begin

36.

DLatch: entity WORK.DLatch(arch_DLatch)

37.

port map (

38.

D => Q1_D,

39.

CLK => Enable_D,

40.

Q => R1_D,

QN => 1$N2);

41.

DLatch1: entity WORK.DLatch(arch_DLatch)

42.

43.

port map (

44.

D => Q2_D

```

```

• D Latch

```

1. LIBRARY IEEE; 2. USE ieee.std\_logic\_1164.all; 3. USE ieee.electrical\_systems.all; 4. LIBRARY edulib; USE work.all; 5. entity DLatch is 6. 7. port ( 8. signal D: in std\_logic; 9. signal CLK: in std\_logic;

```

10.

signal Q: out std_logic;

11.

signal QN: out std_logic );

12.

end entity DLatch;

architecture arch_DLatch of DLatch is

13.

14.

begin

15.

process(D,CLK)

16.

begin

17.

if clk = '1' then

18.

Q <= D;

19.

QN <= not D;

20.

end if;

21.

end process;

22.

end architecture arch_DLatch;

```

```

• SNOR

```

```

1.

library IEEE;

2.

use ieee.std_logic_1164.all;

З.

use ieee.electrical_systems.all;

library EduLib;

4.

use WORK.all;

5.

entity SNOR_D is

6.

7.

port (

signal IN1_D: in std_logic;

8.

9.

signal IN2_D: in std_logic;

10.

signal OUT_D: out std_logic );

11.

end entity SNOR_D;

12.

architecture arch_SNOR_D of SNOR_D is

13.

signal \1$N63\: std_logic;

14.

signal \1$N64\: std_logic;

15.

begin

16.

G_AND1: entity EDULIB.AND2

17.

port map (

18.

IN1 => 1%N63,

IN2 => 1$N64,

19.

20.

OUTPUT => OUT_D);

G_NOT1: entity EDULIB.INVERTER

21.

22.

port map (

23.

INPUT => IN1_D,

OUTPUT => 1$N63);

24.

25.

G_NOT2: entity EDULIB.INVERTER

26.

port map (

27.

INPUT => IN2_D,

28.

OUTPUT => 1$N64);

29.

end architecture arch_SNOR_D;

```

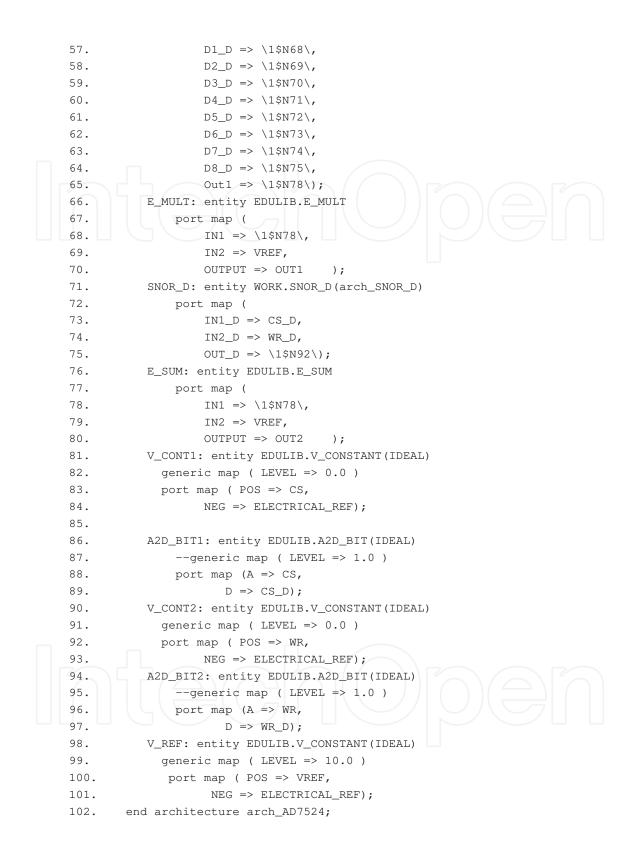

#### • AD7524

library IEEE;

use ieee.std\_logic\_1164.all;

use ieee.electrical\_systems.all;

use ieee.radiant\_systems.all;

```

5.

library EduLib;

use WORK.all;

6.

entity AD7524 is

7.

8.

end entity AD7524;

architecture arch_AD7524 of AD7524 is

9.

10.

signal IN1_D: std_logic;

11.

signal IN2_D: std_logic;

12.

signal IN3_D: std_logic;

13.

signal IN4_D: std_logic;

signal IN5_D: std_logic;

14.

signal IN6_D: std_logic;

15.

16.

signal IN7_D: std_logic;

17.

signal IN8_D: std_logic;

signal CS_D: std_logic;

18.

signal WR_D: std_logic;

19.

terminal VREF: electrical;

20.

21.

terminal OUT1: electrical;

22.

terminal OUT2: electrical;

23.

signal \1$N68\: std_logic;

24.

signal \1$N69\: std_logic;

signal \1$N70\: std_logic;

25.

26.

signal \1$N71\: std_logic;

27.

signal \1$N72\: std_logic;

28.

signal \1$N73\: std_logic;

29.

signal \1$N74\: std_logic;

signal \1$N75\: std_logic;

30.

31.

terminal \1$N78\: electrical;

32.

terminal WR: electrical;

33.

terminal CS: electrical;

34.

signal \1$N92\: std_logic;

35.

begin

DataLatch_D: entity WORK.DataLatch_D(arch_DataLatch_D)

36.

37.

port map (

38.

Q1_D => IN1_D,

39.

Q2_D \implies IN2_D,

40.

Q3_D \implies IN3_D,

41.

Q4_D \implies IN4_D,

42.

Q5_D => IN5_D,

43.

Q6_D \implies IN6_D,

Q7_D => IN7_D,

44.

Q8_D => IN8_D,

45.

46.

Enable_D => 1%N92,

47.

R1_D \implies \1\$N68

48.

R2_D \implies 1\$N69,

R3_D \implies 1\$N70

49.

50.

R4_D \implies 1\$N71

51.

R5_D \implies 1\$N72

52.

R6_D \implies 1\$N73,

53.

R7_D \implies 1\$N74

R8_D => (1$N75);

54.

55.

LadderR2R: entity WORK.LadderR2R(arch_LadderR2R)

56.

port map (

```

### Appendix C- AD7528 converter descriptions in structural VHDL-AMS

The complete VHDL-MAS code is listed for Control\_Logic and AD7528 converter.

#### • Control\_Logic

```

1.

library IEEE;

2.

use ieee.std_logic_1164.all;

3.

use ieee.electrical_systems.all;

library EduLib;

4.

use WORK.all;

5.

6.

entity ControlLogic_D is

7.

port (

8.

signal DADB_D: in std_logic;

9.

signal WR_D: in std_logic;

10.

signal CS_D: in std_logic;

signal EnA_D: out std_logic;

11.

12.

signal EnB_D: out std_logic );

13.

end entity ControlLogic_D;

14.

architecture arch_ControlLogic_D of ControlLogic_D is

15.

signal \1$N9\: std_logic;

signal \1$N2\: std_logic;

16.

17.

signal \1$N3\: std_logic;

18.

signal \1$N4\: std_logic;

19.

begin

20.

G_AND1: entity EDULIB.AND2

21.

port map (

22.

IN1 => 1%N2,

IN2 => 1%N3,

23.

24.

OUTPUT => 1$N9);

25.

G_AND2: entity EDULIB.AND2

26.

port map (

27.

IN1 => 1$N4,

28.

IN2 => 1$N9,

29.

OUTPUT => EnA_D);

30.

G_AND3: entity EDULIB.AND2

31.

port map (

32.

IN1 => DADB_D,

33.

IN2 => 1$N9,

34.

OUTPUT => EnB_D);

35.

G_NOT1: entity EDULIB.INVERTER

36.

port map (

37.

INPUT => WR_D,

OUTPUT => \1$N2\);

38.

39.

G_NOT2: entity EDULIB.INVERTER

40.

port map (

41.

INPUT => CS_D,

OUTPUT => 1%N3);

42.

G_NOT3: entity EDULIB.INVERTER

43.

44.

port map (

INPUT => DADB_D,

45.

46.

OUTPUT => 1%N4);

47.

end architecture arch_ControlLogic_D;

```

• AD7528

```

library IEEE;

1.

2.

use ieee.std_logic_1164.all;

3.

use ieee.electrical_systems.all;

4.

library EduLib;

use WORK.all;

5.

entity AD7528 is

6.

7.

end entity AD7528;

architecture arch_AD7528 of AD7528 is

8.

9.

signal IN1_D: std_logic;

signal IN2_D: std_logic;

10.

signal IN3_D: std_logic;

11.

12.

signal IN4_D: std_logic;

13.

signal IN5_D: std_logic;

14.

signal IN6_D: std_logic;

15.

signal IN7_D: std_logic;

16.

signal IN8_D: std_logic;

17.

signal DA_DB_D: std_logic;

18.

signal WR_D: std_logic;

19.

signal CS_D: std_logic;

20.

terminal CS: electrical;

21.

terminal WR: electrical;

22.

terminal DA_DB: electrical;

23.

terminal VrefA: electrical;

24.

terminal VrefB: electrical;

25.

terminal Out1A: electrical;

terminal Out1B: electrical;

26.

27.

signal \1$N204\: std_logic;

28.

signal \1$N205\: std_logic;

begin

29.

30.

ControlLogic_D: entity WORK.ControlLogic_D(arch_ControlLogic_D)

31.

port map (

32.

DADB_D => DA_DB_D,

33.

WR_D => WR_D,

34.

CS_D \implies CS_D,

EnA_D \implies \1\$N204,

35.

EnB_D \implies 1\$N205

36.

);

37.

DAC_A: entity WORK.DAC_A(arch_DAC_A)

38.

port map (

39.

A1_D \implies IN1_D,

A2_D => IN2_D,

40.

A3_D \implies IN3_D,

41.

42.

A4_D \implies IN4_D,

A5_D \implies IN5_D,

43.

A6_D \implies IN6_D,

44.

A7_D \implies IN7_D,

45.

46.

A8_D \implies IN8_D,

47.

VrefA_I => VrefA,

48.

EnA_D \implies \1\$N204

OutA => Out1A

49.

);

50.

DAC_B: entity WORK.DAC_B(arch_DAC_B)

51.

port map (

B1_D => IN1_D,

52.

```

### Acknowledgements

The authors would like to thank to National Council for Scientific and Technological Development (CNPq, process: 141744/2010-3 and 309023/2012-2).

### Author details

Tiago da Silva Almeida<sup>1</sup>, Ian Andrew Grout<sup>2</sup> and Alexandre César Rodrigues da Silva<sup>1</sup>

1 Univ Estadual Paulista, UNESP, Brazil

2 University of Limerik, UL, Ireland

# References

- [1] Gerstlauer A, Haubelt C, Pimentel A D, Stefanov T P, Gajski D D, Teich J. Electronic System-Level Synthesis Methodologies. Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on 2009; 28(10)1517-1530.

- [2] Gajski D D, Kuhn R H. Introduction new VLSI tools. IEEE Computer 1983; 16(12) 11-14.

- [3] Riesgo T, Torroja Y, Torre E. Design methodologies based on hardware description languages. IEEE Transactions on Industrial Electronics 1999; 46(1) 3-12.

- [4] Auburn R, Barnett J, Bodell M, Raman T. State chart XML (SCXML): State machine notation for control abstraction 1.0. http://www.w3.org/TR/2005/WDscxml-20050705/ (accessed 5 September 2013).