# We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

6,900

185,000

200M

Downloads

154

Countries delivered to

Our authors are among the

$\mathsf{TOP}\:1\%$

most cited scientists

12.2%

Contributors from top 500 universities

WEB OF SCIENCE™

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected.

For more information visit www.intechopen.com

# HaLoS – Integrated RF-Hardware Components for Ultra-Wideband Localization and Sensing

Stefan Heinen, Ralf Wunderlich, Markus Robens, Jürgen Sachs, Martin Kmec, Robert Weigel, Thomas Ußmüller, Benjamin Sewiolo, Mohamed Hamouda, Rolf Kraemer, Johann-Christoph Scheytt and Yevgen Borokhovych

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/54987

#### 1. Introduction

Ultra-Wideband (UWB) sensors exploit very weak electromagnetic waves within the lower microwave range for sounding the objects or processes of interest. The interaction of electromagnetic waves with matter provides interesting options to gain information from a great deal of different scenarios. To mention only a few, it enables the assessment of the state of building materials and constructions, the investigation of biological tissue, the detection and localization of persons buried by rubble after an earthquake or unauthorized people hidden behind walls, and much more [1]. The advantage of such methods consists in their non-destructive and continuously running measurement procedure which may work at high speed and in contactless fashion.

Sensors applying electromagnetic interactions with the test object have been in use for a long time. However, most of such sensors are restricted to a relatively narrow bandwidth and, consequently, they can provide only a small amount of information about the test object. Sophisticated data processing supposed, UWB sensors may be able to provide more information and, therefore, to reduce ambiguities which are inherently part of indirect measurement methods such as electromagnetic sensing.

Depending on the actual tasks, the requirements on the sensing system may be quite different, such as the optimum operational frequency band, measurement speed, sensitivity, system costs, reliability, power consumption etc. There are several UWB sensing principles known, each having specific advantages and disadvantages. Generally, one can state that the usability of UWB-sensors will be largely improved with increasing degree of system

integration regardless of the sensor principle. The HaLoS-project addresses this topic by investigating general purpose UWB sub-modules like amplifiers, ADCs, fast processing units etc. as well as an integration-friendly sensor concept based on ultra-wideband pseudonoise codes.

The chapter is organized as follows. First, the most important performance figures of UWB sensors are introduced. Second, we give an overview of various UWB-sensor principles recently in use and explain the UWB pseudo-noise concept. Then, we address some specific topics like wideband receiver circuits, transmitter circuits and high-speed data capture. Finally, some aspects of monolithically integrated UWB-sensors are discussed.

#### 2. Properties and basic concepts of UWB-sensors

#### 2.1. Key figures of UWB-sensors

The UWB sensor configuration may be determined by demands which are guided by two different and partially conflicting aspects. On the one hand, these are the UWB radiation rules, and on the other one, we have to respect the physical constraints of the sensing problem. The radiation rules, which are not unique within different regions of the world, mainly limit spectral power emission, restrict the operation frequency band and require sounding signals of large instantaneous bandwidth. Seen from a physical point of view, we need an adequate operational frequency band which provides reasonable interaction between the sounding signal and the object of interest. This may lead to conflicting situations with the radiation rule for sensing tasks requiring wave penetration like throughwall radar or medical imaging. Thus, one has to search a proper compromise in the case of frequency mask violation. Though UWB sensors are banned from long-range applications due to low-radiation power, they promote biological and medical sensing since the target exposition is harmless. Furthermore, the interaction between sounding wave and target is based on linear phenomena. Hence, the sounding bandwidth may be provided instantaneously (complying with FCC or ECC radiation rules) or sequentially (violating these radiation rules) without affecting the measurement results as long as the scenario under test behaves stationary during the measurement. This paper is focused on techniques for information capture by exploiting electromagnetic interactions. Hence, we do not exclude sensor principles or frequency bands violating UWB radiation rules from our further discussions.

Spectral band and related parameters: As frequency diversity is a key issue of unambiguous information gathering by electric sensors, the widths and the occupation density of the spectral sounding band is of major interest. For the sake of brevity, we will deal here only with baseband signals (see [2] for deeper discussions) which we characterize by their twosided bandwidth *B* that can be linked to typical time domain parameters:

Here,  $t_w$  represents the width of a pulse, and  $au_{coh}$  is the coherence time of a random or pseudo-random signal (i.e. the width of the auto-correlation function). The occupation density of the frequency band is given by the line spacing  $\Delta f$  which is either determined by the repetition rate  $f_0$  of a periodic sounding signal ( $t_p$  - period duration) or via the Fourier Transform by the observation interval T of non-periodic signals:

$$\Delta f = \begin{cases} f_0 = t_p^{-1} & \text{periodic signal} \\ T^{-1} & \text{non-periodic signal} \end{cases}$$

(2)

As non-periodic signals are quite unusual in UWB sensing, we will avoid discussing them. The line spacing  $\Delta f$  gives the frequency resolution of the sensor or it determines the maximum observable length  $T_W = \Delta f^{-1}$  of the impulse response g(t) of a scenario under test. If g(t) does not settle down within  $T_w = t_p$ , we have to anticipate time aliasing.

In the case of UWB radar sensing, we can convert (1) and (2) into corresponding spatial parameters. One of them assigns the range resolution  $\delta_r$ , i.e. the capability of the radar to separate two close point targets of identical reflectivity. We will refer to the usual relation (c - wave velocity):

$$\delta_{r} \approx \frac{c}{2 \, B} \approx \begin{cases} \frac{1}{2} \tau_{coh} \, c & \text{for time stretched signal} \\ \frac{1}{2} t_{w} \, c & \text{for pulse shaped signal} \end{cases}$$

(3)

even if it should be considered with care. The relation originates from narrowband radar whose sounding signal suffers not from signal deformation neither by reflection at small bodies nor by antenna transmission. In contrast to that, a UWB signal bouncing a point scatterer will sustain a twofold differentiation and further deformations due to the antennas. The unambiguous rage  $r_{ua}$  of the UWB radar relates to the signal repetition by:

$$r_{ua} = \frac{1}{2} t_P c \tag{4}$$

Recording time: UWB sensors provide, depending on their principle of work, either the impulse response function (IRF) or the frequency response function (FRF) of the scenario under test. The time needed to collect all data for one IRF or FRF (including synchronous averaging of repetitive measurements) we call recording time  $T_R$ . Non-stationary test scenarios limit the recording time either to

$$T_R \ B_{SC} \le \frac{1}{2} \tag{5}$$

$\ensuremath{\beta_{SC}}$  - physical (single-sided) bandwidth of the scenario variation

or to

$$T_R \not \underline{B} \le \frac{c}{2|v|} \tag{6}$$

|v| - radial speed of a target

Equation (5) simply indicates the Nyquist theorem telling us that the refresh rate of the measurement  $R = T_R^{-1}$  must be twice the bandwidth of the process to be observed. Relation (6) refers to the Doppler-effect. It is evoked from moving targets causing an expansion or compression of the scattered signal. If such signals are accumulated (by correlation or/and synchronous averaging) over a too long duration, they de-correlate resulting in an amplitude degradation of the receiving signal and finally in the loss of the target. Equation (6) should not be confused with Doppler ambiguity which is not relevant for UWB sensing.

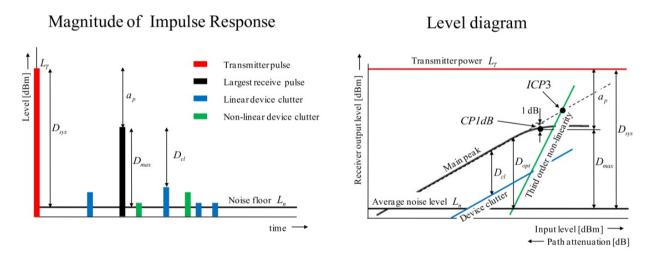

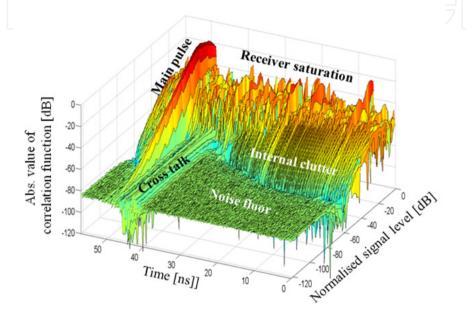

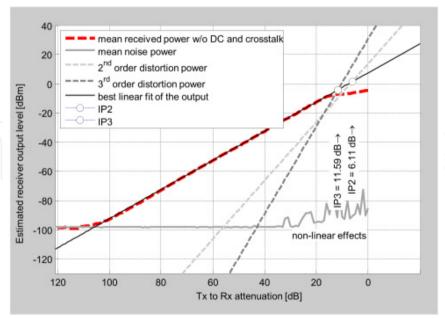

Figure 1. Stylized impulse response (left) and level diagram (right) of an UWB sensor

Dynamic range: Another group of important features relates to the sensitivity of weak signal detection. For illustration, we consider Fig. 1. The illustration on the left-hand side symbolizes the response of a single target. The red line represents the transmitter pulse (or also the auto-correlation function of a wideband CW-signal), and the black line is the target return which should be the only signal visible on the receiver screen. Obviously, we may detect many signal components hampering the detection of weak targets if there are some. These perturbing signals are random noise (electronic and quantization noise) and device internal clutter. It depends on the receiving signal and may be caused by the linear (internal mismatch, cross-coupling, frequency-dependent transmission behavior of electronic compounds) and non-linear effects (e.g. device saturation). Fig. 1 (right) depicts typical dependences of the perturbations from the level of the receiving signal. Based on this, we can derive various dynamic ranges:

- Clutter-free dynamic range  $D_{cl}$ : It refers to the level difference between receiving signal and the strongest internal clutter peak.  $D_{cl}$  determines the sensitivity to detect weak targets in the presence of a strong one, and also the strength of artefacts in radar images.

- Optimum dynamic range  $D_{opt}$ : Internal clutter caused by linear effects can be removed by sensor calibration as used in network analyzer measurements. A perfect calibration supposed, the erroneous signals are curtailed now by the noise floor and non-linear distortions. Hence, we get optimum conditions for a large dynamic range at the interception of noise and third-order distortion lines.

- *Maximum dynamic range*  $D_{max}$ : It is defined by the difference between 1 dB compression point and noise level. Its value gives a hint on the sensitivity to detect moving targets of weak reflectivity. In many cases, the strongest backscatter signals are caused by static objects. As long as the UWB sensor is not moved, these signals and their clutter contributions are stationary so that they may be simply removed by high-pass filtering in observation time. Hence, the detectability of moving targets is only limited by the noise level. The maximum dynamic range can be roughly estimated using the following relation [2]:

$$D_{\text{max}} \approx \frac{2 \eta_r T_R V_{1\text{dB}}^2}{k T_0 CF^2 F R_0} = \frac{3 \eta_r T_R B_2^2 E^{NOB}}{CF^2}$$

(7)

$\eta_{r}$  - receiver efficiency;  $T_{R}$  - recording time;  $V_{\rm 1dB}$  - input voltage at 1 dB compression point (before correlation); k - Boltzmann constant;  $T_0$  - temperature; CF - crest factor; F- noise factor;  $R_0$  - receiver input impedance;  $\underline{B}$  - receiver bandwidth; ENOB - effective number of bits (before correlation).

The left part of eq. (7) applies performance parameters of analog receivers while the right part deals with the global effective number of bits merging the performance of analog and digital receiver components.

System performance  $D_{sus}$ : It relates the transmitter level to the noise level. Hence, it is given by the maximum dynamic range and the attenuation of the strongest transmission path.

Time and frequency errors: While above mentioned device characteristics refer to ordinate quantities of a signal representation, the following features quantify the quality of the abscissa representation, i.e. the time or frequency axis. Related to this, we can observe systematic deviations like non-linear frequency or time axis representations resulting in non-equidistant sampling and distortions of frequency-time conversions. Random errors of the time or frequency axis representation, we call jitter or phase noise in the case of short time variation and drift for long term variations. Jitter (respectively phase noise) causes signal-dependent noise which is elevated at signal edges and disappears at flat signal parts. Jitter limits the performance of super resolution techniques and reduces the sensor sensitivity to detect weak scattering targets in the vicinity of strong reflectors.

*Efficiency*: The term efficiency can be seen under different aspects. We will consider three of them here.

Receiver efficiency  $\eta_r$  (see also (7)): The receiver efficiency describes the capability of the receiver to exploit the incident signal energy. As the receiving signals are usually quite weak due to the restrictions of transmission power, one has to attach great importance to the receiver efficiency. It is determined by losses in the receiver front end, e.g. the insertion loss of filters or conversion loss of mixers or sampling gates. However, dead times for energy accumulation due to filter settling, incomplete data capture by reason of sub-sampling or incomplete exploitation of captured date due to serial instead of parallel data processing are much more important. Thus, the efficiency of recent UWB receivers is often reduced to values below 1 ‰ or even less which provides some potential for further improvements.

*Figure of Merit FoM*: In general terms, the Figure of Merit expresses the expense of energy which is required to achieve a certain effect. Two examples shall illustrate the approach. The first one deals with a Nyquist analog-to-digital converter which is aimed to digitize data with a certain rate  $f_s$ . An obvious definition of the Figure of Merit can be:

$$FoM_{flashADC} = \frac{P}{2^{ENOB} f_s} [J/conversion]$$

(8)

P - power dissipation of the ADC; ENOB - effective number of bits of the ADC;  $f_s$  - sampling rate

Typical FoM-values for high speed ADCs are to be found at about 10 pJ/conversion. Hence, the power requirement of a 6 bit ADC @ 10 GHz is in the order of 6 W.

The second example relates to an amplifier whose FoM-value is expressed by:

$$FoM_{ampl} = \frac{P}{g \not B CP_{1dB}} \left[ Hz^{-1} \right]$$

(9)

P - power dissipation of the amplifier; g - power gain in linear units; B - bandwidth;  $CP_{1dB}$  - 1 dB compression point in linear units.

The FoM-approach can be extended to further electronic components and numerical algorithms as well. We can conclude two things from FoM-philosophy. Firstly, the designer of an electronic sub-system or algorithm has to achieve a reasonable small FoM-value with his design. Secondly, the designer of the whole system gets some hints on the feasibility of his system conception and the scope of its features if the corresponding FoM-values are known.

Data throughput: UWB sensors provide lots of data particularly if they are assigned for MIMO-systems and high measurement rate. In order to conserve energy, memory space and data transmission capacity, the sensors should not provide unnecessary data. We have six basic options to reduce the data throughput:

- The data should be captured close to the Nyquist rate.

- The length of the measured impulse response should not be much longer than the settling time of the scenario under test.

- Synchronous averaging (if appropriate) should be performed immediately after data

- A short word length of digitized data should be kept by avoiding high crest factor signals.

- Stationary data should be removed by feedback sampling or digital filtering immediately after data capture (see also chapter 3.3.4 in [2]), and

- Sparse or compressive sampling [3] should be performed. However, this point will not be considered here as it would go beyond the scope of this chapter.

Without going into detail, we would like to mention at least some further aspects that influence the performance of sensor operation, too. They concern interference issues like robustness against jamming and low probability of intercept (LPIR- low probability of intercept radar).

The performance figures summarized above are the basis for deciding on a certain sensor configuration for a specific application. In what follows, the most popular UWB sensor principles will be tabulated and assessed with respect to the introduced performance figures.

#### 2.2. Principles of UWB-sensors

We divide the UWB sensor principles into two groups. While the sensors of the first group generate sounding signals of large instantaneous bandwidth, the devices belonging to the second group deal with narrowband signals swept over a large bandwidth. A thorough analysis of the different sensor concepts of both groups including a reference list can be found in [2]. Here, we will only give a short summary to get an impression of the most common sub-components of UWB sensors and to understand the advantages and disadvantages of the various principles.

#### 2.2.1. Sensors of large instantaneous bandwidth

There are several UWB approaches known exploiting signals of large instantaneous bandwidth. Usually, they are denoted according the sounding signal applied by the sensor. Typical representatives of this signal class are:

- sub-nanosecond pulses

- very wideband pseudo-noise codes

- multi-carrier signals (also assigned as multi-sine), and

- white random noise.

By assumption, these signals have a bandwidth in the GHz range requiring often Nyquist rates of the measurement receivers above 10 GHz. Disregarding the device costs, this is hardly to achieve with the limited power budget and the restricted means of data handling (see section  $2.1 - Figure \ of \ Merit$  and  $Data \ throughput$ ) which a sensor usually has at its disposal. Hence, all these devices must reduce their data rates at the expense of receiver efficiency, which is reflected by a reduced dynamic range  $D_{\rm max}$  (see(7)). The data rate reduction is either achieved by sub-sampling or by serializing the data recording.

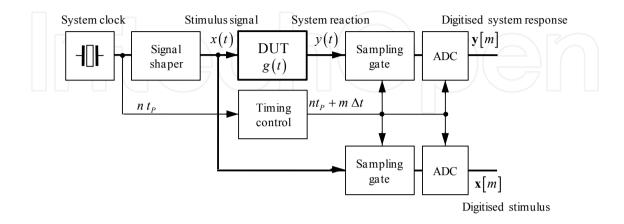

Fig. 2 refers to three possible device conceptions for illustration. The two upper approaches require periodic sounding signals. Here, the signal shaper may be a pulse generator, a binary PN-generator or an arbitrary waveform generator. The most often found device implementations apply sub-nanosecond pulse generators. Indeed, the concept allows the implementation of very cost-effective and power saving sensors. However, their system performance often suffers from reduced dynamic range due to the large crest factor of the sounding signal (compare (7)); they do not provide jitter suppression (see also sub-chapter 2.3) and they are not robust against jamming. Wideband PN-generators are an interesting alternative to pulse generators since they provide powerful signals of low magnitude (i.e. of low crest factor). Arbitrary waveform generators are able to provide signals which can flexibly be adapted to the measurement problem. However, they are quite expensive, power hungry and limited with respect to the bandwidth. Hence, they have not been found in practically applicable sensor concepts recently.

Sub-sampling receiver: It is the most often applied UWB concept. It supposes periodic sounding signals ( $t_P$  - signal period). Typically, the measurement signals are captured by sequential sampling, providing one data sample per period whose time position is stepwise shifted over the whole signal. The actual sampling interval is  $t_P + \Delta t$ , while the equivalent sampling interval which has to meet the Nyquist criteria is  $\Delta t$ . Newer concepts apply interleaved sampling permitting higher sampling rates since more than one point per period is taken. The classical concept of time shift control uses the fast ramp-slow ramp approach which, however, tends to non-linear time axis representation, sampling jitter and time drift. A second method deals with two stable sine wave generators (e.g. Direct Digital Synthesizers of slightly different frequency  $(f_1 = t_p^{-1}; f_2 = (t_p + \Delta t)^{-1})$ . This reduces time drift and avoids time axis non-linearity. However, it still keeps the sampling jitter quite high since the trigger events launching the sounding pulse and activating the sampling gates are based on relative flat edges of the two sine waves of (comparatively low) frequency  $f_1$  and  $f_2$ . Timing control based on digital counters for coarse timing exploits steep trigger edges improving the jitter performance. Then, the fine tuning is typically done by programmable delay chips which consist of hundreds of delay gates. As these gates are not absolutely identical, the delay line cannot ensure equidistant sampling. Furthermore, the delay time depends on temperature, and the huge number of gates consumes plenty of energy.

### Sub-sampling receiver

## **Analog Correlator**

# Sub-sampling correlator

**Figure 2.** Three possible sensor structures exploiting signals of large instantaneous bandwidth.

Analog correlator: Due to the lag of programmable analog wideband delay lines, one applies two wideband sources (pulse or PN-sequence) providing two identical signals which are shifted in time. The time shift may be controlled by the same approaches as mentioned above. One of these signals stimulates the DUT, and the other one acts as reference in a correlator. Even if the mixer and the integrator do not waste signal energy, the correlator has about the same efficiency as a sequential sampling receiver as long as one does not deal with parallel correlation stages. We can find from eq. (7) that the correlation principle will provide the best dynamic range due to the large time-bandwidth product. But this benefit will be gambled away if sounding signals of large crest factors are applied.

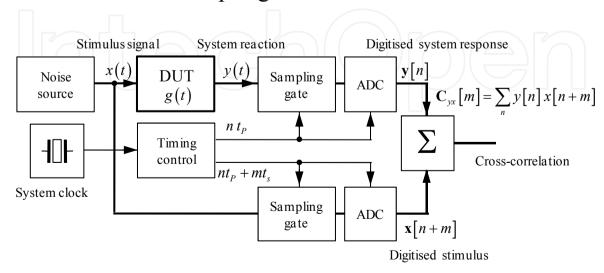

Sub-sampling correlator: Here, we can use also random noise as stimulus. The time lag between measurement and reference signal is performed by shifting the sampling time as explained before. The correlation is done in the numerical domain. The approach is quite time consuming since the averaging time must be high in order to achieve a stable estimation.

#### 2.2.2. Sensors of narrow instantaneous bandwidth

Strictly spoken, such sensors do not belong to UWB systems but they are doing the same job as real UWB devices if they are applied for sensing. Hence, they are worth being considered.

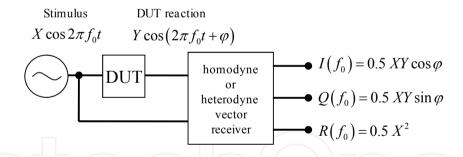

**Figure 3.** Principle of sine wave measurement.

Fig. 3 depicts the very basic principle. The signal source is a sine wave generator which steps or sweeps the signal frequency over the wanted bandwidth. Depending on the requirements (signal purity, frequency stability, frequency axis linearity, settling time etc.), free-running VCO's, synthesizers or DDS-circuits are in use. The receivers are based on homodyne or heterodyne down-conversion providing the complex valued frequency response function of the DUT:

$$\underline{G}(f) = \frac{I(f) + jQ(f)}{R(f)} \xrightarrow{IFFT} g(t)$$

(10)

which can be transformed via IFFT into the impulse response function. Simple implementations (e.g. many FMCW-radars) abstain from vector receivers. They only deal with the in-phase component.

Measurement principles applying sine waves provide the best suppression of noise and harmonic distortions due to narrowband filtering before signal capture. Their receiver efficiency tends to one as long as the settlement of resolution filters and signal source are negligible against the recording time. Hence, such devices often suffer from long measurement duration which leads to a strong range-Doppler coupling. The recording time can be reduced either by simultaneous measurements at different frequencies [7] (requiring complex parallel receiver and synthesizer) or by renouncing the narrowband filters (giving up the sensitivity benefits compared to the wideband approaches).

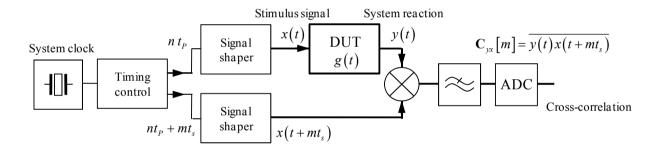

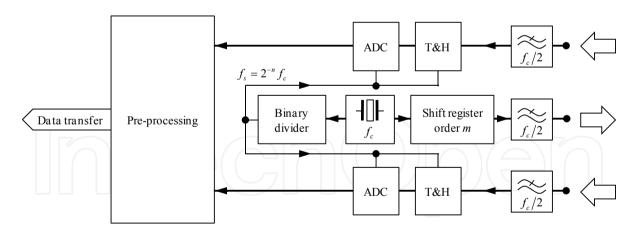

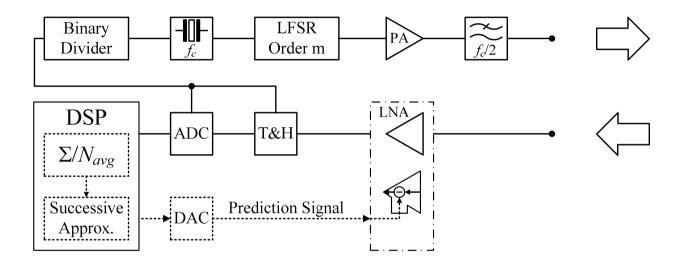

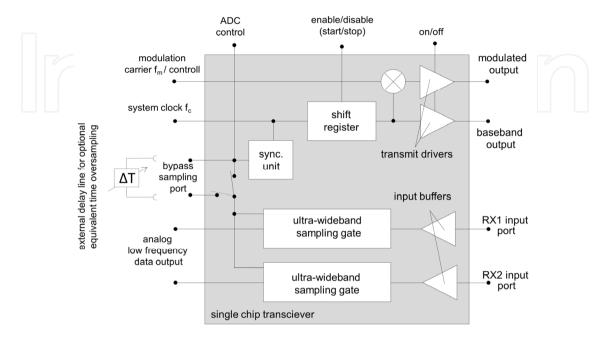

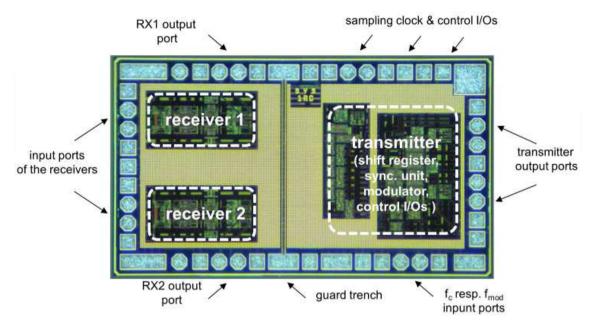

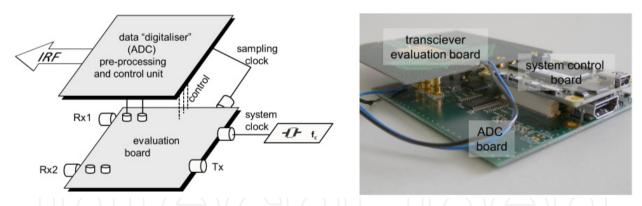

#### 2.3. UWB pseudo-Noise Concept

Under the assumption of Pseudo-Noise (PN)-codes for sounding, Nyquist sampling for data capture and embedded pre-processing for data reduction, the principle depicted on the top of Fig. 2 seems to be the most promising if one trades the pros and cons of the various UWB principles with respect to monolithic integration, system performance, MIMO-capability and power consumption. Fig. 4 represents the modified structure adapted to the conditions mentioned above. The use of two receiver channels yields the best performance with respect to different application aspects like synchronous measurement of stimulus and reaction signal, opportunity of device calibration, difference or interferometric measurements as well as long term sensor stability.

**Figure 4.** Basic structure of UWB PN-device.

A stable microwave oscillator controls the whole system. It has to provide only a single frequency  $f_c$  which allows the use of simple and stable generator concepts. The oscillator pushes a high-speed shift register. Depending on its feedback structure, it provides any binary sequence. Preferentially, M-sequences are used due to their favorable autocorrelation function. Other options could be Golay-codes [8] or Gold-codes if crosscorrelation properties are in the foreground of interest.

For the sake of brevity, we restrict ourselves here solely to M-sequences. These codes have a sinc<sup>2</sup>-spectrum with the first zero located at  $f_c$  and they have concentrated about 80% of their energy in the spectral band from DC to  $f_c/2$ . Hence, we will not provoke a dramatic performance loss if we limit the upper frequency to  $f_c/2$ . On the contrary, the band limitation avoids disproportionate growth of noise against ever decreasing signal power.

The band limitation to half the clock rate touches several performance-relevant issues:

- We need a sampling rate of at least  $f_c$  in order to meet the Nyquist theorem. In other words, it is sufficient to capture one sample per chip of the M-sequence. As the Msequence is periodic, we can do this by sub-sampling. It is easy to show that a binary divider is sufficient for timing control since the number N of chips in the sequence is always one less than a power of two  $(N = 2^m - 1)$ . If the order m of the shift register and the order n of the binary divider are identical, we have sequential sampling. For n < m, one speaks about interleaved sampling which takes more than one sample within one period.

- Both, the signal edges of the microwave clock  $f_c$  as well as of the sampling clock  $f_s$  are quite steep. Hence, the trigger events activated by them are robust against jitter and drift.

- The time axis of the receiver is defined by the sampling clock  $f_s$ . This clock originates from a stable RF-generator and a digital frequency divider which has to run trough all its states before it can launch a new impulse. Hence, any internal deviations between the involved flip-flops have no effect on the divided signal. Therefore, apart from the remaining jitter, we can expect exact equidistant sampling i.e. an absolutely linear time axis representation.

- The principle of interleaved sampling allows the sampling rate to be varied by keeping the sensor concept. Thus, one can reduce the sampling rate in favor of reduced power consumption and device costs or it can also be increased to improve the receiver efficiency  $\eta_r$  depending on the development state of high-speed electronics.

- Nyquist sampling provides the lowest possible data throughput<sup>1</sup> without violation of sampling theorem.

The embedded pre-processing is mainly aimed at data reduction by synchronous averaging (often the measurement rate is much higher than required by the time variance of the test scenarios), static background removal or signal transformations. It should, however, be respected that impulse compression (in order to get the impulse response) performed at this point will increase the data throughput toward the main processor since the word length of the data samples increases.

<sup>&</sup>lt;sup>1</sup> Here, we refer to general measurement conditions. We disregard sparse sampling which is largely dependent on the measurement objects.

The sensor principle depicted in Fig. 4 is basically also able to deal with short subnanosecond pulses. However, this would greatly degrade the performance of the system which is largely determined by the amount of signal energy accumulated in the receiver. In the case of pulse signals, this requires amplifiers of high compression points and high resolution ADCs since the whole signal energy is concentrated in a short moment. Furthermore, the measurement object may be exposed to strong fields in the case of nearfield measurements. The application of PN-codes avoids all these flaws since it carries enough energy even with small signal magnitudes. As the impulse compression (leading to high crest factor signals) is performed in the digital domain, the analog sensor components and test objects are spared from high voltage peaks.

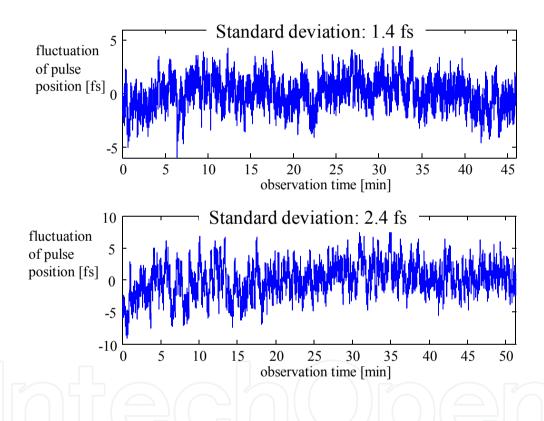

Figure 5. Stability of time position measurement. The delay time of a 50 cm long RF cable was measured at constant temperature. The RF clock was provided either by a sophisticated sine wave generator (SMP04 from Rhode & Schwarz) (top) or by a free running DRO (bottom).

It is well known that the impulse compression of time-extended wideband signals largely improves the dynamic range. As shown in [2] (chapter 4.7.3), it also reduces the jitter susceptibility. The impulse compression distributes the jitter power evenly over the whole signal like additive noise. However, a noise increase above the "natural" level of electronic and quantization noise cannot be observed since the jitter-induced perturbations remain quite low due to the measures described above. Hence, the edges of the impulse response of a DUT measured by the PN-principle are not affected by jitter as usually in pulse

measurements. This favors the PN-sensor concept for applications dealing with super resolution techniques or micro-Doppler problems, particularly if weak scattering targets are overwhelmed by strong ones. Chapter11 ultraMedis gives some examples of related problems, and Fig. 5 illustrates the achieved short-time stability of an M-sequence sensor having a bandwidth of about 8 GHz. The short-time variance of the pulse position measurement was in the lower fs range corresponding to a distance variation below 1 µm.

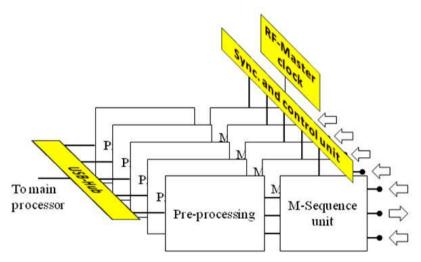

The simple timing concept of the PN-sensors enables the implementation of large MIMOarrays at which the number of cascaded measurement units is basically not limited. The principle is shown in Fig. 6. However, the data handling will be increasingly demanding with a rising number of channels. In a typical operation mode, the transmitters are sequentially activated while the receivers of all channels work in parallel. Some details of implemented MIMO-systems can be found in chapter 11 *ultraMedis*.

Figure 6. Creation of a MIMO-system by cascading M-sequence sensors.

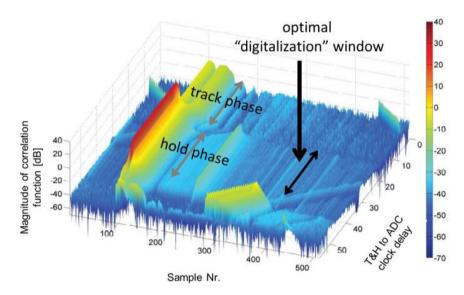

The receiver of the UWB PN-sensor applies sub-sampling for data capture. Hence, its efficiency gives some potential of further improvements. This would, however, be connected with a considerable increase of the sampling rate  $f_s$ . As we can see from (8), the elevation of the sampling rate has to be done at the expense of the ADC resolution since the FoM-value is primarily fixed by the semi-conductor technology, while the maximum power is limited by the achievable heat transport. However, simply increasing the sampling rate based on low bit ADCs will not bring any profit with respect to the sensor performance, i.e. the opposite will happen.

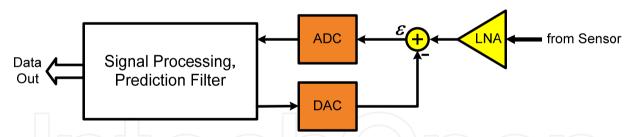

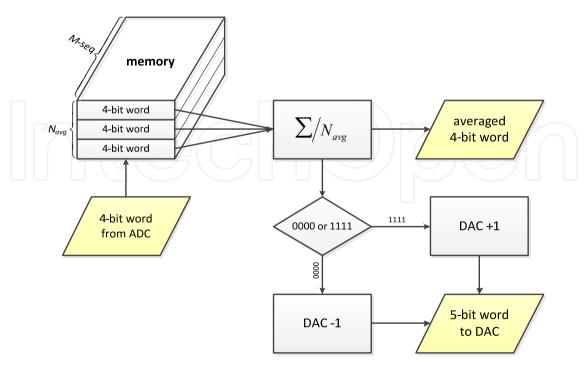

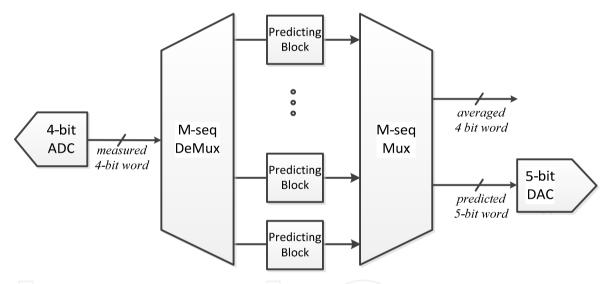

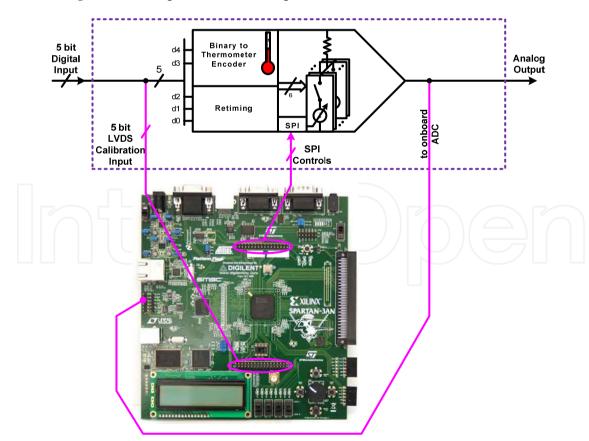

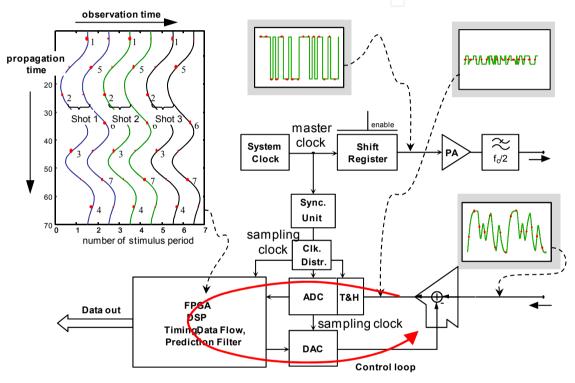

As, however, the update rate of UWB PN-sensors is much higher than required by the time variance of the test object, the difference between two consecutive measurements is very low so that low resolution ADCs are sufficient for capturing these deviations. Anyway, this supposes a fast control loop and a (less power hungry) DAC of sufficient resolution which provides the captured signals from previous measurements for reference. Some basic considerations related to this type of feedback sampling can be found in [2]. Details of the layout and implementation of related sub-components are discussed in sections 3.4, 5 and 6.2.

#### 3. Analog wideband receiver circuits

#### 3.1. Introduction

In order to support system design in its individual stages, different amplifier versions have been developed. Classical ultra-wideband low-noise amplifiers (UWB-LNAs) have been implemented first to ensure early availability and to assess the SiGe BiCMOS technology applied. Then, new receiving components have been considered to address the requirements discovered in system design. This way, a new subtraction amplifier has been made available which allows for practical evaluation of the feedback sampling approach. Fig. 7 illustrates the way in which LNAs and subtraction amplifiers are used as part of the system.

Figure 7. Transmit and receive path of the basic UWB PN-device from Fig. 4 (solid lines) and proposed extension to allow for feedback sampling (dashed lines - see subsection 6.2.3). Either the LNA component or the amplifier with integrated signal subtraction capability are present (dash-dotted box) according to the system state at which it is focused.

In this figure, the basic M-Sequence system is indicated by solid lines. Within this system, classical UWB-LNAs (the LNA component in the dash-dotted box) are used to support the way of operation presented in subsection 2.3. Possible implementations are covered in subsections 3.2.1 to 3.2.3. In addition, a system extension is indicated by the dashed lines, which tries to overcome the limitations imposed by the analog-to-digital converter. For this reason, a digitally calculated prediction signal is provided by a digital-to-analog converter and subtracted from the receive signal to generate a difference signal of highly reduced signal swing close to sampling time instances (see sections 5.1 and 6.2.3). Subtraction is performed by an amplifier with integrated signal subtraction capability, practical realizations of which are presented in sections 3.4.1 and 3.4.2.

The latest subtractor also accounts for low feeding point impedance, which is imperative for the conceptual design of dielectrically scaled antennas. The use of such a device is intended by the collaborative project *ultraMedis* (see chapter 11). For establishing common interface definitions, the performance of individual components has to be characterized by appropriate metrics. While those are well established for single-ended arrangements, this is not the case with the noise characterization of multiport or differential structures. Hence, a new de-embedding scheme for the noise figure of a differential device has been developed and will be presented.

#### 3.2. LNAs for the basic M-Sequence system

Within the basic M-sequence system, low noise amplifiers (LNAs) perform the classical task of adapting the input signal swing to the dynamic range of the analog-to-digital converter (ADC) while adding only a minimum amount of excess noise and providing reasonable power-match conditions. If a high-gain LNA is used, the system also is less sensitive to noise added by succeeding components. Gain, in turn, is limited by the required linearity, and an appropriate compromise with respect to all counteracting requirements has to be found. While trading one parameter against the other, the conditions set by the technology have to be considered for the individual LNA. Resonant tuning and resistive feedback topologies are predominantly used in literature for mapping specifications to circuit designs. Though a resonant solution is favored in [11], the authors do admit that the parasitic base resistance of bipolar transistors causes a large contribution to output noise. Thus, the advantage of extraordinary low noise figures enabled by narrow-band resonant designs as compared to designs matched by resistive feedback is relativized. High magnetic field gradients potentially encountered in some of the applications, and the limited ability to use shielding as identified in [12] also make the use of inductors questionable. Therefore, resistive feedback solutions have been preferred as their use is additionally accompanied by notable die size advantages. While the design of individual amplifiers will be covered in the following subsections, general guidelines can be taken from standard textbooks. In [13], for example, the impact of feedback on noise and impedance match is analyzed in detail. For the design, too, a simplified version of the bipolar transistor small signal equivalent circuit model with additional noise sources as presented in [13] has been used.

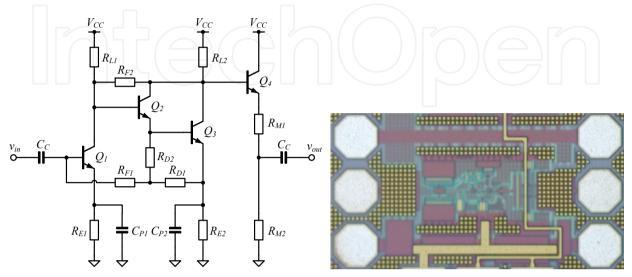

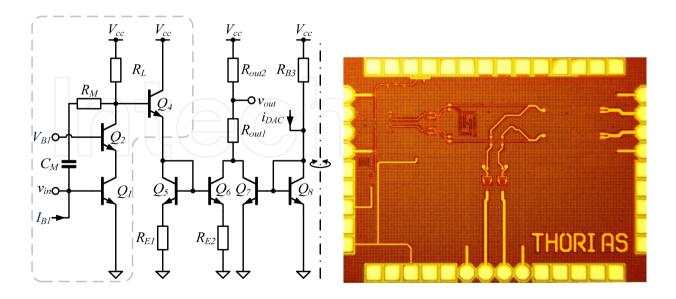

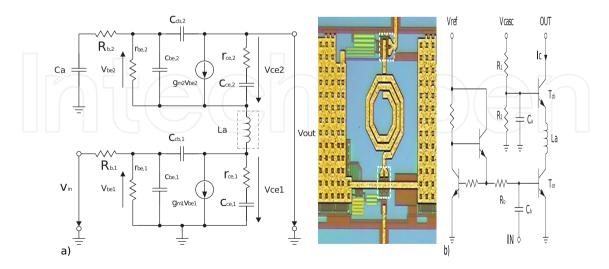

#### 3.2.1. Multiple resistive feedback LNA

One of the implemented amplifier versions which have been inspired by classical UWB-LNAs is depicted in Fig. 8. According to [10], this is a popular wideband amplifier topology often referred to as *Kukielka* amplifier. Due to numerous results reported in literature for this kind of amplifier, the impact of technology on circuit performance can be assessed. For comparison, especially SiGe implementations as presented in [9] are valuable. The main characteristics of this amplifier are set by the core circuit which comprises transistors  $Q_1$  to  $Q_3$ . For analysis, the Darlington pair  $Q_2 - Q_3$ , which is used for gain-bandwidth extension

of the second stage, is treated as single compound-transistor  $Q_{23}$ . Within the simplified circuit thus obtained, four feedback loops can be identified. For proper biasing, series-series feedback is applied to  $Q_1$  and  $Q_{23}$ . By this measure, the bandwidth of both stages is improved. In turn, input and output impedances of the amplifier are increased rather than decreased as required for input and output power matching.

Figure 8. Schematic diagram (left) and chip photo (right) of the multiple resistive feedback LNA - the die area is only 530  $\mu$ m × 280  $\mu$ m.

Hence, local shunt-shunt feedback is applied to  $\mathcal{Q}_{23}$  in order to reduce the output impedance. Finally, to enable input power matching, global shunt-series feedback from the emitter node of  $Q_{23}$  to the base of  $Q_{1}$  is applied. According to [10], this configuration tends to present an overdamped response. For this reason, peaking capacitors  $C_{P1}$  and  $C_{P2}$  are inserted to improve the frequency behavior of the amplifier. The addition of peaking capacitors might, however, impair stability which has to be diligently observed during design for this reason as stated in [13]. In the same publication, an approximate calculation of the noise figure (NF) for this topology reveals that the latter is dominated by the noise properties of  $Q_1$  as long as  $R_{F1} \gg R_S$  and  $R_{F1} \gg R_{\underline{eq}}$ .  $R_{\underline{eq}}$  is related to the equivalent input noise voltage source  $v_{Q1}$  of transistor  $Q_1$  by  $R_{eq} = v_{Q1}^2/(4kT)$ . For this reason, the selection of transistor  $Q_1$ 's bias current to yield optimal current density with respect to its noise properties should be a first step in design. After this initial step, one of the directed design procedures given in [10] or [9], respectively, can be used for further development. Those are derived from input and output power match conditions as well as from pole positions. In order to account for the characteristics of the Darlington pair transistors  $Q_2$  and  $Q_3$ , substitutions  $g_{m,23} \to g_{m,3}$  and  $\omega_{T,23} \to 2 \cdot \omega_{T,3}$  can be applied according to [10]. In Fig. 8 (left), an emitter follower has been attached for further improving the output power matching in the technology used. Fig. 8 (right) shows the chip photograph of the implemented LNA without pads used for biasing. The dimensions of the displayed die area are  $530 \mu m \times 280 \mu m$ only, which confirms the advantage resistive feedback amplifiers provide in view of die area as compared to resonant solutions. For the accurate characterization of the fabricated amplifier, on-waver measurements have been performed using a PM 8 probe station of Süss MicroTec (now acquired by Cascade Microtech). Due to the measurement arrangement, losses preceding and succeeding the device under test (DUT), i.e. the amplifier, cannot be avoided. However, their impact on the scattering parameters of the DUT can be eliminated by proper calibration of the network analyzer applied. Also, the spectrum analyzer with noise figure measurement personality in use allows for the specification of losses preceding and succeeding the DUT which are compensated for during measurement in this case<sup>2</sup>. Measurement results obtained in this way are shown in Fig. 9 together with results from post-layout simulation. Initially, they have been presented in [14].

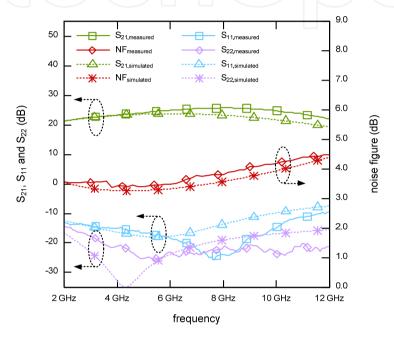

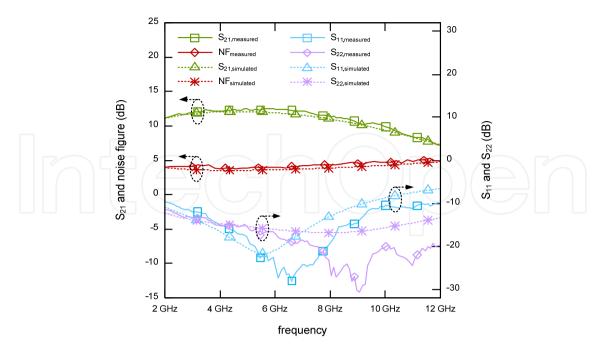

**Figure 9.** Measurement results of the multiple resistive feedback LNA. (The arrows point to the related axis scaling.)

From Fig. 9, peaking in the gain curve progression of the measurement data can be observed as compared to the results from post layout simulation. The maximum difference appears at about 8 GHz, which is the frequency at which a notch in measured  $S_{11}$  values also appears. In [14] it is thus suspected that this deviation arises due to the interaction of the test set-up with the DUT. In short summary, the results presented in Fig. 9 for the low-cost technology applied map pretty well the state-of-the-art performances reported in literature at that time. For a more detailed analysis, the reader may consult [14].

#### 3.2.2. Active Feedback LNA

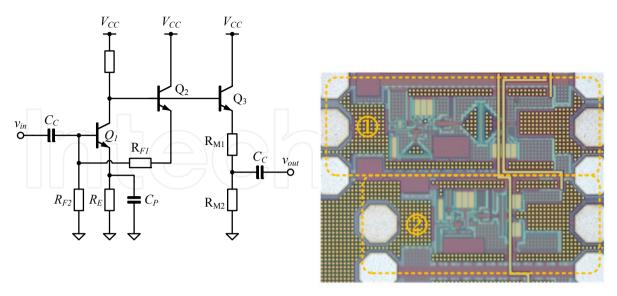

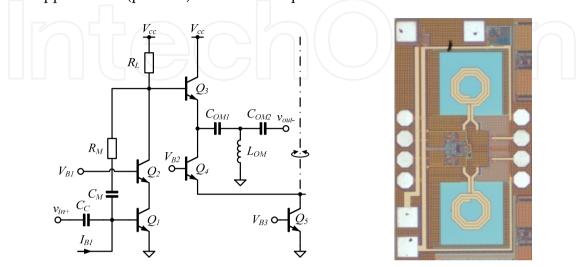

This amplifier has been inspired by the work presented in [15]. Due to the characteristics of the applied technology, certain adaptations have been required, though. Fig. 10 (left) shows the schematic diagram of the final design.

<sup>&</sup>lt;sup>2</sup> Rhode & Schwarz ZVA-24 and FSQ-40 have been used for the measurements.

Figure 10. Schematic diagram (left) and chip photo of both active feedback LNA versions (right). The die areas are (1)  $630 \mu m \times 280 \mu m$  and (2)  $530 \mu m \times 280 \mu m$ , respectively.

It is a one-stage amplifier with resistive emitter degeneration to ensure a stable DC operating point and to improve bandwidth. Due to the presence of the peaking capacitor  $C_p$ , degeneration is continuously shifted to higher frequencies. As in the case of the multiple resistive feedback amplifier, this technique has to be used with care to ensure that this measure does not impair amplifier stability. Input matching of  $Q_1$  is achieved by feedback via transistor  $Q_2$  as well as resistors  $R_{F1}$  and  $R_{F2}$ . The advantage of  $Q_2$  is twofold: It improves the isolation between the input node and the output node in forward direction and, according to [15], it helps to enlarge the collector-emitter voltage of  $Q_1$ . Thus, the maximum oscillation frequency  $f_{max}$  is expected to be increased, and the large-signal behavior is said to be improved. The amplifier according to Fig. 10 was presented in [14] for the first time. Compared to the amplifier in [15], the inductor used for improving the frequency behavior has been abscised from the design while the peaking capacitor has been added. Also, for better output matching, emitter follower  $Q_3$  has been attached. To avoid a lengthy discussion of circuit characteristics, Fig. 10 (left) uses an alternative way to depict the circuit as compared to [14] or [15]. This representation points out the large similarity of feedback paths in both amplifiers shown in Fig. 8 and Fig. 10. Though the actual implementations of the passive feedback networks differ, shunt-series feedback is applied for input matching in both cases, and many design steps can be executed by analogy. Fig. 10 (right) shows the chip photograph of two variants, which have been implemented to assess the impact of layout on circuit performance. In the first version, 90° lead corners are avoided and consecutive 45° lead corners are used instead. By this measure, the average lead length is increased. By contrast, a compact design has been targeted in the second layout version. As discussed in [14], results do not differ significantly as long as the length of the lead connecting the RF input with the first amplifying transistor is kept comparably long. Thus, only results for the second layout version are shown in Fig. 11.

**Figure 11.** Measurement results of the active feedback LNA. (The arrows point to the related axis scaling.)

The die area occupied by the first layout version is  $630\mu m \times 280\mu m$  while the second layout version only occupies  $530\mu m \times 280\mu m$  (both excluding DC-pads). Measurements have been performed the same way as explained for the multiple resistive feedback LNA. Compared to Fig. 9, gain is much lower, which is expected due to the single stage nature of the active feedback amplifier. At the same time, the input referred 1dB compression point is improved notably. A more complete discussion of amplifier characteristics is presented in [14].

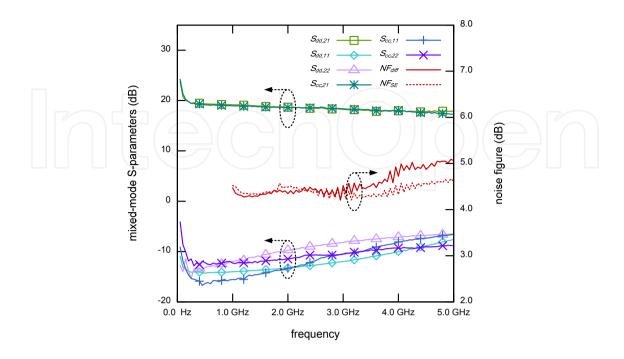

#### 3.2.3. Pseudo-differential LNA

Core of the half-circuit shown in Fig. 12 (left) is the cascode amplifier with reactive shunt feedback on the left-hand side. As for the single-ended amplifiers, bias current of this arrangement should be selected due to noise and linearity considerations. While a more detailed analysis of this topology, as presented for the inductively degenerated cascade amplifier with capacitive shunt feedback in [16], might be desirable at this point, limited space for this section does not permit a lengthy discussion. Instead, we allude to the amplifier of [17] from which the topology of Fig. 12 (left) has been derived.

A pseudo-differential amplifier has been implemented to support the development of the basic M-sequence system by adding the capability to use differential circuitry, especially differential antennas. Many of its characteristics are inherited from the topology of [17]. However, emphasis with respect to certain design parameters has been shifted. The most peculiar aspect is the fact that the input matching network used in [17] could be abscised from the design. This modification was enabled by improved input-output isolation due to altered feedback tapping points. Some results of the manufactured chip, a photo of which is contained in Fig. 12 (right), are summarized in Fig. 13. Together with additional topological

aspects, they are discussed in [18] in more detail. Measurements to gather those results have been performed on-waver at the PM 8 probe station using ground-signal-signal-ground (GSSG) probes. Similar to the single-ended case, scattering parameters could be determined directly by a calibrated network analyzer. By contrast, only single-ended equipment has been available for noise figure measurement, and it is left to the next subsection to discuss a method applicable to (pseudo-)differential amplifiers.

Figure 12. Half-circuit schematic diagram (left) and chip photo (right) of the pseudo-differential LNA.

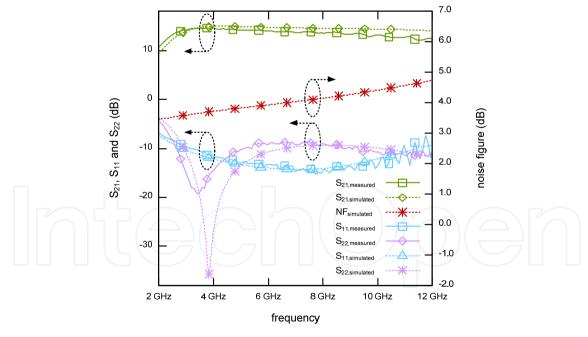

Figure 13. Measurement results of the pseudo-differential LNA. (The arrows point to the related axis scaling.)

#### 3.3. Differential noise figure measurement

Due to space limitations, only a short introduction to this topic will be presented here. While there are alternative methods as presented in [23] and [24], for example, focus will be on a

new powerful method proposed in [20]. A convenient definition for the noise figure of a differential (or multiport) device with respect to one of its ports has been given by Randa [22] and is reprinted in (11) with slight modifications:

$$F_{i}(\Gamma_{k}, C_{k}) = \frac{\left\{ \left[ \mathbf{I} - \mathbf{S}_{k} \Gamma_{k} \right]^{-1} \left( \mathbf{S}_{k} C_{k} \mathbf{S}_{k}^{\dagger} + C_{S,a} \right) \left[ \left[ \mathbf{I} - \mathbf{S}_{k} \Gamma_{k} \right]^{-1} \right]^{\dagger} \right\}_{ii}}{\left\{ \left[ \mathbf{I} - \mathbf{S}_{k} \Gamma_{k} \right]^{-1} \mathbf{S}_{k} C_{k} \mathbf{S}_{k}^{\dagger} \left[ \left[ \mathbf{I} - \mathbf{S}_{k} \Gamma_{k} \right]^{-1} \right]^{\dagger} \right\}_{ii}}$$

$$(11)$$

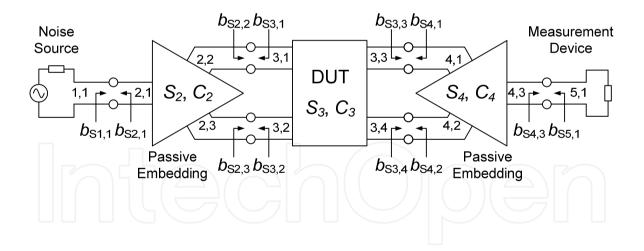

The noise figure in (11) is parameterized by the matrix of reflection coefficients seen by the DUT into the ports of connected components  $\Gamma_k$  and the noise correlation matrix of incident noise waves injected by an external source  $\mathbf{C}_k$ . I is the identity matrix in (11), the dagger indicates the Hermitian conjugate, and  $\mathbf{S}_k$  as well as  $\mathbf{C}_{s,a}$  are the scattering matrix and the noise correlation matrix of emergent waves contributed by the DUT, respectively. To apply this definition,  $\mathbf{C}_{s,a}$  has to be determined first. Therefore, the differential device has to be embedded into a network of passive components which provide the differential excitation as only single-ended measurement equipment is currently available. This is demonstrated in Fig. 14. The noise correlation matrix of the DUT then has to be de-embedded from the results measured for the component chain.

**Figure 14.** DUT embedded into passive components.  $\mathbf{b}_{Sx,y}$  are equivalent generator noise waves caused by component x and ejected from the respective port y.

For this purpose, the noise distribution matrix defined in [21] is a convenient starting point. Multiplied by Boltzmann's constant k and the physical temperature T, it is the correlation matrix of emergent noise waves caused by a passive component which account for all the noise generated within the device. It can be related to the scattering matrix as shown by (12). A short and intuitive proof of this relation is contained in [25]:

$$\hat{\mathbf{N}} = \left(\overline{\mathbf{b}_{S}\mathbf{b}_{S}^{\dagger}}\right) / (kT) = \mathbf{I} - \mathbf{S}\mathbf{S}^{\dagger}$$

(12)

Making use of single-ended noise measurement equipment, the characteristic noise equation reference goes here temperature  $\hat{T}_{chain}$ , which characterizes noise from all the elements of the whole component chain, can also be determined. Thus, we are only left with the problem to describe signal transfer via the component chain to accomplish the goal of de-embedding  $C_{s_a}$ . In [20], an approach based on the connection scattering matrix W has been presented for this purpose, which surpassed the method of [19], because it is applicable without simplifying assumptions. The connection scattering matrix was introduced long ago, and its use for computer-aided circuit analysis has been discussed in [26], for example. For all ports in a component network, it relates the incident to the impressed waves. To enable such matrix representation, incident, reflected, and impressed waves have to be composed to wave vectors  $\mathbf{a}$ ,  $\mathbf{b}$ , and  $\mathbf{b}_{\rm s}$ , respectively, which should be sorted in a component-wise way. For convenience, a component index is assigned to the vector entries, and it is assumed that elements corresponding to the DUT (index k) are placed at the bottom of each wave vector. An element is thus identified by two indices i,j representing the component and the respective port number. With this convention, all complex wave amplitudes can be related by the set of linear equations

$$\mathbf{b} = \mathbf{S} \cdot \mathbf{a} + \mathbf{b}_{\varsigma} \tag{13}$$

where S is a block-diagonal matrix assembled from the individual component S-parameter matrices. The connections between the single components impose additional constraints on the wave amplitudes. To account for them, the connection matrix  $\Gamma$  is used as in (14):

$$\mathbf{b} = \mathbf{\Gamma} \cdot \mathbf{a} \tag{14}$$

Most often, a common real reference impedance is applied for all components. Then, all entries of  $\Gamma$  are zero except those which refer to connected ports and, thus, are one. In this case,  $\Gamma$  is a permutation matrix with  $\Gamma^{-1} = \Gamma^{T}$ . From (13) and (14), the incident wave vector a can be eliminated to get

$$\mathbf{W} \mathbf{\Gamma}^{-1} \mathbf{b} = \mathbf{b}_{S}, \text{ with } \mathbf{W} = \mathbf{\Gamma} - \mathbf{S} \mathbf{W} = \mathbf{\Gamma} - \mathbf{S}$$

(15)

Noise generated by the source does not contribute to the characteristic noise temperature of the component chain. The respective entries of  $b_S$  can thus be set to zero. Furthermore, in the case of  $S_1$  containing zero entries<sup>3</sup>, the corresponding rows of  $W\Gamma^{-1}$  should be deleted to avoid rank deficient matrix problems in some of the computations. For convenience, we will refer to the matrix obtained from this operation by V. After additional matrix partitioning, which is required later, (15) then becomes

$<sup>^{3}</sup>$   $\mathbf{S}_{1}$  is a submatrix of  $\mathbf{S}$  .

$$\mathbf{b}_{S,p} \begin{bmatrix} \mathbf{b}_{S,2} \\ \mathbf{b}_{S,k-1} \\ \mathbf{b}_{S,k+1} \\ \vdots \\ \mathbf{b}_{S,n} \\ \mathbf{\overline{b}}_{S,k} \end{bmatrix} = \begin{bmatrix} \mathbf{V}_{pm} & \mathbf{V}_{pp} & \mathbf{V}_{pa} \\ \mathbf{V}_{am} & \mathbf{V}_{ap} & \mathbf{V}_{aa} \\ \end{bmatrix} \begin{bmatrix} \frac{\mathbf{b}_{1}}{\mathbf{b}_{2}} \\ \vdots \\ \mathbf{b}_{k-1} \\ \mathbf{b}_{k+1} \\ \vdots \\ \frac{\mathbf{b}_{n}}{\mathbf{b}_{k}} \end{bmatrix} \mathbf{b}_{m}$$

$$(16)$$

In (16), submatrix  $V_{am}$  will always be zero, because there is no direct connection from the input to the DUT. Hence, we are left with

$$\mathbf{b}_{S,p} = \mathbf{V}_{pm} \mathbf{b}_m + \left[ \mathbf{V}_{pp} | \mathbf{V}_{pa} \right] \begin{bmatrix} \mathbf{b}_p \\ \mathbf{b}_a \end{bmatrix}, \tag{17}$$

and

$$\mathbf{b}_{S,a} = \left[ \mathbf{V}_{ap} | \mathbf{V}_{aa} \right] \begin{bmatrix} \mathbf{b}_p \\ \mathbf{b}_a \end{bmatrix}. \tag{18}$$

Setting  $\mathbf{Q} = \left[\mathbf{V}_{ap} \mid \mathbf{V}_{aa}\right] \left[\mathbf{V}_{pp} \mid \mathbf{V}_{pa}\right]^{-1}$  for abbreviation, (19) is obtained from (17) and (18) after some algebra<sup>4</sup>:

$$\mathbf{Q}\,\mathbf{V}_{pm}\,\mathbf{b}_{m} = \mathbf{Q}\,\mathbf{b}_{S,p} - \mathbf{b}_{S,a}\,. \tag{19}$$

Finally, since  $\mathbf{b}_{S,p}$  and  $\mathbf{b}_{S,a}$  arise from different sources and are thus uncorrelated,  $\mathbf{C}_{S,a}$  can be determined from (20)

$$\mathbf{Q} \mathbf{V}_{pm} \mathbf{C}_{m} \mathbf{V}_{pm}^{\dagger} \mathbf{Q}^{\dagger} = \mathbf{Q} \mathbf{C}_{S,p} \mathbf{Q}^{\dagger} + \mathbf{C}_{S,a}$$

with  $\mathbf{C}_{m} = \overline{\mathbf{b}_{m} \mathbf{b}_{m}^{\dagger}}$ ,  $\mathbf{C}_{S,p} = \overline{\mathbf{b}_{S,p} \mathbf{b}_{S,p}^{\dagger}}$ , and  $\mathbf{C}_{S,a} = \overline{\mathbf{b}_{S,a} \mathbf{b}_{S,a}^{\dagger}}$ . (20)

In (20), noise correlation matrices of single passive components given by the product of kT and (12) are composed to the block diagonal matrix<sup>5</sup>  $\mathbf{C}_{S,p}$ .  $\mathbf{C}_m$  accounts for noise from all

$<sup>^4</sup>$  As the right division function of a math program can be used to compute  $\mathbf{Q}$ , there is no need for an explicit inversion, and a minimum norm solution is obtained for a non-square system.

<sup>&</sup>lt;sup>5</sup> Note that noise contributions of the output loads, according to [22], should not be considered for NF computation. With respect to the set-up of Fig. 14 this implies  $\overline{b_{S,5,1}} \, b_{S,5,1}^* = 0$ , which can be achieved by using the second stage correction of the NF meter.

components of the chain related back to the input. For the set-up of Fig. 14,  $C_m$  is a  $1\times1$ matrix associated with the characteristic noise temperature as shown by (21):

$$\mathbf{C}_{m} \approx \left\lceil k \, \hat{T}_{chain} \right\rceil \tag{21}$$

For using (11) in noise figure computations, its parameter matrices  $\Gamma_k$  and  $C_k$  still need to be determined.  $\Gamma_k$  contains reflection coefficients, which relate waves injected from the DUT  $b_{S,a}$  to those reflected back from the embedding network  $a_a$ . It follows from inspection that  $\Gamma_k$  is a submatrix of  $\mathbf{W}^{-1}$ . Focusing on  $C_k$ , a simple argument leads to some confidence that (22) is a reasonable choice: Assume that the power splitter at the input of Fig. 14 only excites the differential mode. In this case, noise at the input of the DUT is completely correlated. Also, there should be a noise power of kT available at the input of the DUT in differential mode to stay comparable to the standard noise figure definition. Then, due to the properties of mixed-mode transformation, (22) is the evident solution. This is discussed in [20] in more detail.

Thus, all inputs required for (11) are determined, and the noise figure with respect to a certain output port can be calculated. Instead of a physical port, also a logical port can be considered. For this purpose, matrices in the numerator and the denominator of (11) have to be transformed by an appropriate transformation. In view of Fig. 14, mixed-mode transformation provides noise power spectral densities in the differential mode at the selected output of the DUT for both cases: Noise generated by the DUT and the input sources, as well as noise generated by the input sources alone. Their ratio finally determines the differential noise figure of the device. This approach has been applied to the pseudodifferential amplifier shown in Fig. 15. The result is contained in Fig. 16 together with the noise figure measured from one signal branch, which is given for comparison. In the measurements, the losses of the probe heads have been appropriately taken into account.

#### 3.4. Solutions for the feedback-sampling approach

The introduction of the feedback-sampling concept by system design spawned the requirement of signal subtraction at the input of the receive path. Hence, the demand for new components equipped with two inputs arose - one for the RF signal taken from the antenna, and another one for a digital prediction signal provided by the signal processing via a digital-to-analog converter (DAC). In theory, subtraction results in an output signal of highly reduced voltage swing to which the analog-to-digital converter (ADC) used for signal acquisition will be exposed. To confirm this theory in practice, two versions of an input subtractor have been implemented and will be presented in the following subsections.

#### 3.4.1. Pseudo-differential feedback-sampling amplifier

Similar to the design of amplifiers for the basic system, the development of the feedbacksampling amplifier has been guided by the assumption that the receive signal in the RF path is rather week and sufficient amplification has to be provided, while the least amount of excess noise should be added. Hence, the amplifier of Fig. 12 has been reviewed and was deemed to be suited as RF input stage of the new topology. In Fig. 15, it can be identified in the dashed box on the left-hand side. Some adjustments - especially with respect to the values of components in the feedback network - had to be made, though, as the application required a shift in the covered frequency range. At that time, the prediction signal had to be provided by a current steering DAC and can be assumed to be of rather large signal swing. Hence, no amplification is provided for this signal. Promoted by the nature of the prediction signal, the required signal subtraction is performed in the current domain. In Fig. 15, two current mirrors inject their output signals into a common output node for this purpose. While this implies signal addition instead of signal subtraction at first glance, signal addition can be turned into signal subtraction by simple sign inversion, which is enabled either by exploiting the properties of the pseudo-differential amplifier structure itself or by sign selection of the prediction signal in the digital domain. The special current-mirror arrangement of Fig. 15 has been chosen for balancing the maximum output powers which is important to ensure that the signal from the DAC input can cancel the signal from the RF input. Linearity of both signal paths, transconductance from the DAC input to the common output and maximum output currents of the DAC have to be harmonized to account for this requirement.

**Figure 15.** Half-circuit schematic diagram (left) and chip photograph (right) of the feedback-sampling LNA

Figure 16. Measurement results for the RF path of the feedback-sampling amplifier. (The arrows point to the related axis scaling.)

This topology has been characterized in detail. Results for the RF signal path are presented in Fig. 16.

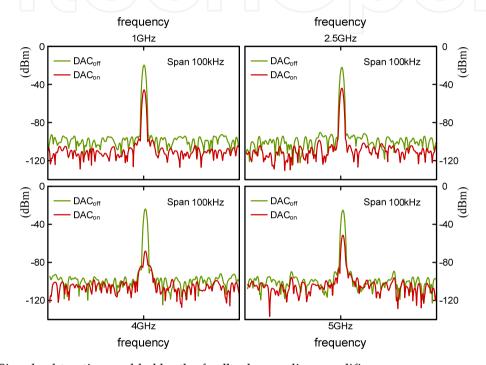

As explained for the pseudo-differential amplifier in section 3.2.3, the PM 8 probe station equipped with GSSG-probes can be used to examine an individual differential signal path. In order to detect the mixed-mode parameters given in Fig. 16, the device has been exposed to true mode excitation provided by the network analyzer, while calibration data have been applied to compensate for losses caused by the test set-up. Noise characterization can be performed by the method presented in section 3.3 and has been discussed in [19][20]. A remarkable feature of the results of this measurement is the fact that the differential noise figure  $NF_{diff}$  does not coincide with the noise figure measured from one signal path<sup>6</sup>  $NF_{SE}$ . Especially at higher frequencies, a large deviation occurs. In [20], this is explained by crosstalk caused by parasitics. So, the use of differential de-embedding schemes is recommended instead of a single-ended noise figure measurement from one signal branch. However, in view of the aim to assess the capabilities of the feedback-sampling approach, the signal subtraction itself is most interesting. In [27], we presented different test set-ups for verification purposes. Fig. 17 shows four representative results which confirm the ability to cancel the RF signal by an appropriate prediction signal.

<sup>6</sup> In Fig. 16, NF curve progressions start at 1 GHz because this is the lower corner frequency of the hybrid couplers used for measurement.

Those measurements were obtained from a test set-up incorporating the PM 8 probe station with GSSG-probes, in which two signal generators<sup>7</sup> synchronized by a frequency standard provided the input signals to both inputs at appropriate power levels via two hybrid couplers. The differential output signal of the DUT was recombined by a third hybrid coupler and displayed by a signal analyzer<sup>8</sup>. In Fig. 17, no loss compensation is applied and results are clipped to 100 kHz span. Two cases can be distinguished: First, the digital prediction signal has been switched off (DAC<sub>off</sub>) and only the RF signal has been present at the inputs. Then, also the prediction signal has been applied (DAC<sub>on</sub>) and a notable reduction in output signal power can be observed for all frequencies.

Figure 17. Signal subtraction enabled by the feedback-sampling amplifier.

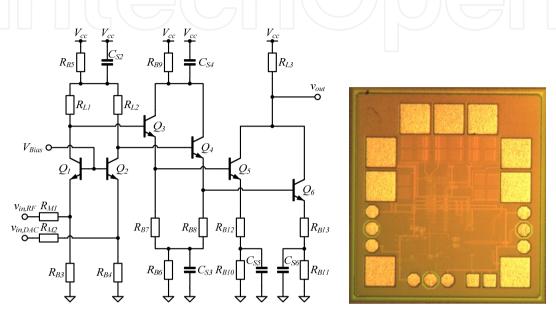

#### 3.4.2. Subtractor with Low Impedance antenna interface

The feedback-sampling amplifier of the preceding subsection is expected to perform well as long as the assumption of (reasonable) small input signals is justified. A key requirement in the feedback-sampling concept is linearity preceding the signal subtraction in order not to distort the zero crossings which are sampled by the analog-to-digital converter. However, as soon as array operation is considered, antenna cross-talk is likely to violate this assumption. In addition, a dense antenna array requires the antennas to have small outer dimensions. This can be achieved by dielectrically scaling the antennas, which - in turn - leads to a low  $(7 \Omega)$  feeding point impedance. The latter has to be interfaced by the subtraction circuit. The topology shown in Fig. 18 is a first approach towards an analog subtractor which provides appropriate single-ended inputs to interface with both, a dielectrically scaled antenna and

<sup>7</sup> Rhode & Schwarz SMJ100A

<sup>&</sup>lt;sup>8</sup> Rhode & Schwarz FSV

the DAC. In this implementation, noise figure is traded against linearity, as input signals close to 0 dBm might occur. For its implementation, component parameters have been determined by a semi-automated procedure, in which the input stage - a common base configuration - was optimized with respect to input power matching, while an upper bound for  $NF_{min}$  was respected and noise matching was clearly observed. As in the case of the feedback-sampling amplifier according to Fig. 15, signal subtraction is performed in the current domain using a common output node.

**Figure 18.** Schematic diagram (left) and chip photo (right) of the subtractor.

A printed circuit board has been designed to enable joint performance evaluation of this amplifier and the 7  $\Omega$  antenna. Due to the low feeding point impedance, separate characterization is less useful. To avoid problems involved in interconnecting devices with 7  $\Omega$  reference impedance, the amplifier should directly be attached to the antenna, which is supported by the board. Thus, both evaluation and refinement of this circuit will have to be performed in close collaboration with our partners from the ultraMedis project.

#### 4. Transmitter circuits

#### 4.1. Introduction

The circuits introduced in this section serve for the M-sequence topology. They have been implemented in a cost-efficient 0.25 µm Silicon Germanium BiCMOS technology, which opens up new fields of ultra-wideband radar applications. In the following sub-chapters, the design of different hardware blocks for the ultra-wideband radar front-end is presented. The design of a multi-purpose M-Sequence generator is presented which acts as a pulse compression modulator and exhibits an up-conversion mixer. A highly efficient powerdistributed amplifier has been implemented utilizing a novel cascode power matching

approach to achieve superior output power performance. Additionally, a fully differential broadband amplifier using cascaded emitter followers has been designed that exhibits a variable gain control and excellent broadband performance.

#### 4.2. M-sequence generator

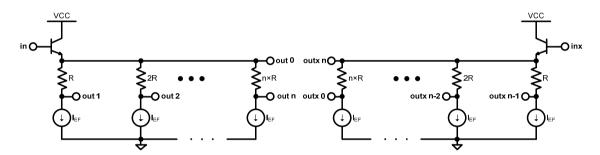

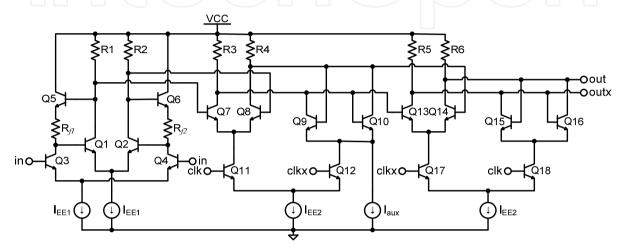

The well-known very broadband spectrum of M-sequences is widely used for testing the correct functionality of broadband integrated circuits, such as amplifiers, multiplexers, and transceivers. The run for higher data rates and amplifiers with broader bandwidth often outperforms commercially available test equipment and necessitates some sources to test these circuits. The measurement equipment vendors cannot supply data sources as fast as the technology evolves. The application which is targeted in this chapter is that M-sequences are used for pulse compression in ultra-wideband radar systems. For this application, it is important that the generator consumes little energy only, and it should generate a sequence of appropriate length (see (2)). Early high-speed PRBS generators for high data rates have been employed in III/V HBT technologies [28]. Moreover, a 110 Gb/s PRBS generator has been published in [29] using InP HBT technology with a transit frequency ( $f_T$ ) more than 300 GHz. Recently, several PRBS generator circuits have been published in SiGe bipolar technology for test purposes in fiber-optic communications. In [30] a 100 Gb/s  $2^7 - 1$  PRBS generator has been implemented in a 200 GHz  $f_T$  SiGe bipolar technology. As in the 80 Gb/s  $2^{31}-1$  pseudo random binary sequence generator introduced in [31], the output of the shift register has been multiplexed to achieve a higher maximum data rate. However, these circuits have a power consumption of 1.9-9.8W and utilize cost-intensive high-end processes. A  $4\times23$  Gb/s  $2^7-1$ PRBS generator with a power consumption of 60 mW per lane has been publicized in [32] utilizing a 150 GHz  $f_T$  SiGe BiCMOS technology. A  $2^7 - 1$  multiplexed PRBS generator in 0.13 µm bulk CMOS exhibits 24 Gb/s output data rate [33]. In the following section, the circuit implementation with measurement results of the M-Sequence generator is presented.

#### 4.2.1. Upconverted M-sequence generator

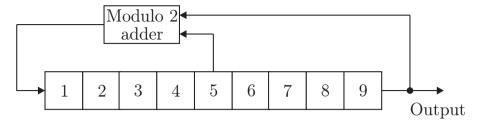

A simple way to generate M-sequences is to utilize a digital linear feedback shift register (LFSR), as depicted in Fig. 19. This device generates a binary pseudo-random code of length  $2^n-1$ , where n is the number of stages in the shift register. Feedback is provided by adding the output of the shift register, modulo two, to the output of one of the previous stages. The actual sequence obtained depends on both the feedback connections and the initial loading of the register.

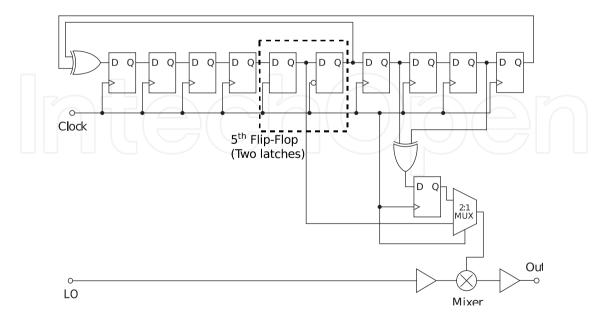

The proposed architecture depicted in Fig. 20 consists of serially connected shift registers with the characteristic polynomial

$$f(x) = x^9 \oplus x^5 \oplus 1 \tag{23}$$

an additional XOR gate acting as a modulo-2 adder to yield the delayed sequence, and one multiplexer. The selected feedback in the proposed architecture enables to generate two M-

**Figure 19.** Nine bit linear feedback shift register for  $9^{th}$  order M-Sequence.

sequences with a mutual shift of half the word length. Those are multiplexed to yield the same M-sequence at twice the data rate. The input for the multiplexer is set between the two latches of the fifth flip-flop highlighted Fig. 20. This leads to a phase shift of half the pulse width in order to achieve the maximum voltage swing at the input of the multiplexer. Thus, the proposed architecture makes it possible to boost the circuit performance at the cost of an additional adder and a multiplexer. The architecture is extended to provide the possibility of upconversion for the generated M-sequence. This has been facilitated by implementing a mixer core at the output of the multiplexed LFSR. The mixer performs a BPSK modulation of the 9<sup>th</sup> order M-sequence signal generated by the multiplexed shift register. The circuit was implemented as an XOR gate instead of a conventional Gilbert cell as opposed to [34]. The actual circuit is nearly identical but the XOR operates in the limiting region compared to the small-signal operation of the Gilbert cell. The limiting behavior simplifies the design and requirements of the mixer, and results in lower power consumption. No emitter degeneration has to be implemented to increase linearity for large signal inputs. The XOR gate is driven by a LO buffer that can be digitally controlled to allow the generation of baseband M-sequence signals without the need for up-conversion. An additional output buffer with a resistively matched output has been included in order to control the output voltage swing in a wide range.

**Figure 20.** Circuit architecture of the proposed  $2^9 - 1$  M-sequence generator providing the possibility of up-conversion for the radar signal.

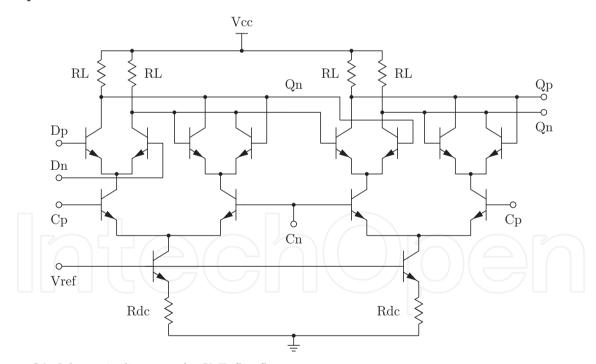

Once the functional simulations have been completed, each individual block is designed on the transistor level. As the multiplexing architecture has been chosen, the flip-flops only have to work at half the operation speed. Standard CML flip-flops have been designed consisting of two latches, which inhibit two differential pairs. A schematic diagram of a CML flip-flop is depicted in Fig. 21. The flip-flops used in the LFSR are designed to offer a differential output voltage of  $2\times300\,$  mV. According to [31], the tail current  $I_T$  and the emitter area  $A_s$  are related by

$$A_e = l_e \times w_e = \frac{I_T}{1.5 J_{peak f_T}}$$

(24)

for fastest switching time such that  $J_{peak\,f_T}$  is the current density for maximum  $f_T$ . The lowest tail current is set by the minimum allowed transistor size, which is  $l_e\times w_e=0.84~\mu m\times 0.42~\mu m$ . Thus, the tail current is chosen to be 0.85 mA whereby the collector current for the maximum transit frequency  $f_T$  is 1.25 mA for a 84  $\mu m\times 0.42~\mu m$  transistor. The output voltage swing of each flip-flop was set to 2×250 mV. Simulations indicate that the latches work up to 12.5 Gb/s, which is sufficient for a 25 Gb/s multiplexed M-sequence.

**Figure 21.** Schematic diagram of a CML flip-flop.

#### 4.2.2. Simulated and measured results

The M-sequence generator has been simulated in time domain to find out the maximum data rate and to verify the correct function of the register. At clock frequencies higher than the maximum allowable clock frequency, the PRBS register does not work as expected and

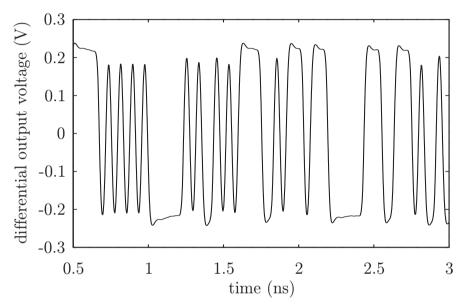

the output is not an M-sequence. A simulated waveform of a 25 Gb/s M-sequence is shown in Fig. 22 using the techniques described above. It can be seen that every bit can be distinguished from each other. A single bit has a slightly lower output voltage than a bit sequence with the same value, which is caused by the limited output bandwidth. As mentioned before, the mixer and the output buffer both have a limiting character which attenuates the flip-flop glitches. Thus, the waveform exhibits low ripple, actually at sequences with a series of equal bits, which indicates that the clock feed through is very low. However, the output waveform exhibits some deviations, which is quite common for circuits at this high data rate. This behavior may result from the slightly inductive behavior of an emitter follower in the signal chain. As long as the circuit is stable, this does not cause problems.

Figure 22. Simulated M-sequence waveform at 25 Gb/s data rate.

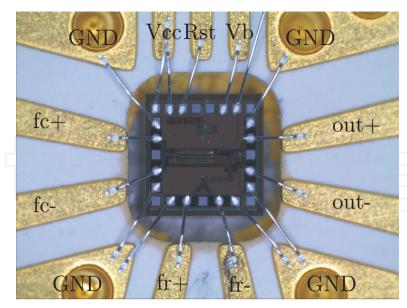

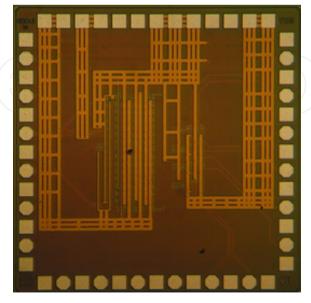

The M-sequence generator chip is placed on a Rogers TMM10i ceramic substrate for wire bonding. In order to protect the circuit mechanically and keep the bond wires as short as possible, it is placed in a topside cavity and fixed utilizing an electrical and thermal conductive epoxy glue, as shown in Fig. 23. The thickness of the ceramic substrate has been chosen to be 381 µm, which is almost equal to the chip height of 370 µm and the glue. Thus, the distance between the substrate edge and the bond pad can be reduced. The continuous ground plane below ensures a good thermal conduction, and 1.2 mm thick FR4 stabilize the brittle ceramic substrate.

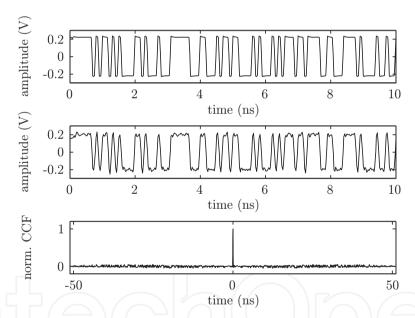

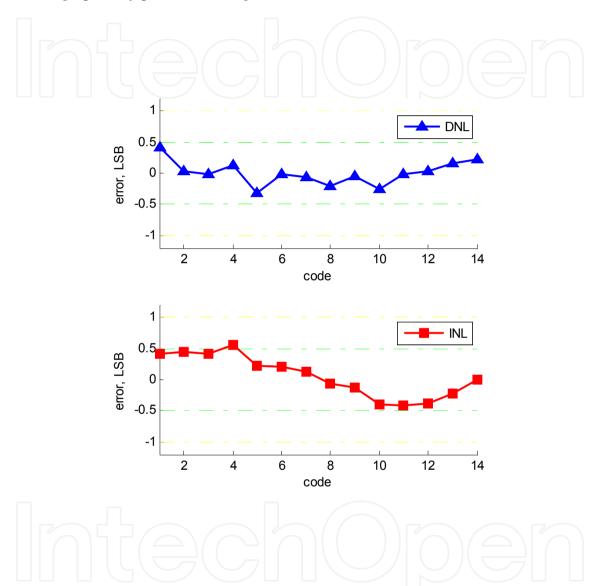

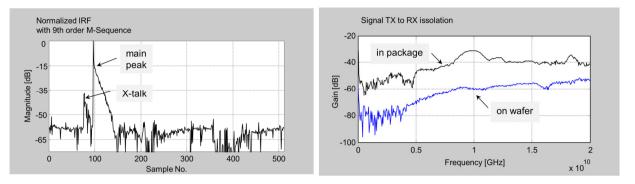

The correct function of the generator can be checked through calculation of the normalized autocorrelation function of one complete M-sequence. The calculation of the ACF has been implemented in Matlab. As the correlation properties are of substantial interest for radar applications utilizing pulse compressed waveforms, the PRBS signal is measured with an Agilent DSO 91204A oscilloscope and compared with the simulation results. The simulated and measured 10 Gb/s waveforms together with the normalized cross correlation function of the measured signal are presented in Fig. 24.

Figure 23. Photograph of the bonded M-sequence generator chip placed in a topside cavity on a ceramic substrate.

Figure 24. Simulated (top) and measured (middle) time domain representation of the proposed 10 Gb/s M-Sequence and their normalized cross correlation function.

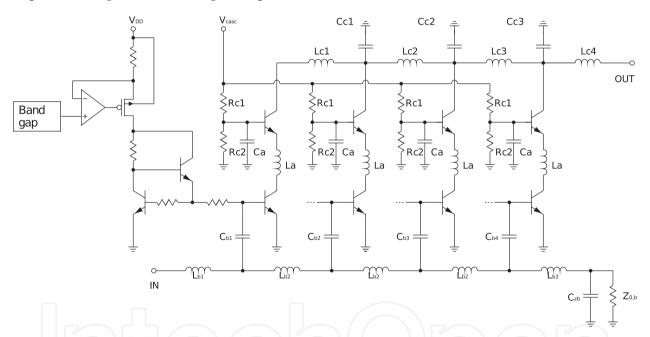

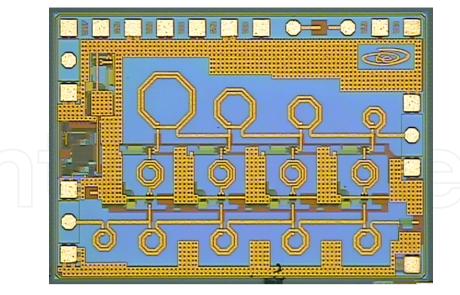

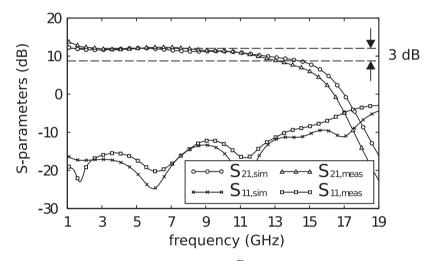

#### 4.3. Distributed power amplifier

The transmitted random sequence is subjected to high losses especially when transmitted through human body cells. Thus, a power amplifier is required to be placed directly before the antenna to increase the signal power. Distributed amplifiers (DAs) are appealing aspirants for UWB systems due to their inherently large bandwidth. The two major challenges in designing distributed power amplifiers are maintaining high linearity over the entire bandwidth, since narrowband linearization techniques cannot be utilized, and achieving high output power and efficiency. In order to increase the HBT distributed power

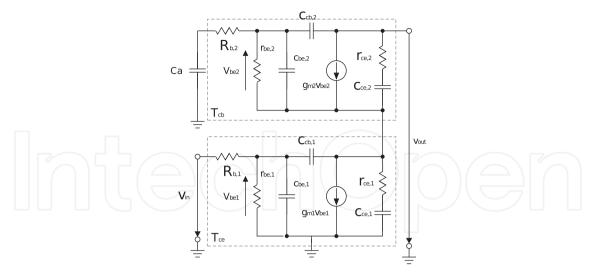

amplifier performance, which is limited by the characteristics of the active cells used [35], alternative structures are investigated. The cascode cell is an appealing circuit due to its higher output impedance, higher breakdown voltage, and reduced Miller effect. Moreover, loading the two transistors by the required impedance for optimum power leads to an output power twice as high as compared to a single transistor. However, the conventional cascode configuration does not meet these conditions since the common base transistor's  $(T_{ch})$  low-input impedance restricts the output voltage excursion of the common emitter transistor ( $T_{ce}$ ). Therefore, it does not see its optimum power load impedance. In addition, the power performance of the cascode cell becomes one of the most important challenges to obtain maximum output power over the required bandwidth. To be power optimized, another series capacitor  $C_a$  is inserted on the base of  $T_{cb}$  to avoid its early power saturation compared to  $T_{ce}$ . A small signal model of the modified cascode gain cell is depicted in Fig. 25. The input impedance of the common base transistor can be calculated as follows:

$$z_{in,cb} = r_{be,2} + R_{b,2} + \frac{1}{j\omega C_a}$$

(25)

The capacitor  $C_a$  and input impedance  $z_{in,cb}$  act as a voltage divider between the optimum values for  $v_{ce,1}$  and  $v_{be,2}$ .

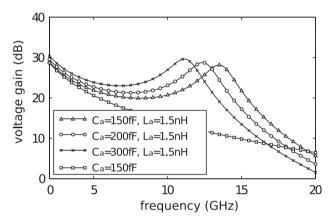

In order to achieve higher gain and greater bandwidth, an additional inductor is added between the collector of  $T_{ce}$  and the emitter of  $T_{cb}$ . The influence of a 1.5 nH inductor and various capacitances on the voltage gain of the cascode cell is demonstrated in Fig. 26. The small-signal schematic diagram of the modified cascode cell with inductive peaking is presented in Fig. 27a. The output resistance of the modified cascode circuit can be written as

$$z_{out} \approx z_{ce,2} + \left[ \left( j\omega L_a + z_{ce,1} \right) \mid \left( z_{be,2} + R_{b,2} + \frac{1}{j\omega C_a} \right) \right]$$

(26)

neglecting the influence of miller capacitance  $\,c_{cb}^{}$  . This leads to a resonance effect which is dominated by  $L_a$ ,  $C_a$  and  $c_{be}$ . The self-resonant frequency  $f_r$  of the LC low pass can be calculated as

$$f_r = \frac{1}{\pi \sqrt{\frac{L_a C_a c_{be,2}}{C_a + c_{be,2}}}}$$

(27)

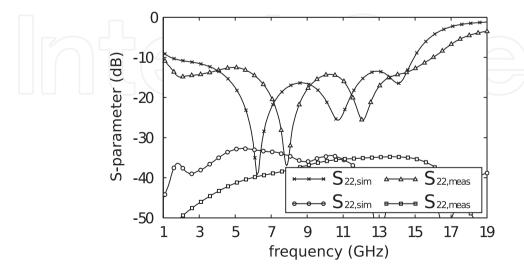

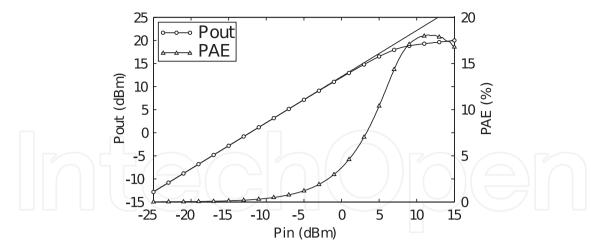

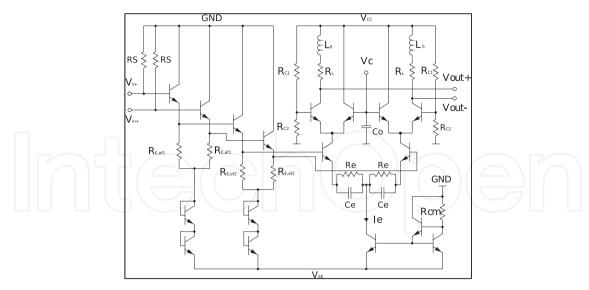

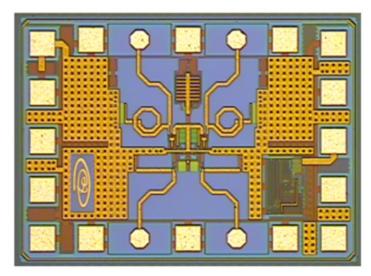

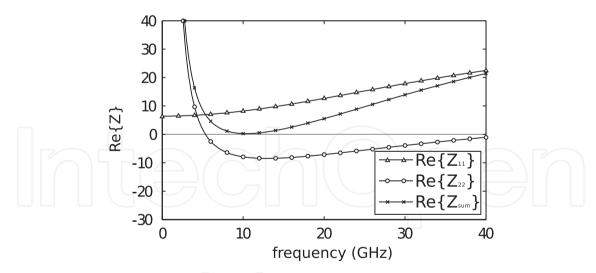

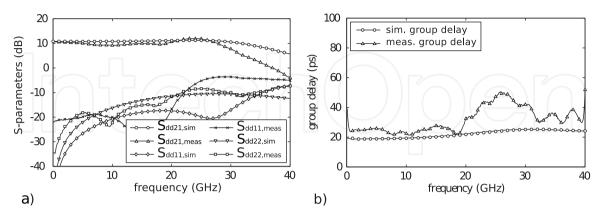

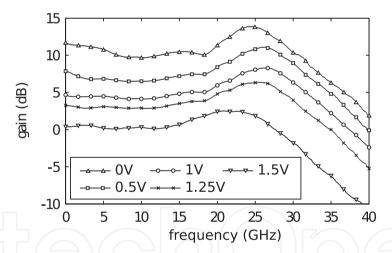

The resonant frequency shows good agreement with the theoretical considerations set out in (27).